### Advanced PWM and Dual Linear Power Control

### **Features**

- 3 Regulated Voltage are provided

- Switching Power for VTT(1.25V)

- Linear1 Regulator for FBVDDQ(2.5V)

- Linear2 Regulator for NVVDD(2.05V)

- Simple Single-Loop Control Design

- Voltage-Mode PWM Control

- Excellent Output Voltage Regulation

• PWM Output: ±1%

• Linear Output: ±3%

- Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Ratio

- Power-Good Output Voltage Monitor

- Over-Voltage and Over-Current Fault Monitors

- Small Converter Size

- Constant Frequency Operation(200kHz)

- Programmable Oscillator from 50kHz to 1MHz

- Reduce External Component Count

# **Applications**

- Motherboard Power Regulation for Computers

- Low-Voltage Distributed Power Supplies

- VGA Card Power Regulation

## **General Description**

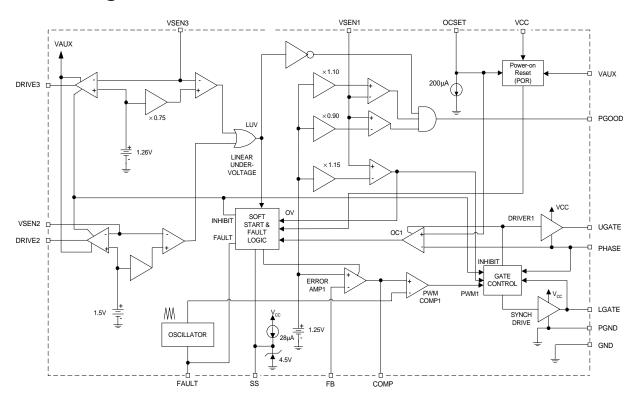

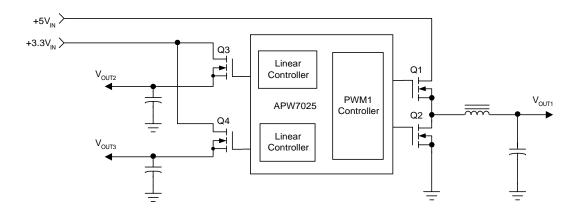

The APW7025 integrates a PWM controller and Dual linear controller, as well as the monitoring and protection functions into a single package, which provides three controlled power outputs with over-voltage and over-current protections. The PWM controller regulates the DDR reference voltage with a synchronous-rectified buck converter. The linear controller regulates power for microprocessor core voltage and Memory Voltage.

The precision reference and voltage-mode PWM control provide  $\pm 2\%$  static regulation. The linear controller drives an external N-channel MOSFET to provide adjustable voltage.

The APW7025 monitors all the output voltages , and a single Power Good signal is issued when the PWM Voltage is within 10% of the 1.25V setting and the other output levels are above their under-voltage thresholds. Additional built-in over-voltage protection for the PWM output uses the lower MOSFET to prevent output voltages above 115% of the 1.25V setting. The PWM over-current function monitors the output current by using the voltage drop across the upper MOSFET's  $\rm R_{\rm DS(ON)}$  , eliminating the need for a current sensing resistor.

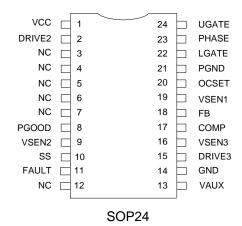

# Pin Description

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

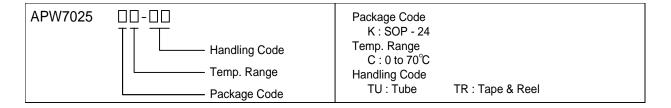

# **Ordering Information**

# **Block Diagram**

# **Absolute Maximum Ratings**

| Symbol           | Parameter                           | Rating                          | Unit |  |

|------------------|-------------------------------------|---------------------------------|------|--|

| V <sub>cc</sub>  | Supply Voltage                      | 15                              | V    |  |

| $V_{I}, V_{O}$   | Input , Output or I/O Voltage       | GND -0.3 V to $V_{\rm CC}$ +0.3 | V    |  |

| T <sub>A</sub>   | Operating Ambient Temperature Range | 0 to 70                         | °C   |  |

| T <sub>J</sub>   | Junction Temperature Range          | 0 to 125                        | °C   |  |

| T <sub>STG</sub> | Storage Temperature Range           | -65 to +150                     | °C   |  |

| T <sub>s</sub>   | Soldering Temperature               | 300 ,10 seconds                 | °C   |  |

## **Thermal Characteristics**

| Symbol           | Parameter                              | Value | Unit |

|------------------|----------------------------------------|-------|------|

| R <sub>eJA</sub> | Thermal Resistance in Free Air         |       |      |

| 0071             | SOIC                                   | 75    | °C/W |

|                  | SOIC (with 3in <sup>2</sup> of Copper) | 65    |      |

# **Electrical Characteristics**

(Recommended operating conditions , Unless otherwise noted) Refer to Block and Simplified Power System Diagrams , and Typical Application Schematic

| Symbol               | Parameter                           | Test Conditions                              | APW7025 |       |      |           |

|----------------------|-------------------------------------|----------------------------------------------|---------|-------|------|-----------|

|                      |                                     |                                              | Min.    | Тур.  | Max. | Unit      |

| V <sub>cc</sub> Supp | ly Current                          |                                              |         |       |      |           |

| I <sub>cc</sub>      | Nominal Supply Current              | UGATE, LGATE, DRIVE2,<br>DRIVE3 open         |         | 9     |      | mA        |

| Power-or             | n Reset                             |                                              |         |       |      |           |

|                      | Rising VCC Threshold                | Vocset=4.5V                                  |         |       | 10.4 | V         |

|                      | Falling VCC Threshold               | Vocset=4.5V                                  | 8.2     |       |      | V         |

|                      | Rising VAUX Threshold               | Vocset=4.5V                                  |         | 2.5   |      | V         |

|                      | VAUX Threshold Hysteresis           | Vocset=4.5V                                  |         | 0.5   |      | V         |

|                      | Rising V <sub>OCSET</sub> Threshold |                                              |         | 1.26  |      | V         |

| Oscillato            | r                                   |                                              | •       | •     | •    |           |

| F <sub>ocs</sub>     | Free Running Frequency              | RT= Open                                     | 185     | 200   | 215  | kHz       |

| $\Delta V_{OSC}$     | Ramp Amplitude                      | RT= Open                                     |         | 1.9   |      | $V_{P-P}$ |

|                      | Bandgap Reference                   |                                              |         |       |      |           |

|                      | DAC Voltage accuracy                |                                              | -1.0    |       | +1.0 | %         |

| $V_{BG}$             | Bandgap Reference Voltage           |                                              |         | 1.265 |      | V         |

|                      | Bandgap Reference Tolerance         |                                              | -2.5    |       | +2.5 | %         |

| Linear Ro            | egulators (OUT2, OUT3)              |                                              | ,       |       |      |           |

|                      | Regulation (All Linears)            |                                              |         | 3     |      | %         |

|                      | Output Drive Current (All Liners)   | VAUX-V <sub>DRIVE</sub> >0.6V                | 20      | 40    |      | mA        |

| Synchro              | nous PWM Controller Error Amp       | lifier                                       |         | •     | •    |           |

|                      | DC Gain                             |                                              |         | 88    |      | dB        |

| GBWP                 | Gain-Bandwidth Product              |                                              |         | 15    |      | MHz       |

| SR                   | Slew Rate                           | COMP=10pF                                    |         | 6     |      | V/μs      |

| PWM Co               | ntroller Gate Driver                | •                                            |         |       |      |           |

| I <sub>UGATE</sub>   | UGATE Source                        | V <sub>CC</sub> =12V, V <sub>UGATE</sub> =6V |         | 1     |      | Α         |

|                      | UGATE Sink                          | V <sub>UGATE1-PHASE</sub> =1V                |         |       | 3.5  | Ω         |

| I <sub>LGATE</sub>   | LGATE Source                        | $V_{CC}$ =12V, $V_{LGATE}$ =1V               |         | 1     |      | Α         |

| R <sub>LGATE</sub>   | LGATE Sink                          | V <sub>LGATE</sub> = 1V                      |         |       | 3    | Ω         |

### **Electrical Characteristics Cont.**

| Symbol             | Parameter                               | Test Conditions             | APW7025 |      |      |      |  |

|--------------------|-----------------------------------------|-----------------------------|---------|------|------|------|--|

|                    |                                         |                             | Min.    | Тур. | Max. | Unit |  |

| Protectio          | Protection                              |                             |         |      |      |      |  |

|                    | VSEN1 Over-Voltage<br>(VSEN1/DACOUT)    | VSEN1 Rising                |         | 115  | 120  | %    |  |

| I <sub>OVP</sub>   | FAULT Souring Current                   | V <sub>FAULT/RT</sub> =2.0V |         | 8.5  |      | mA   |  |

| I <sub>OCSET</sub> | OCSET Current Source                    | $V_{OCSET} = 4.5V_{DC}$     | 170     | 200  | 230  | μΑ   |  |

| I <sub>ss</sub>    | Soft Start Current                      |                             |         | 28   |      | μΑ   |  |

| Power Good         |                                         |                             |         |      |      |      |  |

|                    | VSEN1 Upper Threshold<br>(VSEN1/DACOUT) | VSEN1 Rising                | 108     |      | 110  | %    |  |

|                    | VSEN1 Under Voltage<br>(VSEN1/DACOUT)   | VSEN1 Rising                | 92      |      | 94   | %    |  |

|                    | VSEN1 Hysteresis (VSEN1<br>/DACOUT)     | Upper /Lower Threshold      |         | 2    |      | %    |  |

| $V_{PGOOD}$        | PGOOD Voltage Low                       | I <sub>PGOOD</sub> = -4mA   |         |      | 8.0  | V    |  |

## **Functional Pin Description**

### VCC (Pin 1)

Provide a 12V bias supply for the IC to this pin. This pin also provides the gate bias charge for all the MOSFETs controlled by the IC. The voltage at this pin is monitored for Power-On Reset (POR) purposes.

### DRIVE2 (Pin 2)

Connect this pin to the gate of an external MOSFET. This pin provides the drive for the NVVDD regulator's pass transistor.

#### PGOOD (Pin 8)

PGOOD is an open collector output used to indicate the status of the output voltages. This pin is pulled low when the synchronous regulator output is not within ±10% of the DACOUT reference voltage or when any of the other outputs are below their undervoltage thresholds.

### VSEN2 (Pin 9)

Connect this pin to a resistor divider to set the linear

regulator (NVVDD) output voltage.

#### SS (Pin 10)

Connect a capacitor from this pin to ground. This capacitor, along with an internal 28µA current source, sets the soft-start interval of the converter.

### FAULT (Pin 11)

This pin provides oscillator switching frequency adjustment. By placing a resistor (R<sub>→</sub>) from this pin to GND, the nominal 200kHz switching frequency is increased according to the following equation:

Fs =200kHz +

$$5 \times 10^6 / R_{T} (k\Omega)$$

( $R_{T}$  to GND)

Conversely, connecting a resistor from this pin to VCC reduces the switching frequency according to the following equation:

Fs = 200kHz +

$$4 \times 10^7 / R_{_T} (k\Omega) (R_{_T} \text{ to } 12\text{V})$$

Nominally, the voltage at this pin is 1.26V. In the event of an over-voltage or over-current condition, this pin

# Functional Pin Description Cont.

is internally pulled to VCC.

### VAUX (Pin 13)

This pin provides boost current for the linear regulator's output drives in the event bipolar NPN transistors (instead of N-channel MOSFETs) are employed as pass elements. The voltage at this pin is monitored for power-on reset purposes.

### **GND (Pin 14)**

Signal ground for the IC. All voltage levels are measured with respect to this pin.

### DRIVE3 (Pin 15)

Connect this pin to the gate of an external MOSFET. This pin provides the drive for the FBVDDQ regulator's pass transistor.

#### **VSEN3 (Pin 16)**

Connect this pin to a resistor divider to set the linear regulator (FBVDDQ) output voltage.

#### COMP and FB (Pin 17, and 18)

COMP and FB are the available external pins of the PWM converter error amplifier. The FB pin is the inverting input of the error amplifier. Similarly, the COMP pin is the error amplifier output. These pins are used to compensate the voltage-mode control feedback loop of the synchronous PWM converter.

### **VSEN1 (Pin 19)**

This pin is connected to the PWM converter's output voltage. The PGOOD and OVP comparator circuits use this signal to report output voltage status and for over- voltage protection.

#### OCSET (Pin 20)

Connect a resistor from this pin to the drain of the respective upper MOSFET. This resistor, an internal 200µA current source, and the upper MOSFET's onresistance set the converter over-

current trip point. An over-current trip cycles the softstart function.

The voltage at this pin is monitored for power-on reset (POR) purposes and pulling this pin low with an open drain device will shutdown the IC.

### PGND (Pin 21)

This is the power ground connection. Tie the synchronous PWM converter's lower MOSFET source to this pin.

### LGATE (Pin 22)

Connect LGATE to the PWM converter's lower MOSFET gate. This pin provides the gate drive for the lower MOSFET.

### PHASE (Pin 23)

Connect the PHASE pin to the PWM converter's upper MOSFET source. This pin represents the gate drive return current path and is used to monitor the voltage drop across the upper MOSFET for over-current protection.

#### **UGATE (Pin 24)**

Connect UGATE pin to the PWM converter's upper MOSFET gate. This pin provides the gate drive for the upper MOSFET.

# **Typical Characteristics**

6

## **Customer Service**

### **Anpec Electronics Corp.**

Head Office:

5F, No. 2 Li-Hsin Road, SBIP, Hsin-Chu, Taiwan, R.O.C. Tel: 886-3-5642000

Fax: 886-3-5642050

Taipei Branch:

7F, No. 137, Lane 235, Pac Chiao Rd., Hsin Tien City, Taipei Hsien, Taiwan, R. O. C.

Tel: 886-2-89191368 Fax: 886-2-89191369