# **High Temperature H-bridge Motor Driver**

### **DATASHEET**

#### **Features**

- PWM and direction-controlled driving of four externally-powered NMOS transistors

- High temperature capability up to 200°C junction

- A programmable dead time is included to avoid peak currents within the H-bridge

- Integrated charge pump to provide gate voltages for high-side drivers and to supply the gate of the external battery reverse protection NMOS

- 5V/3.3V regulator and current limitation function

- Reset derived from 5V/3.3V regulator output voltage

- A programmable window watchdog

- Battery overvoltage protection and battery undervoltage management

- Overtemperature warning and protection (Shutdown)

- High voltage serial interface for communication

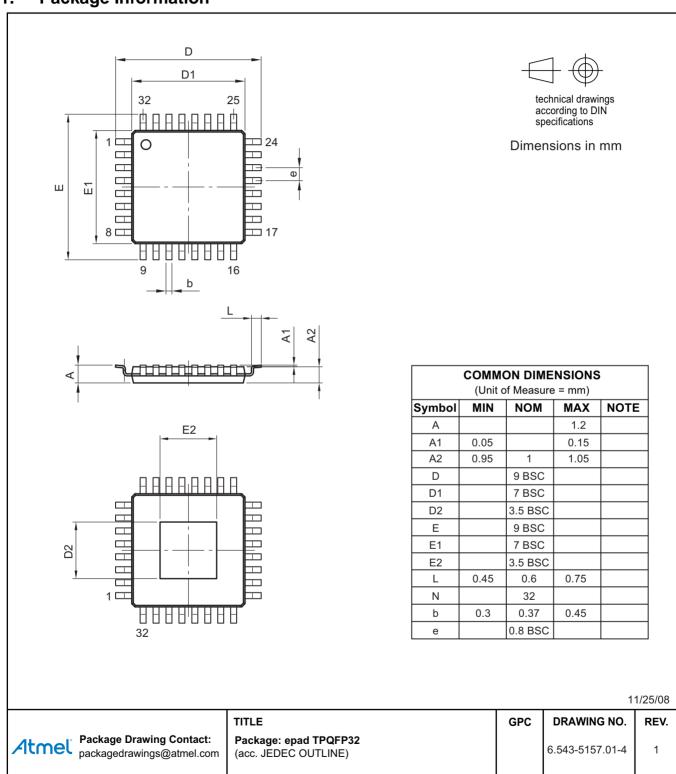

- TPQFP package

# **Description**

The Atmel<sup>®</sup> ATA6824C is designed for DC motor control application in automotive high temperature environment like in mechatronic assemblies in the vicinity of the hot engine, e.g. turbo charger. With a maximum junction temperature of 200°C, Atmel ATA6824C is suitable for applications with an ambient temperature up to 150°C.

The IC includes 4 driver stages to control 4 external power MOSFETs. An external microcontroller provides the direction signal and the PWM frequency. In PWM operation, the high-side switches are permanently on while the low-side switches are activated by the PWM frequency. Atmel ATA6824C contains a voltage regulator to supply the microcontroller; via the input pin VMODE the output voltage can be set to 5V or 3.3V respectively.

The on-chip window watchdog timer provides a pin-programmable time window. The watchdog is internally trimmed to an accuracy of 10%. For communication a high voltage serial interface with a maximum data range of 20kBaud is integrated.

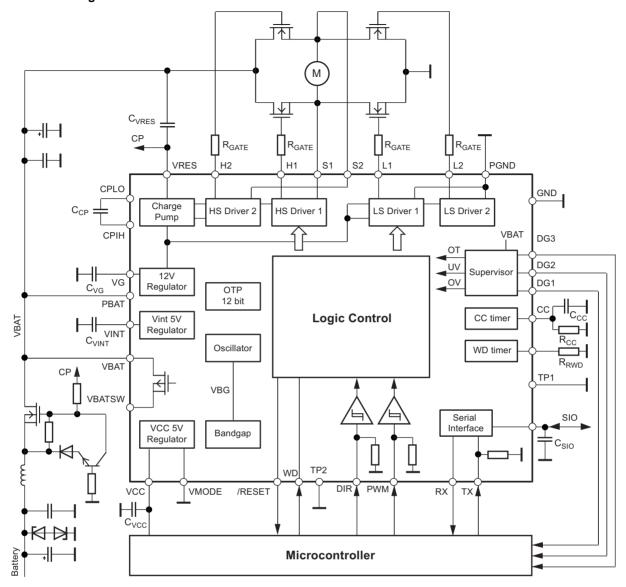

Figure 1. Block Diagram

# 1. Pin Configuration

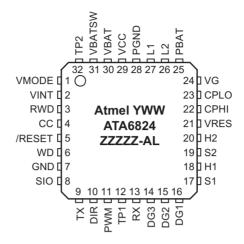

Figure 1-1. Pinning TPQFP32

Note: YWW Date code (Y = Year - above 2000, WW = week number)

ATA6824C Product name ZZZZZ Wafer lot number

AL Assembly sub-lot number

Table 1-1. Pin Description

| Pin | Symbol | I/O | Function                                                                   |

|-----|--------|-----|----------------------------------------------------------------------------|

| 1   | VMODE  | I   | Selector for V <sub>CC</sub> and interface logic voltage level             |

| 2   | VINT   | I/O | Blocking capacitor 220nF/10V/X7R                                           |

| 3   | RWD    | I   | Resistor defining the watchdog interval                                    |

| 4   | CC     | I/O | RC combination to adjust cross conduction time                             |

| 5   | /RESET | 0   | Reset signal for microcontroller                                           |

| 6   | WD     | I   | Watchdog trigger signal                                                    |

| 7   | GND    | I   | Ground for chip core                                                       |

| 8   | SIO    | I/O | High Voltage (HV) serial interface                                         |

| 9   | TX     | I   | Transmit signal to serial interface from microcontroller                   |

| 10  | DIR    | I   | Defines the rotation direction for the motor                               |

| 11  | PWM    | I   | PWM input controls motor speed                                             |

| 12  | TP1    | _   | Test pin to be connected to GND                                            |

| 13  | RX     | 0   | Receive signal from serial interface for microcontroller                   |

| 14  | DG3    | 0   | Diagnostic output 3                                                        |

| 15  | DG2    | 0   | Diagnostic output 2                                                        |

| 16  | DG1    | 0   | Diagnostic output 1                                                        |

| 17  | S1     | I/O | Source voltage H-bridge, high-side 1                                       |

| 18  | H1     | 0   | Gate voltage H-bridge, high-side 1                                         |

| 19  | S2     | I/O | Source voltage H-bridge, high-side 2                                       |

| 20  | H2     | 0   | Gate voltage H-bridge, high-side 2                                         |

| 21  | VRES   | I/O | Gate voltage for reverse protection NMOS, blocking capacitor 470nF/25V/X7R |

| 22  | CPHI   | I   | Charge pump capacitor 220nF/25V/X7R                                        |

| 23  | CPLO   | 0   | Charge pump capacitor 220HF/25V/A/R                                        |

Table 1-1. Pin Description (Continued)

| Pin | Symbol | I/O | Function                                                               |

|-----|--------|-----|------------------------------------------------------------------------|

| 24  | VG     | I/O | Blocking capacitor 470nF/25V/X7R                                       |

| 25  | PBAT   | I   | Power supply (after reverse protection) for charge pump and H-bridge   |

| 26  | L2     | 0   | Gate voltage H-bridge, low-side 2                                      |

| 27  | L1     | 0   | Gate voltage H-bridge, low-side 1                                      |

| 28  | PGND   | I   | Power ground for H-bridge and charge pump                              |

| 29  | VCC    | 0   | 5V/100 mA supply for microcontroller, blocking capacitor 2.2μF/10V/X7R |

| 30  | VBAT   | I   | Supply voltage for IC core (after reverse protection)                  |

| 31  | VBATSW | 0   | 100 $\Omega$ PMOS switch from V <sub>VBAT</sub>                        |

| 32  | TP2    | _   | Test pin to be connected to GND                                        |

### 2. General Statement and Conventions

- Parameter values given without tolerances are indicative only and not to be tested in production

- Parameters given with tolerances but without a parameter number in the first column of parameter table are

"guaranteed by design" (mainly covered by measurement of other specified parameters). These parameters are not to

be tested in production. The tolerances are given if the knowledge of the parameter tolerances is important for the

application

- The lowest power supply voltage is named GND

- All voltage specifications are referred to GND if not otherwise stated

- Sinking current means that the current is flowing into the pin (value is positive)

- Sourcing current means that the current is flowing out of the pin (value is negative)

#### 2.1 Related Documents

- Qualification of integrated circuits according to Atmel<sup>®</sup> HNO procedure based on AEC-Q100

- AEC-Q100-004 and JESD78 (Latch-up)

- ESD STM 5.1-1998

- CEI 801-2 (only for information regarding ESD requirements of the PCB)

# 3. Application

#### 3.1 General Remark

This chapter describes the principal application for which the Atmel<sup>®</sup> ATA6824C was designed. Because Atmel cannot be considered to understand fully all aspects of the system, application and environment, no warranties of fitness for a particular purpose are given.

Table 3-1. Typical External Components (See also Figure 1 on page 2)

| Component         | Function                                   | Value                    | Tolerance |

|-------------------|--------------------------------------------|--------------------------|-----------|

| C <sub>VINT</sub> | Blocking capacitor at VINT                 | 220nF, 10V, X7R          | 50%       |

| C <sub>VCC</sub>  | Blocking capacitor at VCC                  | 2.2µF, 10V, X7R          | 50%       |

| C <sub>CC</sub>   | Cross conduction time definition capacitor | Typical 680pF, 100V, COG |           |

| R <sub>CC</sub>   | Cross conduction time definition resistor  | Typical 10kΩ             |           |

| $C_{VG}$          | Blocking capacitor at VG                   | Typical 470nF, 25V, X7R  | 50%       |

| C <sub>CP</sub>   | Charge pump capacitor                      | Typical 220nF, 25V, X7R  |           |

| C <sub>VRES</sub> | Reservoir capacitor                        | Typical 470nF, 25V, X7R  |           |

| R <sub>RWD</sub>  | Watchdog time definition resistor          | Typical 51kΩ             |           |

| C <sub>SIO</sub>  | Filter capacitor for SIO                   | Typical 220pF, 100V      |           |

# 4. Functional Description

# 4.1 Power Supply Unit with Supervisor Functions

### 4.1.1 Power Supply

The IC is supplied by a reverse-protected battery voltage. To prevent it from destruction, proper external protection circuitry has to be added. It is recommended to use at least a capacitor combination of storage and HF caps behind the reverse protection circuitry and closed to the VBAT pin of the IC (see Figure 1 on page 2).

An internal low-power and low drop regulator ( $V_{INT}$ ), stabilized by an external blocking capacitor, provides the necessary low-voltage supply for all internal blocks except the digital IO pins. This voltage is also needed in the wake-up process. The low-power band gap reference is trimmed and is used for the bigger VCC regulator, too. All internal blocks are supplied by the internal regulator.

The internal supply voltage V<sub>INT</sub> must not be used for any other supply purpose!

Nothing inside the IC except the logic interface to the microcontroller is supplied by the 5V/3.3V VCC regulator.

A power-good comparator checks the output voltage of the  $V_{INT}$  regulator and keeps the whole chip in reset as long as the voltage is too low.

There is a high-voltage switch which brings out the battery voltage to the pin VBATSW for measurement purposes. This switch is switched ON for VCC = HIGH and stays ON in case of a watchdog reset. The signal can be used to switch on external voltage regulators, etc.

### 4.1.2 Voltage Supervisor

This block is intended to protect the IC and the external power MOS transistors against overvoltage on battery level and to manage undervoltage on it.

Function: in case of both overvoltage alarm ( $V_{THOV}$ ) and of undervoltage alarm ( $V_{THUV}$ ) the external NMOS motor bridge transistors will be switched off. The failure state will be flagged via DG2. No other actions will be carried out. The undervoltage comparator is connected to the pin VBAT while the overvoltage comparator is connected to pin PBAT. Both are filtered by a first-order low pass with a corner frequency of typical 15kHz.

#### 4.1.3 Temperature Supervisor

There is a temperature sensor integrated on-chip to prevent the IC from overheating due to a failure in the external circuitry and to protect the external NMOSFET transistors.

In case of detected overtemperature (180°C), the diagnostic pin DG3 will be switched to "H" to signalize overtemperature warning to the microcontroller. It should undertake actions to reduce the power dissipation in the IC. In case of detected overtemperature (200°C), the  $V_{CC}$  regulator and all drivers including the serial interface will be switched OFF immediately and /RESET will go LOW.

Both temperature thresholds are correlated. The absolute tolerance is ±15K and there is a built-in hysteresis of about 10K to avoid fast oscillations. After cooling down below the 170°C threshold; the IC will go into Active mode.

The occurrence of overtemperature shutdown is latched in DG3. DG3 stays on high until first WD trigger.

### 4.2 5V/3.3V VCC Regulator

The 5V/3.3V regulator is fully integrated on-chip. It requires only a  $2.2\mu F$  ceramic capacitor for stability and has 100 mA current capability. Using the VMODE pin, the output voltage can be selected to either 5V or 3.3V. Switching of the output voltage during operation is not intended to be supported. The VMODE pin must be hard-wired to either VINT for 5V or to GND for 3.3V. The logic HIGH level of the microcontroller interface will be adapted to the VCC regulator voltage.

The output voltage accuracy is in general  $< \pm 3\%$ ; in the 5V mode with  $V_{VBAT} < 9V$  it is limited to < 5%.

To prevent destruction of the IC, the current delivered by the regulator is limited to maximum 100mA to 350mA. The delivered voltage will break down and a reset may occur.

Please note that this regulator is the main heat source on the chip. The maximum output current at maximum battery voltage and high ambient temperature can only guaranteed if the IC is mounted on an efficient heat sink.

A power-good comparator checks the output voltage of the VCC regulator and keeps the external microcontroller in reset as long as the voltage is too low.

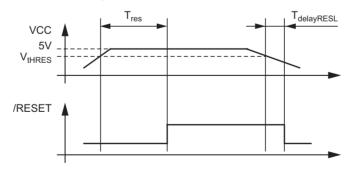

Figure 4-1. Voltage Dependence and Timing of VCC Controlled RESET

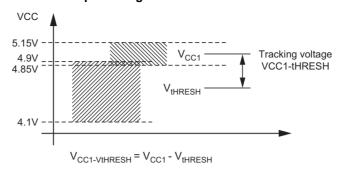

Figure 4-2. Correlation between VCC Output Voltage and Reset Threshold

The voltage difference between the regulator output voltage and the upper reset threshold voltage is bigger than 75mV (VMODE = HIGH) and bigger than 50mV (VMODE = LOW).

# 4.3 Reset and Watchdog Management

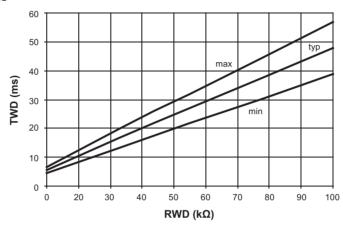

The timing basis of the watchdog is provided by the trimmed internal oscillator. Its period  $T_{OSC}$  is adjustable via the external resistor  $R_{WD}$ .

The watchdog expects a triggering signal (a rising edge) from the microcontroller at the WD input within a period time window of  $T_{WD}$ .

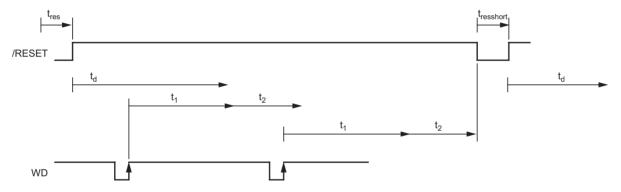

Figure 4-3. Timing Diagram of the Watchdog Function

### 4.3.1 Timing Sequence

For example, with an external resistor  $R_{WD} = 33 \text{ k}\Omega \pm 1\%$  we get the following typical parameters of the watchdog.

$$T_{OSC} = 12.32 \mu s$$

,  $t_1 = 12.1 ms$ ,  $t_2 = 9.61 ms$ ,  $T_{WD} = 16.88 ms \pm 10\%$

The times  $t_{res}$  = 70ms and  $t_d$  = 70ms are fixed values with a tolerance of 10%.

After ramp-up of the battery voltage (power-on reset), the  $V_{CC}$  regulator is switched on. The reset output, /RESET, stays low for the time  $t_{res}$ , then switches to high. For an initial lead time  $t_d$  (for setups in the controller) the watchdog waits for a rising edge on WD to start its normal window watchdog sequence. If no rising edge is detected, the watchdog will reset the microcontroller for  $t_{res}$  and wait  $t_d$  for the rising edge on WD.

Times  $t_1$  (close window) and  $t_2$  (open window) form the window watchdog sequence. To avoid receiving a reset from the watchdog, the triggering signal from the microcontroller must hit the timeframe of  $t_2$  = 9.61ms. The trigger event will restart the watchdog sequence.

Figure 4-4. T<sub>WD</sub> versus R<sub>WD</sub>

If triggering fails, /RESET will be pulled to ground for a shortened reset time of typically 2ms. The watchdog start sequence is similar to the power-on reset.

The internal oscillator is trimmed to a tolerance of  $< \pm 10\%$ . This means that  $t_1$  and  $t_2$  can also vary by  $\pm 10\%$ . The following calculation shows the worst case calculation of the watchdog period  $T_{wd}$  which the microcontroller has to provide.

$$t_{1min}$$

= 0.90 ×  $t_{1}$  = 10.87ms,  $t_{1max}$  = 1.10 ×  $t_{1}$  = 13.28ms

$$t_{2min} = 0.90 \times t_2 = 8.65ms$$

,  $t_{2max} = 1.10 \times t_2 = 10.57ms$

$$T_{wdmax} = t_{1min} + t_{2min} = 10.87ms + 8.65ms = 19.52ms$$

$$T_{\text{wdmin}} = t_{1\text{max}} = 13.28\text{ms}$$

$$T_{wd} = 16.42 \text{ms} \pm 3.15 \text{ms} (\pm 19.1\%)$$

Figure 4-4 on page 8 shows the typical watchdog period T<sub>WD</sub> depending on the value of the external resistor R<sub>OSC</sub>.

A reset will be active for  $V_{CC} < V_{thRESx}$ ; the level  $V_{thRESx}$  is realized with a hysteresis (HYS<sub>RESth</sub>).

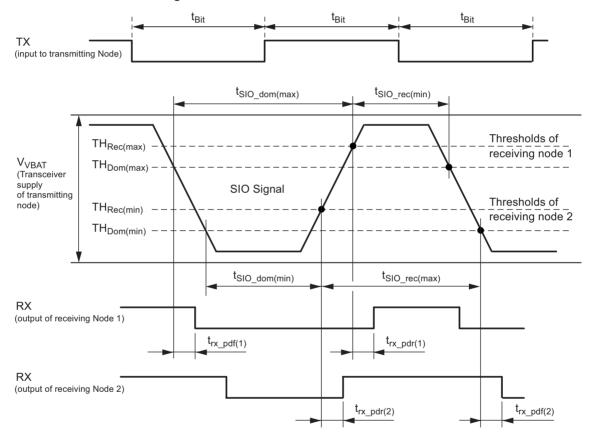

# 4.4 High Voltage Serial Interface

A bi-directional bus interface is implemented for data transfer between hostcontroller and the local microcontroller (SIO).

The transceiver consists of a low side driver (1.2V at 40mA) with slew rate control, wave shaping, current limitation, and a high-voltage comparator followed by a debouncing unit in the receiver.

#### 4.4.1 Transmit Mode

During transmission, the data at the pin TX will be transferred to the bus driver to generate a bus signal on pin SIO. The pin TX has a pull-down resistor included.

To minimize the electromagnetic emission of the bus line, the bus driver has an integrated slew rate control and wave-shaping unit. In transmit mode, transmission will be interrupted in case of overheating at the SIO driver.

#### 4.4.2 Reset Mode

In case of an active reset shown at pin /RESET the pin SIO is switched to low, independent of the temperature. The maximum current is limited to  $I_{SIO\ LIM\ RESET}$ .

Figure 4-5. Definition of Bus Timing Parameters

The recessive BUS level is generated from the integrated 30 k $\Omega$  pull-up resistor in series with an active diode. This diode prevents the reverse current of VBUS during differential voltage between VSUP and BUS ( $V_{BUS} > V_{SUP}$ ).

# 4.5 Control Inputs DIR and PWM

#### 4.5.1 Pin DIR

Logical input to control the direction of the external motor to be controlled by the IC. An internal pull-down resistor is included.

#### 4.5.2 Pin PWM

Logical input for PWM information delivered by external microcontroller. Duty cycle and frequency at this pin are passed through to the H-bridge. An internal pull-down resistor is included.

Table 4-1. Status of the IC Depending on Control Inputs and Detected Failures

|    | Control In | outs | Driver | Stage for Ext | Comments |     |                         |

|----|------------|------|--------|---------------|----------|-----|-------------------------|

| ON | DIR        | PWM  | H1     | L1            | H2       | L2  |                         |

| 0  | Х          | Х    | OFF    | OFF           | OFF      | OFF | DG1, DG2 fault or RESET |

| 1  | 0          | PWM  | ON     | OFF           | /PWM     | PWM | Motor PWM forward       |

| 1  | 1          | PWM  | /PWM   | PWM           | ON       | OFF | Motor PWM reverse       |

The internal signal ON is high when

- At least one valid WD trigger has been accepted

- No short circuit detected

- V<sub>PBAT</sub> is inside the specified range (V<sub>PBAT</sub> OV ≤ V<sub>PBAT</sub> ≤ V<sub>THOV</sub>)

- V<sub>VBAT</sub> is higher than V<sub>THUV</sub>

- The device temperature is not above shutdown threshold

In case of a short circuit, the appropriate transistor is switched off after a blanking time of  $t_{SC}$ . In order to avoid cross current through the bridge, a cross conduction timer is implemented. Its time constant is programmable by means of an RC combination.

Table 4-2. Status of the Diagnostic Outputs

|         | Device Status |         |         |      | Diag | gnostic O | utputs | Comments |                         |

|---------|---------------|---------|---------|------|------|-----------|--------|----------|-------------------------|

| PBAT_UV | SC            | VBAT_UV | PBAT_OV | CPOK | OT   | DG1       | DG2    | DG3      |                         |

| Х       | Х             | Х       | Х       | Х    | 1    | _         | _      | 1        | Overtemperature warning |

| X       | Х             | Х       | X       | 0    | X    | 0         | 1      | _        | Charge pump failure     |

| X       | Χ             | X       | 1       | Χ    | X    | 0         | 1      | _        | Overvoltage PBAT        |

| X       | Х             | 1       | X       | Х    | X    | 0         | 1      | _        | Undervoltage VBAT       |

| X       | 1             | 0       | 0       | 1    | X    | 1         | 0      | _        | Short circuit           |

| 1       | 0             | 0       | 0       | 1    | X    | 1         | 1      | _        | Undervoltage PBAT       |

Note:

X represents: don't care – no effect)

PBAT\_UV: Undervoltage PBAT pin

SC: Short circuit drain source monitoring

VBAT\_UV: Undervoltage of VBAT pin

PBAT\_OV: Overvoltage of PBAT pin

CPOK: Charge pump OK

OT: Overtemperature warning

- Status of the diagnostic outputs depends on device status

# 4.6 VG Regulator

The VG regulator is used to generate the gate voltage for the low-side driver. Its output voltage will be used as one input for the charge pump, which generates the gate voltage for the high-side driver. The purpose of the regulator is to limit the gate voltage for the external power MOS transistors to 12V. It needs a ceramic capacitor of 470nF for stability. The output voltage is reduced if the supply voltage at VBAT falls below 12V.

### 4.7 Charge Pump

The integrated charge pump is needed to supply the gates of the external power MOS transistors. It needs a shuffle capacitor of 220nF and a reservoir capacitor of 470nF. Without load, the output voltage on the reservoir capacitor is  $V_{VBAT}$  plus VG. The charge pump is clocked with a dedicated internal oscillator of 100KHz. The charge pump is designed to reach a good EMC level. The charge pump will be switched off for  $V_{VBAT} > V_{THOV}$ .

#### 4.8 Thermal Shutdown

There is a thermal shutdown block implemented. With rising junction temperature, a first warning level will be reached at 180°C. At this point the IC stays fully functional and a warning will be sent to the microcontroller. At junction temperature 200°C the drivers for H1, H2, L1, L2, SIO and the VCC regulator will be switched off and a reset occurs.

### 4.9 H-bridge Driver

The IC includes two push-pull drivers for control of two external power NMOS used as high-side drivers and two push-pull drivers for control of two external power NMOS used as low-side drivers. The drivers are able to be used with standard and logic-level power NMOS.

The drivers for the high-side control use the charge pump voltage to supply the gates with a voltage of VG above the battery voltage level. The low-side drivers are supplied by VG directly. It is possible to control the external load (motor) in the forward and reverse direction (see Table 4-1 on page 10). The duty cycle of the PMW controls the speed. A duty cycle of 100% is possible in both directions.

#### 4.9.1 Cross Conduction Time

To prevent high peak currents in the H-bridge, a non-overlapping phase for switching the external power NMOS is realized. An external RC combination defines the cross conduction time in the following way:

$t_{CC}$  ( $\mu$ s) = 0.41 × R<sub>CC</sub> ( $k\Omega$ ) × C<sub>CC</sub> (nF) (tolerance: ±5% ±0.15 $\mu$ s)

The RC combination is charged to 5V and the switching level of the internal comparator is 67% of the start level.

The resistor  $R_{CC}$  must be greater than  $5k\Omega$  and should be as close as possible to  $10k\Omega$ , the  $C_{CC}$  value has to be  $\leq 5nF$ . Use of COG capacitor material is recommended.

The time measurement is triggered by the PWM or DIR signal crossing the 50% level.

PWM or DIR

50%

t

t

t

x

20%

t<sub>HxHL</sub>

t<sub>Hxr</sub>

$t_{HxLH}$

Figure 4-6. Timing of the Drivers

The delays  $t_{HxLH}$  and  $t_{LxLH}$  include the cross conduction time  $t_{CC}$ .

#### 4.10 Short Circuit Detection

Hx

To detect a short in H-bridge circuitry, internal comparators detect the voltage difference between source and drain of the external power NMOS. If the transistors are switched ON and the source-drain voltage difference is higher than the value  $V_{SC}$  (4V with tolerances) the diagnosis pin DG1 will be set to 'H' and the drivers will be switched off. All gate driver outputs (Hx and Lx) will be set to 'L'. Releasing the gate driver outputs will set DG1 back to 'L'. With the next transition on the pin PWM, the corresponding drivers, depending on the DIR pin, will be switched on again.

80%

20%

There is a PBAT supervision block implemented to detect the possible voltage drop on PBAT during a short circuit. If the voltage at PBAT falls under  $V_{PBAT\_OK}$  the drivers will be switched off and DG1 will be set to "H". It will be cleared as soon as the PBAT undervoltage condition disappears.

The detection of drain source voltage exceedances is activated after the short circuit blanking time  $t_{SC}$ , the short circuit detection of PBAT failures operates immediately.

# 5. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Pin Description                                      | Pin Name                    | Min                                | Max                                 | Unit |

|------------------------------------------------------|-----------------------------|------------------------------------|-------------------------------------|------|

| Ground                                               | GND                         | 0                                  | 0                                   | V    |

| Power ground                                         | PGND                        | -0.3                               | +0.3                                | V    |

| Reverse protected battery voltage                    | VBAT                        |                                    | +40                                 | V    |

| Reverse current out of pin                           | VBAT                        | <b>–1</b>                          |                                     | mA   |

| Reverse protected battery voltage                    | PBAT                        |                                    | +40                                 | V    |

| Reverse current out of pin                           | PBAT                        | -20                                |                                     | mA   |

| Digital output                                       | /RESET                      | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Digital output                                       | DG1, DG2, DG3               | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| 4.9V output, external blocking capacitor             | VINT                        | -0.3                               | +5.5                                | V    |

| Cross conduction time capacitor/resistor combination | CC                          | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Digital input coming from microcontroller            | WD                          | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Watchdog timing resistor                             | RWD                         | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Digital input direction control                      | DIR                         | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Digital input PWM control + Test mode                | PWM                         | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| 5V regulator output                                  | VCC                         | -0.3                               | +5.5                                | V    |

| Digital input                                        | VMODE                       | -0.3                               | V <sub>VINT</sub> + 0.3             | V    |

| 12V output, external blocking capacitor              | VG                          |                                    | +16                                 | V    |

| Digital output                                       | RX                          | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Digital input                                        | TX                          | -0.3                               | V <sub>VCC</sub> + 0.3              | V    |

| Serial interface data pin                            | SIO                         | -27                                | V <sub>VBAT</sub> + 2               | V    |

| Source external high-side NMOS                       | S1, S2                      | (-2)                               | +30<br>+40 <sup>(3)</sup>           | V    |

| Gates external low-side NMOS                         | L1, L2                      | V <sub>PGND</sub> - 0.3            | V <sub>VG</sub> + 0.3               | V    |

| Gates of external high-side NMOS                     | H1, H2                      | V <sub>Sx</sub> - 1 <sup>(2)</sup> | V <sub>Sx</sub> + 16 <sup>(2)</sup> | V    |

| Charge pump                                          | CPLO                        |                                    | V <sub>PBAT</sub> + 0.3             | V    |

| Charge pump                                          | CPHI                        |                                    | V <sub>VRES</sub> + 0.3             | V    |

| Charge pump output                                   | VRES                        |                                    | +40 <sup>(4)</sup>                  | V    |

| Switched VBAT                                        | VBATSW                      | -0.3                               | V <sub>VBAT</sub> + 0.3             | V    |

| Power dissipation                                    | P <sub>tot</sub>            |                                    | 1.4 <sup>(1)</sup>                  | W    |

| Storage temperature                                  | $\vartheta_{STORE}$         | <b>–</b> 55                        | +150                                | °C   |

| Reverse current                                      | CPLO, CPHI, VG,<br>VRES, Sx | -2                                 |                                     | mA   |

|                                                      | Lx, Hx                      | -1                                 |                                     | mA   |

Notes:

- 1. May be additionally limited by external thermal resistance

- 2. x = 1.2

- 3. t < 0.5s

- 4. Load dump of t < 0.5s tolerated

#### **Thermal Resistance** 6.

| Parameters                                                               | Symbol            | Value | Unit |

|--------------------------------------------------------------------------|-------------------|-------|------|

| Thermal resistance junction to heat slug                                 | R <sub>thjc</sub> | < 5   | K/W  |

| Thermal resistance junction to ambient when heat slug is soldered to PCB | R <sub>thja</sub> | 25    | K/W  |

#### **Operating Range** 7.

The operating conditions define the limits for functional operation and parametric characteristics of the device. Functionality outside these limits is not implied unless otherwise stated explicitly.

| Parameters                                                                      | Symbol         | Min                 | Max                 | Unit |

|---------------------------------------------------------------------------------|----------------|---------------------|---------------------|------|

| Operating supply voltage <sup>(1)</sup>                                         | $V_{VBAT1}$    | $V_{THUV}$          | V <sub>THOV</sub>   | V    |

| Operating supply voltage <sup>(2)</sup>                                         | $V_{VBAT2}$    | 6                   | < V <sub>THUV</sub> | V    |

| Operating supply voltage <sup>(3)</sup>                                         | $V_{VBAT3}$    | 4.5                 | < 6                 | V    |

| Operating supply voltage <sup>(4)</sup>                                         | $V_{VBAT4}$    | 0                   | < 4.5               | V    |

| Operating supply voltage <sup>(5)</sup>                                         | $V_{VBAT5}$    | > V <sub>THOV</sub> | 40                  | V    |

| Junction temperature range under bias                                           | T <sub>j</sub> | -40                 | +200                | °C   |

| Normal functionality                                                            | T <sub>a</sub> | -40                 | +150                | °C   |

| Normal functionality, overtemperature warning set                               | T <sub>j</sub> | 165                 | 195                 | °C   |

| Switch-off temperatures of drivers for H1, H2, L1, L2, SIO and of VCC regulator | Т <sub>j</sub> | 185                 | 215                 | °C   |

- Notes: 1. Full functionality

- 2. H-bridge drivers are switched off (undervoltage detection)

- 3. H-bridge drivers are switched off, 5V/3.3V regulator with reduced parameters, RESET works correctly

- 4. H-bridge drivers are switched off, 5V regulator not working, RESET not correct

- 5. H-bridge drivers are switched off

#### 8. **Noise and Surge Immunity**

| Parameters                | Test Conditions | Value                  |

|---------------------------|-----------------|------------------------|

| Conducted interferences   | ISO 7637-1      | Level 4 <sup>(1)</sup> |

| Interference suppression  | IEC-CISPR25     | Level 5                |

| ESD (Human Body Model)    | ESD S 5.1       | 2kV                    |

| CDM (Charge Device Model) | ESD STM5.3.     | 500V                   |

Note:

Test pulse 5: V<sub>vbmax</sub> = 40V

# 9. Electrical Characteristics

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.   | Parameters                                          | Test Conditions                                                                     | Pin    | Symbol                    | Min        | Тур   | Max        | Unit | Type* |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------|--------|---------------------------|------------|-------|------------|------|-------|

| 1     | Power Supply and Supervis                           | sor Functions                                                                       |        |                           |            |       |            |      |       |

| 1.1   | Current consumption V <sub>VBAT</sub>               | $V_{VBAT} = 13.5V^{(1)}$                                                            | 25, 30 | I <sub>VBAT1</sub>        |            |       | 7          | mA   | Α     |

| 1.2   | Internal power supply                               |                                                                                     | 2      | V <sub>INT</sub>          | 4.8        | 4.94  | 5.1        | V    | Α     |

| 1.3   | Band gap voltage                                    |                                                                                     | 3      | $V_{BG}$                  |            | 1.235 |            | V    | Α     |

| 1.4   | Overvoltage threshold Up $V_{\text{PBAT}}$          |                                                                                     | 25     | V <sub>THOV_UP</sub>      | 21.2       |       | 22.7       | V    | Α     |

| 1.4.1 | Overvoltage threshold Down V <sub>PBAT</sub>        |                                                                                     | 25     | V <sub>THOV_DOWN</sub>    | 19.7       |       | 21.3       | V    | Α     |

| 1.5   | Overvoltage threshold hysteresis V <sub>PBAT</sub>  |                                                                                     | 25     | V <sub>TOVhys</sub>       | 1          |       | 2.4        | V    | Α     |

| 1.6   | Undervoltage threshold Up $V_{VBAT}$                |                                                                                     | 30     | V <sub>THUV_UP</sub>      | 6.8        |       | 7.4        | V    | Α     |

| 1.6.1 | Undervoltage threshold<br>Down V <sub>VBAT</sub>    |                                                                                     | 30     | V <sub>THUV_DOWN</sub>    | 6.5        |       | 7.0        | V    | Α     |

| 1.7   | Undervoltage threshold hysteresis V <sub>VBAT</sub> | Measured during qualification only                                                  | 30     | V <sub>TUVhys</sub>       | 0.2        |       | 0.6        | V    | А     |

| 1.8   | On resistance of V <sub>VBAT</sub> switch           | V <sub>VBAT</sub> = 13.5V                                                           | 31     | R <sub>ON_VBATSW</sub>    |            |       | 100        | Ω    | А     |

| 1.9   | Undervoltage threshold PBAT                         | V <sub>VBAT</sub> = 13.5V                                                           | 25     | V <sub>PBAT_OK</sub>      | 6.1        |       | 7          | V    | А     |

| 1.10  | Undervoltage threshold hysteresis PBAT              | V <sub>VBAT</sub> = 13.5V                                                           | 25     | V <sub>PBAT_OK_HYST</sub> | 0          |       | 100        | mV   | А     |

| 2     | 5V/3.3V Regulator                                   |                                                                                     |        |                           |            |       |            |      |       |

| 2.1   | Regulated output voltage                            | 9V < V <sub>VBAT</sub> < 40V,<br>I <sub>load</sub> = 0mA to 100mA                   | 29     | V <sub>CC1</sub>          | 4.85 (3.2) |       | 5.15 (3.4) | V    | А     |

| 2.2   | Regulated output voltage                            | $6V < V_{VBAT} \le 9V$<br>$I_{load} = 0mA to 100mA$                                 | 29     | V <sub>CC2</sub>          | 4.75 (3.2) |       | 5.25 (3.4) | V    | Α     |

| 2.2a  | Regulated output voltage                            | $6V < V_{VBAT} \le 9V$<br>$I_{load} = 0mA \text{ to } 80mA$<br>$T_a > 125^{\circ}C$ | 29     | V <sub>CC2</sub>          | 4.75 (3.2) |       | 5.25 (3.4) | V    | А     |

| 2.3   | Line regulation                                     | I <sub>load</sub> = 0mA to 100mA                                                    | 29     | DC line regulation        |            | <1    | 50         | mV   | А     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on  $T_{100}$ ; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.  | Parameters                                                  | Test Conditions                                    | Pin | Symbol                    | Min        | Тур        | Max          | Unit             | Type* |

|------|-------------------------------------------------------------|----------------------------------------------------|-----|---------------------------|------------|------------|--------------|------------------|-------|

| 2.4  | Load regulation                                             | I <sub>load</sub> = 0mA to 100mA                   | 29  | DC load regulation        |            | <10        | 50           | mV               | Α     |

| 2.5  | Output current limitation                                   | V <sub>VBAT</sub> > 6V                             | 29  | I <sub>OS1</sub>          | 100        |            | 350          | mA               | Α     |

| 2.6  | Serial inductance to C <sub>VCC</sub> including PCB         |                                                    | 29  | ESL                       | 1          |            | 20           | nH               | D     |

| 2.7  | Serial resistance to C <sub>VCC</sub> including PCB         |                                                    | 29  | ESR                       | 0          |            | 0.5          | Ω                | D     |

| 2.8  | Blocking cap at VCC                                         | (2), (3)                                           | 29  | C <sub>VCC</sub>          | 1.1        |            | 3.3          | μF               | D     |

| 2.9  | HIGH threshold VMODE                                        |                                                    | 1   | VMODE H                   |            |            | 4.0          | V                | Α     |

| 2.10 | LOW threshold VMODE                                         |                                                    | 1   | VMODE L                   | 0.7        |            |              | V                | Α     |

| 3    | VG Regulator                                                |                                                    |     |                           |            |            |              |                  |       |

| 3.1  | Regulated output voltage                                    | V <sub>PBAT</sub> ≥ 14V<br>I <sub>max</sub> = 20mA | 24  | $V_{VG}$                  | 11         |            | 14           | V                | Α     |

| 3.2  | Regulated output voltage                                    | V <sub>PBAT</sub> = 9V<br>I <sub>max</sub> = 20mA  | 24  | $V_{VG}$                  | 7.0        |            | 9.0          | V                | Α     |

| 4    | Reset and Watchdog                                          |                                                    |     |                           |            |            |              |                  |       |

| 4.1  | $V_{\text{CC}}$ threshold voltage level for /RESET          | VMODE = "H"<br>(VMODE = "L")                       | 29  | V <sub>tHRESH</sub>       |            | 4.8 (3.15) |              | V                | А     |

| 4.1a | Tracking of reset thres-hold with regulated output voltage  | VMODE = "H"<br>(VMODE = "L")                       | 29  | V <sub>VCC1-VtHRESH</sub> | 75<br>(50) |            |              | mV               | А     |

| 4.2  | $V_{\text{CC}}$ threshold voltage level for /RESET          | VMODE = "H"<br>(VMODE = "L")                       | 29  | V <sub>tHRESL</sub>       | 4.3 (2.86) |            |              | V                | А     |

| 4.3  | Hysteresis of /RESET level                                  | VMODE = "H"<br>(VMODE = "L")(4)                    | 29  | HYS <sub>RESth</sub>      | 70         | 200        | 350<br>(240) | mV               | Α     |

| 4.4  | Length of pulse at /RESET pin                               | (5)                                                | 5   | t <sub>res</sub>          |            | 7000       |              | T <sub>100</sub> | А     |

| 4.5  | Length of short pulse at /RESET pin                         | (5)                                                | 5   | t <sub>resshort</sub>     |            | 200        |              | T <sub>100</sub> | А     |

| 4.6  | Wait for the first WD trigger                               | (5)                                                | 5   | t <sub>d</sub>            |            | 7000       |              | T <sub>100</sub> | Α     |

| 4.7  | Time for VCC < V <sub>tHRESL</sub> before activating /RESET | (4)                                                | 29  | t <sub>delayRESL</sub>    | 0.5        |            | 2            | μs               | С     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on T<sub>100</sub>; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.  | Parameters                                                       | Test Conditions                                               | Pin | Symbol              | Min                  | Тур                  | Max                                                  | Unit | Type* |

|------|------------------------------------------------------------------|---------------------------------------------------------------|-----|---------------------|----------------------|----------------------|------------------------------------------------------|------|-------|

| 4.8  | Resistor defining internal bias currents for watchdog oscillator |                                                               | 3   | R <sub>RWD</sub>    | 10                   |                      | 91                                                   | kΩ   | D     |

| 4.9  | Watchdog oscillator period                                       | $R_{RWD} = 33k\Omega$                                         | 3   | T <sub>OSC</sub>    | 11.09                |                      | 13.55                                                | μs   | Α     |

| 4.11 | Watchdog input low-voltage threshold                             |                                                               | 6   | V <sub>ILWD</sub>   |                      |                      | $\begin{array}{c} 0.3 \times \\ V_{VCC} \end{array}$ | V    | Α     |

| 4.12 | Watchdog input high-voltage threshold                            |                                                               | 6   | $V_{IHWD}$          | $0.7 \times V_{VCC}$ |                      |                                                      | V    | Α     |

| 4.13 | Hysteresis of watchdog input voltage threshold                   |                                                               | 6   | V <sub>hysWD</sub>  | 0.3                  |                      | 0.8                                                  | V    | Α     |

| 4.14 | Close window                                                     | (5)                                                           | 6   | t1                  |                      | $980 \times T_{OSC}$ |                                                      |      | Α     |

| 4.15 | Open window                                                      | (5)                                                           | 6   | t2                  |                      | $780 \times T_{OSC}$ |                                                      |      | Α     |

| 4.16 | Output low-voltage of /RESET                                     | At I <sub>OLRES</sub> = 1mA                                   | 5   | V <sub>OLRES</sub>  |                      |                      | 0.4                                                  | V    | А     |

| 4.17 | Internal pull-up resistor at pin /RESET                          |                                                               | 5   | R <sub>PURES</sub>  | 5                    | 10                   | 15                                                   | kΩ   | А     |

| 5    | High Voltage Serial Interfac                                     | e                                                             |     |                     |                      |                      |                                                      |      |       |

| 5.1  | Low-level output current                                         | Normal mode;<br>$V_{SIO} = 0V$ , $V_{RX} = 0.4V$              | 13  | IL <sub>RX</sub>    | 2                    |                      |                                                      | mA   | А     |

| 5.2  | High-level output current                                        | Normal mode; $V_{SIO} = V_{VBAT}$<br>$V_{RX} = V_{CC} - 0.4V$ | 13  | IH <sub>RX</sub>    | 0.8                  |                      |                                                      | mA   | А     |

| 5.4  | Driver dominant voltage V <sub>BUSdom_DRV_LoSUP</sub>            | $V_{VBAT} = 7.3V$<br>$R_{load} = 500\Omega$                   | 8   | V_LoSUP             |                      |                      | 1.2                                                  | V    | Α     |

| 5.5  | Driver dominant voltage V <sub>BUSdom_DRV_HiSUP</sub>            | $V_{VBAT} = 18V$<br>$R_{load} = 500\Omega$                    | 8   | V_ <sub>HiSUP</sub> |                      |                      | 2                                                    | V    | Α     |

| 5.6  | Driver dominant voltage V <sub>BUSdom_DRV_Losup</sub>            | $V_{VBAT} = 7.3V$<br>$R_{load} = 1000\Omega$                  | 8   | V_LoSUP_1k          | 0.6                  |                      |                                                      | V    | А     |

| 5.7  | Driver dominant voltage V <sub>BUSdom_DRV_HiSUP</sub>            | $V_{VBAT} = 18V$<br>$R_{load} = 1000\Omega$                   | 8   | V_HiSUP_1k_         | 0.8                  |                      |                                                      | V    | Α     |

| 5.8  | Pull up resistor to VBAT                                         | The serial diode is mandatory                                 | 8   | R <sub>SIO</sub>    | 20                   | 30                   | 60                                                   | kΩ   | А     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on T<sub>100</sub>; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}\text{C} \le 9$  ambient  $\le 150^{\circ}\text{C}$  unless stated otherwise.

| No.  | Parameters                                                                                                                                      | Test Conditions                                                                                                                                                                                                            | Pin | Symbol                     | Min                       | Тур                   | Max                     | Unit | Type* |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|---------------------------|-----------------------|-------------------------|------|-------|

| 5.9  | Current limitation                                                                                                                              | $V_{SIO} = V_{BAT_{max}}$                                                                                                                                                                                                  | 8   | I <sub>SIO_LIM</sub>       | 40                        |                       | 250                     | mA   | Α     |

| 5.9a | Current limitation in case of RESET and SIO overheat                                                                                            | V <sub>SIO</sub> = V <sub>BAT_max</sub><br>RESET = high                                                                                                                                                                    | 8   | I <sub>SIO_LIM_RESET</sub> | 30                        |                       | 100                     | mA   | Α     |

| 5.10 | Input leakage current at the receiver including pull-up resistor as specified                                                                   | Input leakage current<br>driver off<br>V <sub>SIO</sub> = 0V<br>V <sub>VBAT</sub> = 12V                                                                                                                                    | 8   | I <sub>SIO_PAS_dom</sub>   | -1                        |                       |                         | mA   | Α     |

| 5.11 | Leakage current SIO recessive                                                                                                                   | Driver off<br>$8V < V_{VBAT} < 18V$<br>$8V < V_{SIO} < 18V$<br>$V_{SIO} \ge V_{VBAT}$                                                                                                                                      | 8   | I <sub>SIO_PAS_rec</sub>   |                           |                       | 30                      | μA   | А     |

| 5.12 | Leakage current at ground loss Control unit disconnected from ground Loss of local ground must not affect communication in the residual network | $GND_{Device} = V_{VBAT}$ $V_{VBAT} = 12V$ $0V < V_{SIO} < 18V$                                                                                                                                                            | 8   | I <sub>SIO_NO_gnd</sub>    | -1                        |                       | 1                       | mA   | А     |

| 5.13 | Node has to sustain the current that can flow under this condition. Bus must remain operational under this condition                            | $V_{VBAT}$ disconnected $V_{SUP\_Device} = GND$ $0V < V_{SIO} < 18V$                                                                                                                                                       | 8   | I <sub>SIO</sub>           |                           |                       | 100                     | μА   | Α     |

| 5.14 | Center of receiver threshold                                                                                                                    | $V_{SIO\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$                                                                                                                                                                             | 8   | V <sub>SIO_CNT</sub>       | 0.475 × V <sub>VBAT</sub> | $0.5 \times V_{VBAT}$ | $0.525 \times V_{VBAT}$ | V    | Α     |

| 5.15 | Receiver dominant state                                                                                                                         | V <sub>EN</sub> = 5V                                                                                                                                                                                                       | 8   | V <sub>SIOdom</sub>        |                           |                       | $0.4 \times V_{VBAT}$   | V    | Α     |

| 5.16 | Receiver recessive state                                                                                                                        | V <sub>EN</sub> = 5V                                                                                                                                                                                                       | 8   | V <sub>SIOrec</sub>        | $0.6 \times V_{VBAT}$     |                       |                         | V    | Α     |

| 5.17 | Receiver input hysteresis                                                                                                                       | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$                                                                                                                                                                                      | 8   | V <sub>SIOhys</sub>        |                           | $0.1 \times V_{VBAT}$ | $0.175 \times V_{VBAT}$ | V    | А     |

| 5.18 | Duty cycle 1                                                                                                                                    | $\begin{split} TH_{Rec(max)} &= 0.744 \times V_{VBAT} \\ TH_{Dom(max)} &= 0.581 \times V_{VBAT} \\ V_{VBAT} &= 7V \text{ to } 18V \\ t_{Bit} &= 50 \mu s \\ D1 &= t_{sio\_rec(min)} / 2 \times t_{Bit}^{(11)} \end{split}$ | 8   | D1                         | 0.380                     |                       |                         |      | А     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on T<sub>100</sub>; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.  | Parameters                             | Test Conditions                                                                                                                                                                                                                | Pin             | Symbol               | Min                                     | Тур | Max                                    | Unit | Type* |

|------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|-----------------------------------------|-----|----------------------------------------|------|-------|

| 5.19 | Duty cycle 2                           | $\begin{aligned} &TH_{Rec(min)} = 0.422 \times V_{VBAT} \\ &TH_{Dom(min)} = 0.284 \times V_{VBAT} \\ &V_{VBAT} = 7V \text{ to } 18V \\ &t_{Bit} = 50 \mu s \\ &D2 = t_{sio\_rec(max)} / 2 \times t_{Bit}^{(11)} \end{aligned}$ | 8               | D2                   |                                         |     | 0.600                                  |      | Α     |

| 5.20 | Propagation delay of receiver          | $\begin{aligned} t_{\text{rec\_pd}} &= \text{max}(t_{\text{rx\_pdr}}, \ t_{\text{rx\_pdf}})^{(11)} \\ 7\text{V} &< \text{V}_{\text{VBAT}} < 18\text{V} \end{aligned}$                                                          | 8               | t <sub>rx_pd</sub>   |                                         |     | 6                                      | μs   | Α     |

| 5.21 | Symmetry of receiver propagation delay | $t_{rx\_sym} = t_{rx\_pdr} - t_{rx\_pdf}^{(11)}$<br>7V < V <sub>VBAT</sub> < 18V                                                                                                                                               | 8               | t <sub>rx_sym</sub>  | -2                                      |     | +2                                     | μs   | Α     |

| 6    | Control Inputs DIR, PWM, V             | VD, TX                                                                                                                                                                                                                         |                 |                      |                                         |     |                                        |      |       |

| 6.1  | Input low-voltage threshold            |                                                                                                                                                                                                                                | 10, 11,<br>6, 9 | V <sub>IL</sub>      |                                         |     | 0.3 ×<br>V <sub>VCC</sub>              | V    | Α     |

| 6.2  | Input high-voltage threshold           |                                                                                                                                                                                                                                | 10, 11,<br>6, 9 | V <sub>IH</sub>      | 0.7 ×<br>V <sub>VCC</sub>               |     |                                        | V    | Α     |

| 6.3  | Hysteresis                             |                                                                                                                                                                                                                                | 10, 11,<br>6, 9 | HYS                  | 0.3                                     | 0.5 | 0.8                                    | V    | Α     |

| 6.4  | Pull-down resistor                     | DIR, PWM, WD, TX                                                                                                                                                                                                               | 10, 11,<br>6, 9 | $R_{PD}$             | 25                                      | 50  | 140                                    | kΩ   | Α     |

| 6.5  | Rise/fall time                         |                                                                                                                                                                                                                                | 10, 11,<br>6, 9 | t <sub>rf</sub>      |                                         |     | 100                                    | ns   | Α     |

| 7    | Charge Pump                            |                                                                                                                                                                                                                                |                 |                      |                                         |     |                                        |      |       |

| 7.1  | Charge pump voltage                    | Load = 0A                                                                                                                                                                                                                      | 21              | VCP                  |                                         |     | V <sub>VBAT</sub><br>+ V <sub>VG</sub> | V    | Α     |

| 7.2  | Charge pump voltage                    | Load = 3mA,<br>C <sub>CP</sub> = 100nF                                                                                                                                                                                         | 21              | VCP                  | V <sub>VBAT</sub> + V <sub>VG</sub> – 1 |     |                                        | V    | Α     |

| 7.3  | Period charge pump oscillator          |                                                                                                                                                                                                                                | 21              | T <sub>100</sub>     | 9                                       |     | 11                                     | μs   | Α     |

| 7.4  | CP load current in VG without CP load  | Load = 0A                                                                                                                                                                                                                      | 21              | I <sub>VGCPz</sub>   |                                         |     | 600                                    | μA   | Α     |

| 7.5  | CP load current in VG with CP load     | C <sub>CP</sub> = 100nF                                                                                                                                                                                                        | 21              | I <sub>VGCP</sub>    |                                         |     | 4                                      | mA   | Α     |

| 7.6  | Charge pump OK threshold UP            | Reference: PBAT                                                                                                                                                                                                                | 21              | V <sub>CPOK_UP</sub> | 5.3                                     |     | 6.3                                    | V    | Α     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on T<sub>100</sub>; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.  | Parameters                                                    | Test Conditions                                                           | Pin               | Symbol                               | Min                                     | Тур | Max                                 | Unit | Type* |

|------|---------------------------------------------------------------|---------------------------------------------------------------------------|-------------------|--------------------------------------|-----------------------------------------|-----|-------------------------------------|------|-------|

| 7.7  | Charge pump OK threshold DOWN                                 | Reference: PBAT                                                           | 21                | V <sub>CPOK_DOWN</sub>               | 4.5                                     |     | 5.5                                 | V    | А     |

| 7.8  | Charge pump OK hysteresis                                     |                                                                           | 21                | V <sub>CPOK_HYS</sub>                | 0.3                                     |     | 1.3                                 | V    | Α     |

| 8    | H-bridge Driver                                               |                                                                           |                   |                                      |                                         |     |                                     |      |       |

| 8.1  | Low-side driver HIGH output voltage                           |                                                                           | 26, 27            | $V_{LxH}$                            | V <sub>VG</sub><br>- 0.5V               |     | $V_{VG}$                            | V    | Α     |

| 8.2  | ON-resistance of sink stage of pins L1, L2                    |                                                                           | 26, 27            | $R_{DSON\_LxL,}$ $x = 1, 2$          |                                         |     | 25                                  | Ω    | Α     |

| 8.3  | ON-resistance of source stage of pins L1, L2                  |                                                                           | 26, 27            | $R_{DSON\_LxH,}$ $x = 1, 2$          |                                         |     | 25                                  | Ω    | Α     |

| 8.4  | Output peak current at pins L1, L2, switched to LOW           | V <sub>Lx</sub> = 3V                                                      | 26, 27            | I <sub>LxL,</sub><br>x = 1, 2        | 100                                     |     |                                     | mA   | А     |

| 8.5  | Output peak current at pins L1, L2, switched to HIGH          | V <sub>Lx</sub> = 3V                                                      | 26, 27            | I <sub>LxH,</sub><br>x = 1, 2        |                                         |     | -100                                | mA   | Α     |

| 8.6  | Ohmic pull-down resistance at pins L1, L2                     | Designed for<br>0V < V <sub>VBAT</sub> < 40V                              | 26, 27            | $R_{PDLx}$ $x = 1, 2$                | 25                                      |     | 140                                 | kΩ   | Α     |

| 8.7  | ON-resistance of sink stage of pins H1, H2                    | V <sub>Sx</sub> = 0                                                       | 18, 20            | $R_{DSON\_HxL}$ , $x = 1, 2$         |                                         |     | 25                                  | Ω    | Α     |

| 8.8  | ON-resistance of source stage of pins H1, H2                  | $V_{Sx} = V_{VBAT}$                                                       | 18, 20            | $R_{DSON\_HxH,}$ $x = 1, 2$          |                                         |     | 25                                  | Ω    | Α     |

| 8.9  | Output peak current at pins Hx, switched to LOW               | $V_{VBAT}$ = 13.5V<br>$V_{Sx}$ = $V_{VBAT}$<br>$V_{Hx}$ = $V_{VBAT}$ + 3V | 18, 20            | I <sub>HxL,</sub><br>x = 1, 2        | 100                                     |     |                                     | mA   | А     |

| 8.10 | Output peak current at pins Hx, switched to HIGH              | $V_{VBAT} = 13.5V$<br>$V_{Sx} = V_{VBAT}$<br>$V_{Hx} = V_{VBAT} + 3V$     | 18, 20            | I <sub>HxH</sub> ,<br>x = 1, 2       |                                         |     | -100                                | mA   | А     |

| 8.11 | Static switch output low voltage at pins Hx and Lx            | $V_{Sx} = 0V$<br>$I_{Hx} = 1mA$ , $I_{Lx} = 1mA$                          | 18, 20,<br>26, 27 | $V_{HxL}, V_{LxL}$<br>x = 1, 2       |                                         |     | 0.3                                 | V    | Α     |

| 8.12 | Static high-side switch<br>output high-voltage pins<br>H1, H2 | I <sub>Lx</sub> = -10μA<br>(PWM = static)                                 | 18, 20            | V <sub>HxHstat1</sub> <sup>(7)</sup> | V <sub>VBAT</sub> + V <sub>VG</sub> - 1 |     | V <sub>VBAT</sub> + V <sub>VG</sub> | V    | А     |

| 8.13 | Ohmic sink resistance between pins Hx and Sx                  | Designed for<br>0V < V <sub>VBAT</sub> < 40V                              | 17, 18,<br>19, 20 | R <sub>PDHx</sub>                    | 25                                      |     | 140                                 | kΩ   | Α     |

<sup>\*</sup> Type: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

- 2. The use of X7R material is recommended

- 3. For higher values, stability at zero load is not guaranteed

- 4. Tested during qualification only

- 5. Value depends on  $T_{100}$ ; function tested with digital test pattern

- 6. Tested during characterization only

- 7. Supplied by charge pump

- 8. See Section 4.9.1 "Cross Conduction Time" on page 11

- 9. Voltage between source-drain of external switching transistors in active case

- 10. The short-circuit message will never be generated for switch-on time <  $t_{\rm sc}$

- 11. See Figure 4-5 on page 9 "Definition of Bus Timing Parameters"

All parameters given are valid for  $V_{THUV} \le V_{VBAT} \le V_{THOV}$  and for  $-40^{\circ}C \le 9$  ambient  $\le 150^{\circ}C$  unless stated otherwise.

| No.  | Parameters                                                      | Test Conditions                                    | Pin           | Symbol            | Min  | Тур | Max                   | Unit | Type* |

|------|-----------------------------------------------------------------|----------------------------------------------------|---------------|-------------------|------|-----|-----------------------|------|-------|

|      | Dynamic Parameters                                              | '                                                  |               |                   |      |     |                       |      |       |

| 8.15 | Propagation delay time,<br>low-side driver from high to<br>low  | Figure 4-6 on page 12<br>V <sub>VBAT</sub> = 13.5V | 26, 27        | t <sub>LxHL</sub> |      |     | 0.5                   | μs   | A     |

| 8.16 | Propagation delay time,<br>low-side driver from low to<br>high  | V <sub>VBAT</sub> = 13.5V                          | 26, 27        | t <sub>LxLH</sub> |      |     | 0.5 + t <sub>CC</sub> | μs   | А     |

| 8.17 | Fall time low-side driver                                       | $V_{VBAT}$ = 13.5V<br>$C_{Gx}$ = 5nF               | 26, 27        | $t_Lxf$           |      |     | 0.5                   | μs   | Α     |

| 8.18 | Rise time low-side driver                                       | V <sub>VBAT</sub> = 13.5V                          | 26, 27        | t <sub>Lxr</sub>  |      |     | 0.5                   | μs   | Α     |

| 8.19 | Propagation delay time,<br>high-side driver from high<br>to low | Figure 4-6 on page 12<br>V <sub>VBAT</sub> = 13.5V | 18, 20        | t <sub>HxHL</sub> |      |     | 0.5                   | μs   | А     |

| 8.20 | Propagation delay time,<br>high-side driver from low to<br>high | V <sub>VBAT</sub> = 13.5V                          | 18, 20        | t <sub>HxLH</sub> |      |     | 0.5 + t <sub>CC</sub> | μs   | А     |

| 8.21 | Fall time high-side driver                                      | $V_{VBAT} = 13.5V$ ,<br>$C_{Gx} = 5nF$             | 18, 20        | t <sub>Hxf</sub>  |      |     | 0.5                   | μs   | Α     |

| 8.22 | Rise time high-side driver                                      | V <sub>VBAT</sub> = 13.5V                          | 18, 20        | t <sub>Hxr</sub>  |      |     | 0.5                   | μs   | Α     |

| 8.24 | External resistor                                               |                                                    | 4             | R <sub>CC</sub>   | 5    |     |                       | kΩ   | D     |

| 8.25 | External capacitor                                              |                                                    | 4             | C <sub>CC</sub>   |      |     | 5                     | nF   | D     |

| 8.26 | R <sub>ON</sub> of t <sub>CC</sub> switching transistor         |                                                    | 4             | R <sub>ONCC</sub> |      |     | 200                   | Ω    | А     |

| 8.27 | Cross conduction time <sup>(8)</sup>                            | $R_{CC} = 10k\Omega$<br>$C_{CC} = 1nF$             | 4             | t <sub>CC</sub>   | 3.75 |     | 4.45                  | μs   | А     |

| 8.28 | Short circuit detection voltage                                 | (9)                                                | 17, 19        | $V_{SC}$          | 3.5  | 4   | 4.7                   | V    | Α     |

| 8.29 | Short circuit blanking time                                     | (10)                                               | 17, 19        | t <sub>SC</sub>   | 5    | 10  | 15                    | μs   | Α     |

| 9    | Diagnostic Outputs DG1, D                                       | G2, DG3                                            |               |                   |      |     |                       |      |       |

| 9.1  | Low level output current                                        | $V_{DG} = 0.4V^{(6)}$                              | 14, 15,<br>16 | IL                | 2    |     |                       | mA   | А     |