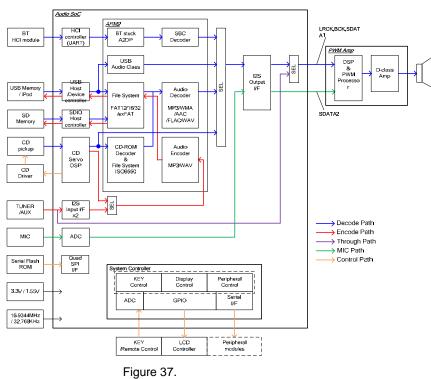

# Audio 1-Chip SOC

# BM94801KUT

#### **General Description**

The BM94801KUT is a 1-Chip SOC for multimedia audio systems, which supports the Bluetooth A2DP, USB memory, SD memory card, and CD.

This IC has a built-in ARM946ES processor, SDRAM, and various peripherals. It is designed to download programs from external Serial Flash ROM and execute system control, file system management, Audio CODEC, and a wide range of media control.

#### Features

This IC includes the following blocks: Processor

ARM946ES Microprocessor Core

Memory

- SDRAM

- Initial Program ROM

- Program SRAM

- Data SRAM

- SDRAM Controller

System

- Multilayer AHB

- DMA BUS

- Interrupt Controller

- DMA Controller

Serial, Media I/F

- GPIO

- Pin Controller

- USB2.0 Dual Role (Host/Device) Controller

- SD I/F

- Quad SPI I/F

- SPI I/F (Master/Slave)

- I2C I/F (Master/Slave)

- UART I/F

- I2S Input I/F

- I2S Output I/F

- CD Servo Controllers

- CD-ROM Decoder

- General Purpose A/D Converter

Timer

- Timer

- Watchdog Timer

- Real Time Clock

Other

- Clock Generator

- Reset Generator

- PLL

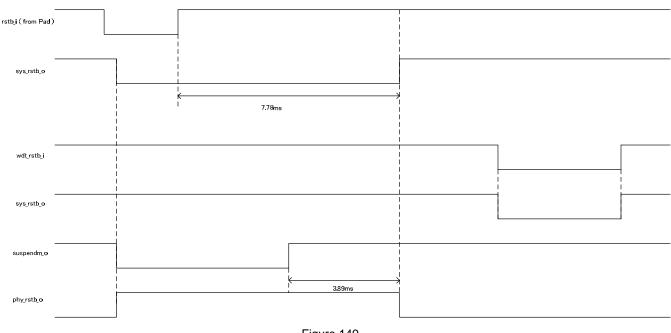

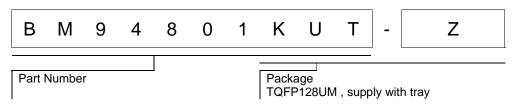

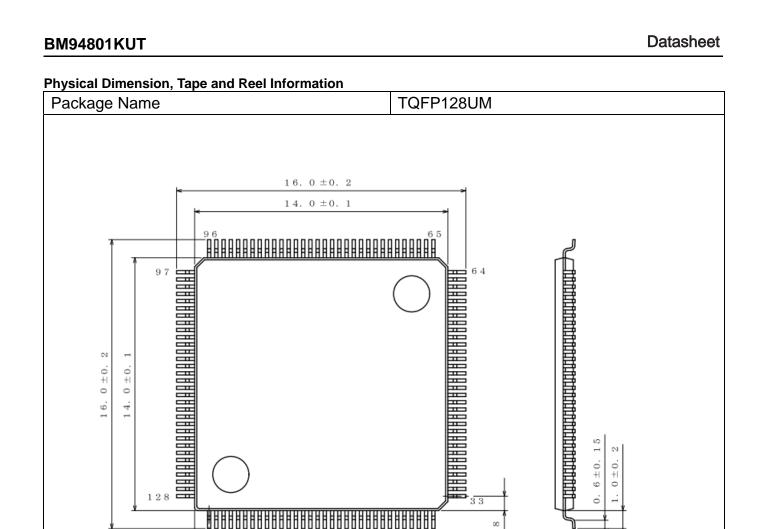

#### Package

#### Application

Component Stereo

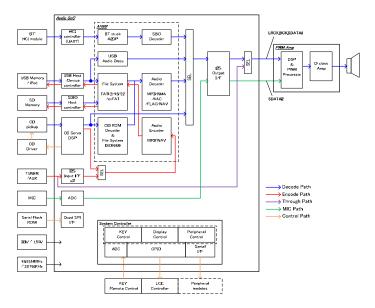

#### **Application Block**

Figure 1.

OProduct structure : Silicon monolithic integrated circuit O This product has no designed protection against radioactive rays

ARM946ES Microprocessor Core

- ♦ 32 Bit RISC Processor

- ♦ Operating Frequency: 96 MHz (118 DMIPS)

- ♦ 8 kByte Cache

- 4 kByte Data Cache

- 4 kByte Instruction Cache

# SDRAM

- 16 MBits

- SDRAM with built-in MSM56V16160K from LAPIS Semiconductor

- ♦ 2 Bank x 524,288 Word x 16 Bit

#### Initial Program ROM

- ♦ ITCM ROM Size: 2 kByte (512 Word x 32 Bit)

- Boot Program

- ♦ No Wait Access

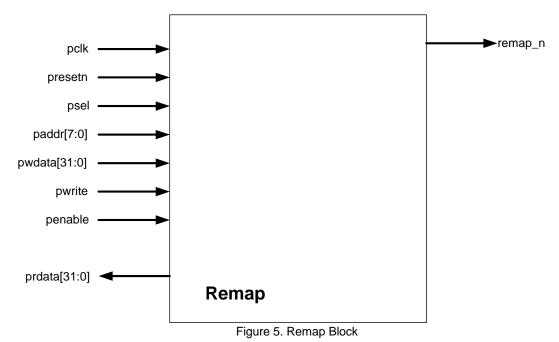

#### REMAP

$\diamondsuit$  Remapping can be implemented by writing to internal registers.

#### SHADOW SRAM

- RAM Size: 512 Byte (128 Word x 32 Bit)

- ♦ No Wait Access

#### Program SRAM

- ♦ ITCM RAM Size: 64 kByte (16,384 Word x 32 Bit)

- No Wait Access

### Data SRAM

- DTCM RAM Size: 64 kByte (16,384 Word x 32 Bit)

- No Wait Access

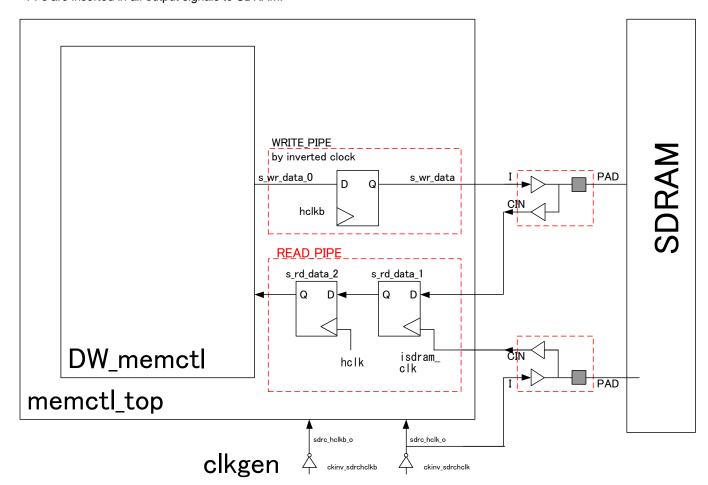

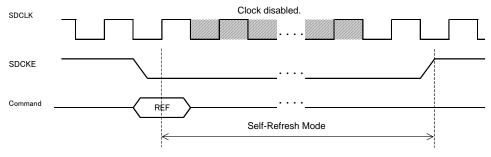

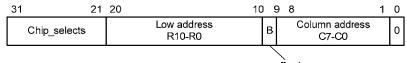

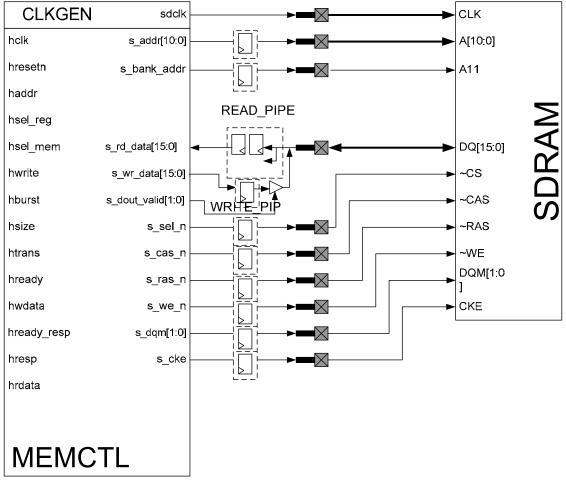

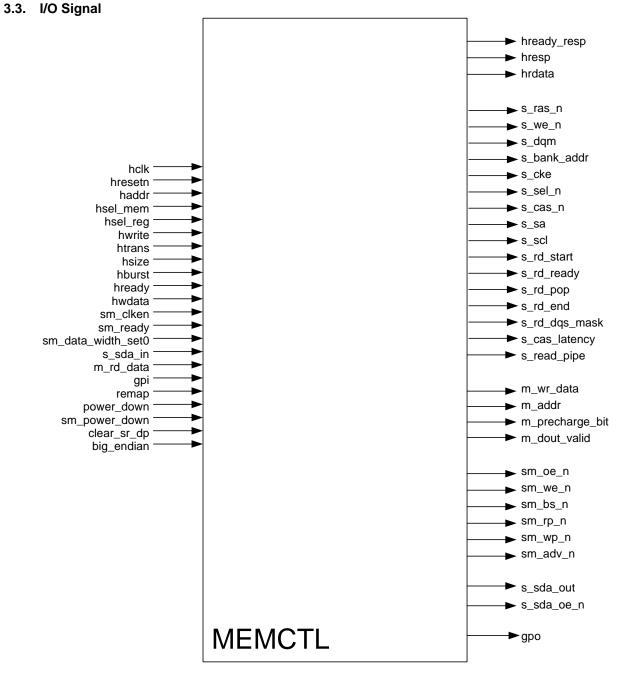

# SDRAM Controller

- Supports SDRAM

- Supports 11 Bit row address, 8-bit column address, and 1-bit bank address to SDRAM

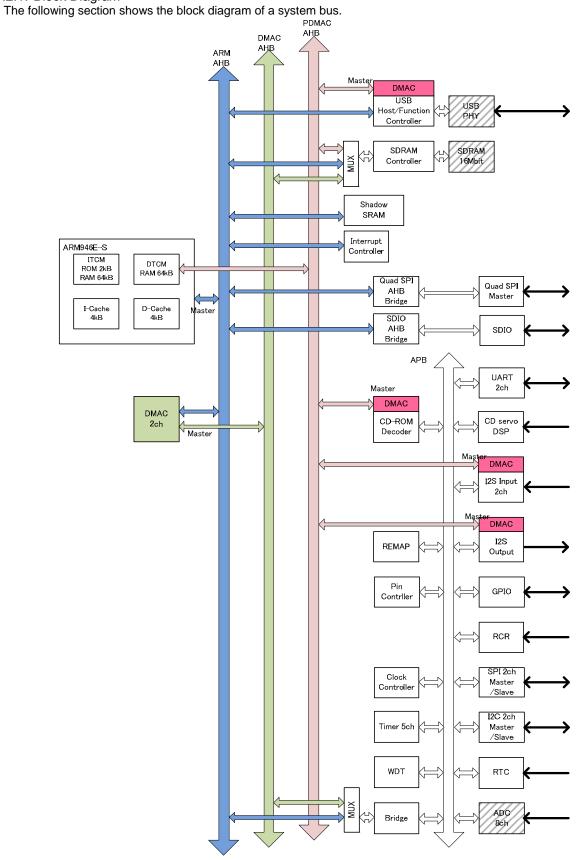

#### AMBA

- Multilayer AHB

- 32 Bit Data Bus

- Arbitrates ARM and DMA access with an arbiter

- Allows parallel access according to different master/slave combinations

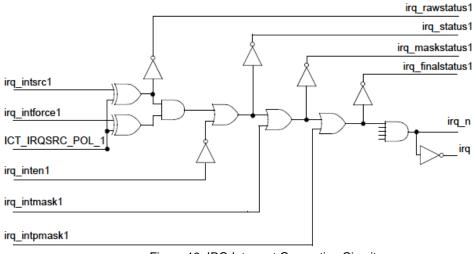

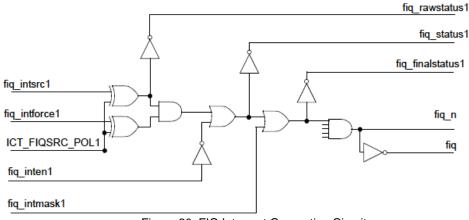

#### Interrupt Controller

- 32 IRQ Interrupt Lines

- ♦ 1 FIQ Interrupt Line

- Allows programmable setting of interrupt priority levels

- Allows setting of 16 vector addresses

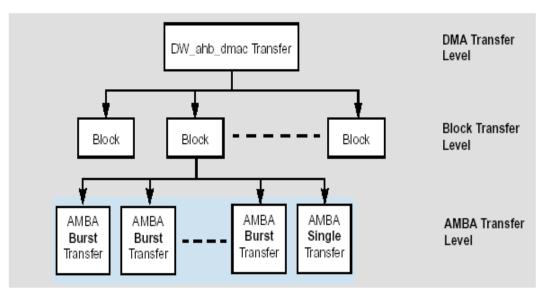

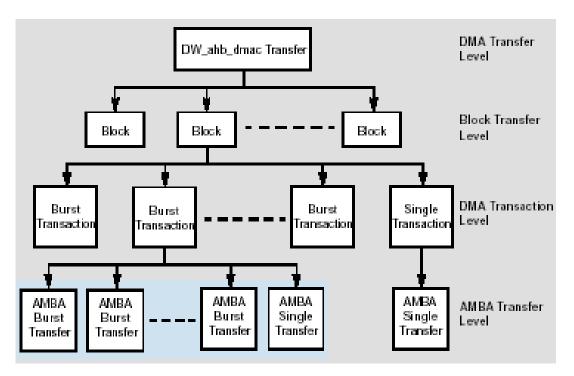

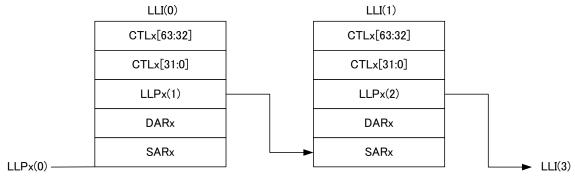

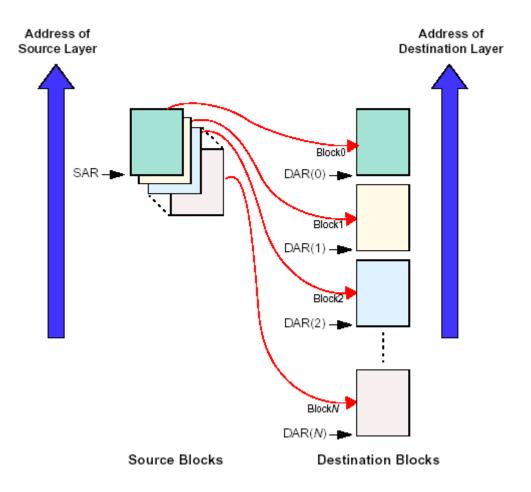

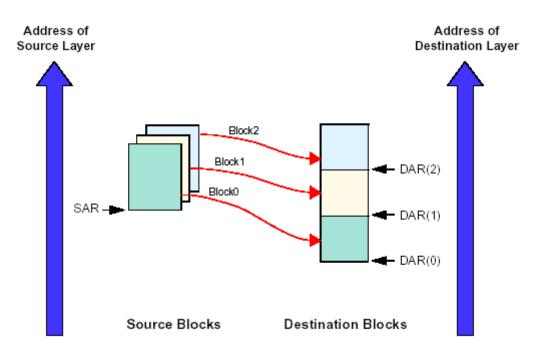

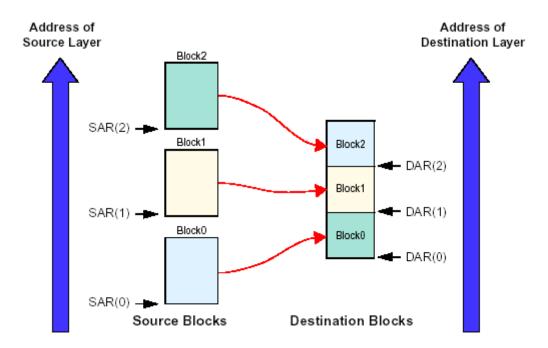

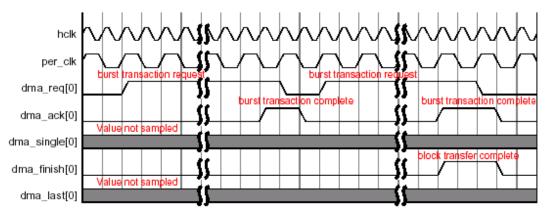

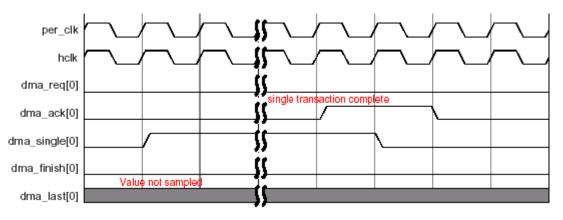

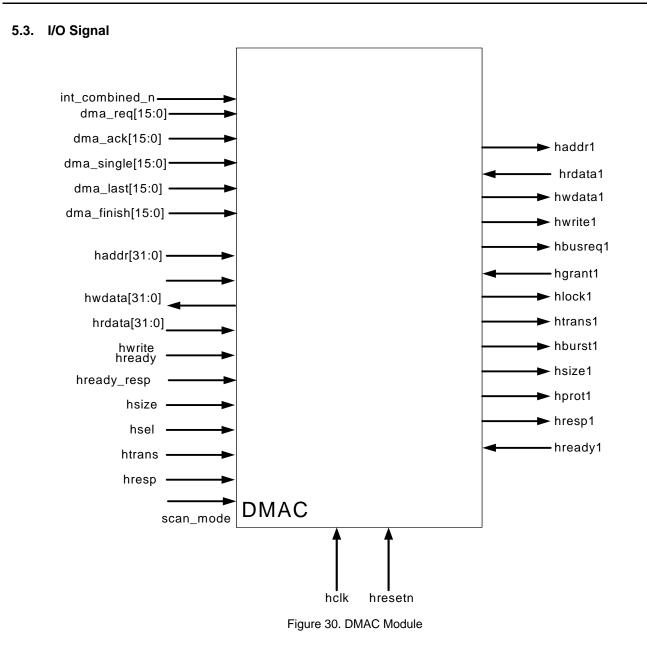

## DMA Controller

- Up to 2 DMA Channels

- Channel FIFO Depth Up to 16 Bytes

- Allows programmable setting of transfer data width in the range of 1 byte to 4 bytes

- ♦ Allows programmable setting of channel priority levels

- Maximum Block Length Up to 4,095 Words

- ♦ Includes 12 handshake interfaces available for assignment to channels with software

- ♦ Supports multiblock transfers

- Connects the master board to system bus

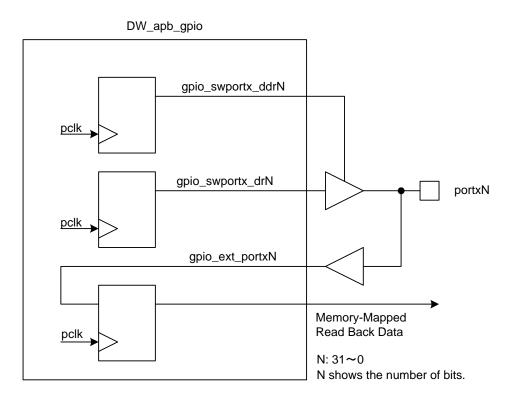

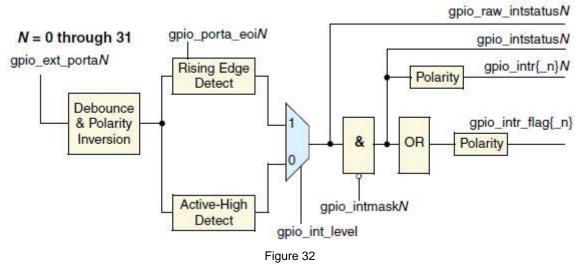

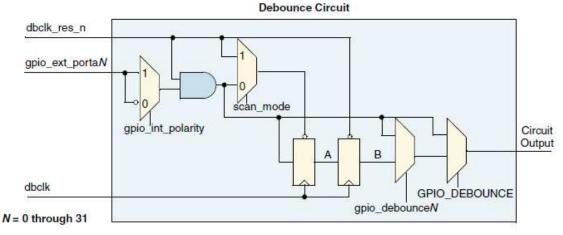

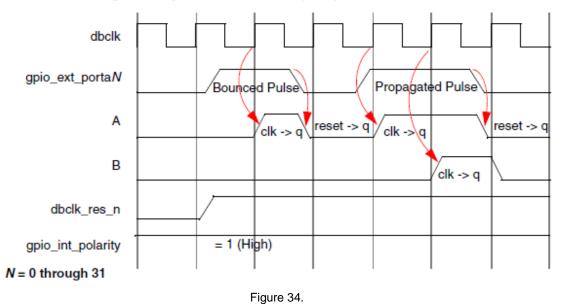

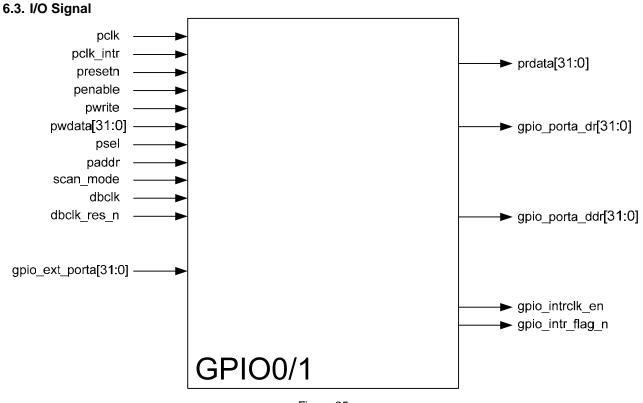

### GPIO

- ♦ GPIO0 (32 pins), GPIO1 (32 pins)

- $\diamond$  Supports a maximum of 64 I/O pins

- ♦ Supports the interrupt function

- Supports external level-sensitive interrupt

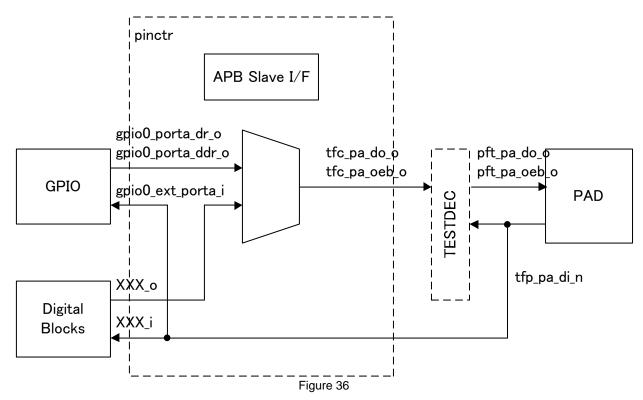

#### Pin Controller

Controls connection settings between pins and blocks

| Block                           | Number of GPIO Pins |  |  |

|---------------------------------|---------------------|--|--|

| Dedicated GPIO Pins             | 20                  |  |  |

| Combined GPIO Pins              | 44                  |  |  |

| <br>One Line of 2-Ch I2S Output | 5                   |  |  |

| Two Lines of 2-Ch I2S Input     | 6                   |  |  |

| SDIO I/F                        | 8                   |  |  |

| SPI Master                      | 4                   |  |  |

| SPI Slave                       | 4                   |  |  |

| Quad SPI I/F                    | 6                   |  |  |

| 2-Ch UART                       | 6                   |  |  |

| 2-Ch I2C Master/Slave           | 4                   |  |  |

| RCR                             | 1                   |  |  |

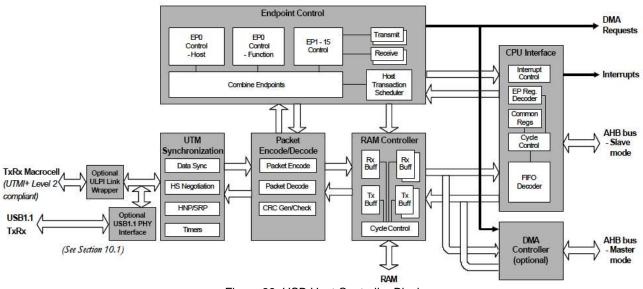

#### USB 2.0 Dual Role (Host/Device) Controller

- ♦ USB 2.0 Compatible

- Sit Rate: High Speed (480 Mbps) / Full Speed (12 Mbps)

- Configurable for up to five transmit endpoint FIFOs and four receive endpoint FIFOs (including endpoint 0)

- Each endpoint FIFO supports bulk transfer, interrupt transfer, and isochronous transfer.

- ♦ 2048-Byte RAM for Endpoint FIFO

SD I/F

- Supports SDXC, SDHC, and SD cards

- Provide access to SD card in SD Bus mode

- Allows control from the AMBA-AHB bus

- ♦ Includes 512 byte data transmit/receive FIFOs

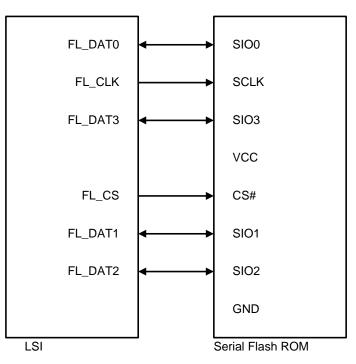

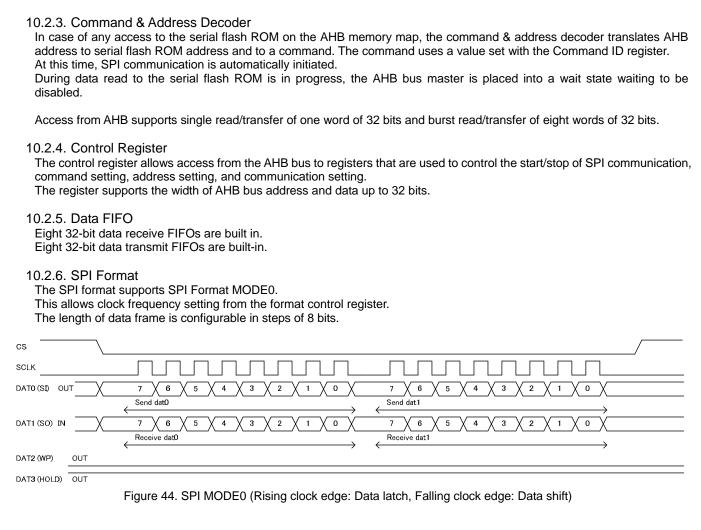

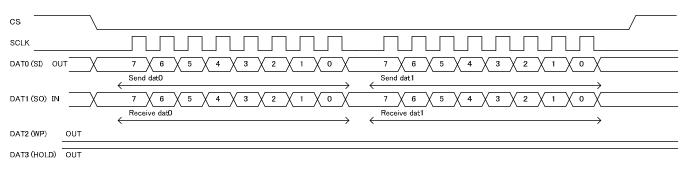

Quad SPI I/F

- ♦ Supports quad serial flash ROM

- Supports serial flash ROM address up to 24 bits

- ♦ Allows the setting of control registers from the AMBA-AHB bus

- Allows direct access from the memory map of the AMBA-AHB bus to serial flash ROM

- Includes 32 byte data transmit/receive FIFOs

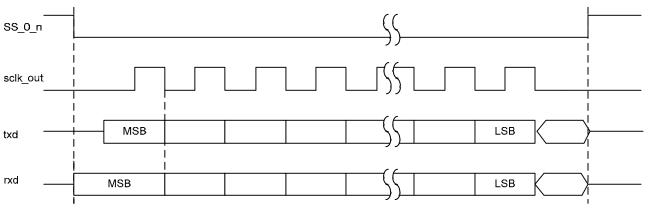

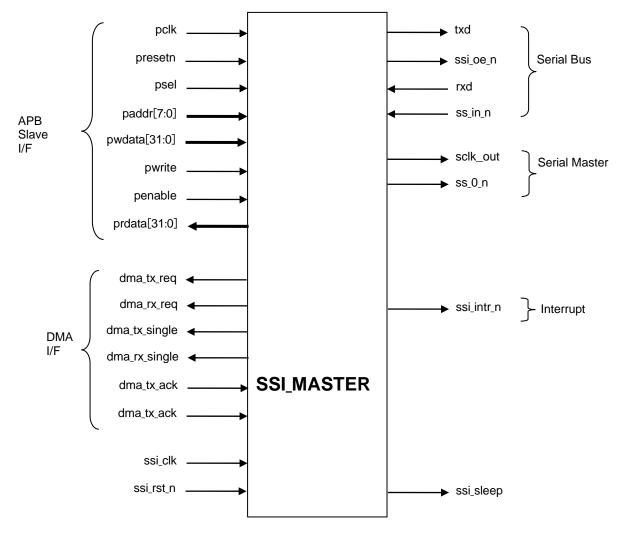

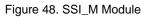

#### SSI Master

- FIFO Depth Up to 16 Words and FIFO Data Width Up to 16 Bits

- Selectable Data Size from 4 Bits to 16 Bits

- Serial protocol supports SPI from Motorola

- ♦ Includes DMA handshake interface

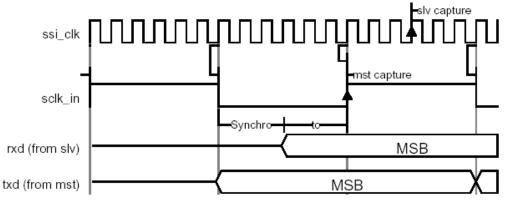

#### SSI Slave

- FIFO Depth Up to 16 Words and FIFO Data Width Up to 16 Bits

- Selectable Data Size from 4 Bits to 16 Bits

- Serial protocol supports SPI from Motorola

- ♦ Includes DMA handshake interface

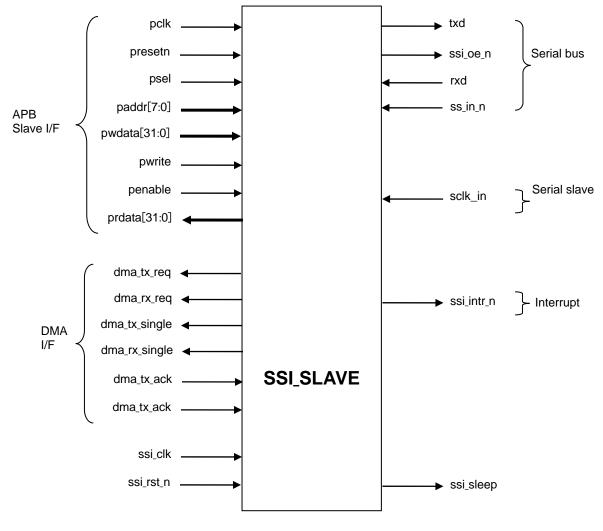

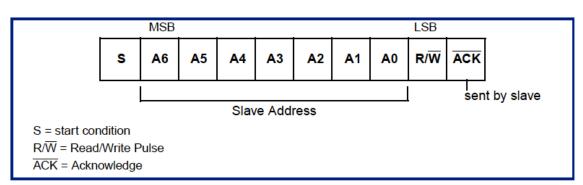

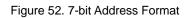

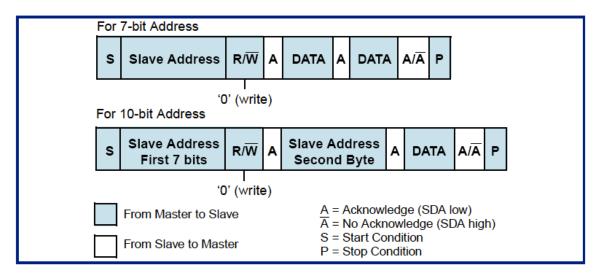

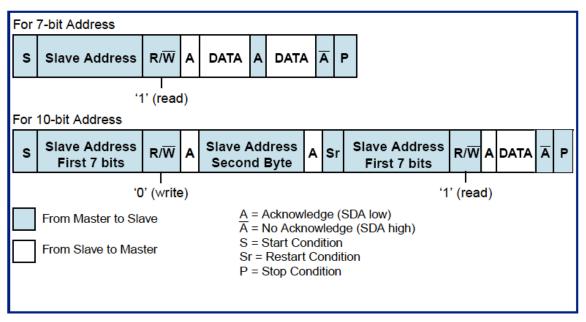

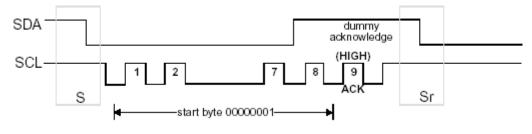

#### I2C I/F (Master/Slave)

- ♦ 2 Ch I2C Serial Interface

- $\diamond$  Supports two speed modes

- Standard Mode (100 Kb/s)

- Fast Mode (400 Kb/s)

- Supports I2C Master and Slave operation

- Allows 7 and 10 bit address generation

- $\diamondsuit$  Has built-in 32 stage transmit and receive FIFOs

- Includes DMA handshake interface

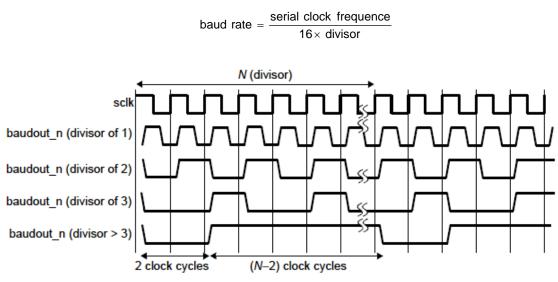

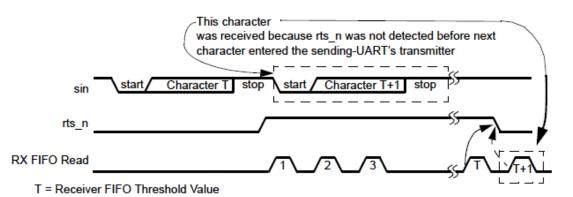

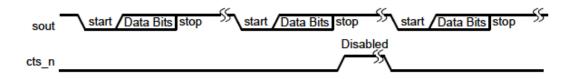

UART I/F

- IS16550-Based

- Allows various baud rate settings with software (up to 6 Mbps)

- No Support for IrDA

- ♦ FIFO DepthUp to 32 Words and FIFO Data Width Up to 8 Bits

- Incorporates a function to invert output

- ♦ Includes DMA handshake interface

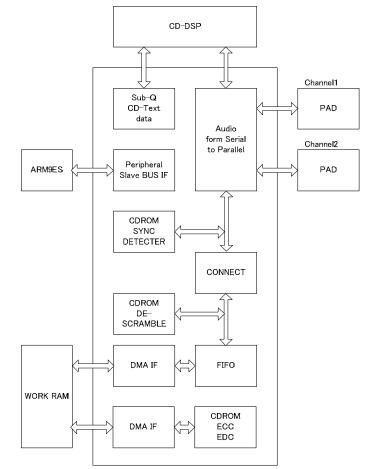

#### I2S Input I/F

- Two Lines of 2-Ch Digital Audio Input

- I2S, EIAJ Format

- 16-Bit Data

- Selectable Bit Clock from 32 fs, 48 fs, and 64 fs

- Selectable Input Sample Rate from 32 kHz, 44.1 kHz, and 48 kHz

- One Line of Internal Input from the CD Servo Controller

- Maximum Input Rate Up to 4×

- Supports detection of CD-DA link

- ♦ Supports detection of CD-ROM sync

- Supports CD-ROM data descrambling

- ♦ Acquires Sub-Q data

- Acquires CD-Text data

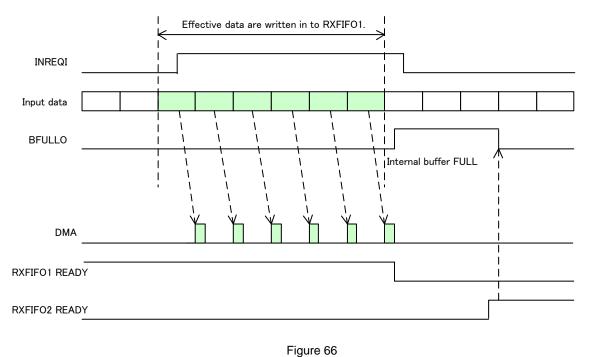

- ♦ Built-in DMA

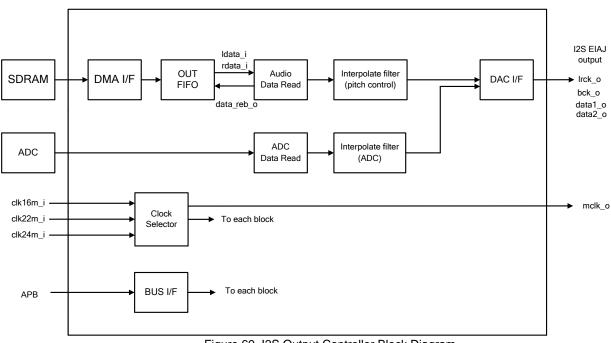

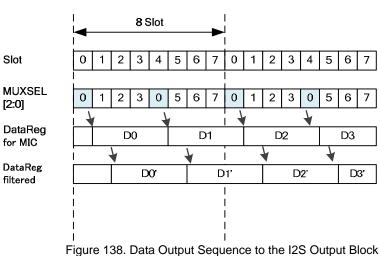

#### I2S Output I/F

- 2.1-Ch Digital Audio Output x 1

- ♦ 2 Channels from Decoder, 1 Channel from ADC

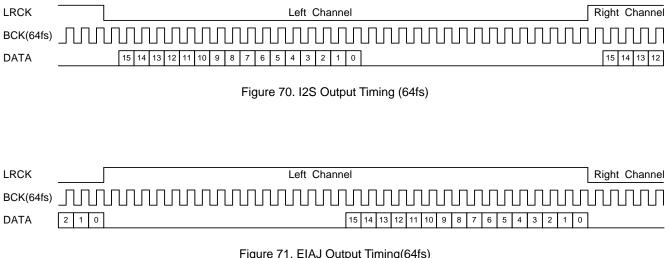

- I2S, EIAJ Format

- Selectable Output Sample Rate from 32 kHz, 44.1 kHz, 48 kHz, 88.2 kHz, 96 kHz,176.4 kHz, and 192 kHz

- Selectable Data Width from 16, 24, and 32 bits

- ♦ 64 fs Bit Clock

- Supports pitch control (×0.5 to ×2.0 in 25 steps)

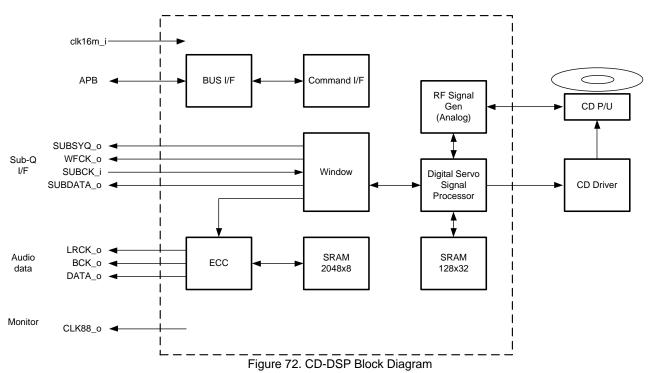

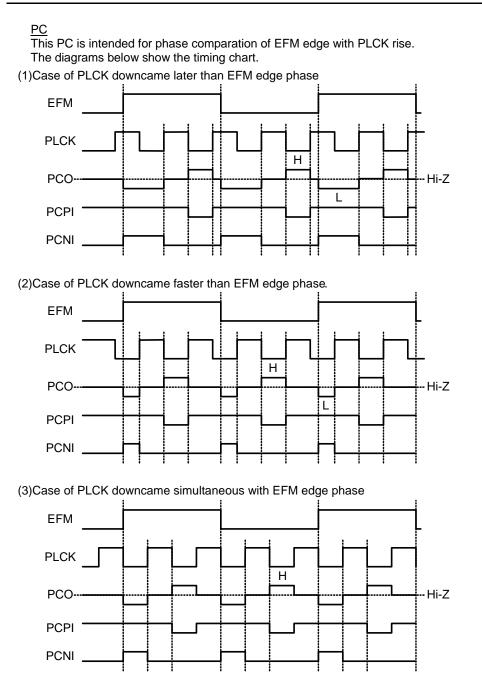

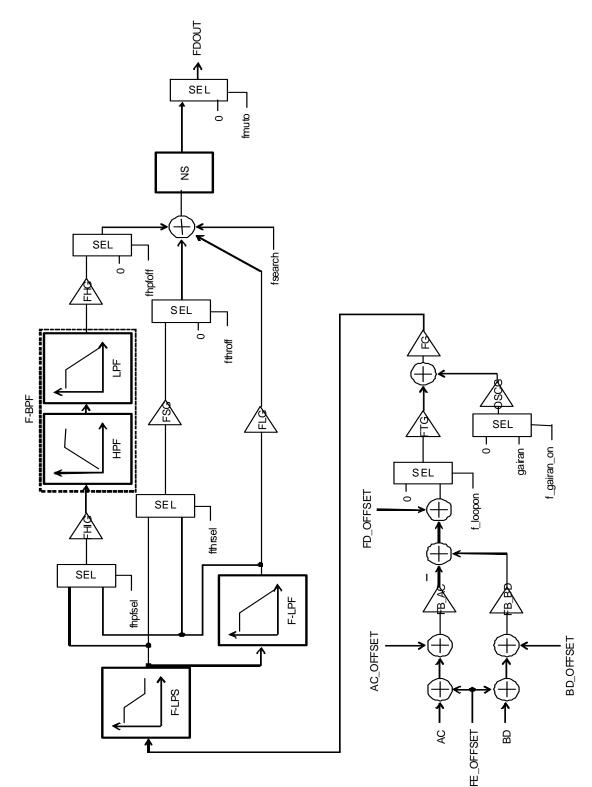

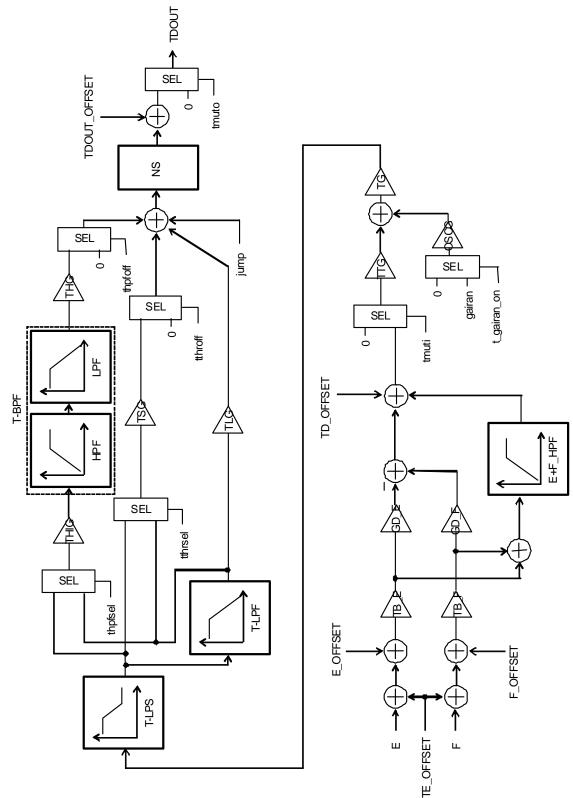

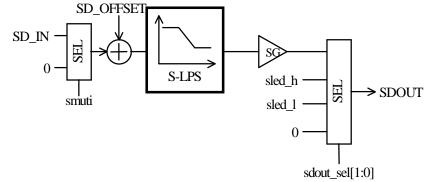

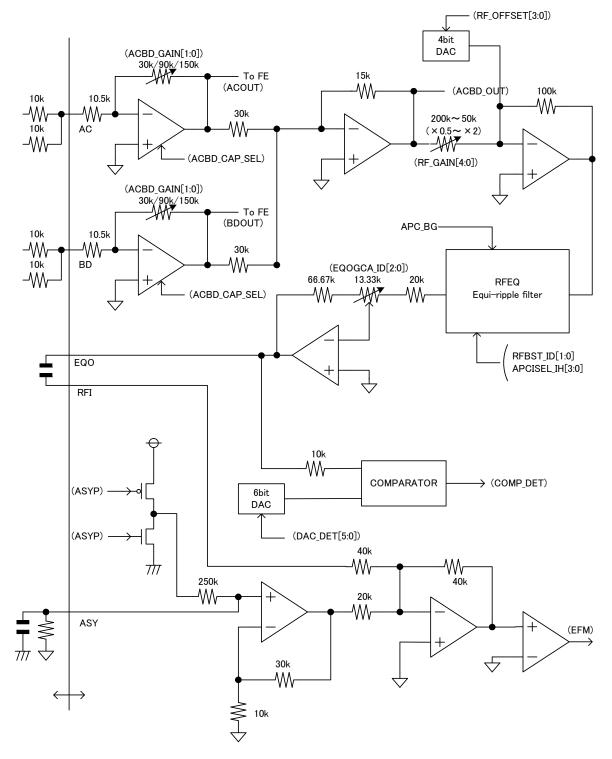

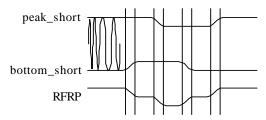

- CD Servo Controller

- Supports rotation speed of CD up to 4×

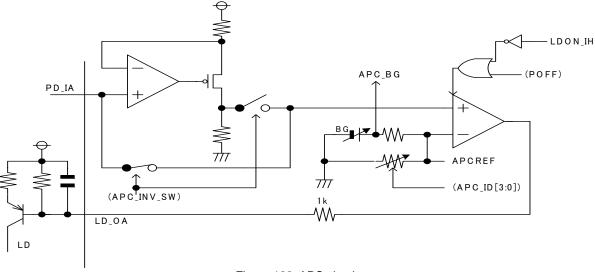

- Suilt-in Preservo-Amplifier with Power Save Mode, Which Supports Playback of CD-RW

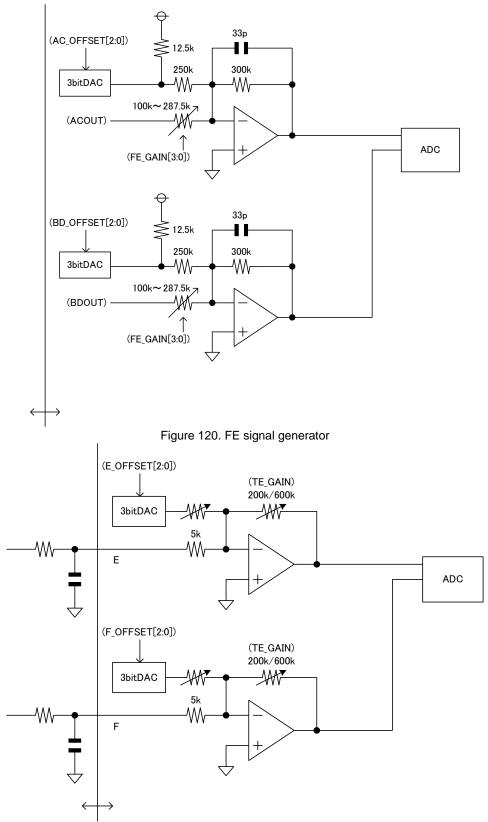

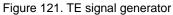

- Allows independent offset adjustment of AC, BD, E, and F amplifiers

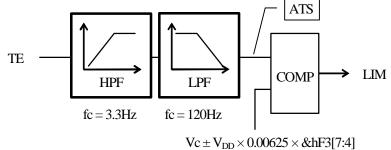

- Suilt-in Auto-Tracking and Focus Adjustment Function

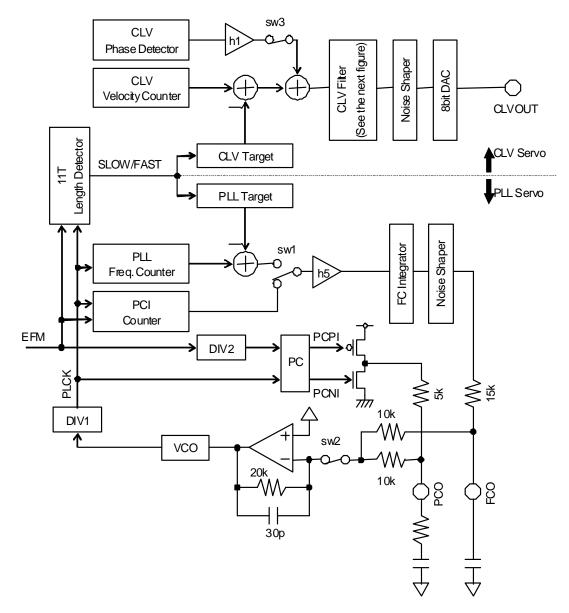

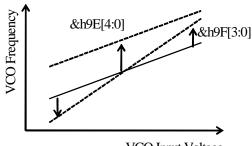

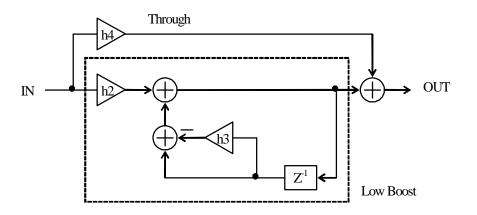

- Built in PLL and CLV with a Wide Lock Range

- ♦ Built-in Asymmetry Correction Function

#### **CD-ROM** Decoder

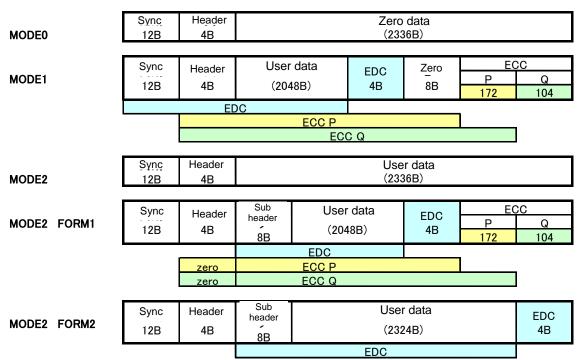

- Supports Mode1, Mode2 form1, and Mode2 form2

- ♦ Supports ECC and EDC

- ♦ Built-in DMA

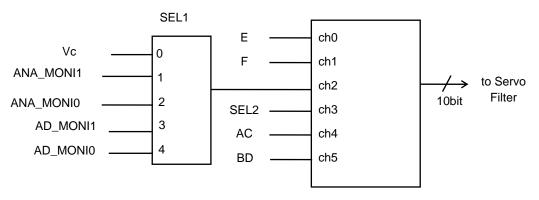

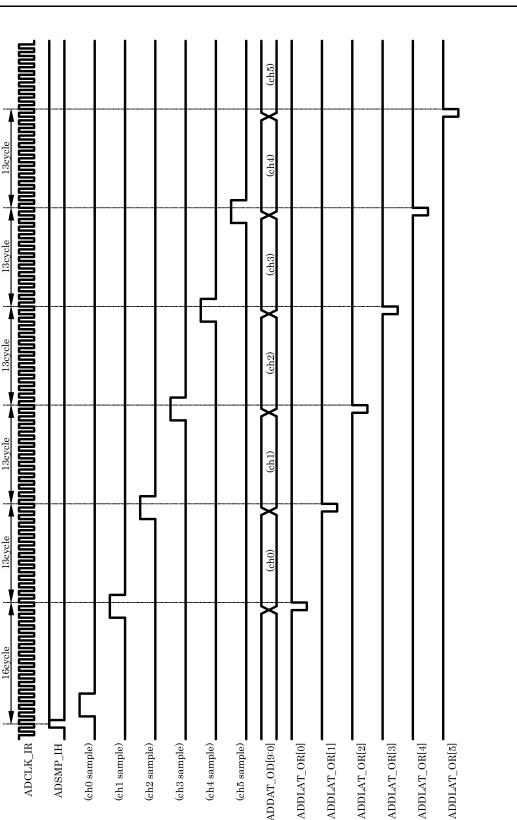

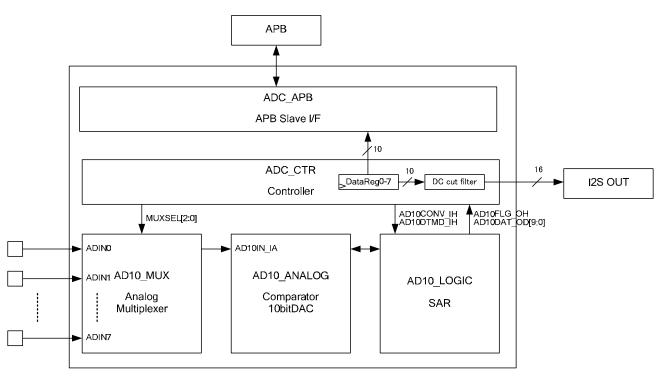

### General Purpose A/D Converter

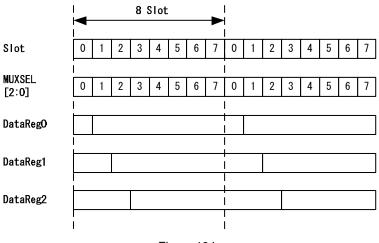

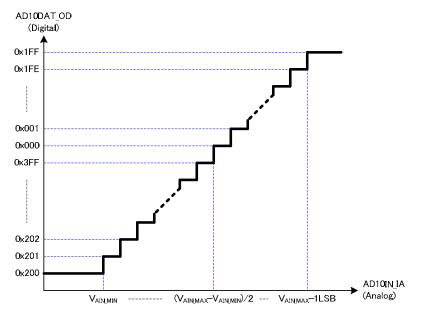

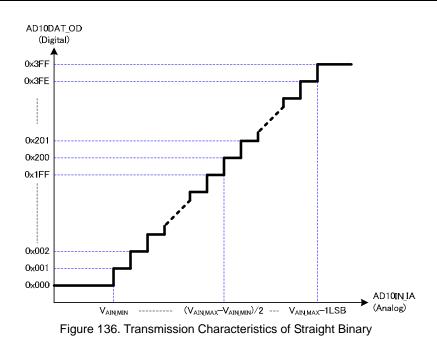

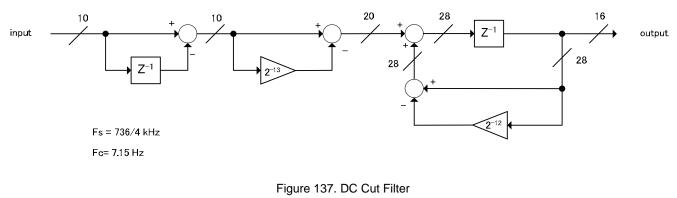

- ♦ 10-Bit SAR ADC, 8 Ch ADC

- Maximum Frequency for A/D Conversion Up to 736 kHz (for 1 Ch Converter)

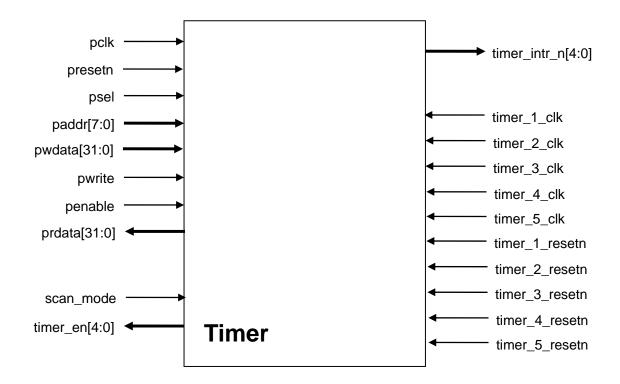

#### Timer

- ♦ Supports five independent programmable timer functions

- $\diamond$  Each timer supports time width up to 32 bits

- Each timer supports independent interrupt signal

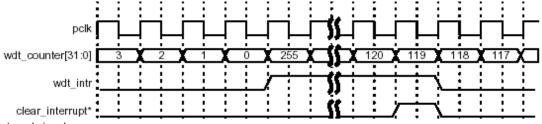

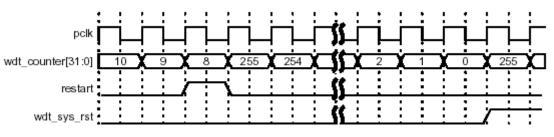

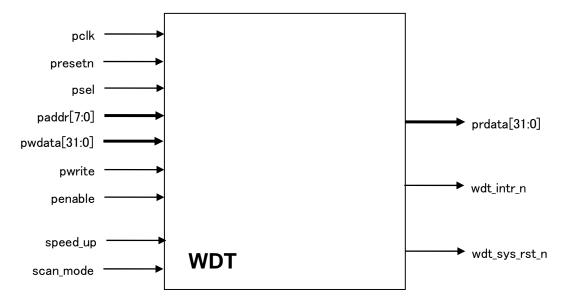

#### Watchdog Timer

- $\diamond$  Composed of a counter having a set cycle to monitor the occurrence of timeout event

- ♦ Counter Width Up to 32 Bits

- ♦ The counter counts down from the set value and sets timeout occurrence when it reaches zero

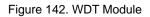

#### Real Time Clock

- ♦ 32 Bit Programmable Timer

- $\diamond$  Supports interrupt signals

- External 32.768 kHz Crystal Oscillator (External 32.768 kHz X'tal)

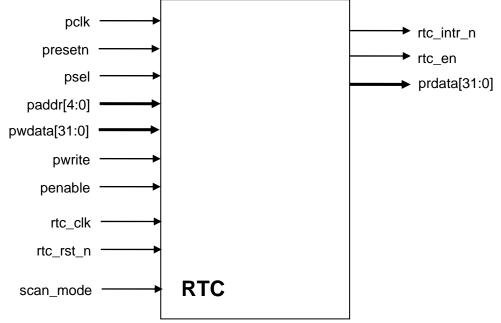

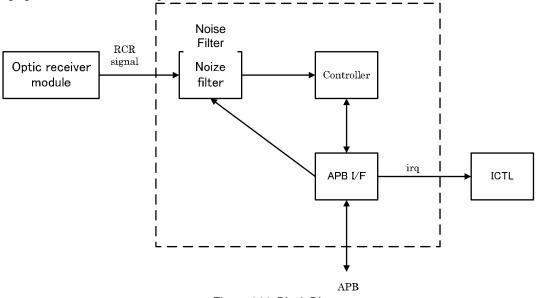

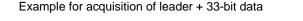

Remote Controller Receiver (RCR)

- Converts infrared remote control signal to code

- $\diamondsuit$  Compatible with the signal format of the Association for Electric Home Appliances

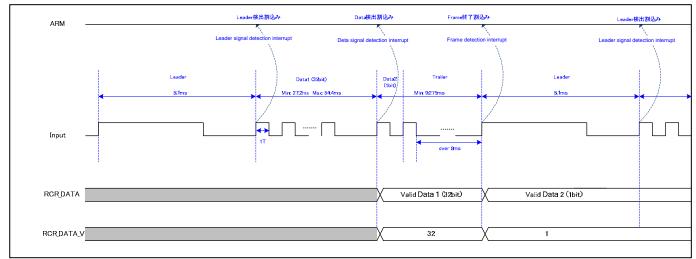

#### **Clock Generator**

- $\diamondsuit$  Supplies clocks to individual internal blocks

- Allows on/off control of clocks to individual blocks

- Generates master audio clocks

- Supports Power-Down Mode

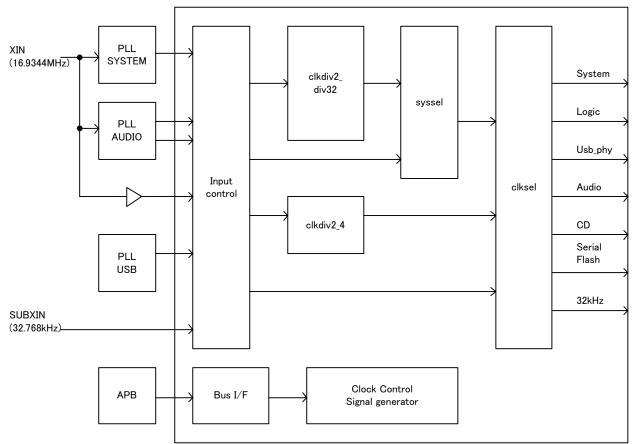

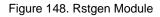

#### **Reset Generator**

♦ Generates a pulse to be supplied to individual blocks

#### PLL

- ♦ Generates 192 MHz clock used to generate system clocks

- ♦ Generates 135.4752 MHz and 147.456 MHz clocks used to generate audio clocks

Power Supply Voltage

- ♦ I/O Power Supply Voltage: 3.3V (3.0 to 3.5V)

- ♦ Analog Power Supply Voltage: 3.3V (3.0 to 3.5V)

- (used for SDRAM, CD servo, and USB) ♦ Digital Core Power Supply Voltage: 1.55V (1.5 to 1.6V)

- (used for digital core and ADC)

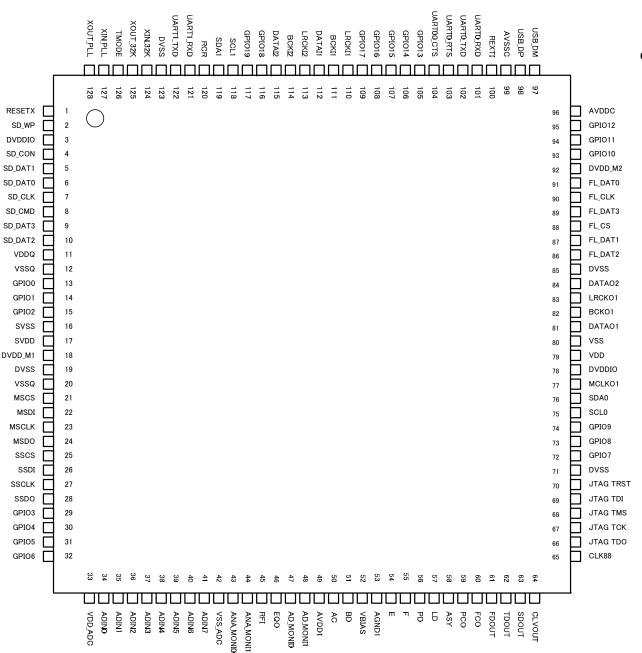

# Pin Description Pin Assignment

Figure 2. Pin Assignment Diagram

www.rohm.com © 2014 ROHM Co., Ltd. All rights reserved. TSZ22111 • 15 • 001 Downloaded from: http://www.datasheetcatalog.com/

6/376

TSZ02201-0V2V0E600300-1-2 18.Apr.2014 Rev.003

# **Pin Description**

|     | escription |           |          |                                         |

|-----|------------|-----------|----------|-----------------------------------------|

| No. | Block      | Pin Name  | I/O      | Function                                |

| 1   | RESET      | RESETX    | I        | H: Release RESET, L: RESET              |

| 2   | SDIO       | SD_WP     |          | SD Card I/F WP Detect                   |

|     |            |           |          |                                         |

| 3   | POWER      | DVDDIO    | -        | VDD (3V)                                |

| 4   | SDIO       | SD_CON    | I        | SD Card I/F Connection Detect           |

| 5   | SDIO       | SD_DAT1   | I/O      | SD Card I/F Data I/O (1)                |

| 6   | SDIO       | SD_DAT0   | I/O      | SD Card I/F Data I/O (0)                |

|     |            |           |          |                                         |

| 7   | SDIO       | SD_CLK    | 0        | SD Card I/F Clock Output                |

| 8   | SDIO       | SD_CMD    | 0        | SD Card I/F Command Output              |

| 9   | SDIO       | SD_DAT3   | I/O      | SD Card I/F Data I/O (3)                |

|     |            |           |          |                                         |

| 10  | SDIO       | SD_DAT2   | I/O      | SD Card I/F Data I/O (2)                |

| 11  | POWER      | VDDQ      | -        | SDRAM Power Supply (VDD1)               |

| 12  | POWER      | VSSQ      | -        | SDRAM Ground                            |

| 13  | GPIO       | GPIO0     | I/O      | GPIO I/O (0)                            |

| 14  |            |           |          |                                         |

|     | GPIO       | GPIO1     | I/O      | GPIO I/O (1)                            |

| 15  | GPIO       | GPIO2     | I/O      | GPIO I/O (2)                            |

| 16  | POWER      | SVSS      | -        | SDRAM Ground                            |

| 17  | POWER      | SVDD      | _        | SDRAM Power Supply (VDD1)               |

|     |            |           |          |                                         |

| 18  | POWER      | DVDD      | -        | VDD (1.5V)                              |

| 19  | POWER      | DVSS      | -        | Ground                                  |

| 20  | POWER      | VSSQ      | -        | SDRAM Ground                            |

| 21  | Master SIO | MSCS      | 0        | SIO Master Chip Select Output           |

|     |            |           | -        |                                         |

| 22  | Master SIO | MSDI      |          | SIO Master Data Input                   |

| 23  | Master SIO | MSCLK     | 0        | SIO Master Clock Output                 |

| 24  | Master SIO | MSDO      | 0        | SIO Master Data Output                  |

| 25  | Slave SIO  | SSCS      | Ī        | SIO Slave Chip Select Input             |

|     |            |           |          |                                         |

| 26  | Slave SIO  | SSDI      |          | SIO Slave Data Input                    |

| 27  | Slave SIO  | SSCLK     |          | SIO Slave Clock Input                   |

| 28  | Slave SIO  | SSDO      | 0        | SIO Slave Data Output                   |

| 29  | GPIO       | GPIO3     | I/O      | GPIO I/O (3)                            |

|     |            |           |          |                                         |

| 30  | GPIO       | GPIO4     | I/O      | GPIO I/O (4)                            |

| 31  | GPIO       | GPIO5     | I/O      | GPIO I/O (5)                            |

| 32  | GPIO       | GPIO6     | I/O      | GPIO I/O (6)                            |

| 33  | POWER      | VDD_ADC   | -        | ADC Power Supply (1.5V)                 |

|     |            |           |          |                                         |

| 34  | ADC        | ADIN0     |          | ADC Analog Input (0)                    |

| 35  | ADC        | ADIN1     | I        | ADC Analog Input (1)                    |

| 36  | ADC        | ADIN2     |          | ADC Analog Input (2)                    |

| 37  | ADC        | ADIN3     | 1        | ADC Analog Input (3)                    |

|     |            |           |          |                                         |

| 38  | ADC        | ADIN4     | I        | ADC Analog Input (4)                    |

| 39  | ADC        | ADIN5     | I        | ADC Analog Input (5)                    |

| 40  | ADC        | ADIN6     |          | ADC Analog Input (6)                    |

| 41  | ADC        | ADIN7     | 1        | ADC Analog Input (7)                    |

|     |            |           | •        |                                         |

| 42  | POWER      | VSS_ADC   | -        | ADC Ground                              |

| 43  | CDDSP      | ANA_MONI0 | 0        | Input & Analog Monitor Output           |

| 44  | CDDSP      | ANA_MONI1 | 0        | Input & Analog Monitor Output           |

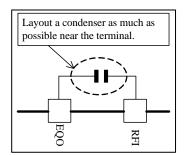

| 45  | CDDSP      | RFI       | -        | RF Output Capacitance Coupling Re-Input |

|     |            |           |          |                                         |

| 46  | CDDSP      | EQO       | 0        | Output after RF Equalizer               |

| 47  | CDDSP      | AD_MONI0  | 0        | Input & Monitor Signal Output           |

| 48  | CDDSP      | AD_MONI1  | 0        | Input & Monitor Signal Output           |

| 49  | POWER      | AVDD1     | -        | RF Analog Power Supply                  |

|     |            |           | -        |                                         |

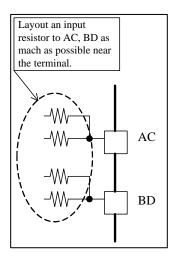

| 50  | CDDSP      | AC        | I        | A + C Voltage Input                     |

| 51  | CDDSP      | BD        | I        | B + D Voltage Input                     |

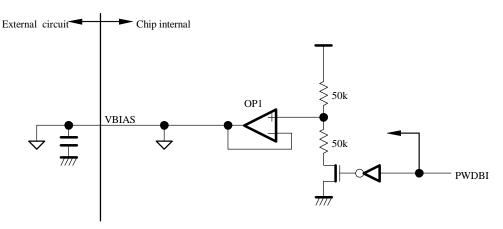

| 52  | CDDSP      | VBIAS     | 0        | Bias Level                              |

|     |            |           | <b>_</b> |                                         |

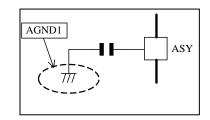

| 53  | POWER      | AGND1     | -        | RF Analog Ground                        |

| 54  | CDDSP      | E         |          | E Voltage Input                         |

| 55  | CDDSP      | F         |          | F Voltage Input                         |

| 56  | CDDSP      | PD        | I        | APC Photo Detector Input                |

|     |            |           |          |                                         |

| 57  | CDDSP      | LD        | 0        | APC Laser Drive Output                  |

| 58  | CDDSP      | ASY       |          | Asymmetric Correction                   |

| 59  | CDDSP      | PCO       | 0        | PLL PCO Output                          |

| 60  | CDDSP      | FCO       | 0        | PLL FCO-DAC Output                      |

|     |            |           |          |                                         |

| 61  | CDDSP      | FDOUT     | 0        | Focus Drive Output                      |

| 62  | CDDSP      | TDOUT     | 0        | Tracking Drive Output                   |

| 63  | CDDSP      | SDOUT     | 0        | Sled Drive Output                       |

| 64  | CDDSP      | CLVOUT    | Ő        | CLV Drive Output                        |

|     |            |           |          |                                         |

| 65  | CDDSP      | CLK88     | 0        | Clock Output for Driver IC              |

|     |            |           |          |                                         |

# **Pin Description - continued**

| ГШИ                                                                                                                                                                                                                                                                                                                                                                                                        | escription - c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ontinuea                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No                                                                                                                                                                                                                                                                                                                                                                                                         | Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin Name                                                                                                                                                                                                                                                                                                                      | I/O                                                                                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                            | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 66                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | JTAG TDO                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                              | JTAG TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 67                                                                                                                                                                                                                                                                                                                                                                                                         | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JTAG TCK                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                | JTAG TCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 68                                                                                                                                                                                                                                                                                                                                                                                                         | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JTAG TMS                                                                                                                                                                                                                                                                                                                      | I                                                                                                                                              | JTAG TMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 69                                                                                                                                                                                                                                                                                                                                                                                                         | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JTAG TDI                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                | JTAG TDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 70                                                                                                                                                                                                                                                                                                                                                                                                         | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JTAG TRST                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                | JTAG TRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 71                                                                                                                                                                                                                                                                                                                                                                                                         | POWER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DVSS                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

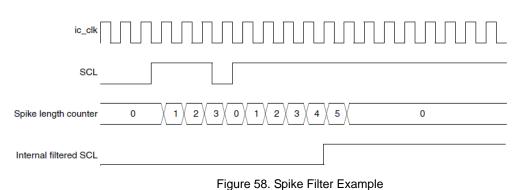

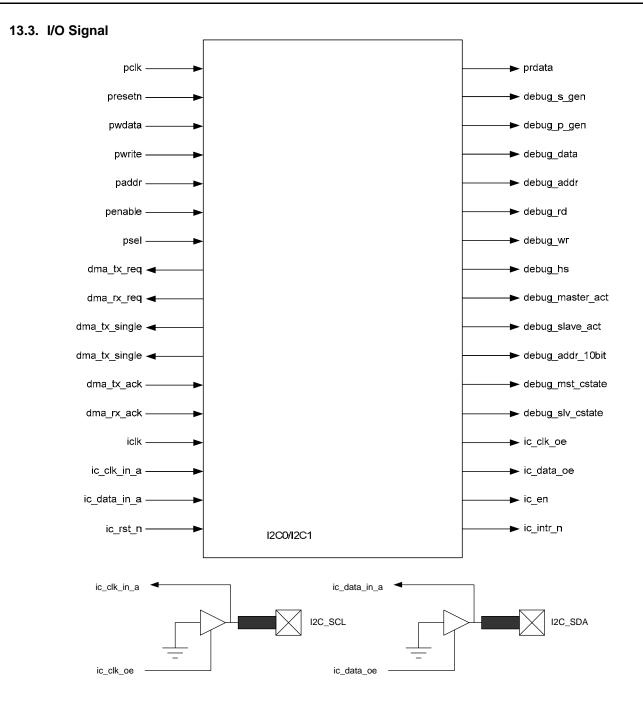

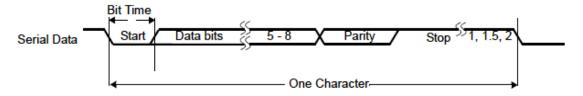

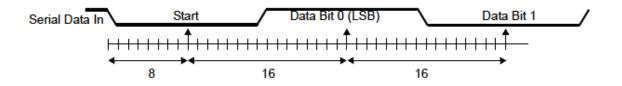

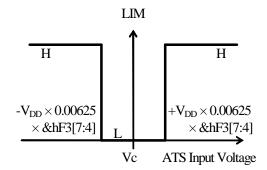

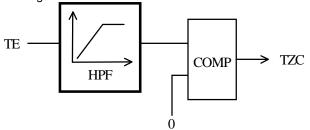

| 72                                                                                                                                                                                                                                                                                                                                                                                                         | GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPIO7                                                                                                                                                                                                                                                                                                                         | I/O                                                                                                                                            | GPIO I/O (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |