# LTC3872 No R<sub>SENSE</sub> Current Mode Boost DC/DC Controller

### **FEATURES**

- No Current Sense Resistor Required

- Vollt up to 60V

- **Constant Frequency 550kHz Operation**

- **Internal Soft-Start and Optional External Soft-Start**

- Adjustable Current Limit

- Pulse Skipping at Light Load

- $V_{IN}$  Range: 2.75V to 9.8V

- ±1.5% Voltage Reference Accuracy

- Current Mode Operation for Excellent Line and Load Transient Response

- Low Profile (1mm) SOT-23 and 2mm × 3mm DFN **Packages**

### **APPLICATIONS**

- Telecom Power Supplies

- 42V Automotive Systems

- 24V Industrial Controls

- IP Phone Power Supplies

### DESCRIPTION

The LTC®3872 is a constant frequency current mode boost DC/DC controller that drives an N-channel power MOSFET and requires very few external components. The No R<sub>SENSE</sub>™ architecture eliminates the need for a sense resistor, improves efficiency and saves board space.

The LTC3872 provides excellent AC and DC load and line regulation with ±1.5% output voltage accuracy. It incorporates an undervoltage lockout feature that shuts down the device when the input voltage falls below 2.3V.

High switching frequency of 550kHz allows the use of a small inductor. The LTC3872 is available in an 8-lead low profile (1mm) ThinSOT™ package and 8-pin 2mm × 3mm DFN package.

$oldsymbol{\mathcal{D}}$  , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and No R<sub>SENSE</sub> and ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

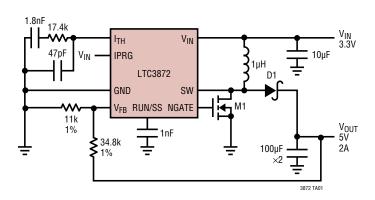

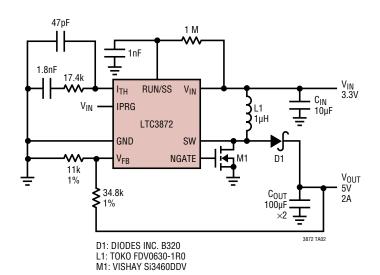

## TYPICAL APPLICATION

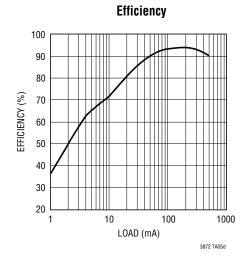

High Efficiency 3.3V Input, 5V Output Boost Converter

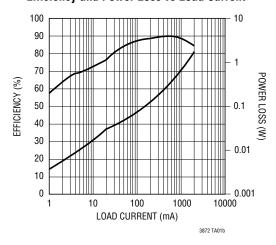

#### Efficiency and Power Loss vs Load Current

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Input Supply Voltage (V <sub>IN</sub> ), RU | N/SS0.3V to 10V              |

|---------------------------------------------|------------------------------|

| IPRG Voltage                                | $-0.3V$ to $(V_{IN} + 0.3V)$ |

| V <sub>FB</sub> , I <sub>TH</sub> Voltages  | 0.3V to 2.4V                 |

| SW Voltage                                  | 0.3V to 60V                  |

| Operating Junction Temperature Range | Э             |

|--------------------------------------|---------------|

| (Notes 2, 3)                         | 40°C to 150°C |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |               |

| TS8 Package                          | 300°C         |

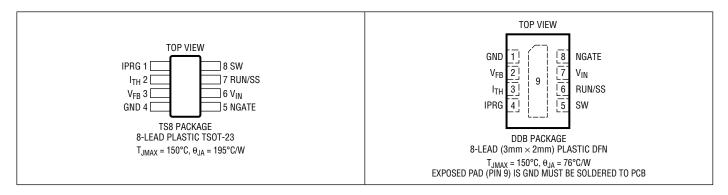

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION            | TEMPERATURE RANGE |

|------------------|-------------------|---------------|--------------------------------|-------------------|

| LTC3872ETS8#PBF  | LTC3872ETS8#TRPBF | LCGB          | 8-Lead Plastic TSOT-23         | -40°C to 85°C     |

| LTC3872ITS8#PBF  | LTC3872ITS8#TRPBF | LCGB          | 8-Lead Plastic TSOT-23         | -40°C to 125°C    |

| LTC3872HTS8#PBF  | LTC3872HTS8#TRPBF | LCGB          | 8-Lead Plastic TSOT-23         | -40°C to 150°C    |

| LTC3872EDDB#PBF  | LTC3872EDDB#TRPBF | LCHT          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 85°C     |

| LTC3872IDDB#PBF  | LTC3872IDDB#TRPBF | LCHT          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 125°C    |

| LTC3872HDDB#PBF  | LTC3872HDDB#TRPBF | LCHT          | 8-Lead (3mm × 2mm) Plastic DFN | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating temperature range, otherwise specifications are at $T_A = 25$ °C (Note 2). $V_{IN} = 4.2$ V unless otherwise noted.

| PARAMETER                                                       | CONDITIONS                                                                                                     |                                  |   | MIN               | TYP               | MAX               | UNITS          |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------|---|-------------------|-------------------|-------------------|----------------|

| Input Voltage Range                                             |                                                                                                                |                                  | • | 2.75              |                   | 9.8               | V              |

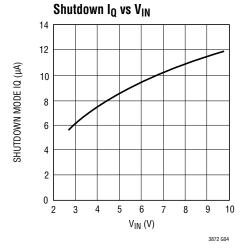

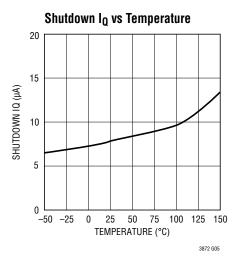

| Input DC Supply Current<br>Normal Operation<br>Shutdown<br>UVLO | Typicals at $V_{IN}$ = 4.2V (I 2.75V $\leq$ $V_{IN}$ $\leq$ 9.8V $V_{RUN/SS}$ = 0V $V_{IN}$ $<$ UVLO Threshold | V <sub>RUN/SS</sub> = 0V         |   |                   | 250<br>8<br>20    | 400<br>20<br>35   | μΑ<br>μΑ<br>μΑ |

| Undervoltage Lockout Threshold                                  | V <sub>IN</sub> Rising<br>V <sub>IN</sub> Falling                                                              |                                  | • | 2.3<br>2.05       | 2.45<br>2.3       | 2.75<br>2.55      | V              |

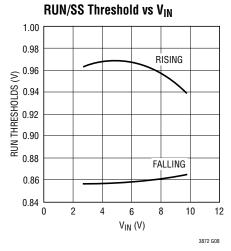

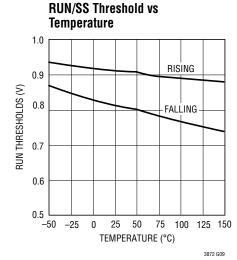

| Shutdown Threshold (at RUN/SS)                                  | V <sub>RUN/SS</sub> Falling<br>V <sub>RUN/SS</sub> Rising                                                      |                                  | • | 0.6<br>0.65       | 0.85<br>0.95      | 1.05<br>1.15      | V              |

| Regulated Feedback Voltage                                      | (Note 5) LTC3872E<br>LTC3872I and LTC3872I                                                                     | 1                                | • | 1.182<br>1.178    | 1.2<br>1.2        | 1.218<br>1.218    | V              |

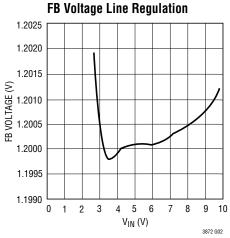

| Feedback Voltage Line Regulation                                | 2.75V < V <sub>IN</sub> < 9V (Note                                                                             | 5)                               |   |                   | 0.14              |                   | mV/V           |

| Feedback Voltage Load Regulation                                | V <sub>ITH</sub> = 1.6V (Note 5)<br>V <sub>ITH</sub> = 1V (Note 5)                                             |                                  |   |                   | 0.05<br>-0.05     |                   | %<br>%         |

| V <sub>FB</sub> Input Current                                   | (Note 5)                                                                                                       |                                  |   |                   | 25                | 50                | nA             |

| RUN/SS Pull Up Current                                          | V <sub>RUN/SS</sub> = 0                                                                                        |                                  |   | 0.35              | 0.7               | 1.25              | μА             |

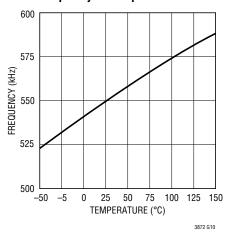

| Oscillator Frequency<br>Normal Operation                        | V <sub>FB</sub> = 1V                                                                                           |                                  |   | 500               | 550               | 650               | kHz            |

| Gate Drive Rise Time                                            | C <sub>LOAD</sub> = 3000pF                                                                                     |                                  |   |                   | 40                |                   | ns             |

| Gate Drive Fall Time                                            | C <sub>LOAD</sub> = 3000pF                                                                                     |                                  |   |                   | 40                |                   | ns             |

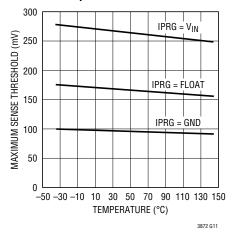

| Peak Current Sense Voltage                                      | IPRG = GND (Note 6)                                                                                            | LTC3872E<br>LTC3872I<br>LTC3872H | • | 80<br>70<br>65    | 100<br>100<br>100 | 120<br>120<br>120 | mV<br>mV<br>mV |

|                                                                 | IPRG = Float                                                                                                   | LTC3872E<br>LTC3872I<br>LTC3872H | • | 145<br>135<br>130 | 170<br>170<br>170 | 195<br>195<br>195 | mV<br>mV<br>mV |

|                                                                 | IPRG = V <sub>IN</sub>                                                                                         | LTC3872E<br>LTC3872I<br>LTC3872H | • | 240<br>225<br>215 | 270<br>270<br>270 | 290<br>290<br>290 | mV<br>mV<br>mV |

| Default Internal Soft-Start Time                                |                                                                                                                |                                  |   |                   | 1                 |                   | ms             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3872 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3872E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3872I is guaranteed over the -40°C to 125°C operating junction temperature range. The LTC3872H is guaranteed over the full -40°C to 150°C operating junction temperature range. The maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

LTC3872TS8:  $T_J = T_A + (P_D \cdot 195^{\circ}C/W)$ LTC3872DDB:  $T_J = T_A + (P_D \cdot 76^{\circ}C/W)$

**Note 4:** The dynamic input supply current is higher due to power MOSFET gate charging ( $Q_G \cdot f_{OSC}$ ). See Applications Information.

**Note 5:** The LTC3872 is tested in a feedback loop which servos  $V_{FB}$  to the reference voltage with the  $I_{TH}$  pin forced to the midpoint of its voltage range (0.7V  $\leq$   $V_{ITH} \leq$  1.9V, midpoint = 1.3V).

Note 6: Rise and fall times are measured at 10% and 90% levels.

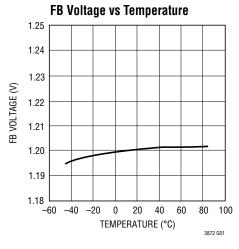

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

**Gate Drive Rise and Fall Time** vs C<sub>load</sub> 100 90 80 70 RISE TIME 60 TIME (ns) FALL TIME 50 40 30 20 10 0 2000 6000 8000 4000 10000 C<sub>LOAD</sub> (pF)

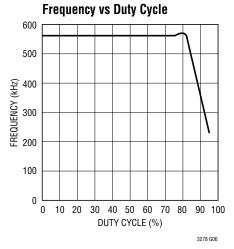

#### Frequency vs Temperature

# Maximum Sense Threshold vs Temperature

## PIN FUNCTIONS (TS8/DD8)

IPRG (Pin 1/Pin 4): Current Sense Limit Select Pin.

I<sub>TH</sub> (Pin 2/Pin 3): It serves as the error amplifier compensation point. Nominal voltage range for this pin is 0.7V to 1.9V.

**V<sub>FB</sub> (Pin 3/Pin 2):** Receives the feedback voltage from an external resistor divider across the output.

**GND (Pin 4/Pin 1, Exposed Pad Pin 9):** Ground. The exposed pad must be soldered to PCB ground for electrical contact and rated thermal performance.

**NGATE (Pin 5/Pin 8):** Gate Drive for the External N-Channel MOSFET. This pin swings from 0V to  $V_{IN}$ .

$V_{IN}$  (Pin 6/Pin 7): Supply Pin. This pin must be closely decoupled to GND.

**RUN/SS (Pin 7/Pin 6):** Shutdown and external soft-start pin. In shutdown, all functions are disabled and the NGATE pin is held low.

**SW** (**Pin 8/Pin 5**): Switch node connection to inductor and current sense input pin through external slope compensation resistor. Normally, the external N-channel MOSFET's drain is connected to this pin.

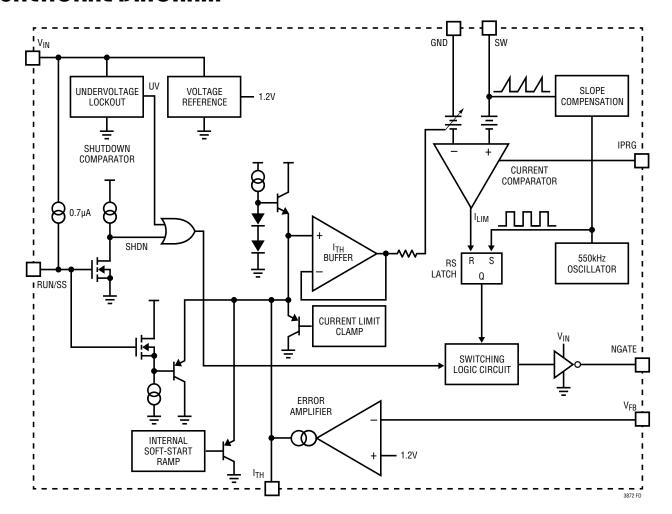

## **FUNCTIONAL DIAGRAM**

## **OPERATION**

#### **Main Control Loop**

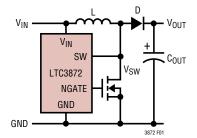

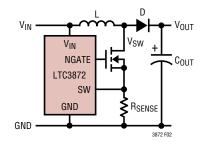

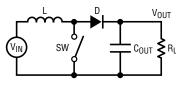

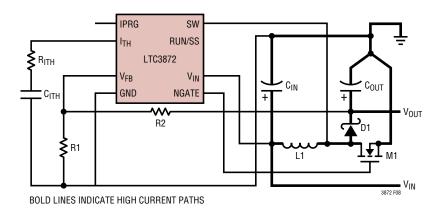

The LTC3872 is a No  $R_{SENSE}$  constant frequency, current mode controller for DC/DC boost, SEPIC and flyback converter applications. The LTC3872 is distinguished from conventional current mode controllers because the current control loop can be closed by sensing the voltage drop across the power MOSFET switch or across a discrete sense resistor, as shown in Figures 1 and 2. This No  $R_{SENSE}$  sensing technique improves efficiency, increases power density and reduces the cost of the overall solution.

For circuit operation, please refer to the Block Diagram of the IC and the Typical Application on the front page. In normal operation, the power MOSFET is turned on when the oscillator sets the RS latch and is turned off when the current comparator resets the latch. The divided-down output voltage is compared to an internal 1.2V reference by the error amplifier, which outputs an error signal at the  $I_{TH}$  pin. The voltage on the  $I_{TH}$  pin sets the current comparator input threshold. When the load current increases, a fall in the FB voltage relative to the reference voltage causes the  $I_{TH}$  pin to rise, which causes the current comparator to trip at a higher peak inductor current value. The average inductor current will therefore rise until it equals the load current, thereby maintaining output regulation.

The LTC3872 can be used either by sensing the voltage drop across the power MOSFET or by connecting the SW pin to a conventional sensing resistor in the source of the power MOSFET. Sensing the voltage across the power MOSFET maximizes converter efficiency and minimizes the

Figure 1. SW Pin (Internal Sense Pin) Connection for Maximum Efficiency

component count; the maximum rating for this pin, 60V, allows MOSFET sensing in a wide output voltage range.

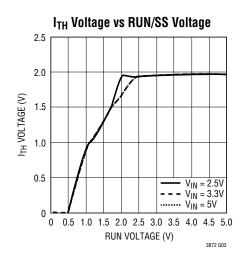

The RUN/SS pin controls whether the IC is enabled or is in a low current shutdown state. With the RUN/SS pin below 0.85V, the chip is off and the input supply current is typically only  $8\mu A$ . With an external capacitor connected to the RUN/SS pin an optional external soft-start is enabled. A 0.7 $\mu A$  trickle current will charge the capacitor, pulling the RUN/SS pin above shutdown threshold and slowly ramping RUN/SS to limit the  $V_{ITH}$  during start-up. Because the noise on the SW pin could couple into the RUN/SS pin, disrupting the trickle charge current that charges the RUN/SS pin, a 1M resistor is recommended to pull-up the RUN/SS pin when external soft-start is used. When RUN/SS is driven by an external logic, a minimum of 2.75V logic is recommended to allow the maximum  $I_{TH}$  range.

#### **Light Load Operation**

Under very light load current conditions, the I<sub>TH</sub> pin voltage will be very close to the zero current level of 0.85V. As the load current decreases further, an internal offset at the current comparator input will assure that the current comparator remains tripped (even at zero load current) and the regulator will start to skip cycles, as it must, in order to maintain regulation. This behavior allows the regulator to maintain constant frequency down to very light loads, resulting in low output ripple as well as low audible noise and reduced RF interference, while providing high light load efficiency.

Figure 2. SW Pin (Internal Sense Pin) Connection for Sensing Resistor

#### **Output Voltage Programming**

The output voltage is set by a resistor divider according to the following formula:

$$V_0 = 1.2V \cdot \left(1 + \frac{R2}{R1}\right)$$

The external resistor divider is connected to the output as shown in the Typical Application on the front page, allowing remote voltage sensing.

#### **Application Circuits**

A basic LTC3872 application circuit is shown on the front page of this datasheet. External component selection is driven by the characteristics of the load and the input supply.

#### **Duty Cycle Considerations**

For a boost converter operating in a continuous conduction mode (CCM), the duty cycle of the main switch is:

$$D = \left(\frac{V_{0} + V_{D} - V_{IN}}{V_{0} + V_{D}}\right)$$

where  $V_D$  is the forward voltage of the boost diode. For converters where the input voltage is close to the output voltage, the duty cycle is low and for converters that develop a high output voltage from a low voltage input supply, the duty cycle is high. The LTC3872 has a built-in circuit that allows the extension of the maximum duty cycle while keeping the minimum switch off time unchanged. This is accomplished by reducing the clock frequency when the duty cycle is close to 80%. This function allows the user to obtain high output voltages from low input supply voltages. The shift of frequency with duty cycle is shown in the Typical Performance Characteristics section.

### The Peak and Average Input Currents

The control circuit in the LTC3872 is measuring the input current (either by using the  $R_{DS(ON)}$  of the power MOSFET or by using a sense resistor in the MOSFET source), so the output current needs to be reflected back to the input in order to dimension the power MOSFET properly. Based

on the fact that, ideally, the output power is equal to the input power, the maximum average input current is:

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

The peak input current is:

$$I_{IN(PEAK)} = \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

#### Ripple Current I<sub>L</sub> and the $\chi$ Factor

The constant  $\chi$  in the equation above represents the percentage peak-to-peak ripple current in the inductor, relative to its maximum value. For example, if 30% ripple current is chosen, then  $\chi = 0.30$ , and the peak current is 15% greater than the average.

For a current mode boost regulator operating in CCM, slope compensation must be added for duty cycles above 50% in order to avoid subharmonic oscillation. For the LTC3872, this ramp compensation is internal. Having an internally fixed ramp compensation waveform, however, does place some constraints on the value of the inductor and the operating frequency. If too large an inductor is used, the resulting current ramp  $(I_I)$  will be small relative to the internal ramp compensation (at duty cycles above 50%), and the converter operation will approach voltage mode (ramp compensation reduces the gain of the current loop). If too small an inductor is used, but the converter is still operating in CCM (continuous conduction mode), the internal ramp compensation may be inadequate to prevent subharmonic oscillation. To ensure good current mode gain and avoid subharmonic oscillation, it is recommended that the ripple current in the inductor fall in the range of 20% to 40% of the maximum average current. For example, if the maximum average input current is 1A, choose an I<sub>I</sub> between 0.2A and 0.4A, and a value  $\chi$  between 0.2 and 0.4.

#### **Inductor Selection**

Given an operating input voltage range, and having chosen the operating frequency and ripple current in the inductor,

> LINEAR TECHNOLOGY

the inductor value can be determined using the following equation:

$$L = \frac{V_{IN(MIN)}}{\Delta I_I \bullet f} \bullet D_{MAX}$$

where:

$$\Delta I_{L} = \chi \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

Remember that boost converters are **not** short-circuit protected. Under a shorted output condition, the inductor current is limited only by the input supply capability.

The minimum required saturation current of the inductor can be expressed as a function of the duty cycle and the load current, as follows:

$$I_{L(SAT)} \ge \left(1 + \frac{\chi}{2}\right) \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

The saturation current rating for the inductor should be checked at the minimum input voltage (which results in the highest inductor current) and maximum output current.

### **Operating in Discontinuous Mode**

Discontinuous mode operation occurs when the load current is low enough to allow the inductor current to run out during the off-time of the switch. Once the inductor current is near zero, the switch and diode capacitances resonate with the inductance to form damped ringing at 1MHz to 10MHz. If the off-time is long enough, the drain voltage will settle to the input voltage.

Depending on the input voltage and the residual energy in the inductor, this ringing can cause the drain of the power MOSFET to go below ground where it is clamped by the body diode. This ringing is not harmful to the IC and it has been shown not to contribute significantly to EMI. Any attempt to damp it with a snubber will degrade the efficiency.

#### Inductor Core Selection

Once the value for L is known, the type of inductor must be selected. Actual core loss is independent of core size for a fixed inductor value, but is very dependent on the inductance selected. As inductance increases, core losses go down. Unfortunately, increased inductance requires more turns of wire and therefore, copper losses will increase. Generally, there is a tradeoff between core losses and copper losses that needs to be balanced.

Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper losses and preventing saturation. Ferrite core material saturates "hard," meaning that the inductance collapses rapidly when the peak design current is exceeded. This results in an abrupt increase in inductor ripple current and consequently, output voltage ripple. **Do not allow the core to saturate!**

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar characteristics. The choice of which style inductor to use mainly depends on the price vs size requirements and any radiated field/EMI requirements. New designs for surface mount inductors are available from Coiltronics, Coilcraft, Toko and Sumida.

#### **Power MOSFET Selection**

The power MOSFET serves two purposes in the LTC3872: it represents the main switching element in the power path and its  $R_{DS(0N)}$  represents the current sensing element for the control loop. Important parameters for the power MOSFET include the drain-to-source breakdown voltage (BV $_{DSS}$ ), the threshold voltage (V $_{GS(TH)}$ ), the onresistance (R $_{DS(0N)}$ ) versus gate-to-source voltage, the gate-to-source and gate-to-drain charges (Q $_{GS}$  and Q $_{GD}$ , respectively), the maximum drain current (I $_{D(MAX)}$ ) and the MOSFET's thermal resistances (R $_{TH(JC)}$  and R $_{TH(JA)}$ ). Logic-level (4.5V V $_{GS-RATED}$ ) threshold MOSFETs should be used when input voltage is high, otherwise if low input voltage operation is expected (e.g., supplying power from a lithium-ion battery or a 3.3V logic supply), then sublogic-level (2.5V V $_{GS-RATED}$ ) threshold MOSFETs should be used.

Pay close attention to the BV<sub>DSS</sub> specifications for the MOSFETs relative to the maximum actual switch voltage in the application. Many logic-level devices are limited

3872f

to 30V or less, and the switch node can ring during the turn-off of the MOSFET due to layout parasitics. Check the switching waveforms of the MOSFET directly across the drain and source terminals using the actual PC board layout (not just on a lab breadboard!) for excessive ringing.

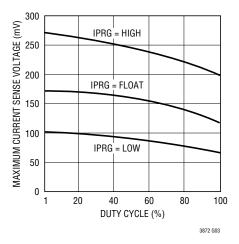

During the switch on-time, the control circuit limits the maximum voltage drop across the power MOSFET to about 270mV, 100mV and 170mV at low duty cycle with IPRG tied to  $V_{IN}$ , GND, or left floating respectively. The peak inductor current is therefore limited to (270mV, 170mV and 100mV)/ $R_{DS(ON)}$  depending on the status of the IPRG pin.

The relationship between the maximum load current, duty cycle and the  $R_{DS(ON)}$  of the power MOSFET is:

$$R_{DS(ON)} \le V_{SENSE(MAX)} \bullet \frac{1 - D_{MAX}}{\left(1 + \frac{\chi}{2}\right) \bullet I_{O(MAX)} \bullet \rho_{T}}$$

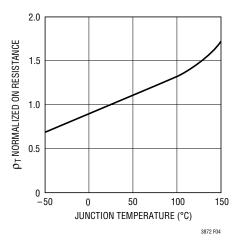

$V_{SENSE(MAX)}$  is the maximum voltage drop across the power MOSFET.  $V_{SENSE(MAX)}$  is typically 270mV, 170mV and 100mV. It is reduced with increasing duty cycle as shown in Figure 3. The  $\rho_T$  term accounts for the temperature coefficient of the  $R_{DS(ON)}$  of the MOSFET, which is typically 0.4%/°C. Figure 4 illustrates the variation of normalized  $R_{DS(ON)}$  over temperature for a typical power MOSFET.

Another method of choosing which power MOSFET to use is to check what the maximum output current is for a given R<sub>DS(ON)</sub>, since MOSFET on-resistances are available in discrete values.

$$I_{O(MAX)} = V_{SENSE(MAX)} \bullet \frac{1 - D_{MAX}}{\left(1 + \frac{\chi}{2}\right) \bullet R_{DS(ON)} \bullet \rho_{T}}$$

It is worth noting that the  $1-D_{MAX}$  relationship between  $I_{O(MAX)}$  and  $R_{DS(ON)}$  can cause boost converters with a wide input range to experience a dramatic range of maximum input and output current. This should be taken into consideration in applications where it is important to limit the maximum current drawn from the input supply.

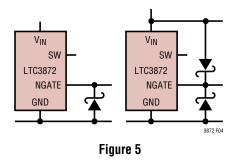

Voltage on the NGATE pin should be within -0.3V to  $(V_{IN} + 0.3V)$  limits. Voltage stress below -0.3V and above  $V_{IN} + 0.3V$  can damage internal MOSFET driver, see Functional Diagram. This is especially important in case of

driving MOSFETs with relatively high package inductance (DPAK and bigger) or inadequate layout. A small Schottky diode between NGATE pin and ground can prevent negative voltage spikes. Two small Schottky diodes can inhibit positive and negative voltage spikes (Figure 5).

Figure 3. Maximum SENSE Threshold Voltage vs Duty Cycle

Figure 4. Normalized  $R_{DS(ON)}$  vs Temperature

# Calculating Power MOSFET Switching and Conduction Losses and Junction Temperatures

In order to calculate the junction temperature of the power MOSFET, the power dissipated by the device must be known. This power dissipation is a function of the duty cycle, the load current and the junction temperature itself (due to the positive temperature coefficient of its  $R_{DS(ON)}$ ). As a result, some iterative calculation is normally required to determine a reasonably accurate value. Since the controller is using the MOSFET as both a switching and a sensing element, care should be taken to ensure that the converter is capable of delivering the required load current over all operating conditions (line voltage and temperature), and for the worst-case specifications for  $V_{SENSE(MAX)}$  and the  $R_{DS(ON)}$  of the MOSFET listed in the manufacturer's data sheet.

The power dissipated by the MOSFET in a boost converter is:

$$P_{FET} = \left(\frac{I_{O(MAX)}}{1 - D_{MAX}}\right)^{2} \cdot R_{DS(ON)} \cdot D_{MAX} \cdot \rho_{T}$$

$$+ k \cdot V_{O}^{1.85} \cdot \frac{I_{O(MAX)}}{(1 - D_{MAX})} \cdot C_{RSS} \cdot f$$

The first term in the equation above represents the  $I^2R$  losses in the device, and the second term, the switching losses. The constant, k=1.7, is an empirical factor inversely related to the gate drive current and has the dimension of 1/current.

From a known power dissipated in the power MOSFET, its junction temperature can be obtained using the following formula:

$$T_J = T_A + P_{FET} \cdot R_{TH(JA)}$$

The  $R_{TH(JA)}$  to be used in this equation normally includes the  $R_{TH(JC)}$  for the device plus the thermal resistance from the case to the ambient temperature ( $R_{TH(CA)}$ ). This value of  $T_J$  can then be compared to the original, assumed value used in the iterative calculation process.

#### **Output Diode Selection**

To maximize efficiency, a fast switching diode with low forward drop and low reverse leakage is desired. The output

diode in a boost converter conducts current during the switch off-time. The peak reverse voltage that the diode must withstand is equal to the regulator output voltage. The average forward current in normal operation is equal to the output current, and the peak current is equal to the peak inductor current.

$$I_{D(PEAK)} = I_{L(PEAK)} = \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

The power dissipated by the diode is:

$$P_D = I_{O(MAX)} \cdot V_D$$

and the diode junction temperature is:

$$T_J = T_A + P_D \bullet R_{TH(JA)}$$

The  $R_{TH(JA)}$  to be used in this equation normally includes the  $R_{TH(JC)}$  for the device plus the thermal resistance from the board to the ambient temperature in the enclosure.

Remember to keep the diode lead lengths short and to observe proper switch-node layout (see Board Layout Checklist) to avoid excessive ringing and increased dissipation.

## **Output Capacitor Selection**

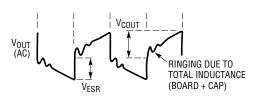

Contributions of ESR (equivalent series resistance), ESL (equivalent series inductance) and the bulk capacitance must be considered when choosing the correct component for a given output ripple voltage. The effects of these three parameters (ESR, ESL and bulk C) on the output voltage ripple waveform are illustrated in Figure 6e for a typical boost converter.

The choice of component(s) begins with the maximum acceptable ripple voltage (expressed as a percentage of the output voltage), and how this ripple should be divided between the ESR step and the charging/discharging  $\Delta V$ . For the purpose of simplicity we will choose 2% for the maximum output ripple, to be divided equally between the ESR step and the charging/discharging  $\Delta V$ . This percentage ripple will change, depending on the requirements of the application, and the equations provided below can easily be modified.

For a 1% contribution to the total ripple voltage, the ESR of the output capacitor can be determined using the following equation:

$$ESR_{COUT} \le \frac{0.01 \cdot V_0}{I_{IN(PEAK)}}$$

where:

$$I_{IN(PEAK)} = \left(1 + \frac{\chi}{2}\right) \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

For the bulk C component, which also contributes 1% to the total ripple:

$$C_{OUT} \ge \frac{I_{O(MAX)}}{0.01 \cdot V_{O} \cdot f}$$

For many designs it is possible to choose a single capacitor type that satisfies both the ESR and bulk C requirements for the design. In certain demanding applications, however, the ripple voltage can be improved significantly by connecting two or more types of capacitors in parallel. For example, using a low ESR ceramic capacitor can minimize the ESR step, while an electrolytic capacitor can be used to supply the required bulk C.

Once the output capacitor ESR and bulk capacitance have been determined, the overall ripple voltage waveform should be verified on a dedicated PC board (see Board Layout section for more information on component placement). Lab breadboards generally suffer from excessive series inductance (due to inter-component wiring), and these parasitics can make the switching waveforms look significantly worse than they would be on a properly designed PC board.

The output capacitor in a boost regulator experiences high RMS ripple currents, as shown in Figure 7. The RMS output capacitor ripple current is:

$$I_{RMS(COUT)} \approx I_{O(MAX)} \bullet \sqrt{\frac{V_{O} - V_{IN(MIN)}}{V_{IN(MIN)}}}$$

Note that the ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life. This makes it advisable to further derate the capacitor or to

choose a capacitor rated at a higher temperature than required. Several capacitors may also be placed in parallel to meet size or height requirements in the design.

Manufacturers such as Nichicon, United Chemicon and Sanyo should be considered for high performance throughhole capacitors. The OS-CON semiconductor dielectric capacitor available from Sanyo has the lowest product of ESR and size of any aluminum electrolytic, at a somewhat higher price.

In surface mount applications, multiple capacitors may have to be placed in parallel in order to meet the ESR or RMS current handling requirements of the application. Aluminum electrolytic and dry tantalum capacitors are

6a. Circuit Diagram

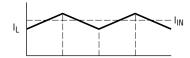

6b. Inductor and Input Currents

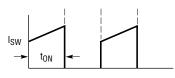

6c. Switch Current

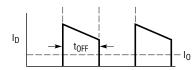

6d. Diode and Output Currents

6e. Output Voltage Ripple Waveform

Figure 6. Switching Waveforms for a Boost Converter

both available in surface mount packages. In the case of tantalum, it is critical that the capacitors have been surge tested for use in switching power supplies. An excellent choice is AVX TPS series of surface mount tantalum. Also, ceramic capacitors are now available with extremely low ESR, ESL and high ripple current ratings.

#### **Input Capacitor Selection**

The input capacitor of a boost converter is less critical than the output capacitor, due to the fact that the inductor is in series with the input and the input current waveform is continuous (see Figure 6b). The input voltage source impedance determines the size of the input capacitor, which is typically in the range of  $10\mu\text{F}$  to  $100\mu\text{F}$ . A low ESR capacitor is recommended, although it is not as critical as for the output capacitor.

The RMS input capacitor ripple current for a boost converter is:

$$I_{RMS(CIN)} = 0.3 \bullet \frac{V_{IN(MIN)}}{L \bullet f} \bullet D_{MAX}$$

Please note that the input capacitor can see a very high surge current when a battery is suddenly connected to the input of the converter and solid tantalum capacitors can fail catastrophically under these conditions. **Be sure to specify surge-tested capacitors!**

# Efficiency Considerations: How Much Does VDS Sensing Help?

The efficiency of a switching regulator is equal to the output power divided by the input power ( $\times 100\%$ ).

Percent efficiency can be expressed as:

% Efficiency =

$$100\% - (L1 + L2 + L3 + ...)$$

,

where L1, L2, etc. are the individual loss components as a percentage of the input power. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Although all dissipative elements in the circuit produce losses, four main sources usually account for the majority of the losses in LTC3872 application circuits:

1. The supply current into  $V_{\text{IN}}.$  The  $V_{\text{IN}}$  current is the

sum of the DC supply current  $I_Q$  (given in the Electrical Characteristics) and the MOSFET driver and control currents. The DC supply current into the  $V_{IN}$  pin is typically about 250µA and represents a small power loss (much less than 1%) that increases with  $V_{IN}$ . The driver current results from switching the gate capacitance of the power MOSFET; this current is typically much larger than the DC current. Each time the MOSFET is switched on and then off, a packet of gate charge  $Q_G$  is transferred from  $V_{IN}$  to ground. The resulting dQ/dt is a current that must be supplied to the Input capacitor by an external supply. If the IC is operating in CCM:

$$I_{Q(T0T)} \approx I_Q = f \cdot Q_G$$

$P_{IC} = V_{IN} \cdot (I_Q + f \cdot Q_G)$

2. Power MOSFET switching and conduction losses. The technique of using the voltage drop across the power MOSFET to close the current feedback loop was chosen because of the increased efficiency that results from not having a sense resistor. The losses in the power MOSFET are equal to:

$$P_{FET} = \left(\frac{I_{O(MAX)}}{1 - D_{MAX}}\right)^{2} \bullet R_{DS(ON)} \bullet D_{MAX} \bullet \rho_{T}$$

$$+ k \bullet V_{O}^{1.85} \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}} \bullet C_{RSS} \bullet f$$

The I<sup>2</sup>R power savings that result from not having a discrete sense resistor can be calculated almost by inspection.

$$P_{R(SENSE)} = \left(\frac{I_{O(MAX)}}{1 - D_{MAX}}\right)^{2} \cdot R_{SENSE} \cdot D_{MAX}$$

To understand the magnitude of the improvement with this  $V_{DS}$  sensing technique, consider the 3.3V input, 5V output power supply shown in the Typical Application on the front page. The maximum load current is 7A (10A peak) and the duty cycle is 39%. Assuming a ripple current of 40%, the peak inductor current is 13.8A and the average is 11.5A. With a maximum sense voltage of about 140mV, the sense resistor value would be  $10m\Omega$ , and the power dissipated in this resistor would be 514mW at maximum

output current. Assuming an efficiency of 90%, this sense resistor power dissipation represents 1.3% of the overall input power. In other words, for this application, the use of  $V_{DS}$  sensing would increase the efficiency by approximately 1.3%.

For more details regarding the various terms in these equations, please refer to the section Boost Converter: Power MOSFET Selection.

3. The losses in the inductor are simply the DC input current squared times the winding resistance. Expressing this loss as a function of the output current yields:

$$P_{R(WINDING)} = \left(\frac{I_{O(MAX)}}{1 - D_{MAX}}\right)^2 \bullet R_W$$

4. Losses in the boost diode. The power dissipation in the boost diode is:

$$P_{DIODE} = I_{O(MAX)} \cdot V_{D}$$

The boost diode can be a major source of power loss in a boost converter. For the 3.3V input, 5V output at 7A example given above, a Schottky diode with a 0.4V forward voltage would dissipate 2.8W, which represents 7% of the input power. Diode losses can become significant at low output voltages where the forward voltage is a significant percentage of the output voltage.

5. Other losses, including  $C_{IN}$  and  $C_0$  ESR dissipation and inductor core losses, generally account for less than 2% of the total additional loss.

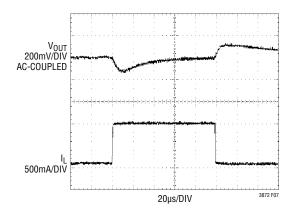

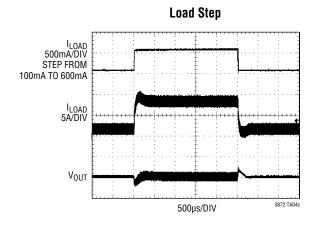

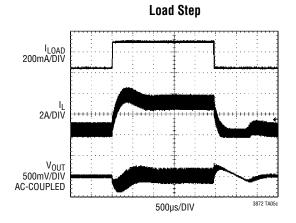

#### **Checking Transient Response**

The regulator loop response can be verified by looking at the load transient response. Switching regulators generally take several cycles to respond to an instantaneous step in resistive load current. When the load step occurs,  $V_0$  immediately shifts by an amount equal to  $(\Delta I_{LOAD})(ESR)$ , and then  $C_0$  begins to charge or discharge (depending on the direction of the load step) as shown in Figure 7. The regulator feedback loop acts on the resulting error amp output signal to return  $V_0$  to its steady-state value. During this recovery time,  $V_0$  can be monitored for overshoot or ringing that would indicate a stability problem.

Figure 7. Load Transient Response for a 3.3V Input, 5V Output Boost Converter Application, 0.1A to 1A Step

A second, more severe transient can occur when connecting loads with large (>1 $\mu$ F) supply bypass capacitors. The discharged bypass capacitors are effectively put in parallel with C<sub>0</sub>, causing a nearly instantaneous drop in V<sub>0</sub>. No regulator can deliver enough current to prevent this problem if the load switch resistance is low and it is driven quickly. The only solution is to limit the rise time of the switch drive in order to limit the inrush current di/dt to the load.

#### **Boost Converter Design Example**

The design example given here will be for the circuit shown on the front page. The input voltage is 3.3V, and the output is 5V at a maximum load current of 2A.

1. The duty cycle is:

$$D = \left(\frac{V_0 + V_D - V_{1N}}{V_0 + V_D}\right) = \frac{5 + 0.4 - 3.3}{5 + 0.4} = 38.9\%$$

2. An inductor ripple current of 40% of the maximum load current is chosen, so the peak input current (which is also the minimum saturation current) is:

$$I_{IN(PEAK)} = \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}} = 1.2 \cdot \frac{2}{1 - 0.39} = 3.9A$$

The inductor ripple current is:

$$\Delta I_{L} = \chi \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}} = 0.4 \bullet \frac{2}{1 - 0.39} = 1.3A$$

And so the inductor value is:

$$L = \frac{V_{IN(MIN)}}{\Delta I_{I} \cdot f} \cdot D_{MAX} = \frac{3.3V}{1.3A \cdot 550 \text{kHz}} \cdot 0.39 = 1.8 \mu \text{H}$$

The component chosen is a 2.2µH inductor made by Sumida (part number CEP125-H 1ROMH).

3. Assuming a MOSFET junction temperature of 125°C, the room temperature MOSFET  $R_{DS(0N)}$  should be less than:

$$R_{DS(ON)} \le V_{SENSE(MAX)} \bullet \frac{1 - D_{MAX}}{\left(1 + \frac{\chi}{2}\right)} \bullet I_{O(MAX)} \bullet \rho_{T}$$

$$= 0.175 V \bullet \frac{1 - 0.39}{\left(1 + \frac{0.4}{2}\right)} \bullet 2A \bullet 1.5$$

The MOSFET used was the Si3460, which has a maximum  $R_{DS(ON)}$  of  $27m\Omega$  at 4.5V  $V_{GS},$  a BV  $_{DSS}$  of greater than 30V, and a gate charge of 13.5nC at 4.5V  $V_{GS}.$

- 4. The diode for this design must handle a maximum DC output current of 2A and be rated for a minimum reverse voltage of  $V_{OUT}$ , or 5V. A 25A, 15V diode from On Semiconductor (MBRB2515L) was chosen for its high power dissipation capability.

- 5. The output capacitor usually consists of a lower valued, low ESR ceramic.

6. The choice of an input capacitor for a boost converter depends on the impedance of the source supply and the amount of input ripple the converter will safely tolerate. For this particular design two  $22\mu F$  Taiyo Yuden ceramic capacitors (JMK325BJ226MM) are required (the input and return lead lengths are kept to a few inches). As with the output node, check the input ripple with a single oscilloscope probe connected across the input capacitor terminals.

#### PC Board Layout Checklist

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the LTC3872. These items are illustrated graphically in the layout diagram in Figure 8. Check the following in your layout:

- 1. The Schottky diode should be closely connected between the output capacitor and the drain of the external MOSFET.

- 2. The input decoupling capacitor (0.1 $\mu$ F) should be connected closely between  $V_{IN}$  and GND.

- 3. The trace from SW to the switch point should be kept short.

- 4. Keep the switching node NGATE away from sensitive small signal nodes.

- 5. The  $V_{FB}$  pin should connect directly to the feedback resistors. The resistive divider R1 and R2 must be connected between the (+) plate of  $C_{OLIT}$  and signal ground.

Figure 8. LTC3872 Layout Diagram (See PC Board Layout Checklist)

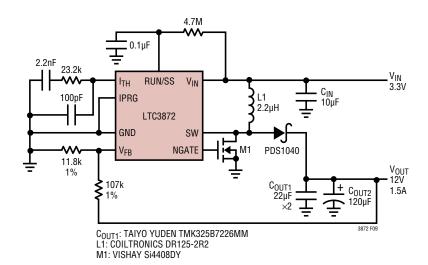

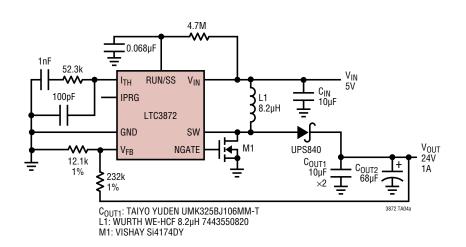

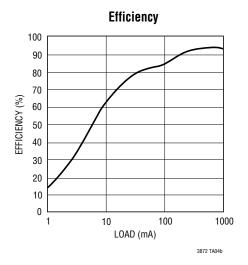

## TYPICAL APPLICATIONS

High Efficiency 3.3V Input, 12V Output Boost Converter

VOUT

12V

AC-COUPLED

5A/DIV

ILOAD

1A/DIV

STEP FROM

500mA TO 1.5A

100µs/DIV

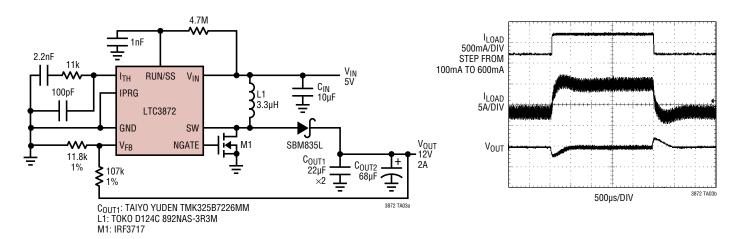

## TYPICAL APPLICATIONS

High Efficiency 5V Input, 12V Output Boost Converter

High Efficiency 5V Input, 24V Output Boost Converter

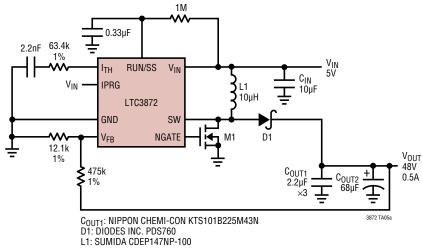

## TYPICAL APPLICATIONS

#### High Efficiency 5V Input, 48V Output Boost Converter

M1: VISHAY Si7850DP

# Soft-Start RUN/SS 5V/DIV I<sub>L</sub> 5A/DIV V<sub>OUT</sub> 20V/DIV 40ms/DIV

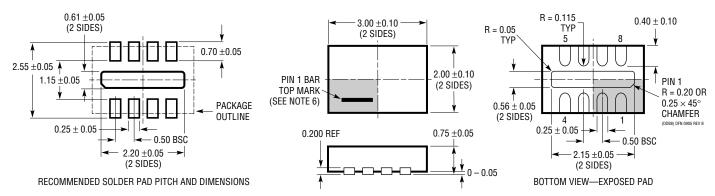

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### DDB Package 8-Lead Plastic DFN (3mm × 2mm)

(Reference LTC DWG # 05-08-1702 Rev B)

#### NOTE

- 1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE M0-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

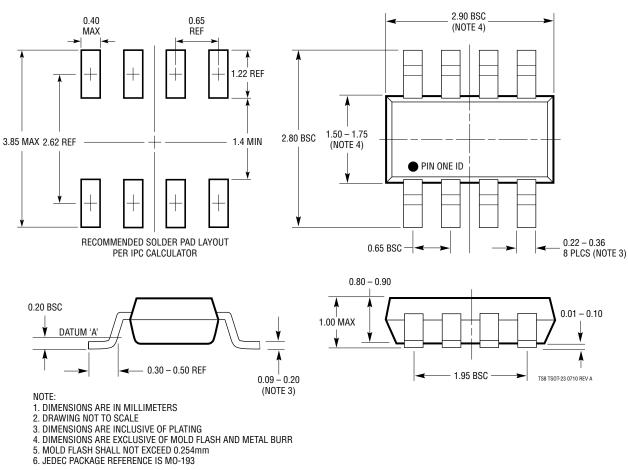

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### TS8 Package 8-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1637 Rev A)

# **REVISION HISTORY** (Revision history begins at Rev B)

| REV | DATE  | DESCRIPTION                                                                   | PAGE NUMBER    |

|-----|-------|-------------------------------------------------------------------------------|----------------|

| В   | 3/11  | Added I-Grade and H-Grade parts. Changes reflected throughout the data sheet. | 1 - 22         |

| С   | 11/13 | F <sub>OSC</sub> normal operation: changed V <sub>FB</sub> from 1.2V to 1.0V  | 3              |

|     |       | Changed Input Supply Current from 10μA to 8μA                                 | 7              |

|     |       | Updated MFG part number on Application schematics                             | 16, 17, 18, 22 |

## TYPICAL APPLICATION

#### 3.3V Input, 5V/2A Output Boost Converter

## **RELATED PARTS**

| PART NUMBER       | DESCRIPTION                                                     | COMMENTS                                                                               |

|-------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|

| LT®1619           | Current Mode PWM Controller                                     | 300kHz Fixed Frequency, Boost, SEPIC, Flyback Topology                                 |

| LTC1624           | Current Mode DC/DC Controller                                   | SO-8; 300kHz Operating Frequency; Buck, Boost, SEPIC Design; $V_{\text{IN}}$ Up to 36V |

| LTC1700           | No R <sub>SENSE</sub> Synchronous Step-Up Controller            | Up to 95% Efficiency, Operating as Low as 0.9V Input                                   |

| LTC1871-7         | Wide Input Range Controller                                     | No R <sub>SENSE</sub> , 7V Gate Drive, Current Mode Control                            |

| LTC1872/LTC1872B  | SOT-23 Boost Controller                                         | Delievers Up to 5A, 550kHz Fixed Frequency, Current Mode                               |

| LT1930            | 1.2MHz, SOT-23 Boost Converter                                  | Up to 34V Output, 2.6V V <sub>IN</sub> 16V, Miniature Design                           |

| LT1931            | Inverting 1.2MHz, SOT-23 Converter                              | Positive-to Negative DC/DC Conversion, Miniature Design                                |

| LTC3401/LTC3402   | 1A/2A 3MHz Synchronous Boost Converters                         | Up to 97% Efficiency, Very Small Solution, $0.5V \le V_{IN} \le 5V$                    |

| LTC3704           | Positive-to Negative DC/DC Controller                           | No R <sub>SENSE</sub> , Current Mode Control, 50kHz to 1MHz                            |

| LTC1871/LTC1871-7 | No R <sub>SENSE</sub> , Wide Input Range DC/DC Boost Controller | No R <sub>SENSE</sub> , Current Mode Control, 2.5V ≤ V <sub>IN</sub> ≤ 36V             |

| LTC3703/LTC3703-5 | 100V Synchronous Controller                                     | Step-Up or Step Down, 600kHz, SSOP-16, SSOP-28                                         |

| LTC3803/LTC3803-5 | 200kHz Flyback DC/DC Controller                                 | Optimized for Driving 6V MOSFETs ThinSOT                                               |