# **Head Amplifier for Digital CCD Cameras**

# **Description**

The CXA1690Q is a bipolar IC developed as a head amplifier for digital CCD cameras. The CXA1690Q provides the following functions: correlated double sampling, AGC for CCD signals, GCA for chroma signals, GCA for line signals, sample and hold for A/D converters, blanking, and reference voltage output/output driver for A/D converters.

### **Features**

- Permits higher sensitivity with a high-gain AGC amplifier

- Blanking function for the purpose of calibrating the deviation in black levels of the CCD output signals

- · Permits output offset adjustment

- Provides a regulator output pin for the reference voltage for A/D converters

- Built-in GCA that amplifies video signals (chroma and line signals) from an external source

- Built-in sample-and-hold circuits (for both camera signals and video signals) required by external A/D converters

### **Structure**

Bipolar silicon monolithic IC

# **Applications**

Digital CCD cameras

# **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>              | Vcc  | 14          | V  |

|-------------------------------------------------|------|-------------|----|

| <ul> <li>Operating temperature</li> </ul>       | Topr | -20 to +75  | °C |

| Storage temperature                             | Tstg | -65 to +150 | °C |

| <ul> <li>Allowable power dissipation</li> </ul> | Pp   | 460         | mW |

# **Operating Conditions**

Supply voltage Vcc1, 2, 3 4.5 to 5 V

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

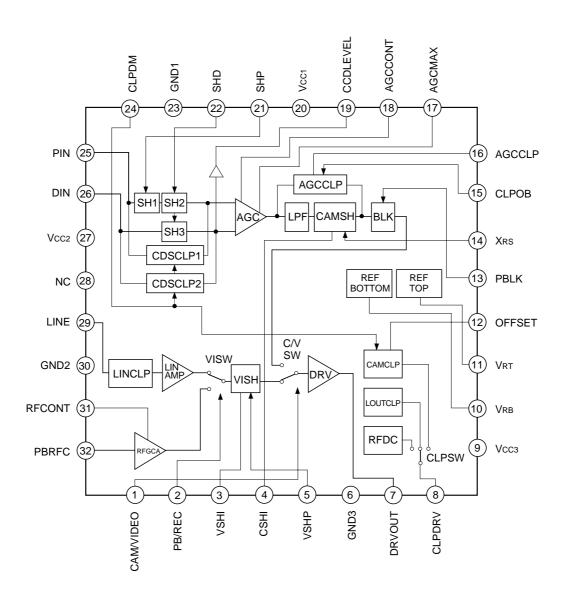

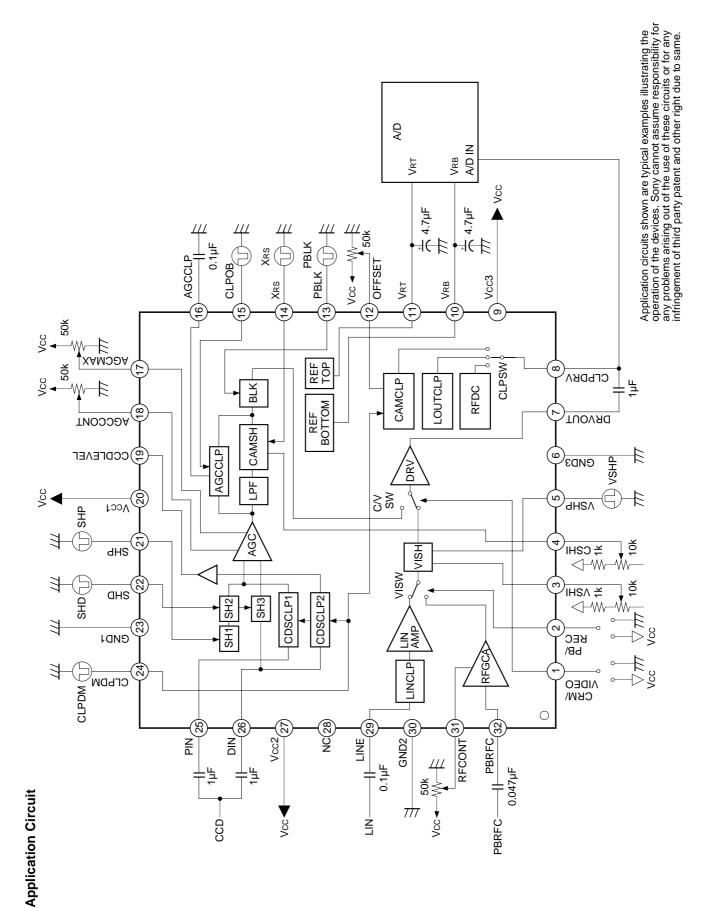

# **Block Diagram and Pin Configuration**

**Pin Description** (Vcc = 4.5V)

|               | •                    |                                                                                                                                                       |                    | ( V CC = 4.5 V )                                                                                                                                                                |  |  |

|---------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>No.    | Symbol               | Pin voltage                                                                                                                                           | Equivalent circuit | Description                                                                                                                                                                     |  |  |

| 1             | CAM<br>VIDEO         | H: Vcc<br>L: GND<br>$VTH = \frac{18}{50} Vcc$                                                                                                         | 1k ≥ 46μA 127      | Switches between CAM mode for the camera signal system and PB and LIN modes for the video signal system.  CAM VIDEO                                                             |  |  |

| 2             | PB REC               | H: Vcc<br>L: GND<br>$VTH = \frac{18}{50} Vcc$                                                                                                         | <b>1</b> 30k       | High Low  Video system Video system PB mode  CAM mode  High Low PB mode osystem PB mode PB mode PB mode PB mode PB mode                                                         |  |  |

| 3             | VSHI                 | 1.4V                                                                                                                                                  | VRT 100 ≥ 127      | This pin adjusts the slew rate when the video sample-and-hold circuit (VISH) built into the CXA1690 is sampling. Normally used open.  R = 1K: approx. +6dB; R = 5K: approx6dB   |  |  |

| 4             | CSHI                 | 1.4V                                                                                                                                                  | 3k                 | This pin adjusts the slew rate when the camera sample-and-hold circuit (CAMSH) built into the CXA1690 is sampling. Normally used open.  R = 1K: approx. +6dB; R = 5K: approx6dB |  |  |

| 5             | VSHP                 | Sampling $VTH = \frac{18}{50} VCC$                                                                                                                    | 100 ≥ 127 Typ. 2mA | Pulse input for VISH.                                                                                                                                                           |  |  |

| 6<br>23<br>30 | GND3<br>GND1<br>GND2 | GND                                                                                                                                                   |                    | Driver GND.<br>Camera signal GND.<br>Video signal GND.                                                                                                                          |  |  |

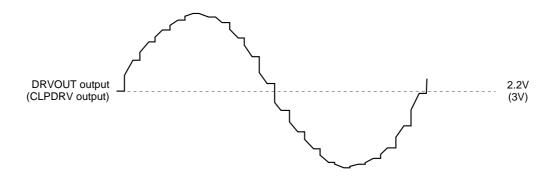

| 7             | DRVOUT               | Camera<br>system CAM<br>mode black<br>level: 1.3V<br>Video<br>system LIN<br>mode black<br>level: 1.4V<br>Video<br>system RF<br>mode DC<br>level: 2.2V | Typ. 14mA 1        | Driver output. Standard D range. Camera system signal: 870mVp-p Video system PB RFC signal: 500mVp-p Video system LIN signal: 1.4Vp-p                                           |  |  |

| Pin<br>No.    | Symbol               | Pin voltage                                                                                                                                     | Equivalent circuit                                                                    | Description                                                                                                                                                                                                                              |

|---------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8             | CLPDRV               | Camera<br>system CAM<br>mode black<br>level: 2V<br>Video<br>system LIN<br>mode clamp<br>level: 2V<br>Video<br>system PB<br>mode DC<br>level: 3V | LIN mode switch 400μ 50μ 127  7/7 7/7  CAM mode switch 78μ 157μ 86μ PB mode switch 1k | Clamps and outputs the DRVOUT (Pin 7) output signal. The switch for each mode is closed and the clamp potentials applied to this pin by selecting CAMVIDEO (Pin 1) or PBRFC (Pin 2).                                                     |

| 9<br>20<br>27 | Vcc3<br>Vcc1<br>Vcc2 | Vcc                                                                                                                                             |                                                                                       | Driver Vcc.<br>Camera signal Vcc.<br>Video signal Vcc.                                                                                                                                                                                   |

| 10            | VRB                  | 2.02V                                                                                                                                           | ₹16k<br>₹13k                                                                          | $2V$ regulator output $V_{RB} - V_{RT}$ load: $160\Omega$ or greater.  Be sure to decouple this pin near the IC pins to prevent the oscillation and external noise when this pin is not used. (Recommended capacitor value: $4.7\mu F$ ) |

| 11            | Vrt                  | 3.88V                                                                                                                                           | ₹4k<br>1.9k<br>7///<br>1.9k<br>7///<br>7///<br>7///<br>7///<br>7///<br>7///           | 4V regulator output.  Be sure to decouple this pin near the IC pins to prevent the oscillation and external noise when this pin is not used. (Recommended capacitor value: 4.7μF)                                                        |

| Pin<br>No. | Symbol | Pin voltage                     | Equivalent circuit                           | Description                                                                                                                                                                                                                                |

|------------|--------|---------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12         | OFFSET | $Vcc to \frac{20}{50} Vcc$      | 127<br>125k<br>125k<br>√ 39µA 39µA 39µA 347k | This pin offset adjusts the CLPDRV black level when the CXA1690 satisfies the operating conditions for the camera signal system (when CAMVI is High and PBREC is Low).  VCC: approx. 500mV 20/50 VCC: approx.  -50mV  Preset: approx. 70mV |

| 13         | PBLK   | $V_{TH} = \frac{18}{50} V_{CC}$ | 62k ₹ 46μA 127 ★ 7/17 7/17 7/17 7/17         | Pulse input for BLK (active: Low). This pin functions only when CAMVI is High and PBREC is Low, and calibrates the black level of the AGC output waveform. When the pulse is low, the DRVOUT potential is forced to 2V.                    |

| 14         | XRS    | $V_{TH} = \frac{22}{50} V_{CC}$ | ≥ 200                                        | High-speed S/H pulse input for CAMSH (active: Low).                                                                                                                                                                                        |

| 21         | SHP    | $V_{TH} = \frac{25}{50} V_{CC}$ | 127                                          | High-speed S/H pulse input for SH1 (active: Low).                                                                                                                                                                                          |

| 22         | SHD    | Sampling                        | ₹ 200<br>777                                 | High-speed S/H pulse input for SH2 and SH3 (active: Low).                                                                                                                                                                                  |

| 15         | CLPOB  | $V_{TH} = \frac{18}{50} V_{CC}$ | 1k ₹ 100µ                                    | Clamp pulse input for AGCCLP (active: Low).                                                                                                                                                                                                |

| Pin<br>No. | Symbol       | Pin voltage                                             | Equivalent circuit                                                        | Description                                                                                                    |

|------------|--------------|---------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 16         | AGCCLP       | Approx. 2.8V                                            | 127<br>41μA<br>32k<br>777<br>777                                          | Capacitor connection for AGCCLP clamping. 0.1 to 1µF                                                           |

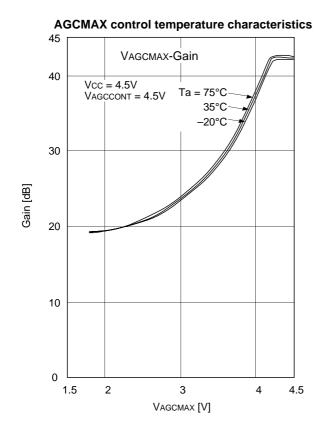

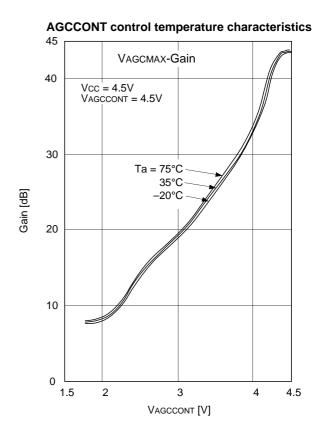

| 17         | AGCMAX       | Vcc to $\frac{20}{50}$ Vcc                              | 127<br>127<br>15k<br>15k<br>15k<br>7/7/ 7/7/ 7/7/ 7/7/ 7/7/ 7/7/ 7/7/ 7/7 | AGC amplifier MAX gain adjustment.                                                                             |

| 18         | AGCCONT      | Vcc to $\frac{20}{50}$ Vcc                              | 300  127  4k  20k  38.4k  20.5µ  20.5µ  20.5µ  20.5µ  20.5µ  20.5µ        | AGC amplifier gain adjustment. MIN GAIN for $\frac{20}{50}$ Vcc, MAX GAIN for Vcc for both AGCMAX and AGCCONT. |

| 19         | CCD<br>LEVEL | DIN input<br>CCD signal<br>black level:<br>approx. 2.6V | 260µ <b>1</b>                                                             | CCD level detector                                                                                             |

| Pin<br>No. | Symbol     | Pin voltage                         | Equivalent circuit                                   | Description                      |

|------------|------------|-------------------------------------|------------------------------------------------------|----------------------------------|

| 24         | CLPDM      | $V_{TH} = \frac{18}{50} V_{CC}$     | 127<br>127<br>127<br>127<br>127<br>127<br>127<br>127 | Clamp pulse input (active: Low). |

| 25         | PIN<br>DIN | Black level:<br>approx. 2.6V        | 86µ                                                  | CCD signal input.                |

| 29         | LINE       | Clamp<br>potential:<br>approx. 2.5V | 3µ 200µ 100µ                                         | LIN signal input.                |

| Pin<br>No. | Symbol | Pin voltage                | Equivalent circuit                                 | Description         |

|------------|--------|----------------------------|----------------------------------------------------|---------------------|

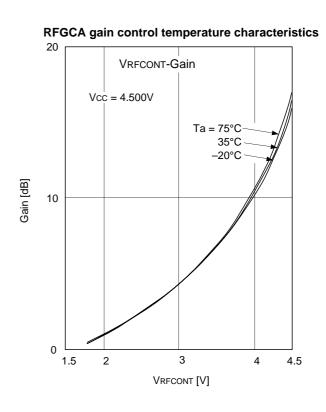

| 31         | RFCONT | Vcc to $\frac{20}{50}$ Vcc | 127<br>42k<br>100μ \$ 52k                          | RFGCA gain control. |

| 32         | PBRFC  | approx. 2.8V               | 127<br>10k ₹ 100μ 100μ<br>7/7 10k 7/7<br>10k ₹ 41k | PBRFC signal input. |

# **Electrical Characteristics**

$(Ta = 25^{\circ}C, VCC1, 2, 3 = 4.5V)$

| It               | tem                         | Symbol        | Conditions                                                                               | Min.       | Тур. | Max. | Unit |

|------------------|-----------------------------|---------------|------------------------------------------------------------------------------------------|------------|------|------|------|

| Current          | Camera<br>mode              | IDC           | CAM/VIDEO = 4.5V, PB/RFC = 0V                                                            | _          | 49   | 62   |      |

| consump-<br>tion | LINE mode                   | IDL           | CAM/VIDEO = 0V, PB/RFC = 4.5V                                                            | _          | 33   | 42   | mA   |

|                  | RF mode                     | Idr           | CAM/VIDEO = 4.5V, PB/RFC = 4.5V                                                          | _          | 33   | 42   |      |

|                  | AGCCONT max.                | A CONmax.     | AGCMAX = 4.5V, AGCCONT = 4.5V                                                            | 40         | 43   |      |      |

|                  | AGCCONT min.                | A CONmin.     | AGCMAX = 4.5V, AGCCONT = 1.8V                                                            | _          | 7.8  | 10   | - dB |

|                  | AGCMAX min.                 | A MAXmin.     | AGCMAX = 1.8V, AGCCONT = 4.5V                                                            | _          | 19   | 21   | ub   |

| AGC              | Amount of variation in gain | AGC G         | A CONmaxA CONmin.                                                                        | 32         | 35   | 1    |      |

|                  | Dynamic range max.          | AGCmax. D     | AGCMAX = 4.5V, AGCCONT = 4.5V<br>Level at which the CLPOUT output<br>signal is saturated | 1.9        | 2.05 | _    | V    |

|                  | Dynamic range min.          | AGCmin. D     | AGCMAX = 4.5V, AGCCONT = 1.8V<br>Level at which the CLPOUT output<br>signal is saturated | 1.9        | 2.05 | _    | V    |

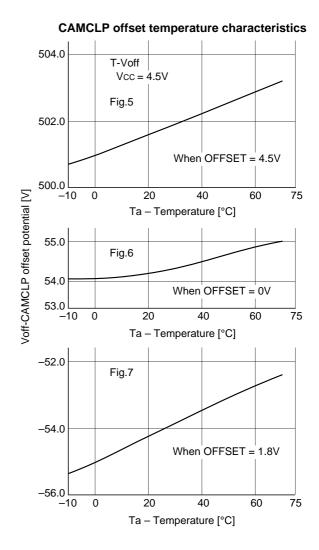

|                  | Offset High                 | CAOF high     | OFFSET = 4.5V                                                                            | 440        | 490  | _    |      |

| CAMCLP           | Offset Low                  | CAOF low      | OFFSET = 1.8V                                                                            | _          | -65  | -30  | mV   |

|                  | Offset<br>Preset            | CAOF pre      | OFFSET = 0V                                                                              | 13         | 43   | 73   |      |

|                  | VRT DC<br>level             | VRTO          | With $200\Omega$ load                                                                    | 3.66       | 3.86 | 4.06 |      |

| REF              | VRB DC<br>level             | VRBO          | With $200\Omega$ load                                                                    | 1.88       | 2.03 | 2.18 | V    |

|                  | VRT – VRB                   | ΔVR           | With $200\Omega$ load                                                                    | 1.73       | 1.83 | 1.93 |      |

| BLK              | Offset                      | BLKOF         | BLKOF (BLK = 4.5V)<br>- BLKOF (BLK = 0V)                                                 | <b>-</b> 5 | 7    | 15   | mV   |

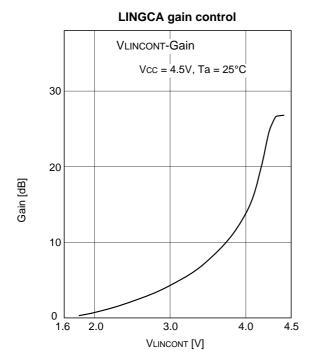

| LINGCA           | Gain                        | LIN G         | Adjust the DC level so that LIN input = 15kHz, 500mVp-p sine wave LINCLP.                | 8.5        | 9.5  | 10.5 |      |

| RFGCA            | RF CONT max.                | RF<br>CONmax. | RFCONT = 4.5V, 15kHz, 80mVp-p sine wave                                                  | 14         | 17   | _    | dB   |

| NI OOA           | RF CONT min.                | RF<br>CONmin. | RFCONT = 1.8V, 15kHz, 400mVp-p sine wave                                                 | _          | 0.5  | 2    |      |

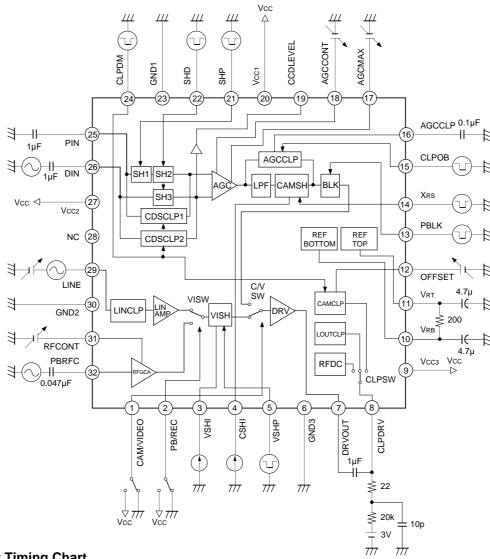

# **Electrical Characteristics Measurement Circuit**

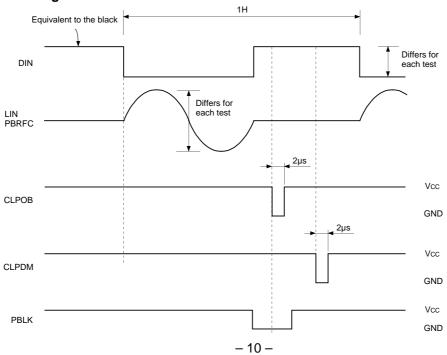

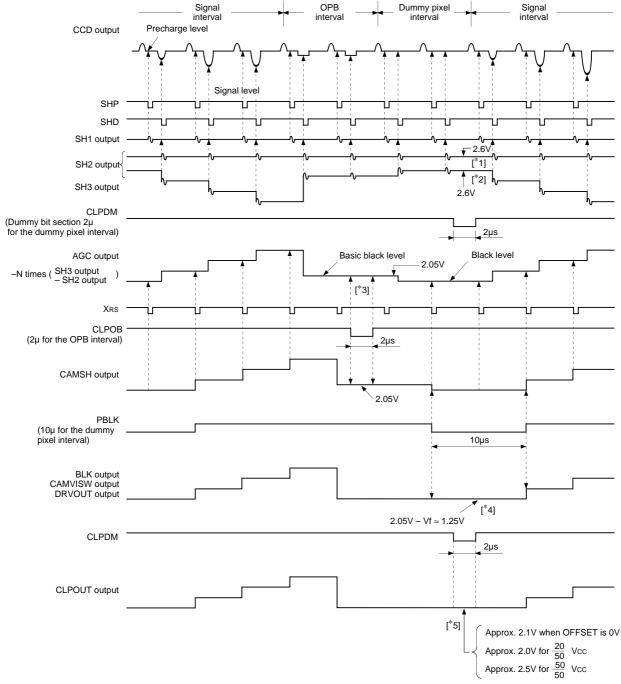

# **Measurement Timing Chart**

# **Description of Operation**

# 1. Camera signal processing system

Process the video signal processing pins as follows only in camera mode.

<5> VSHP ... Connect to GND.

<29> LINE ... Connect to GND via the capacitor (approx. 0.01µF).

<31> RFCONT ... Connect to GND.

<32> PBRFC ... Connect to GND via the capacitor (approx. 0.01µF).

# **Operating conditions**

The camera signal processing system operates when CAM/VIDEO is High, and PB/REC is Low.

# **Camera Signal Processing System Timing Chart**

### CDS:

The CCD signal from the CCD image sensor enters PIN and DIN where it is correlated double sampled (CDS: Correlated Double Sampling) by SH1, SH2 and SH3. The precharge level of the CCD output signal is sampled-and-held and output by the SH2 output, and the signal level is sampled-and-held and output by the SH3 output.

### CDSCLP:

The CDSCLP stabilizes the DC level of the input signal, clamps (CLPDM) the input signal during the dummy pixel interval for the purpose of eliminating the AGC input offset, and combines the DC level ([\*1], [\*2]) of SH2 and SH3.

### AGC:

The gain can be varied with the AGCMAX and AGCCONT voltage control (20/50) Vcc to Vcc. The maximum gain can be varied from 19 to 43dB for AGCMAX, and from 7.9 to 43dB for AGCCONT.

### LPF:

A primary low-pass filter has been installed for the purpose of eliminating unused bands and white noise and improving S/N.

### CAMSH:

The CAMSH is used for camera system signal processing. It is a sample-and-hold circuit which synchronizes the data read-in timing for the external A/D. The slew rate of the input signal for the sample-and-hold circuit can be controlled by adjusting the input current to the CSHI pin.

### AGCCLP:

The basic black level is set ([\*3]) by clamping it with the CLPOB clock during the OPB interval of the AGC output waveform. The capacitance for AGCCLP is connected to the AGCCLP pin.

### BLK:

The black level is calibrated by blanking the black level signal of the AGC output waveform so that it does not fall below the basic black level and replacing the DC potential. ([\*4])

The signal is blanked when PBLK is low.

### C/VSW:

When the CAM/VIDEO and PB/REC pin voltages are set so that the camera signal processing system operates, C/VSW leads the BLK output (camera signal) into the DRV. In addition, when these voltages are set so that the video signal processing system operates, C/VSW leads the VISH output (video signal) into the DRV.

### CLPSW:

By selecting the CAM/VIDEO and PB/REC pin voltages, either [CAMCLP] is connected and lead into the CLPDRV pin as the clamp for the output signal of the camera signal processing system, or [LOUTCLP] as the clamp for the LIN mode output signal or [RFDC] as the DC shift for the PBREC mode output signal of the video signal processing system.

### DRV:

DRV drives the external A/D. RF mode or LIN mode signals for either the camera or video signals are input to the DRV and output from DRVOUT by switching C/VSW.

### CAMCLP:

The signal black level interval is clamped by the CLPDM clock to bring camera system signals within the allowable input voltage range for the external A/D, and the signals are output to CLPOUT. ([\*5]) In addition, the CAMCLP contains an OFFSET control pin which adjusts the CLP potential for the purpose of compensating the clamp level difference generated by the DRV.

### REFBOTTOM, REFTOP:

REFBOTTOM and REFTOP are reference voltage source for the external A/D. They are connected to VRB and VRT, and supply 2V and 4V to the A/D.

### 2. Video signal processing system

# **Operating conditions**

The video signal processing system has two modes: LIN signal mode and PBREC signal mode.

The video signal processing system operates in LIN signal mode when CAM/VIDEO is Low, and PB/REC is High.

The video signal processing system operates in PBREC signal mode when PB/REC is High.

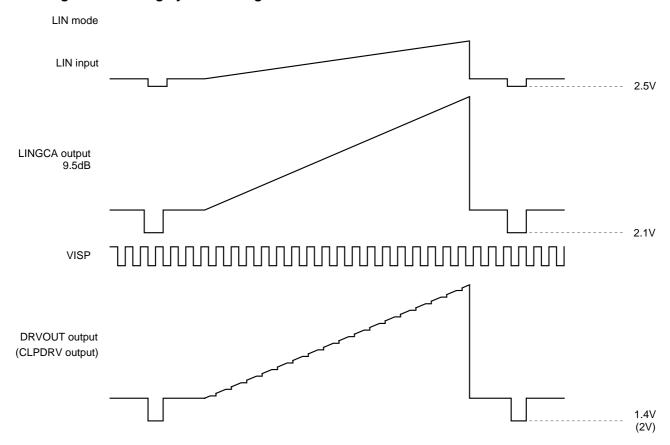

# **Video Signal Processing System Timing Chart**

# LIN signal mode

### LINCLP:

The video signal enters the LIN pin. LINCLP sync tip clamps the input signal to allow full input. The input signal level and frequency are respectively 500mVp-p (typ.) and DC up to approx. 7MHz.

# LINAMP:

This is a 9.5dB gain amplifier.

### VISW:

VISW switches between the LIN signal and PBRFC signal for the video signal processing system. The signals are switched according to the input conditions of the CAM/VIDEO and PB/REC pins.

### VISH:

The VISH is used for video signal processing system. It is a sample-and-hold circuit which synchronizes the data read-in timing for the external A/D. The slew rate of the input signal for the sample-and-hold circuit can be controlled by adjusting the input current to VSHI.

# LOUTCLP:

LOUTCLP is a clamp circuit which operates when the LIN signal is output by the DRV. The clamp potential is 2V.

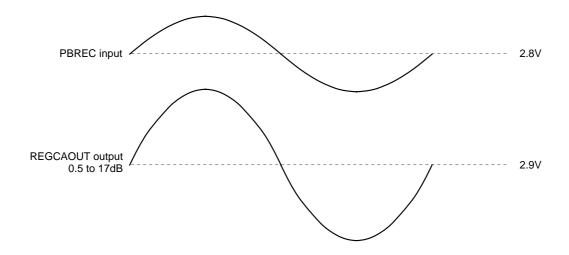

# **PBREC** signal mode

# RFGCA:

This is an amplifier which controls the gain of the video chroma RF signal input to PBRFC. The RFCONT voltage can be varied from (20/50) Vcc to Vcc, enabling the gain to be varied from 0.5 to 17dB.

The input signal level and frequency are respectively 200mVp-p (typ.) and DC up to approx. 1.5MHz.

### RFDC:

RFDC is a DC bias circuit which operates when the PBREC signal is output by the DRV. The DC bias potential is 3V.

# **PBREC** mode

# **Example of Representative Characteristics**

# AGC dynamic range temperature characteristics 2200 Drange-T 10dB dynamic range {VAGCMAX = 4.5V VAGCCONT = 1.8V} 40dB dynamic range {VAGCMAX = 4.5V VAGCCONT = 4.5V VAGCCON

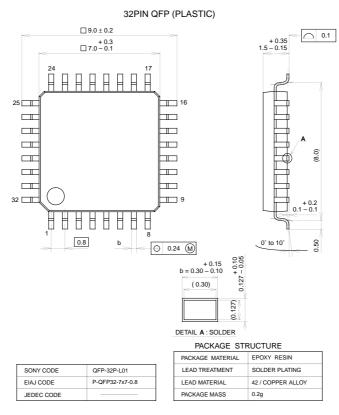

# Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

# LEAD PLATING SPECIFICATIONS

EIAJ CODE

JEDEC CODE

| ITEM               | SPEC.           |

|--------------------|-----------------|

| LEAD MATERIAL      | 42 ALLOY        |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |

| PLATING THICKNESS  | 5-18µm          |

P-QFP32-7x7-0.8

LEAD MATERIAL

PACKAGE MASS

42 / COPPER ALLOY

0.2g