# plerow<sup>™</sup> APL0093.19-R/T

### PLL Synthesizer Module

### **Features**

- · 7dBm Output Level at 93.19 MHz

- · Channel Step Size : 10 kHz

- · 2<sup>nd</sup> Harmonic: < -20dBc

- · Spurious Level: < -65dBc

- Lock Time : < 10 ms</li>

- · 35mA Current Consumption

### **Specifications**

### Description

The plerow<sup>™</sup> PLL synthesizer module was designed for use in wireless and wireline systems in a wide range of frequency from 50 MHz to 6 GHz. ASB's PLL provides exceptionally low spurious and phase noise performance with fast locking time and low current consumption. All products are available in a surface-mount type package.

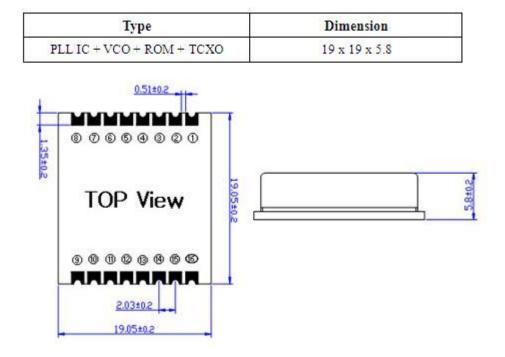

#### Parameter Unit Min. Typical Max. MHz 93.19 Frequency Range **Output Power** dBm 5 7 Supply Voltage V 4.75 5 5.25 **Current Consumption** mΑ 25 35 **Channel Step Size** 10 2<sup>nd</sup> Harmonics dBc -25 -20 Spurious Level dBc -70 -65 Lock Time ms 3 10 MHz **Reference Frequency** 13 **Reference Input Level** dBm Phase Noise (C / N) @ 1 kHz -84 -78 @ 10 kHz dBc/Hz -108 -103 @ 100 kHz -120 -115 **Output Impedance** Ω 50 Operating Temp. Range °C -40 25 80 Package Type & Size mm SMT, 19.0W×19.0L×5.8H

### **More Information**

Website: www.asb.co.kr E-mail: sales@asb.co.kr

Tel: (82) 42-528-7220 Fax: (82) 42-528-7222

ASB Inc., 4th Fl. Venture Town Bldg., 367-17 Goijeong-Dong, Seo-Gu, Daejeon 302-716, Korea

1) Measurement conditions are as follows: T = 25°C, V\_{CC} = 5 V, Freq. = 93.19MHz, 50 ohm system.

2) Frequency stability of internal ref. TCXO is +/- 2.5 ppm (max.) over the operating temperature range.

## plerow<sup>™</sup> APL0093.19-R/T

PLL Synthesizer Module

### **Outline Drawing**

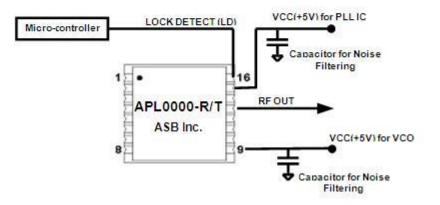

### APL0000-R/T Type

| Pin Out for PLL |             |         |             |

|-----------------|-------------|---------|-------------|

| Pin No.         | Application | Pin No. | Application |

| 1               | GROUND      | 9       | VCC (VCO)   |

| 2               | GROUND      | 13      | RF OUT      |

| 3               | GROUND      | 15      | VCC (PLL)   |

| 4               | GROUND      | 16      | LOCK DETECT |