# KHTEK DA1196 - Digital to Audio Converter 24Bit, 192KHz 6-Channel

## **General Description**

DA1196 is a digital to analog converter especially designed to work with MPEG2/AC-3 decoded data in applications such as, DVD player, home theater, set-top box, and digital TV, etc. DA1196 integrates 6 DA channels providing customers a solution of both simplicity and excellent performance.

## **Features**

#### **High Resolution:**

■ 16/18/20/24/32 Bit Selectable

#### **High Performance:**

Sampling Rate: 8KHz ~ 192KHz

THD+N: -98 dB

Dynamic Range: 104dB S/N Ratio: 104dB

Channel Separation: 107dB

#### **High Integration:**

- 6 Audio Channels, each contains:

- Oversampling Digital Filter

- High-Resolution Delta Sigma DAC

- Analog Low Pass Filter

- Output Amplifier

#### **High Versatility**

- Control via 3-Wire Interface or Hardware Pins

- Left/Right-justified or IIS Format Selectable

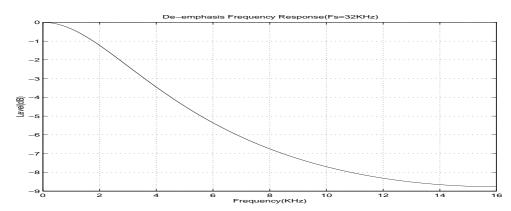

- Selectable De-emphasis Sampling Rate:

- 32KHz, 44.1KHz, 48KHz

- Selectable Multiple Functions:

- Soft Mute

- Attenuation

- De-emphasis

- Zero Detection On/Off Control

- Selectable Output Operation Mode:

- Left, Right, Stereo, Mono, or Mute

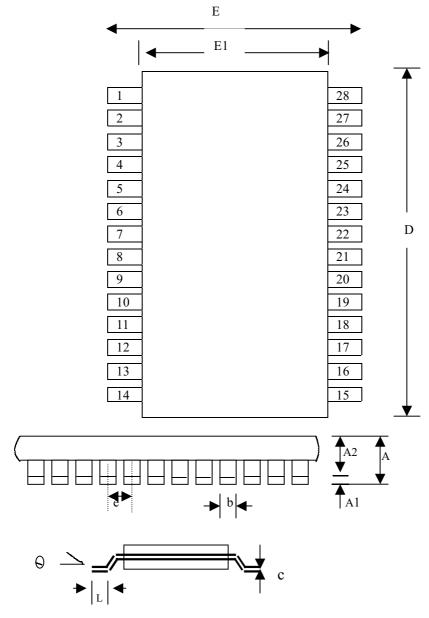

### 28 Pin SSOP Package

## **Pin Configuration**

|    |        |        | 1  |

|----|--------|--------|----|

| 1  | VDD    | VCC1   | 28 |

| 2  | SCKI   | VOUTR1 | 27 |

| 3  | BCKIN  | AGND   | 26 |

| 4  | SRCIN  | VOUTL1 | 25 |

| 5  | DIN1   | AGND1  | 24 |

| 6  | DIN2   | VOUTR2 | 23 |

| 7  | DIN3   | AGND   | 22 |

| 8  | MODE   | VOUTL2 | 21 |

| 9  | MUTE   | AGND2  | 20 |

| 10 | NC     | VOUTR3 | 19 |

| 11 | DGND   | AGND   | 18 |

| 12 | ML/I2S | VOUTL3 | 17 |

| 13 | MC/IWL | CAP    | 16 |

| 14 | MD     | VCC2   | 15 |

|    |        |        |    |

OCT, 2002 KHTEK DA1196

## **Pin Assignments**

| Pin | Name   | I/O | Description                                                            |  |

|-----|--------|-----|------------------------------------------------------------------------|--|

| 1   | VDD    | PWR | Digital Power Supply                                                   |  |

| 2   | SCKI   | IN  | Crystal Oscillator Input or External Master/System Clock Input         |  |

| 3   | BCKIN  | IN  | Bit Clock Input for Audio Data                                         |  |

| 4   | SRCIN  | IN  | Sample Rate Clock Input                                                |  |

| 5   | DIN1   | IN  | Audio Data Input to DAC1                                               |  |

| 6   | DIN2   | IN  | Audio Data Input to DAC2                                               |  |

| 7   | DIN3   | IN  | Audio Data Input to DAC3                                               |  |

| 8   | MODE   | IN  | Mode Control, "0" = Software Mode; "1" = Hardware Mode.                |  |

| 9   | MUTE   | IN  | Mute Control, Active "High". To Mute, Pull this Pin High.              |  |

| 10  | NC     |     | Not Connected (Don't Care)                                             |  |

| 11  | DGND   | GND | Digital Ground                                                         |  |

| 12  | ML/I2S | IN  | Latch for Serial Control in Software Mode or Input Format Selection in |  |

|     |        |     | Hardware Mode.                                                         |  |

| 13  | MC/IWL | IN  | Clock for Serial Control Data in Software Mode or Input Word Length    |  |

|     |        |     | Selection in Hardware Mode.                                            |  |

| 14  | MD     | IN  | Serial Control Data in Software Mode.                                  |  |

| 15  | VCC2   | PWR | Analog Power                                                           |  |

| 16  | CAP    | 1   | Analog Common Mode Pin                                                 |  |

| 17  | VOUTL3 | OUT | L-Channel Output from DAC3                                             |  |

| 18  | AGND   | GND | Analog Ground                                                          |  |

| 19  | VOUTR3 | OUT | R-Channel Output from DAC3                                             |  |

| 20  | AGND2  | GND | Analog Ground                                                          |  |

| 21  | VOUTL2 | OUT | L-Channel Output from DAC2                                             |  |

| 22  | AGND   | GND | Analog Ground                                                          |  |

| 23  | VOUTR2 | OUT | R-Channel Output from DAC2                                             |  |

| 24  | AGND1  | GND | Analog Ground                                                          |  |

| 25  | VOUTL1 | OUT | L-Channel Output from DAC1                                             |  |

| 26  | AGND   | GND | Analog Ground                                                          |  |

| 27  | VOUTR1 | OUT | R-Channel Output from DAC1                                             |  |

| 28  | VCC1   | PWR | Analog Power                                                           |  |

#### Note:

- 1. All digital input pins have Schmitt triggers and internal pull-up resistors except the SCKI pin and MUTE pin, which have internal pull-down resistors.

- 2. Logic high is denoted as either "H" or "1"; logic low is denoted as either "L" or "0" in this document.

## **Absolute Maximum Rating**

| Power Supply Voltage        | + 6.5V                   |

|-----------------------------|--------------------------|

| +VCC to VDD Difference      | +/- 0.1V                 |

| Input Logic Voltage         | -0.3V to (VDD + $0.3V$ ) |

| Power Dissipation           | 600mW                    |

| Operating Temperature Range | -25 C to +85 C           |

| Storage Temperature         | -55 C to +125 C          |

### **ESD Sensitive Device**

Although DA1196 is furnished with KHTEK's proprietary ESD protection circuitry, proper ESD precaution is still recommended to avoid performance degradation or permanent damage.

## **Package Information**

| Model  | Package     | Package Drawing No. |

|--------|-------------|---------------------|

| DA1196 | 28 pin SSOP | 128 -SS             |

Package drawing is at the end of this data sheet

## **Specifications**

Electrical Characteristics:

At 25 °C, VCC1=VCC2=VDD=5V/3.3V, fs=48kHz, 24Bit input data, System Clock = 384/256fs.

| Parameter                            | Conditions                                    | Min          | Туре                  | Max        | Unit       |

|--------------------------------------|-----------------------------------------------|--------------|-----------------------|------------|------------|

| Sampling Frequency                   |                                               | 8            | 48                    | 192        | KHz        |

| Carata and Clark Francisco           |                                               |              |                       |            |            |

| System Clock Frequency               | 128fs                                         | 1.024        | 6.144                 | 24.5760    | MHz        |

|                                      | 192fs                                         | 1.536        | 9.216                 | 36.8640    | MHz        |

|                                      | 256fs                                         | 2.048        | 12.288                | 49.1520    | MHz        |

|                                      | 384fs                                         | 3.072        | 18.432                | 73.7280    | MHz        |

|                                      | 512fs                                         | 4.096        | 24.576                |            | MHz        |

|                                      | 768fs                                         | 6.144        | 36.864                |            | MHz        |

| Audio Data Format                    | Selectable                                    |              | Right/                |            |            |

|                                      |                                               |              | Left/I <sup>2</sup> S |            |            |

| Data Bit Length                      | Selectable                                    |              | 16/20/24/32           |            | Bits       |

| Power Supply                         |                                               |              | _                     |            |            |

| Voltage Range: VCC1, VCC2, VDD       | VCC1=VCC2=VDD=5V<br>VCC1=VCC2=VDD=3.3V        | 4.5<br>3.0   | 5<br>3.3              | 5.5<br>3.7 | V<br>V     |

| @fs=44.1KHz                          | VCC1-VCC2-VDD-3.5V                            | 3.0          | 3.3                   | 3.7        | V          |

| Supply Current: ICC1+ICC2+IDD        | VCC1=VCC2=VDD=5V                              |              | 68                    |            | mA         |

| Supply Cultent, ICC1+ICC2+IDD        | VCC1=VCC2=VDD=3.3V                            |              | 43                    |            | mA         |

| Power Dissipation:                   | VCC1=VCC2=VDD=5V                              |              | 340                   |            | mW         |

|                                      | VCC1=VCC2=VDD=3.3V                            |              | 142                   |            | mW         |

| @fs=96KHz                            |                                               |              |                       |            |            |

| Supply Current: ICC1+ICC2+IDD        | VCC1=VCC2=VDD=5V                              |              | 75                    |            | mA         |

|                                      | VCC1=VCC2=VDD=3.3V                            |              | 48                    |            | mA         |

| Power Dissipation:                   | VCC1=VCC2=VDD=5V                              |              | 375                   |            | mW         |

| 1                                    | VCC1=VCC2=VDD=3.3V                            |              | 158                   |            | mW         |

| Digital Input/Output                 |                                               |              |                       |            |            |

| Input Logic Level                    | VCC1=VCC2=VDD                                 |              |                       |            |            |

| Vih                                  | Pin2                                          | 40%          |                       |            | VDD        |

| VIL                                  | Din 2 4 5 6 7 9 0 12 12 14                    | <b>50</b> 0/ |                       | 16%        | VDD        |

| VIH                                  | Pin 3,4,5,6,7,8,9,12,13,14<br>Schmitt Trigger | 52%          |                       |            | VDD        |

| VIL                                  | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2       |              |                       | 16%        | VDD        |

| Output Logic Level                   | VCC1=VCC2=VDD                                 | 000/         |                       |            |            |

| Vон                                  |                                               | 90%          |                       | 4.007      | VDD        |

| VOL                                  |                                               |              |                       | 10%        | VDD        |

| DC Accuracy                          |                                               |              |                       | . , -      | 0/865      |

| Gain Error                           |                                               |              | +/- 1                 | +/- 3      | %FSR       |

| Gain Mismatch Ch to Ch               |                                               |              | +/- 1                 | +/- 2      | %FSR       |

| Analog Output                        |                                               |              | VCC, VDD              |            |            |

| Walte as Danas                       | VO ID                                         |              | 5V 3.3V               |            | <b>1</b> 7 |

| Voltage Range                        | Vout=0dB                                      |              | 1.0 0.66              |            | Vrms       |

| Center Voltage                       | AC Lood                                       | 10           | 2.5   1.65            |            | V<br>V Ohm |

| Load Impedance<br>Frequency Response | AC Load                                       | 10<br>0      |                       | 20         | KOhm       |

| rrequency Kesponse                   |                                               | U            |                       | 20         | KHz        |

## **Electrical Characteristics:(Cont.)**

At 25 °C, VCC1=VCC2=VDD=5V/3.3V, fs=48kHz, 24Bit input data, System Clock = 384/256fs.

| Parameter           | Conditions       | Min | Тур  | е    | Max  | Unit |

|---------------------|------------------|-----|------|------|------|------|

| Dynamic Performance |                  |     | VCC, | VDD  |      |      |

| @fs=48KHz           |                  |     | 5V   | 3.3V |      |      |

| THD+N at FS(0dB)    | Fout=1kHz        |     | -98  | -97  | -100 | dB   |

| THD+N at -60dB      | Fout=1kHz        |     | -44  | -42  | -46  | dB   |

| Dynamic Range       | EIAJ, A-weighted | 100 | 104  | 102  | 106  | dB   |

| SNR                 | EIAJ, A-weighted | 100 | 104  | 102  | 106  | dB   |

| Channel Separation  | Fout=1kHz        | 105 | 107  | 105  | 110  | dB   |

| @fs=96KHz           |                  |     |      |      |      |      |

| THD+N at FS(0dB)    | Fout=1kHz        |     | -98  | -97  | -100 | dB   |

| THD+N at -60dB      | Fout=1kHz        |     | -43  | -41  | -45  | dB   |

| Dynamic Range       | EIAJ, A-weighted | 98  | 103  | 101  | 105  | dB   |

| SNR                 | EIAJ, A-weighted | 98  | 103  | 101  | 105  | dB   |

| Channel Separation  | Fout=1kHz        | 103 | 105  | 103  | 108  | dB   |

| @fs=192KHz          |                  |     |      |      |      |      |

| THD+N at FS(0dB)    | Fout=1kHz        |     | -97  | -96  | -100 | dB   |

| THD+N at –60dB      | Fout=1kHz        |     | -42  | -39  | -43  | dB   |

| Dynamic Range       | EIAJ, A-weighted | 98  | 102  | 99   | 103  | dB   |

| SNR                 | EIAJ, A-weighted | 98  | 102  | 99   | 103  | dB   |

| Channel Separation  | Fout=1kHz        | 100 | 102  | 100  | 105  | dB   |

## **Timing Characteristics:**

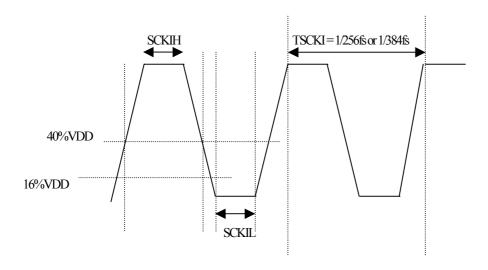

## **SCKI/Master Clock Input Timing:**

## **Timing Parameter**

| Parameter             | Symbol | Value | Unit |

|-----------------------|--------|-------|------|

| Master Clock Timing   |        |       |      |

| SCKI clock high level | SCKIH  | >10   | ns   |

| SCKI clock low level  | SCKIL  | >10   | ns   |

At 25°C, VCC=VDD=5V/3.3V, fs=48kHz, 24Bit input data, System Clock = 384/256fs

### **Timing Diagram**

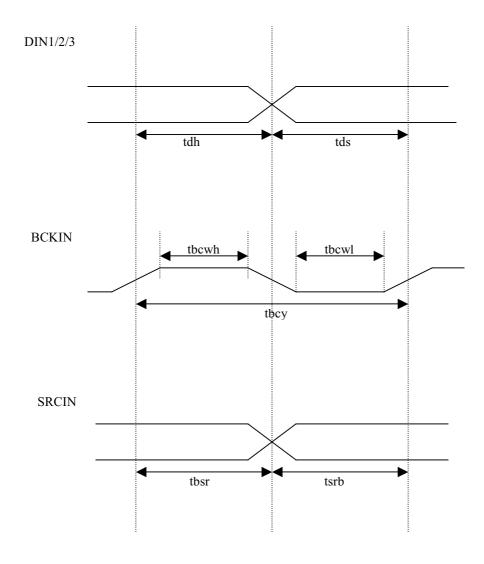

## **Data Input Timing:**

## **Timing Parameter:**

| Parameter                   | Symbol       | Value | Unit |

|-----------------------------|--------------|-------|------|

| Data Input Timing           |              |       | ·    |

| DIN setup time              | tds          | >30   | ns   |

| DIN hold time               | tdh          | >30   | ns   |

| BCKIN high-level, low-level | tbcwh, tbcwl | >50   | ns   |

| BCKIN pulse cycle time      | tbcy         | >100  | ns   |

| BCKIN rising edge to SRCIN  | tbsr         | >30   | ns   |

| SRCIN to BCKIN rising edge  | tsrb         | >30   | ns   |

At 25°C, VCC=VDD=5V/3.3V, fs=48kHz, 24Bit input data, System Clock = 384/256fs

## **Timing Diagram**

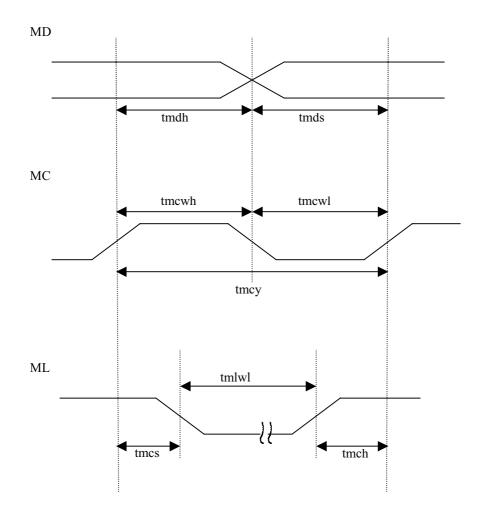

## 3 Wire Serial Mode Control Timing:

## **Timing Parameter:**

| Parameter                           | Symbol       | Value    | Unit |

|-------------------------------------|--------------|----------|------|

| Serial Mode Control Timing          |              |          | ·    |

| MC pulse high-level, low-level      | tmcwh, tmcwl | >50      | ns   |

| MC pulse cycle time                 | tmcy         | >100     | ns   |

| MD setup time                       | tmds         | >30      | ns   |

| MD hold time                        | tmdh         | >30      | ns   |

| ML setup time                       | tmcs         | >30      | ns   |

| ML hold time                        | tmch         | >30      | ns   |

| ML pulsewidth high-level, low-level | tmlwh, tmlwl | >30+1/fs | ns   |

At 25°C, VCC=VDD=5V/3.3V, fs=48kHz, 24Bit input data, System Clock = 384/256fs

## **Timing Diagram**

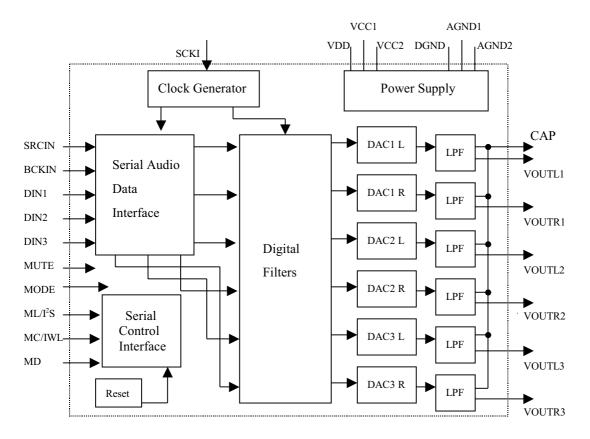

## **Functional Description**

## **Functional Block Diagram**

## **System Clock**

The system clock must be 128fs, 192fs, 256fs, 384fs, 512fs, or 768fs, where fs is the standard audio frequency including 32KHz, 44.1KHz, 48KHz, 96KHz, or 192KHz. The system clock can be input via SCKI (pin2) from an external clock and is used to operate the digital filter and delta sigma modulator. The system clock should be synchronized with SRCIN (pin4) – sampling rate clock. If the phase difference between them becomes greater than 6 bit BCKIN (pin3), the synchronization will be automatically performed and at this time the analog outputs are forced to VCC/2 by the chip.

**Table-1 System Clock and Sampling Rate**

| Sampling Rate | te System Clock Frequency (MHz) |         |                        |             |                        |                        |

|---------------|---------------------------------|---------|------------------------|-------------|------------------------|------------------------|

| fs            | 128 fs                          | 192 fs  | 256fs                  | 384fs       | 512fs                  | 768fs                  |

| 32KHz         | 4.0960                          | 6.1440  | 8.1920                 | 12.2880     | 16.3840 (1)            | 24.5760 (1)            |

| 44.1KHz       | 5.6448                          | 8.4670  | 11.2896                | 16.9340     | 22.5792 (1)            | 33.8688 <sup>(1)</sup> |

| 48KHz         | 6.1440                          | 9.2160  | 12.2880                | 18.4320     | 24.5760 (1)            | 36.8640 (1)            |

| 96KHz         | 12.2880                         | 18.4320 | 24.5760                | 36.8640     | 49.1520 (1)            | 73.7280 (1)            |

| 192KHz        | 24.5760                         | 36.8640 | 49.1520 <sup>(1)</sup> | 73.7280 (1) | 98.3040 <sup>(2)</sup> | 147.456 <sup>(2)</sup> |

<sup>(1)</sup> For these sampling rate and system clock conditions, the SC1 bit of **Reg9** should be set to "0"; and the SC0 bit of **Reg9** should be set to "1".

<sup>(2)</sup> For these sampling rate and system clock conditions, the SC1 bit of **Reg9** should be set to "1"; and the SC0 bit of **Reg9** should be set to "1".

## **Serial Digital Audio Data Input Interface**

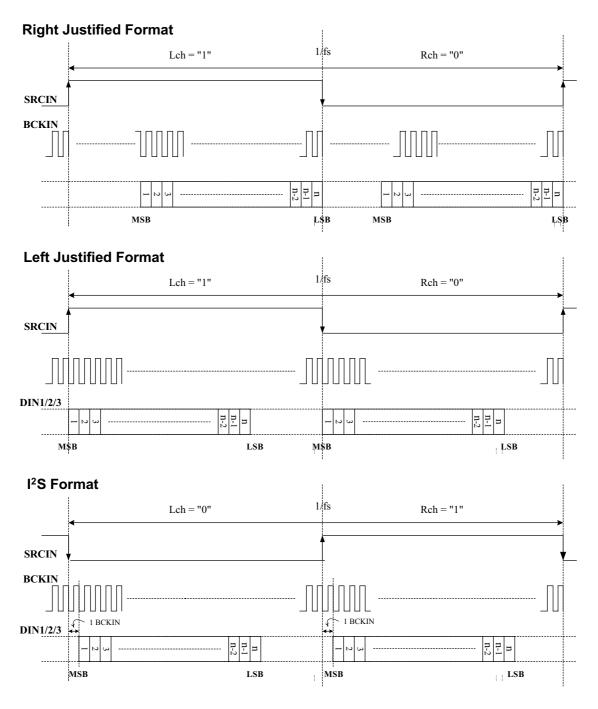

The digital audio information is applied to DA1196 via DIN1/2/3 (pin 5, 6, 7) for audio data input, via SRCIN (pin 4) for sampling rate clock, and via BCKIN (pin 3) for bit clock. The DA1196 supports right justified, left justified, and I<sup>2</sup>S data formats. All data formats are MSB first and two's complement. Both left justified format and I<sup>2</sup>S format support word length from 16 Bit to 32 Bit, but the right justified format supports word length only up to 24 Bit. The I<sup>2</sup>S data format, which is compatible with Philips serial data protocol, is left justified and one bit clock delay between SRCIN and data MSB. The relationship of the three audio input signals, DIN, SRCIN, and BCKIN is illustrated in the following figures for three formats:

Note: 1. Logic high is denoted as either "H" or "1"; logic low is denoted as either "L" or "0" in this document.

2. With IIS format, the word length can go up to 32 Bit as long as the SRCIN period can accommodate.

### **Multi-Functions & Mode Control**

DA1196 can operate in two different control modes – serial (software) or parallel (hardware). Which mode to operate is selected by MODE pin (pin8) and is illustrated in following table:

**Table-2 Serial/Parallel Selection**

| MODE (pin8) | Selected Mode               | Selected Pins                      |

|-------------|-----------------------------|------------------------------------|

| Low         | Serial (or Software) Mode   | MD (pin14), MC (pin13), ML (pin12) |

| High        | Parallel (or Hardware) Mode | IWL (pin13), I2S (pin12)           |

### Hardware (Parallel) Mode Control, MODE="1"

When MODE pin (pin8) is set to "1", DA1196 is in hardware mode; the logic levels set on the hardware pins – pin9, pin12, pin13, and pin14 control a few functions implemented in the DA1196 for hardware mode.

A logic "0" on MUTE pin (pin 9) allows for a normal operation; but a logic "1" on MUTE pin (pin 9) would force the outputs to be soft muted.

**Table-3 Selectable Mute Function**

| MUTE (pin 9) | Mute Function |

|--------------|---------------|

| 0            | OFF           |

| 1            | ON            |

$I^2S$  (pin12) and IWL (pin13) together can be used to obtain different input data format and word length. The proper settings are shown in the following table:

**Table-4 Selectable Input Data Formats**

| Input Data Format    | <b>I</b> <sup>2</sup> <b>S</b> (pin12) | IWL (pin13) |

|----------------------|----------------------------------------|-------------|

| Normal Format -16Bit | 0                                      | 0           |

| Normal Format -20Bit | 0                                      | 1           |

| Normal Format -24Bit | 1                                      | 0           |

| $I^2S$               | 1                                      | 1           |

The De-emphasis function is not available in hardware mode. That is, in hardware mode the MD (pin14) becomes a NC pin and can be connected either to ground or power.

**Table-5 De-emphasis Function**

| MD (pin14) | De-emphasis |

|------------|-------------|

| 0          | OFF         |

| 1          | OFF         |

### Software (Serial) Mode Control, MODE="0"

DA1196 provides several built-in functions in software (serial) mode, such as digital attenuation, de-emphasis, output control, and soft mute. Following **Table-6** shows the selectable functions and their default conditions:

**Table-6 Selectable Functions**

| Function                                   | Selections                                           | Default         |

|--------------------------------------------|------------------------------------------------------|-----------------|

| Digital Audio Input Format Selection       | Right Justified, Left Justified, or I <sup>2</sup> S | Right Justified |

| Input Audio Data Word Length               | 16-bit, 20-bit, 24-bit, or 32-bit                    | 24bit           |

| BCKIN Polarity Selection                   | Sample on Rising Edge or Falling Edge                | On Rising Edge  |

| Digital Attenuation for each channel       | 0dB ~ Mute                                           | 0dB             |

| Master Digital Attenuation of all channels | 0dB ~ Mute                                           | 0dB             |

| Soft Mute Control                          | ON or OFF                                            | OFF             |

| De-emphasis Control                        | ON or OFF                                            | OFF             |

| De-emphasis Sample Rate Selection          | OFF, 32KHz, 48kHz, or 44.1KHz                        | OFF             |

| Modulator Over-sampling Selection          | 32X, 64X, or 128X                                    | 64X             |

| Analog Output Control                      | L, R, Mono, Stereo, or Mute                          | Stereo          |

| Analog Output Reverse Control              | OUT1L/R, OUT2L/R, OUT3L/R, or                        | OUTXL/R         |

|                                            | OUT1R/L, OUT2R/L, OUT3R/L                            | X=1, 2, 3       |

| DAC Operation Control                      | Operate or Disabled                                  | Operated        |

| Infinite Zero Detection Control            | Enabled or Disabled                                  | Not Detected    |

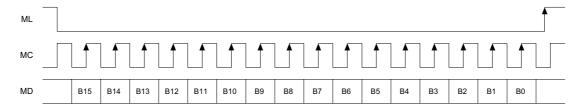

These implemented functions are controlled via a 3-wire serial interface, namely, MD (pin14) is input pin for control data, MC (pin13) is input pin for control clock, and ML (pin12) is for control latch.

### **Control Data Input**

The chip has ten 16-bit internal registers for programming and shown as below. In order to use all the built-in functions that DA1196 provides, the ten registers must be addressed via the three -wire interface using MD (pin 14), MC (pin 13), and ML (pin 12) ten separate times to set all desired register values.

#### **Ten Internal Registers**

| Reg | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8   | В7   | В6   | В5   | В4   | В3   | B2   | В1   | В0   |

|-----|-----|-----|-----|-----|-----|-----|----|------|------|------|------|------|------|------|------|------|

| 0   | Res | Res | Res | A3  | A2  | A1  | A0 | LDL1 | L1A7 | L1A6 | L1A5 | L1A4 | L1A3 | L1A2 | L1A1 | L1A0 |

| 1   | Res | Res | Res | A3  | A2  | A1  | A0 | LDR1 | R1A7 | R1A6 | R1A5 | R1A4 | R1A3 | R1A2 | R1A1 | R1A0 |

| 2   | Res | Res | Res | A3  | A2  | A1  | A0 | PL3  | PL2  | PL1  | PL0  | IZD  | ATC  | OPE  | DEM  | MUT  |

| 3   | Res | Res | Res | A3  | A2  | A1  | A0 | PRV2 | PRV1 | PRV0 | IW1  | IW0  | ВСР  | Res  | FM1  | FM0  |

| 4   | Res | Res | Res | A3  | A2  | A1  | A0 | LDL2 | L2A7 | L2A6 | L2A5 | L2A4 | L2A3 | L2A2 | L2A1 | L2A0 |

| 5   | Res | Res | Res | A3  | A2  | A1  | A0 | LDR2 | R2A7 | R2A6 | R2A5 | R2A4 | R2A3 | R2A2 | R2A1 | R2A0 |

| 6   | Res | Res | Res | A3  | A2  | A1  | A0 | LDL3 | L3A7 | L3A6 | L3A5 | L3A4 | L3A3 | L3A2 | L3A1 | L3A0 |

| 7   | Res | Res | Res | A3  | A2  | A1  | A0 | LDR3 | R3A7 | R3A6 | R3A5 | R3A4 | R3A3 | R3A2 | R3A1 | R3A0 |

| 8   | Res | Res | Res | A3  | A2  | A1  | A0 | LDS  | SA7  | SA6  | SA5  | SA4  | SA3  | SA2  | SA1  | SA0  |

| 9   | Res | Res | Res | A3  | A2  | A1  | A0 | Res  | Res  | SC1  | SC0  | Res  | SF1  | SF0  | MC1  | MC0  |

Following Table-7 describes in detail the functions controlled by each register bit:

**Table-7 Register Mapping**

|        |                 | T       |                                                                     |                          |          |                                     |                        |  |  |  |

|--------|-----------------|---------|---------------------------------------------------------------------|--------------------------|----------|-------------------------------------|------------------------|--|--|--|

|        | Register name   |         | Function Attenuation Control of DAC1 Left Channel                   |                          |          |                                     |                        |  |  |  |

| Reg0   | <u> </u>        |         |                                                                     |                          | DAC1     | Left Channel                        |                        |  |  |  |

| B12~B9 | A3, A2, A1, A0  | _       |                                                                     |                          |          |                                     |                        |  |  |  |

|        |                 | To acco | ess <b>Re</b> ç                                                     | <b>10</b> , set <i>A</i> | 3="0 "   | , A2="0", A1="0", A0                | ="0".                  |  |  |  |

| B8     | LDL1            |         |                                                                     |                          |          | on Data Load Control.               | <del></del>            |  |  |  |

|        |                 | When 1  | When LDL1="0", the attenuation data L1A7~L1A0 are loaded but do not |                          |          |                                     |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | DL1="1". That is when               |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | ne previous attenuation le          |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | ut level becomes affected           |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | L and R channel attenuate           |                        |  |  |  |

|        |                 |         |                                                                     | neously                  |          |                                     |                        |  |  |  |

| B7~B0  | L1A7~L1A0       |         |                                                                     |                          |          | on Data.                            |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | 1A[7:0]/256)dB.                     |                        |  |  |  |

| Reg1   | I.              |         |                                                                     |                          |          | Right Channel                       |                        |  |  |  |

| B12~B9 | A3, A2, A1, A0  |         |                                                                     |                          |          |                                     |                        |  |  |  |

|        | 110,112,111,110 | _       |                                                                     |                          | 3="0 "   | , A2="0", A1="0", A0                | ="1"                   |  |  |  |

| B8     | LDR1            |         |                                                                     |                          |          | tion Data Load Control              |                        |  |  |  |

|        | LDKI            |         |                                                                     |                          |          | tion data R1A7~R1A0                 |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | 1="1". That is when LDR             |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | ne previous attenuation le          |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | put level becomes affecte           |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | l ", the L and R channel a          |                        |  |  |  |

|        |                 |         |                                                                     | neously.                 |          | , une is and ix channel a           | activation data occome |  |  |  |

| B7~B0  | R1A7~R1A0       |         |                                                                     |                          |          | tion Data.                          |                        |  |  |  |

| B1 B0  | KIA/~KIA0       |         | _                                                                   |                          |          | 1A[7:0]/256)dB.                     |                        |  |  |  |

| Reg2   |                 |         |                                                                     | nction C                 |          | IA[7.0]/230)ub.                     |                        |  |  |  |

|        | A2 A2 A1 A0     |         |                                                                     |                          | onuoi    |                                     |                        |  |  |  |

| B1Z~B9 | A3, A2, A1, A0  |         |                                                                     |                          | 2_22055  | A 2-220% A 1-22122 A 0-             | "0"                    |  |  |  |

| B8~B5  | PL3 ~ PL0       | 10 acc  | Ontrod                                                              | 12, set <i>P</i>         | 3=0,     | A2="0", A1="1", A0=                 | 0.                     |  |  |  |

| D0~D3  | PL3 ~ PL0       |         |                                                                     | Mode S                   | 1        | <del>-</del>                        | D.1 (                  |  |  |  |

|        |                 | PL3     | PL2                                                                 | PL1                      | PL0      | Lch (pin17, 21, 25)                 | Rch (pin19, 23, 27)    |  |  |  |

|        |                 | 0       | 0                                                                   | 0                        | 0        | Mute                                | Mute                   |  |  |  |

|        |                 | 0       | 0                                                                   | 0                        | 1        | L                                   | Mute                   |  |  |  |

|        |                 | 0       | 0                                                                   | 1                        | 0        | R                                   | Mute                   |  |  |  |

|        |                 | 0       | 0                                                                   | 1                        | 1        | (L+R)/2                             | Mute                   |  |  |  |

|        |                 | 0       | 1                                                                   | 0                        | 0        | Mute                                | L                      |  |  |  |

|        |                 | 0       | 1                                                                   | 0                        | 1        | L                                   | L                      |  |  |  |

|        |                 | 0       | 1                                                                   | 1                        | 0        | R                                   | L                      |  |  |  |

|        |                 | 0       | 1                                                                   | 1                        | 1        | (L+R)/2                             | L                      |  |  |  |

|        |                 | 1       | 0                                                                   | 0                        | 0        | Mute                                | R                      |  |  |  |

|        |                 | 1       | 0                                                                   | 0                        | 1        | L                                   | R                      |  |  |  |

|        |                 | 1       | 0                                                                   | 1                        | 0        | R                                   | R                      |  |  |  |

|        |                 | 1       | 0                                                                   | 1                        | 1        | (L+R)/2                             | R                      |  |  |  |

|        |                 | 1       | 1                                                                   | 0                        | 0        | ` ′                                 | (L+R)/2                |  |  |  |

|        |                 | 1       | 1                                                                   |                          |          | Mute                                | ` ′                    |  |  |  |

|        |                 | 1       | 1                                                                   | 0                        | 1        | L                                   | (L+R)/2                |  |  |  |

|        |                 | 1       | 1                                                                   | 1                        | 0        | R (I + P) /2                        | (L+R)/2                |  |  |  |

| D4     | 170             | 1       | 17. *                                                               | 1                        |          | (L+R)/2                             | (L+R)/2                |  |  |  |

| B4     | IZD             |         |                                                                     |                          |          | it Control.                         |                        |  |  |  |

| D2     | ATC             |         |                                                                     |                          | oiea; iZ | D="0" disabled.                     |                        |  |  |  |

| B3     | ATC             |         | ator Co                                                             |                          | ra.03 *  | DamA 104[70] . D                    | A 1 T 2 A F7 03 '      |  |  |  |

|        |                 |         |                                                                     |                          |          | <b>Reg0</b> , L2A[7:0] in <b>Re</b> |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | enuation data for both left         |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | ctively; and R1A[7:0] in I          |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | nored. When ATC="0", 1              |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | ] in <b>Reg6</b> are used as the    |                        |  |  |  |

|        |                 |         |                                                                     |                          |          | DAC3; and R1A[7:0] in <b>F</b>      |                        |  |  |  |

|        |                 |         |                                                                     | [7:0] in                 | Reg7 a   | re for right channels of Da         | AC1, DAC2, and         |  |  |  |

|        |                 | DAC3.   |                                                                     |                          |          |                                     |                        |  |  |  |

|        |                 |         |                                                                     |                          |          |                                     |                        |  |  |  |

|        | echnology In   | c. Preliminary Specifications |                                                                             |                    |              |             |              |                  |         |

|--------|----------------|-------------------------------|-----------------------------------------------------------------------------|--------------------|--------------|-------------|--------------|------------------|---------|

| B2     | OPE            | Left and                      | Right D                                                                     | AC Opera           | tion Cont    | <u>rol</u>  |              |                  |         |

|        |                | When Ol                       | When OPE="'0", the device is in normal operation; when OPE="1", outputs are |                    |              |             |              |                  |         |

|        |                | forced to                     | orced to VCC/2 and all registers hold at the present states.                |                    |              |             |              |                  |         |

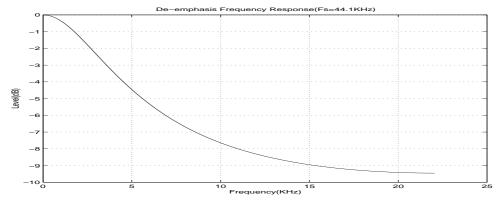

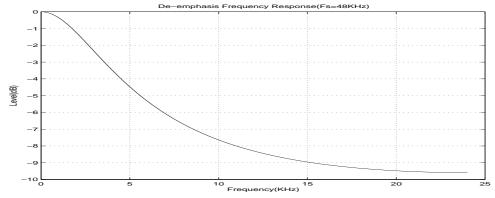

| B1     | DEM            |                               | e-emphasis Control.                                                         |                    |              |             |              |                  |         |

|        |                |                               | EM="0", de-emphasis OFF; DEM="1", de-emphasis ON.                           |                    |              |             |              |                  |         |

| B0     | MUT            |                               | -                                                                           | _                  | i i , BEIII  | 1,400       | присы с      | 7111             |         |

|        | IVICI          |                               | eft and Right Soft Mute.                                                    |                    |              |             |              |                  |         |

| Dow2   |                |                               | MUT="0", Mute OFF; MUT="1", Mute ON.  OAC Interface Control                 |                    |              |             |              |                  |         |

| Reg3   | 1.2.2.1.1.0    |                               |                                                                             |                    |              |             |              |                  |         |

| B12~B9 | A3, A2, A1, A0 |                               |                                                                             |                    |              |             |              |                  |         |

|        |                |                               | o access <b>Reg3</b> , set A3="0", A2="0", A1="1", A0="1".                  |                    |              |             |              |                  |         |

| B8~B6  | PRV2~PRV0      | Analog (                      | <u>Output P</u>                                                             | hase Cont          |              | 1           | 1            | 1                | ı       |

|        |                |                               |                                                                             | DAC1 L             | DAC1 R       | DAC2 L      | DAC2 R       | DAC3 L           | DAC3 R  |

|        |                | PRV2                          | 0                                                                           | -                  | -            | -           | -            | -                | -       |

|        |                | PRV2                          | 1                                                                           | -                  | -            | -           | -            | Reverse          | Reverse |

|        |                | PRV1                          | 0                                                                           | -                  | -            | -           | -            | -                | -       |

|        |                | PRV1                          | 1                                                                           | -                  | -            | Reverse     | Reverse      | -                | _       |

|        |                | PRV0                          | 0                                                                           | -                  | _            | -           | -            | -                | -       |

|        |                | PRV0                          | 1                                                                           | Reverse            | Reverse      |             | _            | _                | -       |

| B5~B4  | IW1,IW0        |                               | ord Lone                                                                    | gth Selection      |              | _           | _            | _                | _       |

| D3~D4  | 1 W 1,1 W U    | _                             |                                                                             |                    |              | 1.          |              |                  |         |

|        |                | IW1                           | IW0                                                                         | Inpu               | Word Le      | ngtn        |              |                  |         |

|        |                | 0                             | 0                                                                           |                    | 16 bit       |             |              |                  |         |

|        |                | 0                             | 1                                                                           |                    | 20 bit       |             |              |                  |         |

|        |                | 1                             | 0                                                                           |                    | 24 bit       |             |              |                  |         |

|        |                | 1                             | 1                                                                           |                    | 32 bit       |             |              |                  |         |

| B3     | BCP            | Bit Cloc                      | k Polarit                                                                   | y Selectio         | n            |             |              |                  |         |

|        |                |                               |                                                                             |                    |              | sampled o   | n the risin  | g edge of        | BCKIN;  |

|        |                |                               |                                                                             |                    |              |             | n the fallin |                  |         |

| B2     | Res            |                               |                                                                             | ould be set        |              | 1           |              | <u> </u>         |         |

| B1~B0  | FM1~FM0        |                               |                                                                             | nat Selecti        |              |             |              |                  |         |

|        | 11111 11110    | FM1                           | FM0                                                                         |                    | Interface I  | Format      |              |                  |         |

|        |                |                               |                                                                             |                    |              |             |              |                  |         |

|        |                | 0                             | 0                                                                           |                    | ght justifie |             |              |                  |         |

|        |                | 0                             | 1                                                                           | L                  | eft justifie | a           |              |                  |         |

|        |                | 1                             | 0                                                                           |                    | $I^2S$       |             |              |                  |         |

|        |                | 1                             | 1                                                                           |                    | Reserved     |             |              |                  |         |

| Reg4   | T              |                               |                                                                             | trol of DA         | C2 Left C    | hannel.     |              |                  |         |

| B12~B9 | A3, A2, A1, A0 |                               |                                                                             |                    |              |             |              |                  |         |

|        |                |                               |                                                                             |                    |              |             | "0", A0="    | 0".              |         |

| B8     | LDL2           |                               |                                                                             | nel Attenu         |              |             |              |                  |         |

|        |                | When L                        | DL2="0                                                                      | ", the atter       | nuation da   | ta L2A7~l   | L2A0 are l   | loaded but       | do not  |

|        |                | affect th                     | e output                                                                    | level until        | LDL2="1      | l". That is | when LD      | L2="0", tl       | ne left |

|        |                | channel o                     | output lev                                                                  | el remains         | at the previ | ous attenua | ation level; | and when         |         |

|        |                | LDL2="                        | 1", the le                                                                  | ft channel o       | utput level  | becomes a   | ffected by   | L2A7~L2 <i>A</i> | ۸0.     |

|        |                |                               |                                                                             |                    |              |             | annel attent |                  |         |

|        |                | effective                     | simultane                                                                   | eously.            |              |             |              |                  |         |

| B7~B0  | L2A7~L2A0      |                               |                                                                             | nel Atteni         | ation Dat    | a.          |              |                  |         |

|        |                |                               |                                                                             | l = 20*log         |              |             |              |                  |         |

| Reg5   |                |                               |                                                                             | trol of DA         |              |             |              |                  |         |

|        | A3, A2, A1, A0 |                               |                                                                             |                    | C2 ragin     | CHAINICI.   |              |                  |         |

| J.2 50 | A3, A2, A1, A0 |                               |                                                                             |                    | 0" A 2="1    | " ^1="      | )", A0="1"   | ,                |         |

| B8     | LDR2           |                               |                                                                             |                    |              |             |              | •                |         |

| 50     | LDR2           |                               |                                                                             | annel Atter        |              |             |              | 1004-41-4        | do ==+  |

|        |                |                               |                                                                             |                    |              |             | R2A0 are     |                  |         |

|        |                |                               |                                                                             |                    |              |             | en LDR2='    |                  | IL      |

|        |                |                               |                                                                             |                    |              |             | ation level; |                  |         |

|        |                |                               |                                                                             |                    |              |             | affected by  |                  |         |

|        |                |                               |                                                                             |                    | o "1", the I | L and R cha | annel attent | uation data      | become  |

|        |                |                               | simultane                                                                   |                    |              |             |              |                  |         |

| B7~B0  | R2A7~R2A0      |                               |                                                                             | <u>annel Attei</u> |              |             |              |                  |         |

|        |                |                               |                                                                             | $l = 20*\log$      |              |             |              |                  |         |

| Reg6   |                | Attenuat                      | tion Con                                                                    | trol of DA         | C3 Left C    | hannel.     |              |                  |         |

| B12~B9 | A3, A2, A1, A0 | Register                      | Address                                                                     | <u>S.</u>          |              |             |              |                  |         |

|        |                |                               |                                                                             |                    | 0 ", A2="    | 1 ", A1="   | 1", A0="0    | ".               |         |

|        |                |                               |                                                                             |                    |              |             |              |                  |         |

| KasH T     | echnology In | C.    |      |   |   |   | Preli | minary | /S | pecifications |

|------------|--------------|-------|------|---|---|---|-------|--------|----|---------------|

| <b>D</b> 0 |              | . ~ ~ | <br> | • | _ | - | . ~   |        |    |               |

| KasH T | echnology In   | C.                                                                                      |                                                                                                                                                      | Prelimii                               | nary Specifications       |  |  |  |

|--------|----------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------|--|--|--|

| B8     | LDL3           |                                                                                         | eft Chann                                                                                                                                            | nel Attenuation Data Load Contro       |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | the attenuation data L3A7~L3A(         |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | evel until LDL3="1". That is whe       |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | I remains at the previous attenuation  |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | channel output level becomes affecte   |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | R3 is set to "1", the L and R channel  |                           |  |  |  |

|        |                | effective s                                                                             |                                                                                                                                                      |                                        | attendation data become   |  |  |  |

| B7~B0  | L3A7~L3A0      |                                                                                         |                                                                                                                                                      |                                        |                           |  |  |  |

| B1~B0  | L3A/~L3A0      |                                                                                         | DAC3 Left Channel Attenuation Data.                                                                                                                  |                                        |                           |  |  |  |

| D7     |                | Attenuation level = 20*log (L3A[7:0]/256)dB. Attenuation Control of DAC3 Right Channel. |                                                                                                                                                      |                                        |                           |  |  |  |

| Reg7   | 1.2.12.11.10   |                                                                                         |                                                                                                                                                      |                                        |                           |  |  |  |

| B12~B9 | A3, A2, A1, A0 | Register Address.                                                                       |                                                                                                                                                      |                                        |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | set A3="0", A2="1", A1="1", A          |                           |  |  |  |

| B8     | LDR3           |                                                                                         |                                                                                                                                                      | nnel Attenuation Data Load Contr       |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | , the attenuation data R3A7~R3A        |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | rel until LDR3="1". That is when LD    |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | l remains at the previous attenuation  |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | nt channel output level becomes affect |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | R3 is set to "1", the L and R channel  | attenuation data become   |  |  |  |

|        |                | effective s                                                                             | simultanec                                                                                                                                           | ously.                                 |                           |  |  |  |

| B7~B0  | R3A7~R3A0      | DAC3 R                                                                                  | ight Char                                                                                                                                            | nnel Attenuation Data.                 |                           |  |  |  |

|        |                | Attenuati                                                                               | on level                                                                                                                                             | $= 20*\log (R3A[7:0]/256)dB.$          |                           |  |  |  |

| Reg8   |                | Simultan                                                                                | eous Atte                                                                                                                                            | enuation Control for All Channels      |                           |  |  |  |

| B12~B9 | A3, A2, A1, A0 |                                                                                         |                                                                                                                                                      |                                        |                           |  |  |  |

|        | ,,             | To access <b>Reg8</b> , set A3="1", A2="0", A1="0", A0="0".                             |                                                                                                                                                      |                                        |                           |  |  |  |

| B8     | LDS            |                                                                                         |                                                                                                                                                      | enuation Data Load Control.            | , , ,                     |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      |                                        | t the output level of all |  |  |  |

|        |                |                                                                                         | When LDS="0", the attenuation data are loaded but the output level of all channels remain at the previous attenuation level until LDS is set to "1". |                                        |                           |  |  |  |

|        |                | When LDS="1", all channels output levels become affected by SA7~SA0.                    |                                                                                                                                                      |                                        |                           |  |  |  |

| B7~B0  | SA7~SA0        | Simultaneous Attenuation Data for All Channels.                                         |                                                                                                                                                      |                                        |                           |  |  |  |

|        | 5717 5710      |                                                                                         |                                                                                                                                                      | $= 20*\log (SA[7:0]/256)dB.$           |                           |  |  |  |

| Reg9   |                |                                                                                         |                                                                                                                                                      | on Control                             |                           |  |  |  |

| B12~B9 | A2 A2 A1 A0    |                                                                                         |                                                                                                                                                      |                                        |                           |  |  |  |

| D1Z~D9 | A3, A2, A1, A0 |                                                                                         |                                                                                                                                                      |                                        | \?; 1 ??                  |  |  |  |

| DO     | D              |                                                                                         |                                                                                                                                                      | set A3="1", A2="0", A1="0", A0         | )= 1 .                    |  |  |  |

| B8     | Res            |                                                                                         |                                                                                                                                                      | uld be set to "0".                     |                           |  |  |  |

| B6~B5  | SC1 ~ SC0      | System C                                                                                |                                                                                                                                                      |                                        |                           |  |  |  |

|        |                | SC1                                                                                     | SC0                                                                                                                                                  | System Clock                           |                           |  |  |  |

|        |                | 0                                                                                       | 0                                                                                                                                                    | SCKI ÷ 1                               |                           |  |  |  |

|        |                | 0                                                                                       | 1                                                                                                                                                    | SCKI ÷ 2                               |                           |  |  |  |

|        |                | 1                                                                                       | 0                                                                                                                                                    | SCKI ÷ 2                               |                           |  |  |  |

|        |                | 1                                                                                       | 1                                                                                                                                                    | SCKI ÷ 4                               |                           |  |  |  |

| B3~B2  | SF1 ~ SF0      | De-emph                                                                                 | asis Sam                                                                                                                                             | pling Rate Selection.                  |                           |  |  |  |

|        |                | SF1                                                                                     | SF0                                                                                                                                                  | De-emphasis Sampling Rate              |                           |  |  |  |

|        |                | 0                                                                                       | 0                                                                                                                                                    | Reserved                               |                           |  |  |  |

|        |                | 0                                                                                       | 1                                                                                                                                                    | 32kHz group                            |                           |  |  |  |

|        |                | 1                                                                                       | 0                                                                                                                                                    | 48kHz group                            |                           |  |  |  |

|        |                |                                                                                         |                                                                                                                                                      | Ŭ 1                                    |                           |  |  |  |

| D1~D0  | MC1 MC0        | l<br>Madulati                                                                           | 1                                                                                                                                                    | 44.1kHz group                          |                           |  |  |  |

| B1~B0  | MC1 ~ MC0      |                                                                                         |                                                                                                                                                      | ampling Control.                       |                           |  |  |  |

|        |                | MC1                                                                                     | MC0                                                                                                                                                  | Modulator Over-sampling Rate           |                           |  |  |  |

|        |                | 0                                                                                       | 0                                                                                                                                                    | 64X                                    |                           |  |  |  |

|        |                | 0                                                                                       | 1                                                                                                                                                    | 128X                                   |                           |  |  |  |

|        |                | 1                                                                                       | 0                                                                                                                                                    | 32X                                    |                           |  |  |  |

|        |                | 1                                                                                       | 1                                                                                                                                                    | Reserved                               |                           |  |  |  |

#### **Power-On Reset**

When power is first up, a reset function is automatically performed. Refer to the **Table-8** below for reset states of the ten registers. During the first 3,072 cycles of the system clock after reset, control data can be loaded to the ten registers and at the same time the output is forced to bipolar zero state. After 3,072 cycles of system clock, a "Low" to "High" at ML (pin12) will initiate programming.

**Table-8 Register Reset States**

| Register Name | State               |

|---------------|---------------------|

| Reg0          | 0000 0001 1111 1111 |

| Reg1          | 0000 0011 1111 1111 |

| Reg2          | 0000 0101 0010 0000 |

| Reg3          | 0000 0110 0010 0000 |

| Reg4          | 0000 1001 1111 1111 |

| Reg5          | 0000 1011 1111 1111 |

| Reg6          | 0000 1101 1111 1111 |

| Reg7          | 0000 1111 1111 1111 |

| Reg8          | 0001 0001 1111 1111 |

| Reg9          | 0001 0010 0000 0000 |

#### **Audio Input Format**

The register bits, FM1 and FM0 of **Reg3** together determine the audio input data format as shown in the following table:

**Table-9 Audio Interface Format Control**

| FM1 | FM0 | Audio Input Format Selected |

|-----|-----|-----------------------------|

| 0   | 0   | Right justified             |

| 0   | 1   | Left justified              |

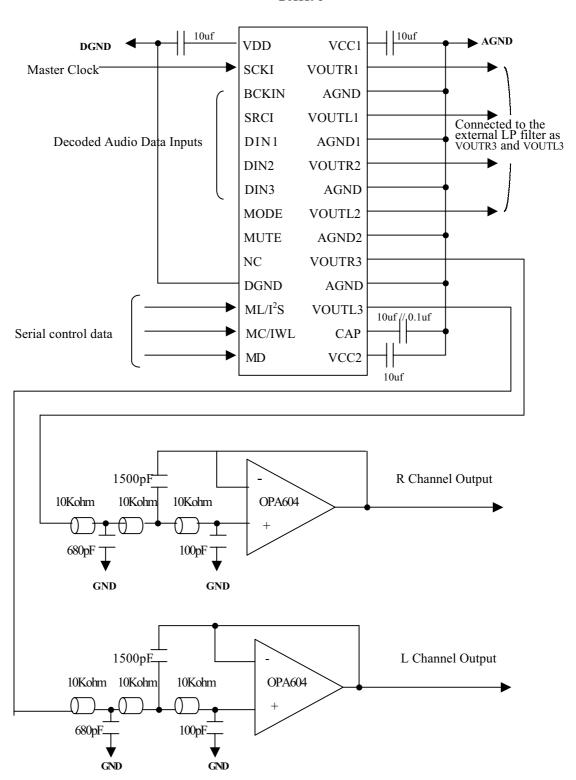

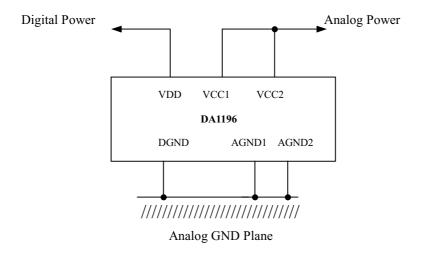

| 1   | 0   | $I^2S$                      |