# **RS2132**

### High Precision CC/CV Primary-Side PWM Controller

## **General Description**

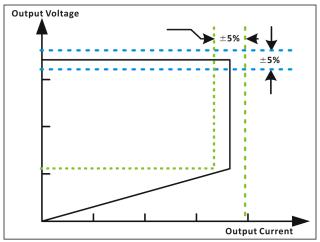

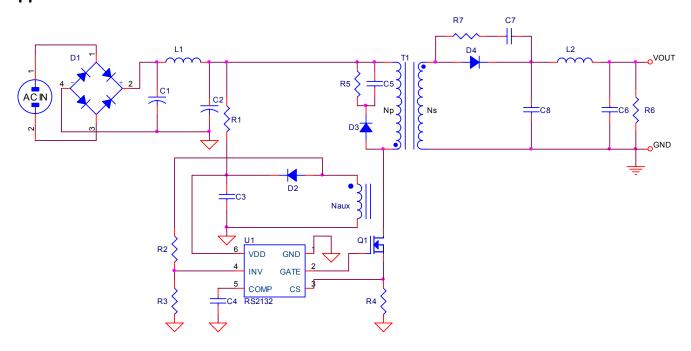

RS2132 is a high performance offline PWM controller for low power AC/DC charger and adapter applications. It operates in primary-side sensing and regulation. Consequently, opto-coupler and 431 could be eliminated. Proprietary Constant Voltage (CV) and Constant Current (CC) control is integrated as shown in the figure below.

In CC control, the current and output power setting can be adjusted externally by the sense resistor at CS pin. In CV control, multi-mode operations are utilized to achieve high performance and high efficiency. In addition, good load regulation is achieved by the built-in cable drop compensation. Device operates in PFM in CC mode as well at large load condition and it operates in PWM with frequency reduction at light/medium load.

RS2132 offers power on soft start control and protection coverage with auto-recovery features including Cycle-by-Cycle current limiting, VDD OVP, VDD clamp and UVLO. Excellent EMI performance is achieved with Orister proprietary frequency jiggling technique. High precision constant voltage (CV) and constant current (CC) can be achieved by RS2132.

#### **Features**

- ±5% Constant Voltage Regulation at Universal AC input

- High Precision Constant Current Regulation at Universal AC input

- Primary-side Sensing and Regulation Without 431 and Optocoupler

- Programmable CV and CC Regulation

- Adjustable Constant Current and Output Power Setting

- Built-in Secondary Constant Current Control with Primary Side Feedback

- Built-in Adaptive Current Peak Regulation

- Built-in Primary winding inductance compensation

- Programmable Cable drop Compensation

- Power on Soft-start

- Built-in Leading Edge Blanking (LEB)

- Cycle-by-Cycle Current Limiting

- VDD Under Voltage Lockout with Hysteresis (UVLO)

- VDD OVP & VDD Clamp

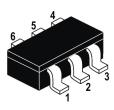

- Available in an SOT-26 Package

- RoHS Compliant and 100% Lead (Pb)-Free and Green (Halogen Free with Commercial Standard)

### **Applications**

- Cell Phone Charger

- Digital Cameras Charger

- Small Power Adaptor

- Auxiliary Power for PC, TV etc.

- Linear Regulator/RCC Replacement

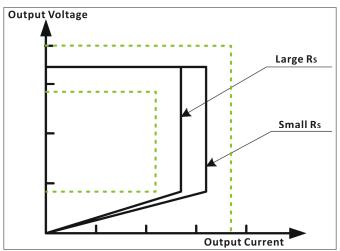

Fig.1. Typical CC/CV Curve

This integrated circuit can be damaged by ESD. Orister Corporation recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **Application Circuits**

# **Pin Assignments**

SOT-26

| PACKAGE  | PIN | SYMBOL | DESCRIPTION                                                                                                                                                                                               |

|----------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 GND    |     | GND    | Ground.                                                                                                                                                                                                   |

|          | 2   | GATE   | Totem output to drive the external Power MOSFET.                                                                                                                                                          |

|          | 3   | CS     | Current sense input.                                                                                                                                                                                      |

| 4 INV wi |     | INV    | The voltage feedback from auxiliary winding. Connected to resistor divider from auxiliary winding reflecting output voltage. PWM duty cycle is determined by EA output and current sense signal at pin 4. |

|          | 5   | COMP   | Loop Compensation for CV Stability.                                                                                                                                                                       |

|          | 6   | VDD    | Power Supply.                                                                                                                                                                                             |

# **Ordering Information**

| DEVICE     | DEVICE CODE                                                             |

|------------|-------------------------------------------------------------------------|

|            | Y is package & Pin Assignments designator :                             |

|            | NF: SOT-26                                                              |

| RS2132 Y Z | <b>Z</b> is Lead Free designator :                                      |

|            | P: Commercial Standard, Lead (Pb) Free and Phosphorous (P) Free Package |

|            | G: Green (Halogen Free with Commercial Standard)                        |

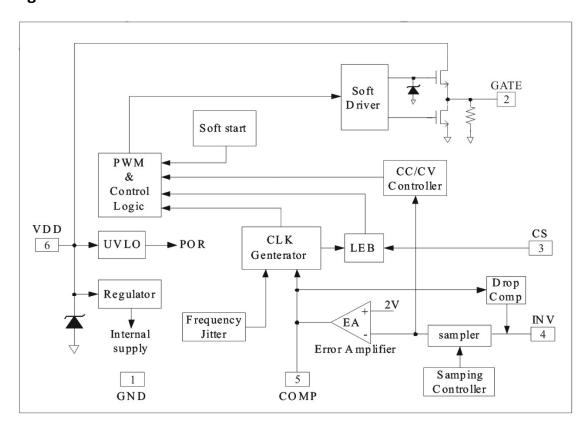

# **Block Diagram**

# **Absolute Maximum Ratings**

| Symbol         | Parameter                                      | Range                      | Units |

|----------------|------------------------------------------------|----------------------------|-------|

| -              | Drain Voltage (Off state)                      | -0.3V to B <sub>VDSS</sub> | V     |

| -              | V <sub>DD</sub> Voltage                        | -0.3 to $V_{DD\_Clamp}$    | V     |

| -              | V <sub>DD</sub> Zener Clamp Continuous Current | 10                         | mA    |

| -              | COMP Voltage                                   | -0.3 to 7                  | V     |

| -              | CS Input Voltage                               | -0.3 to 7                  | V     |

| -              | INV Input Voltage                              | -0.3 to 7                  | V     |

| T <sub>J</sub> | Junction Temperature                           | -20 to 150                 | °C    |

| $T_{OPR}$      | Operating Temperature Range                    | -20 to +85                 | °C    |

| $T_{STG}$      | Storage Temperature Range                      | -55 to 150                 | °C    |

| $T_{LEAD}$     | Lead Temperature (Soldering, 10secs)           | 260                        | °C    |

**Note:** Stress beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

# **Electrical Characteristics** (V<sub>DD</sub>=16V, T<sub>A</sub>=25°C, unless otherwise specified)

| Symbol                       | Parameter                       | Test Conditions                                                                            | Min. | Тур. | Max. | Unit |  |

|------------------------------|---------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|--|

| Supply Voltage (VDD) Section |                                 |                                                                                            |      |      |      |      |  |

| I <sub>DD ST</sub>           | Standby current                 | V <sub>DD</sub> =13V                                                                       | -    | 5    | 20   | uA   |  |

| I <sub>DD_OP</sub>           | Operation Current               | Operation supply current I <sub>NV</sub> =2V,CS=0V, V <sub>DD</sub> =V <sub>DDG</sub> =20V | -    | 2.5  | 3.5  | mA   |  |

| UVLO(ON)                     | VDD Under Voltage Lockout Enter | VDD falling                                                                                | 13.5 | 14.5 | 16.0 | V    |  |

| UVLO(OFF)                    | VDD Under Voltage Lockout Exit  | VDD rising                                                                                 | 7.5  | 8.5  | 10   | V    |  |

| OVP                          | Over voltage protection voltage | Ramp up VDD until gate clock is off                                                        | 27.5 | 29.5 | 31.5 | V    |  |

| V <sub>DD Clamp</sub>        | Maximum VDD opertation voltage  | I <sub>DD</sub> =10mA                                                                      | 30.5 | 32.5 | 34.5 | V    |  |

|                              | Curren                          | t Sense Input Section                                                                      |      |      |      |      |  |

| T <sub>LEB</sub>             | LEB time                        | -                                                                                          | -    | 540  | -    | ns   |  |

| Vth oc                       | Over current threshold          | -                                                                                          | 870  | 900  | 930  | mV   |  |

| Td_oc                        | OCP Propagation delay           | -                                                                                          | -    | 150  | -    | ns   |  |

| Z <sub>SENSE IN</sub>        | Input Impedance                 | -                                                                                          | -    | 50   | -    | ΚΩ   |  |

| Tss                          | Soft start time                 | -                                                                                          | -    | 10   | -    | ms   |  |

|                              |                                 | CV Section                                                                                 |      |      |      |      |  |

| Freq_Nom                     | System Nominal switch frequency | -                                                                                          | -    | 60   | -    | KHZ  |  |

| Freq_startup                 | -                               | INV=0V, Comp=5V                                                                            | -    | 14   | -    | KHZ  |  |

| Δf/Freq                      | Frequency jitter range          | -                                                                                          | -    | +/-4 | -    | %    |  |

|                              | Erro                            | r Amplifier Section                                                                        |      |      |      |      |  |

| V <sub>REF</sub> _EA         | Reference voltage for EA        | -                                                                                          | 1.97 | 2    | 2.03 | V    |  |

| $G_{DC}$                     | DC gain of the EA               | -                                                                                          | -    | 60   | -    | dB   |  |

| I COMP MAX                   | Max. Cable compensation current | INV=2V, COMP=0V                                                                            | -    | 42   | -    | uA   |  |

| Gate Drive Output Section    |                                 |                                                                                            |      |      |      |      |  |

| VOL                          | Output Low Level                | I <sub>O</sub> =20mA                                                                       | -    | -    | 1    | V    |  |

| VOH                          | Output High Level               | I <sub>O</sub> =20mA                                                                       | 8    | -    | -    | V    |  |

| V <sub>clamp</sub>           | Output Clamp Voltage Level      | -                                                                                          | -    | 16   | -    | V    |  |

| T_r                          | Output Rising Time              | CL=0.5nF                                                                                   | -    | 650  | -    | ns   |  |

| T_f                          | Output Falling Time             | CL=0.5nF                                                                                   | -    | 40   | -    | ns   |  |

### **Detail Description**

RS2132 is a cost effective PWM power switch optimized for off-line low power AC/DC applications including battery chargers and adaptors. It operates in primary side sensing and regulation, thus opto-coupler and 431 are not required. Proprietary built-in CV and CC control can achieve high precision CC/CV control meeting most adaptor and charger application requirements.

#### **Startup Current and Start up Control**

Startup current of RS2132 is designed to be very low so that VDD could be charged up above UVLO threshold and starts up quickly. A large value startup resistor can therefore be used to minimize the power loss in application.

#### **Operating Current**

The Operating current of RS2132 is as low as 2.5mA. Good efficiency is achieved with the low operating current together with Multi-mode control features.

#### **Soft Start**

RS2132 features an internal soft start to minimize the component electrical over-stress during power on startup. As soon as VDD reaches UVLO (OFF), the control algorithm will ramp peak current voltage threshold gradually from nearly zero to normal setting of 0.90V. Every restart is a soft start.

#### **CC/CV Operation**

RS2132 is designed to produce good CC/CV control characteristic as shown in the Fig. 1.

In charger applications, a discharged battery charging starts in the CC portion of the curve until it is nearly full charged and smoothly switches to operate in CV portion of the curve.

In an AC/DC adapter, the normal operation occurs only on the CV portion of the curve. The CC portion provides output current limiting. In CV operation, the output voltage is regulated through the primary side control. In CC operation mode, RS2132 will regulate the output current constant regardless of the output voltage drop.

#### **Principle of Operation**

To support RS2132 proprietary CC/CV control, system needs to be designed in DCM mode for flyback system (Refer to Typical Application Diagram).

In the DCM flyback converter, the output voltage can be sensed via the auxiliary winding. During MOSFET turn-on time, the load current is supplied from the output filter capacitor  $C_0$ . The current in the primary winding ramps up. When MOSFET turns off, the primary current transfers to the secondary at the amplitude of

$$I_S = \frac{N_P}{N_S} \times I_P$$

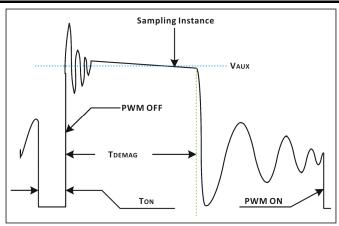

The auxiliary voltage reflects the output voltage as shown in fig.2 and it is given by

$$V_{AUX} = \frac{N_{AUX}}{N_S} \times (V_O + \Delta V)$$

Where  $\Delta V$  indicates the drop voltage of the output Diode.

Fig.2. Auxiliary voltage waveform

Via a resistor divider connected between the auxiliary winding and INV (pin 3), the auxiliary voltage is sampled at the end of the demagnetization and it is hold until the next sampling.

The sampled voltage is compared with  $V_{REF}$  (2.0V) and the error is amplified. The error amplifier output COMP reflects the load condition and controls the PWM switching frequency to regulate the output voltage, thus constant output voltage can be achieved.

When sampled voltage is below  $V_{REF}$  and the error amplifier output COMP reaches its maximum, the switching frequency is controlled by the sampled voltage thus the output voltage to regulate the output current, thus the constant output current can be achieved.

#### **Adjustable CC point and Output Power**

In RS2132, the CC point and maximum output power can be externally adjusted by external current sense resistor  $R_S$  at CS pin as illustrated in Typical Application Diagram. The output power is adjusted through CC point change. The larger  $R_S$ , the smaller CC point is, and the smaller output power becomes, and vice versa as shown in Fig.3.

Fig.3. Adjustable output power by changing  $R_{\text{S}}$

#### Operation switching frequency

The switching frequency of RS2132 is adaptively controlled according to the load conditions and the operation modes. No external frequency setting components are required. The operation switching frequency at maximum output power is set to 60KHz internally.

For flyback operating in DCM, The maximum output power is given by

$$P_{OMAX} = \frac{1}{2} \times L_P \times F_{SW} \times I_{P}^2$$

Where L<sub>P</sub> indicate the inductance of primary winding and I<sub>P</sub> is the peak current of primary winding.

Refer to the equation 3, the change of the primary winding inductance results in the change of the maximum output power and the constant output current in CC mode. To compensate the change from variations of primary winding inductance, the switching frequency is locked by an internal loop such that the switching frequency is

$$F_{SW} = \frac{1}{2T_{DEMAG}}$$

Since  $T_{Demag}$  is inversely proportional to the inductance, as a result, the product  $L_P$  and  $F_{sw}$  is constant, thus the maximum output power and constant current in CC mode will not change as primary winding inductance changes. Up to +/-10% variation of the primary winding inductance can be compensated.

#### Frequency Jiggling for EMI improvement

The Frequency Jiggling (switching frequency modulation) is implemented in RS2132. The oscillation frequency is modulated so that the tone energy is spread out. The spread spectrum minimizes the conduction band EMI and therefore eases the system design.

#### **Current Sensing and Leading Edge Blanking**

Cycle-by-Cycle current limiting is offered in RS2132 current mode PWM control. The switch current is detected by a sense resistor into the CS pin. An internal leading edge blanking circuit chops off the sensed voltage spike at initial internal power MOSFET on state so that the external RC filtering on sense input is no longer needed. The PWM duty cycle is determined by the current sense input voltage and the EA output voltage.

#### **Gate Drive**

The external power MOSFET is driven by a dedicated gate driver of RS2132. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive compromises EMI.

A good tradeoff is achieved through the built-in totem pole gate design with right output strength control.

#### **Programmable Cable drop Compensation**

In RS2132, cable drop compensation is implemented to achieve good load regulation. An offset voltage is generated at INV by an internal current flowing into the resister divider. The current is inversely proportional to the voltage across pin COMP, as a result, it is inversely proportional to the output load current, thus the drop due to the cable loss can be compensated. As the load current decreases from full-load to no-load, the offset voltage at INV will increase. It can also be programmed by adjusting the resistance of the divider to compensate the drop for various cable lines used.

#### **Protection Control**

Good power supply system reliability is achieved with its rich protection features including Cycle-by-Cycle current limiting (OCP), VDD clamp, Power on Soft Start, and Under Voltage Lockout on VDD(UVLO).

VDD is supplied by transformer auxiliary winding output. The output of RS2132 is shut down when VDD drops below UVLO (ON) limit and Switcher enters power on start-up sequence thereafter.

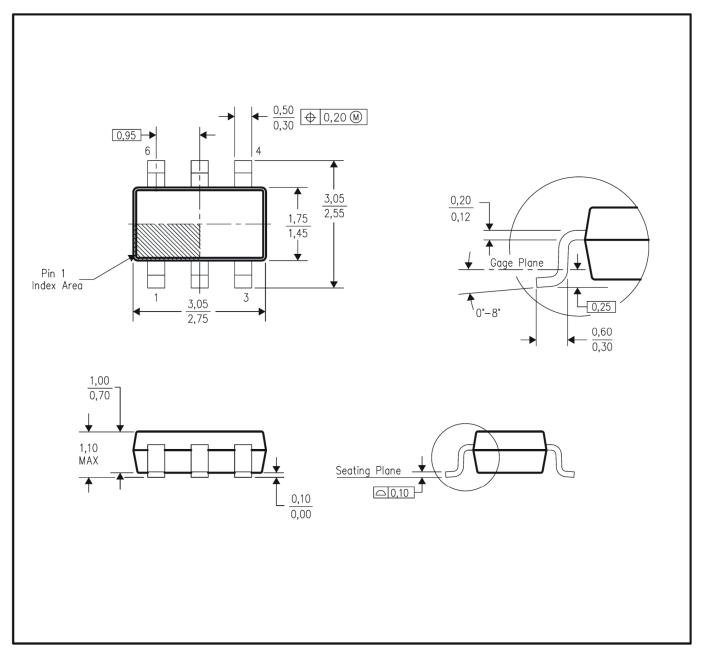

### **SOT-26 Dimension**

### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Leads 1, 2, 3 may be wider than leads 4, 5, 6 for package orientation.

Falls within JEDEC MO-178 variation AB, except minimum lead width.

# **Soldering Methods for Orister's Products**

- 1. Storage environment: Temperature= $10^{\circ}$ C $\sim$ 35 $^{\circ}$ C Humidity= $65\%\pm15\%$

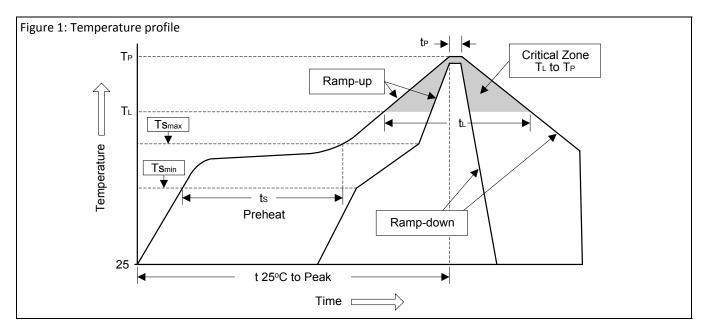

- 2. Reflow soldering of surface-mount devices

| Profile Feature                                          | Sn-Pb Eutectic Assembly | Pb-Free Assembly |  |  |

|----------------------------------------------------------|-------------------------|------------------|--|--|

| Average ramp-up rate (T <sub>L</sub> to T <sub>P</sub> ) | <3°C/sec                | <3°C/sec         |  |  |

| Preheat                                                  |                         |                  |  |  |

| - Temperature Min (Ts <sub>min</sub> )                   | 100°C                   | 150°C            |  |  |

| - Temperature Max (Ts <sub>max</sub> )                   | 150°C                   | 200°C            |  |  |

| - Time (min to max) (ts)                                 | 60~120 sec              | 60~180 sec       |  |  |

| Tsmax to T <sub>L</sub>                                  |                         |                  |  |  |

| - Ramp-up Rate                                           | <3°C/sec                | <3°C/sec         |  |  |

| Time maintained above:                                   |                         |                  |  |  |

| - Temperature (T <sub>L</sub> )                          | 183°C                   | 217°C            |  |  |

| - Time (t <sub>L</sub> )                                 | 60~150 sec              | 60~150 sec       |  |  |

| Peak Temperature (T <sub>P</sub> )                       | 240°C +0/-5°C           | 260°C +0/-5°C    |  |  |

| Time within 5°C of actual Peak                           | 10×20 cos               | 20240.505        |  |  |

| Temperature (t <sub>P</sub> )                            | 10~30 sec               | 20~40 sec        |  |  |

| Ramp-down Rate                                           | <6°C/sec                | <6°C/sec         |  |  |

| Time 25°C to Peak Temperature                            | <6 minutes              | <8 minutes       |  |  |

### 3. Flow (wave) soldering (solder dipping)

| Products         | Peak temperature | Dipping time |

|------------------|------------------|--------------|

| Pb devices.      | 245°C ±5°C       | 5sec ±1sec   |

| Pb-Free devices. | 260°C +0/-5°C    | 5sec ±1sec   |

### **Important Notice:**

#### © Orister Corporation

Orister cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an Orister product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied.

Orister reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Except as provided in Orister's terms and conditions of sale, Orister assumes no liability whatsoever, and Orister disclaims any express or implied warranty relating to the sale and/or use of Orister products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. Testing and other quality control techniques are utilized to the extent Orister deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed.

Orister and the Orister logo are trademarks of Orister Corporation. All other brand and product names appearing in this document are registered trademarks or trademarks of their respective holders.