## **AK4382A**

## 112dB 192kHz 24-Bit 2ch $\Delta\Sigma$ DAC

#### 概 要

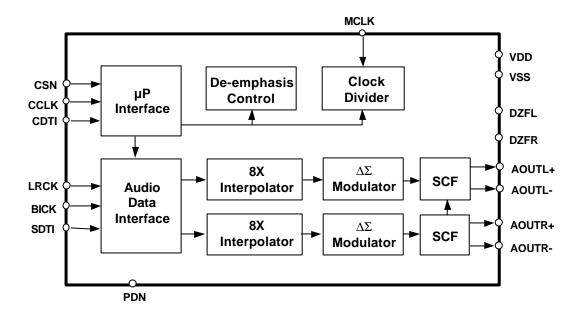

AK4382Aはディジタルオーディオ機器用にコストパフォーマンスを求めた24ビットDACです。ΔΣ変調器にはワイドダイナミックレンジを実現する新開発のアドバンスト・マルチビット方式を採用しています。内蔵のポストフィルタにはスイッチトキャパシタフィルタ(SCF)を採用しており、クロックジッタによる精度の劣化を改善します。サンプリングレートは216kHzまで対応しており、DVD, AC-3アンプ等のシステムに最適です。AK4382Aは超小型16pin TSSOPパッケージに実装され、基板スペースを削減します。

#### 特長

- □ サンプリングレート: 8kHz ~ 216kHz

- □ 128 倍オーバサンプリング(通常速モード)

- □ 64 倍オーパサンプリング(2倍速モード)

- □ 32 倍オーバサンプリング(4倍速モード)

- □ 24 ピット 8 倍 FIR ディジタルフィルタ内蔵

- □ SCF 内蔵

- □ ディジタルディエンファシス内蔵 (32kHz, 44.1kHz, 48kHz 対応)

- ロ ソフトミュート内蔵

- □ ディジタルATT (256ステップ)

- □ ディジタル I/F フォーマット: 24ピット前詰め, 24/20/16ピット後詰め, I<sup>2</sup>S

- □ マスタクロック: 256fs, 384fs, 512fs or 768fs (通常速モード) 128fs, 192fs, 256fs or 384fs (2倍速モード)

128fs or 192fs (4倍速モード)

- ☐ THD+N: -94dB

- ☐ Dynamic Range: 112dB

- 口強ジッタ耐力

- □ 電源電圧: 4.75 ~ 5.25V

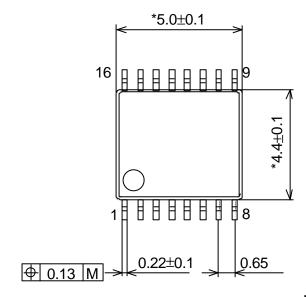

- □ 超小型パッケージ: 16pin TSSOP (6.4mm x 5.0mm)

## ■ オーダリングガイド

AK4382AVT  $-40 \sim +85^{\circ}$ C 16pin TSSOP (0.65mm pitch) AKD4382 AK4382A 用評価ボード

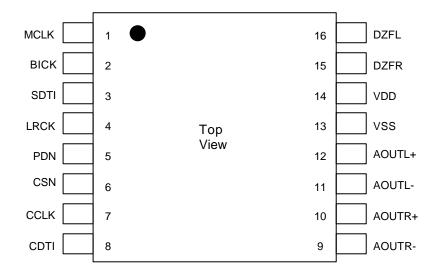

## ■ ピン配置

# ピン / 機能

| No. | Pin Name | I/O | Function                                                                 |

|-----|----------|-----|--------------------------------------------------------------------------|

| 1   | MCLK     | I   | Master Clock Input Pin                                                   |

|     |          |     | An external TTL clock should be input on this pin.                       |

| 2   | BICK     | I   | Audio Serial Data Clock Pin                                              |

| 3   | SDTI     | I   | Audio Serial Data Input Pin                                              |

| 4   | LRCK     | I   | L/R Clock Pin                                                            |

| 5   | PDN      | I   | Power-Down Mode Pin                                                      |

|     |          |     | When at "L", the AK4382A is in the power-down mode and is held in reset. |

|     |          |     | The AK4382A should always be reset upon power-up.                        |

| 6   | CSN      | I   | Chip Select Pin                                                          |

| 7   | CCLK     | I   | Control Data Input Pin                                                   |

| 8   | CDTI     | I   | Control Data Input Pin                                                   |

| 9   | AOUTR-   | О   | Rch Negative Analog Output Pin                                           |

| 10  | AOUTR+   | О   | Rch Positive Analog Output Pin                                           |

| 11  | AOUTL-   | О   | Lch Negative Analog Output Pin                                           |

| 12  | AOUTL+   | О   | Lch Positive Analog Output Pin                                           |

| 13  | VSS      | -   | Ground Pin                                                               |

| 14  | VDD      | -   | Power Supply Pin                                                         |

| 15  | DZFR     | О   | Rch Data Zero Input Detect Pin                                           |

| 16  | DZFL     | 0   | Lch Data Zero Input Detect Pin                                           |

Note: All input pins should not be left floating.

| 絶対最大定格                                       |        |      |         |       |  |  |  |  |

|----------------------------------------------|--------|------|---------|-------|--|--|--|--|

| (VSS=0V; Note 1)                             |        |      |         |       |  |  |  |  |

| Parameter                                    | Symbol | min  | max     | Units |  |  |  |  |

| Power Supply                                 | VDD    | -0.3 | 6.0     | V     |  |  |  |  |

| Input Current (any pins except for supplies) | IIN    | -    | ±10     | mA    |  |  |  |  |

| Input Voltage                                | VIND   | -0.3 | VDD+0.3 | V     |  |  |  |  |

| Ambient Operating Temperature                | Ta     | -40  | 85      | °C    |  |  |  |  |

| Storage Temperature                          | Tstg   | -65  | 150     | °C    |  |  |  |  |

Note: 1. 電圧はすべてグランドピンに対する値です。

注意: この値を超えた条件で使用した場合、デバイスを破壊することがあります。 また通常の動作は保証されません。

| 推奨動作条件           |                                   |      |     |      |   |  |  |

|------------------|-----------------------------------|------|-----|------|---|--|--|

| (VSS=0V; Note 1) |                                   |      |     |      |   |  |  |

| Parameter        | Parameter Symbol min typ max Unit |      |     |      |   |  |  |

| Power Supply     | VDD                               | 4.75 | 5.0 | 5.25 | V |  |  |

注意: 本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので十分ご注意下さい。

## アナログ特性

(特記なき場合は、Ta = 25°C; VDD = 5.0V; fs = 44.1kHz; BICK = 64fs; Signal Frequency = 1kHz;

24bit Input Data; Measurement frequency = 20Hz ~ 20kHz;  $R_L \ge 2k\Omega$ )

| Parameter                      |                   |             | min   | typ   | max   | Units  |

|--------------------------------|-------------------|-------------|-------|-------|-------|--------|

| Resolution                     |                   |             |       |       | 24    | Bits   |

| <b>Dynamic Characteristics</b> | (No               | te 3)       |       |       |       |        |

| THD+N                          | fs=44.1kHz        | 0dBFS       |       | -94   | -86   | dB     |

|                                | BW=20kHz          | -60dBFS     |       | -48   | -     | dB     |

|                                | fs=96kHz          | 0dBFS       |       | -92   | -84   | dB     |

|                                | BW=40kHz          | -60dBFS     |       | -45   | -     | dB     |

|                                | fs=192kHz         | 0dBFS       |       | -92   | -     | dB     |

|                                | BW=40kHz          | -60dBFS     |       | -45   | -     | dB     |

| Dynamic Range (-60dBF          | S with A-weighted | d) (Note 4) | 102   | 112   |       | dB     |

| S/N (A-weigh                   | ted)              | (Note 5)    | 102   | 112   |       | dB     |

| Interchannel Isolation (1kH    | Hz)               |             | 90    | 110   |       | dB     |

| Interchannel Gain Mismat       | ch                |             |       | 0.2   | 0.5   | dB     |

| DC Accuracy                    |                   |             |       |       |       |        |

| Gain Drift                     |                   |             |       | 100   | -     | ppm/°C |

| Output Voltage                 |                   | (Note 6)    | ±2.55 | ±2.75 | ±2.95 | Vpp    |

| Load Resistance                |                   | (Note 7)    | 2     |       |       | kΩ     |

| Power Supplies                 |                   |             |       |       |       |        |

| Power Supply Current (VD       | DD)               |             |       |       |       |        |

| Normal Operation (PD           | ON = "H", fs≤96kF | ·Iz)        |       | 20    | 34    | mA     |

| Normal Operation (PD           | ON = "H", fs=192k | Hz)         |       | 25    | 42    | mA     |

| Power-Down Mode (I             | PDN = "L")        | (Note 8)    |       | 10    | 100   | μA     |

Notes: 3. Audio Precision (System Two)使用。測定結果は評価ボードのマニュアルを参照下さい。

- 4. 100dB at 16bit data.

- 5. S/N比は入力ビット長に依存しません。

- 6. フルスケール電圧 (OdB)。出力電圧は VDD の電圧に比例します。

AOUT (typ.@0dB) = (AOUT+) - (AOUT-) =  $\pm 2.75$ Vpp×VDD/5<sub>o</sub>

- 7. AC負荷に対して。DC負荷がある場合は $4 \, \mathrm{k} \Omega$ 。

- 8. クロック (MCLK, BICK, LRCK)を含む全ディジタル入力ピン を VDD または VSS に固定した場合の 値です。

## シャープロールオフ・フィルタ特性

$(Ta = 25^{\circ}C; VDD = 4.75 \sim 5.25V; fs = 44.1kHz; DEM = OFF; SLOW = "0")$

| Parameter            |                 |            | Symbol | min  | typ     | max    | Units |

|----------------------|-----------------|------------|--------|------|---------|--------|-------|

| Digital filter       |                 |            |        |      |         |        |       |

| Passband ±0.05       | 5dB (Note 9     | 9)         | PB     | 0    |         | 20.0   | kHz   |

| -6.0dB               | }               |            |        | -    | 22.05   | -      | kHz   |

| Stopband             | (Note 9         | ))         | SB     | 24.1 |         |        | kHz   |

| Passband Ripple      | Passband Ripple |            |        |      |         | ± 0.02 | dB    |

| Stopband Attenuation |                 |            | SA     | 54   |         |        | dB    |

| Group Delay          | (Note 1         | 0)         | GD     | -    | 19.3    | -      | 1/fs  |

| Digital Filter + SCF |                 |            |        |      |         |        |       |

| Frequency Response   | 20.0kHz         | fs=44.1kHz | FR     | -    | ± 0.2   | -      | dB    |

|                      | 40.0kHz         | fs=96kHz   | FR     | -    | ± 0.3   | -      | dB    |

|                      | 80.0kHz         | fs=192kHz  | FR     | -    | +0/-0.6 | -      | dB    |

Notes: 9. 通過域、阻止域の周波数は fs (システムサンプリングレート) に比例し、

PB=0.4535\*fs(@±0.05dB)、SB=0.546\*fs です。

10. ディジタルフィルタによる演算遅延で、16/24ビットデータが入力レジスタにセットされてからアナログ信号が出力されるまでの時間です。

## スローロールオフ・フィルタ特性

(Ta = 25°C; AVDD, DVDD = 4.75~5.25V; fs = 44.1kHz; DEM = OFF; SLOW = "1")

| Parameter            | Parameter |           |    |      | typ   | max     | Units |

|----------------------|-----------|-----------|----|------|-------|---------|-------|

| Digital Filter       |           |           |    |      |       |         |       |

| Passband ±0.04       | 4dB (Not  | e 11)     | PB | 0    |       | 8.1     | kHz   |

| -3.0dE               | 3         |           |    | -    | 18.2  | -       | kHz   |

| Stopband             | (Note     | e 11)     | SB | 39.2 |       |         | kHz   |

| Passband Ripple      |           |           | PR |      |       | ± 0.005 | dB    |

| Stopband Attenuation | :         |           | SA | 72   |       |         | dB    |

| Group Delay          | (Note     | 10)       | GD | ı    | 19.3  | -       | 1/fs  |

| Digital Filter + SCF |           |           |    |      |       |         |       |

| Frequency Response   | 20.0kHz   | fs=44.kHz | FR | -    | +0/-5 | -       | dB    |

|                      | 40.0kHz   | fs=96kHz  | FR | -    | +0/-4 | -       | dB    |

|                      | 80.0kHz   | fs=192kHz | FR | -    | +0/-5 | -       | dB    |

Note: 11. The passband and stopband frequencies scale with fs. For example,  $PB = 0.185 \times fs$  (@±0.04dB),  $SB = 0.888 \times fs$ .

## DC特性

$(Ta = 25^{\circ}C; VDD = 4.75 \sim 5.25V)$

| Parameter                                     | Symbol | min     | typ | max  | Units |

|-----------------------------------------------|--------|---------|-----|------|-------|

| High-Level Input Voltage                      | VIH    | 2.2     | -   | -    | V     |

| Low-Level Input Voltage                       | VIL    | -       | -   | 0.8  | V     |

| High-Level Output Voltage (Iout = $-80\mu$ A) | VOH    | VDD-0.4 | -   | -    | V     |

| Low-Level Output Voltage (Iout = $80\mu$ A)   | VOL    | -       |     | 0.4  | V     |

| Input Leakage Current                         | Iin    | -       | -   | ± 10 | μA    |

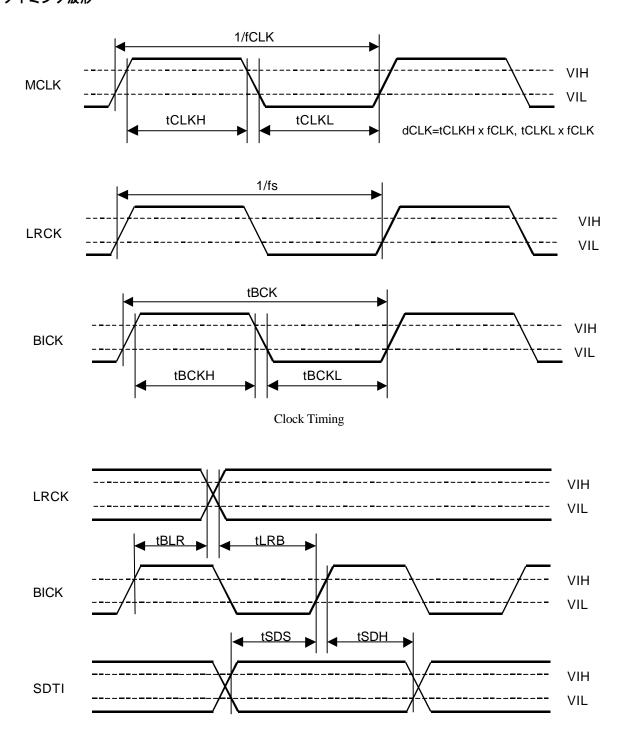

## スイッチング特性

$\overline{\text{(Ta = 25^{\circ}\text{C; VDD = 4.75} \sim 5.25\text{V; C}_{L} = 20\text{pF)}}$

| Parameter                             | Symbol | min     | typ     | max    | Units |

|---------------------------------------|--------|---------|---------|--------|-------|

| Master Clock Frequency                | fCLK   | 2.048   | 11.2896 | 41.472 | MHz   |

| Duty Cycle                            | dCLK   | 40      |         | 60     | %     |

| LRCK Frequency                        |        |         |         |        |       |

| Normal Speed Mode                     | fsn    | 8       |         | 54     | kHz   |

| Double Speed Mode                     | fsd    | 60      |         | 108    | kHz   |

| Quad Speed Mode                       | fsq    | 120     |         | 216    | kHz   |

| Duty Cycle                            | Duty   | 45      |         | 55     | %     |

| Audio Interface Timing                |        |         |         |        |       |

| BICK Period                           |        |         |         |        |       |

| Normal Speed Mode                     | tBCK   | 1/128fs |         |        | ns    |

| Double/Quad Speed Mode                | tBCK   | 1/64fs  |         |        | ns    |

| BICK Pulse Width Low                  | tBCKL  | 30      |         |        | ns    |

| Pulse Width High                      | tBCKH  | 30      |         |        | ns    |

| BICK "↑" to LRCK Edge (Note 12)       | tBLR   | 20      |         |        | ns    |

| LRCK Edge to BICK "\tilde\" (Note 12) | tLRB   | 20      |         |        | ns    |

| SDTI Hold Time                        | tSDH   | 20      |         |        | ns    |

| SDTI Setup Time                       | tSDS   | 20      |         |        | ns    |

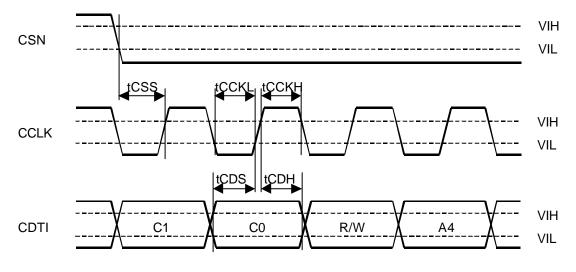

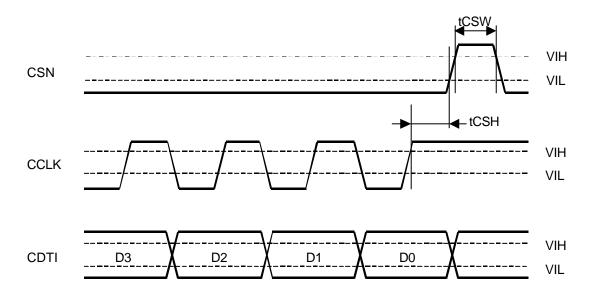

| Control Interface Timing              |        |         |         |        |       |

| CCLK Period                           | tCCK   | 200     |         |        | ns    |

| CCLK Pulse Width Low                  | tCCKL  | 80      |         |        | ns    |

| Pulse Width High                      | tCCKH  | 80      |         |        | ns    |

| CDTI Setup Time                       | tCDS   | 40      |         |        | ns    |

| CDTI Hold Time                        | tCDH   | 40      |         |        | ns    |

| CSN High Time                         | tCSW   | 150     |         |        | ns    |

| CSN "↓" to CCLK "↑"                   | tCSS   | 50      |         |        | ns    |

| CCLK "↑" to CSN "↑"                   | tCSH   | 50      |         |        | ns    |

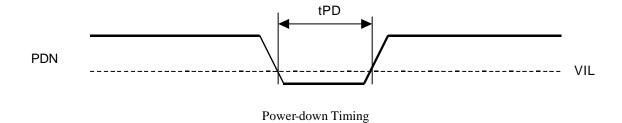

| Reset Timing                          |        |         |         |        |       |

| PDN Pulse Width (Note 13)             | tPD    | 150     |         |        | ns    |

Notes: 12.この規格値はLRCKのエッジとBICKの"<sup>↑</sup>"が重ならないように規定しています。

<sup>13.</sup> 電源投入時はPDNを "L" から "H" にすることでリセットがかかります。

## ■ タイミング波形

Serial Interface Timing

WRITE Command Input Timing

WRITE Data Input Timing

- 8 -

#### 機能説明

#### ■システムクロック

必要なクロックは、MCLK, LRCK, BICK です。マスタクロック (MCLK) とサンプリングクロック (LRCK) は同期する必要はありますが位相を合わせる必要はありません。MCLK はインタポ・レーションフィルタと  $\Delta\Sigma$  変調器に使用されます。 MCLK周波数を設定する方法は内部レジスタで設定する方法 (Manual Setting Mode) とデバイス内部で自動設定する方法 (Auto Setting Mode) の 2 つがあります。Manual Setting Mode (ACKS = "0": Register 00H)では、DFS0/1 でサンプリングスピードが設定され(Table 1)、各スピードでのMCLK周波数は自動設定されます (Table 2~4)。リセット解除時 (PDN = " $\uparrow$ ") はAuto Setting Mode に設定されます。 Auto Setting Mode (ACKS = "1": Default) では、サンプリングスピードとMCLK周波数は自動検出され(Table 5)、内部クロックは適切な周波数 (Table 6) に自動設定されるため、DFS0/1の設定は不要です。

動作時 (PDN="H") は、各外部クロック (MCLK, BICK, LRCK) を止めてはいけません。これらのクロックが供給されない場合、内部にダイナミックなロジックを使用しているため、過電流が流れ、動作が異常になる可能性があります。クロックを止める場合はパワーダウン状態 (PDN="L") にして下さい。電源 ON 等のリセット解除時 (PDN=" $^+$ ") は MCLK, LRCK が入力されるまでパワーダウン状態です。

| DFS1 | DFS0 | Sampling Rate (fs) |               |   |

|------|------|--------------------|---------------|---|

| 0    | 0    | Normal Speed Mode  | 8kHz~54kHz    |   |

| 0    | 1    | Double Speed Mode  | 60kHz~108kHz  | ı |

| 1    | 0    | Ouad Speed Mode    | 120kHz~216kHz | l |

Default

Table 1.サンプリングスピード (Manual Setting Mode)

| LRCK    |            | MCLK       |            |            |           |  |  |

|---------|------------|------------|------------|------------|-----------|--|--|

| fs      | 256fs      | 384fs      | 512fs      | 768fs      | 64fs      |  |  |

| 32.0kHz | 8.1920MHz  | 12.2880MHz | 16.3840MHz | 24.5760MHz | 2.0480MHz |  |  |

| 44.1kHz | 11.2896MHz | 16.9344MHz | 22.5792MHz | 33.8688MHz | 2.8224MHz |  |  |

| 48.0kHz | 12.2880MHz | 18.4320MHz | 24.5760MHz | 36.8640MHz | 3.0720MHz |  |  |

Table 2. システムクロック例 (Normal Speed Mode @Manual Setting Mode)

| LRCK    |            | BICK       |            |            |           |

|---------|------------|------------|------------|------------|-----------|

| fs      | 128fs      | 192fs      | 256fs      | 384fs      | 64fs      |

| 88.2kHz | 11.2896MHz | 16.9344MHz | 22.5792MHz | 33.8688MHz | 5.6448MHz |

| 96.0kHz | 12.2880MHz | 18.4320MHz | 24.5760MHz | 36.8640MHz | 6.1440MHz |

Table 3. システムクロック例 (Double Speed Mode @Manual Setting Mode)

| LRCK     | MC         | BICK       |            |

|----------|------------|------------|------------|

| fs       | 128fs      | 64fs       |            |

| 176.4kHz | 22.5792MHz | 33.8688MHz | 11.2896MHz |

| 192.0kHz | 24.5760MHz | 36.8640MHz | 12.2880MHz |

Table 4. システムクロック例 (Quad Speed Mode @Manual Setting Mode)

| MC    | LK    | Sampling Speed |  |  |

|-------|-------|----------------|--|--|

| 512fs | 768fs | Normal         |  |  |

| 256fs | 384fs | Double         |  |  |

| 128fs | 192fs | Quad           |  |  |

Table 5. サンプリングスピード(Auto Setting Mode: Default)

| LRCK     |         | MCLK (MHz) |         |         |         |         |                |  |  |  |  |

|----------|---------|------------|---------|---------|---------|---------|----------------|--|--|--|--|

| fs       | 128fs   | 192fs      | 256fs   | 384fs   | 512fs   | 768fs   | Sampling Speed |  |  |  |  |

| 32.0kHz  | -       | -          | -       | -       | 16.3840 | 24.5760 |                |  |  |  |  |

| 44.1kHz  | -       | ı          | -       | -       | 22.5792 | 33.8688 | Normal         |  |  |  |  |

| 48.0kHz  | -       | ı          | -       | -       | 24.5760 | 36.8640 |                |  |  |  |  |

| 88.2kHz  | -       | -          | 22.5792 | 33.8688 | -       | -       | Double         |  |  |  |  |

| 96.0kHz  | -       | ı          | 24.5760 | 36.8640 | -       | -       | Double         |  |  |  |  |

| 176.4kHz | 22.5792 | 33.8688    | -       | -       | -       | -       | Ound           |  |  |  |  |

| 192.0kHz | 24.5760 | 36.8640    | -       | -       | -       | -       | Quad           |  |  |  |  |

Table 6. システムクロック例 (Auto Setting Mode)

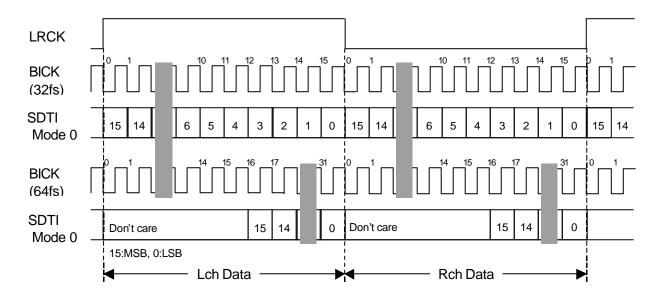

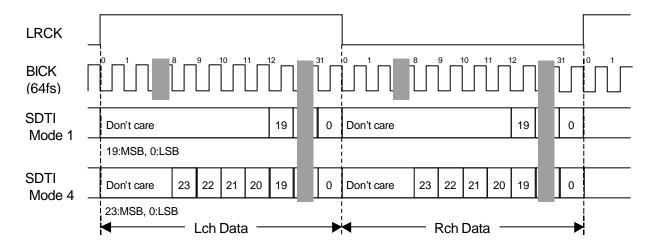

## ■ オーディオシリアルインタフェースフォーマット

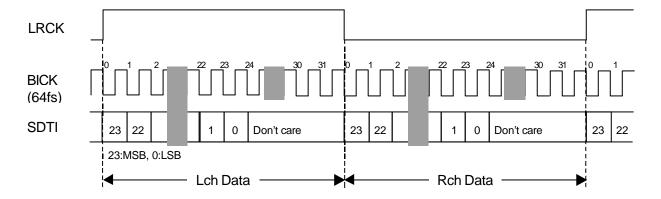

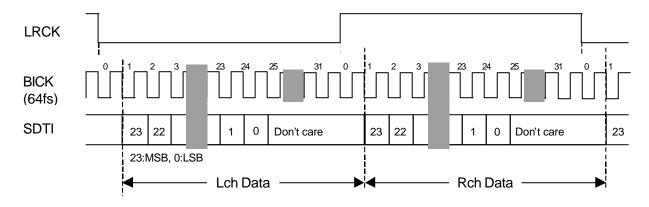

オーディオデータは BICK と LRCK を使って SDTI から入力されます。5 種類のフォーマット (Table 7) が DIF0-2 で選択できます。全モードとも MSB ファースト、2's コンプリメントのデータフォーマットで BICK の立ち上が リでラッチされます。Mode 2 を 16/20ビットで使った場合はデータのない LSB には "0" を入力して下さい。

| Mode | DIF2 | DIF1 | DIF0 | SDTI Format               | BICK  | Figure   |         |

|------|------|------|------|---------------------------|-------|----------|---------|

| 0    | 0    | 0    | 0    | 16bit 後詰め                 | ≥32fs | Figure 1 |         |

| 1    | 0    | 0    | 1    | 20bit 後詰め                 | ≥40fs | Figure 2 |         |

| 2    | 0    | 1    | 0    | 24bit 前詰め                 | ≥48fs | Figure 3 | Default |

| 3    | 0    | 1    | 1    | 24bit I <sup>2</sup> S 互換 | ≥48fs | Figure 4 |         |

| 4    | 1    | 0    | 0    | 24bit 後詰め                 | ≥48fs | Figure 2 |         |

Table 7. オーディオデータフォーマット

Figure 1. Mode 0 Timing

Figure 2. Mode 1,4 Timing

Figure 3. Mode 2 Timing

Figure 4. Mode 3 Timing

## ■ ディエンファシスフィルタ

IIR フィルタによる 3周波数 (32kHz, 44.1kHz, 48kHz) 対応のディエンファシスフィルタ (50/15μs 特性) を内蔵しています。Double Speed Mode, Quad Speed Modeのとき、ディエンファシスフィルタは OFFです。

| 1 |      |      |         | Ī       |  |

|---|------|------|---------|---------|--|

|   | DEM1 | DEM0 | Mode    |         |  |

|   | 0    | 0    | 44.1kHz |         |  |

|   | 0    | 1    | OFF     | Default |  |

|   | 1    | 0    | 48kHz   | ]       |  |

|   | 1    | 1    | 32kHz   |         |  |

Table 8. ディエンファシスコントロール (Normal Speed Mode)

#### ■ 出力ポリューム

AK4382AはMUTEを含むリニアステップ、256レベルのチャネル独立ディジタル出力ボリューム(ATT)を内蔵します。このボリュームはDACの前段にあり入力データを0dBから-48dBまでアテネーション、またはミュートします。設定値間の遷移はソフト遷移です。従って、遷移中にスイッチングノイズは発生しません。1レベル変化したときの遷移時間と256レベル全体の遷移時間をTable 9に示します。

| Sampling Speed    | 遷移時間    |          |  |  |  |  |

|-------------------|---------|----------|--|--|--|--|

|                   | 1 Level | 255 to 0 |  |  |  |  |

| Normal Speed Mode | 4LRCK   | 1020LRCK |  |  |  |  |

| Double Speed Mode | 8LRCK   | 2040LRCK |  |  |  |  |

| Quad Speed Mode   | 16LRCK  | 4080LRCK |  |  |  |  |

Table 9. ATT遷移時間

#### ■ゼロ検出機能

AK4382Aはチャネル独立のゼロ検出機能を持ちます。各チャネルの入力データが8192回連続して"0"の場合、各チャネルのDZFピンが独立に"H"になります。その後各チャネルの入力データが"0"でなくなると対応するチャネルのDZFピンが"L"になります。RSTNビットが"0"の場合、両チャネルのDZFピンが"H"になります。RSTNビットが"0"でなくなると対応するチャネルのDZFピンが4~5LRCK後に"L"になった後各チャネルの入力データが"0"でなくなると対応するチャネルのDZFピンが4~5LRCK後に"L"になります。また、DZFMビットを"1"にすると両チャネルの入力データが8192回連続して"0"の場合のみ両チャネルのDZFピンが"H"になります。ゼロ検出機能はDZFEビットで無効にできます。このとき両チャネルのDZFピンは常に"L"です。DZFピンの極性はDZFBビットで反転することが可能です。

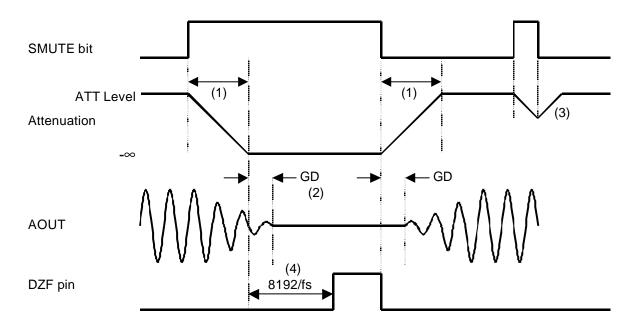

#### ■ ソフトミュート機能

ソフトミュートはディジタル的に実行されます。SMUTEビットを"1"にするとその時点のATT設定値からATT設定値×ATT遷移時間 (Table 9)で入力データが-∞ ("0")までアテネーションされます。SMUTEビットを"0"にすると、-∞状態が解除され、-∞からATT設定値×ATT遷移時間でATT設定値まで復帰します。ソフトミュート開始後、-∞までアテネーションされる前に解除されるとアテネーションが中断され、同じサイクルでATT設定値まで復帰します。ソフトミュート機能は信号を止めずに信号源を切り替える場合などに有効です。

#### 注:

- (1) ATT設定値×ATT遷移時間 (Table 9)。例えば、Normal Speed Mode時、ATT設定値が "255"の場合は1020LRCK サイクルです。

- (2) ディジタル入力に対してアナログ出力は群遅延(GD)を持ちます。

- (3)ソフトミュート開始後、-∞までアテネーションされる前に解除されるとアテネーションが中断され、同じサイクルで0dBまで復帰します。

- (4)入力データが両チャネルともに8192回連続して"0"の場合、DZFピンは"H"になります。 その後入力データが"0"でなくなると、DZFピンはすぐに"L"になります。

Figure 5. ソフトミュート機能とゼロ検出機能

#### ■ システムリセット

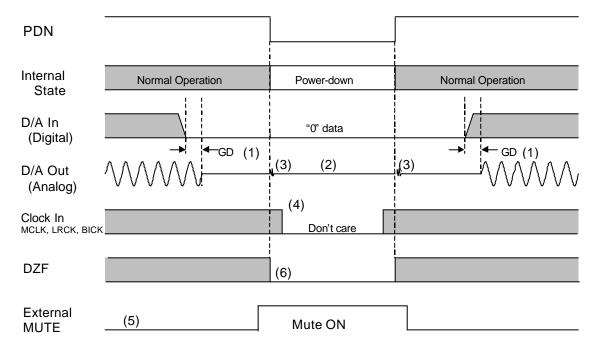

電源 ON時には、PDNピンに一度 "L"を入力してリセットして下さい。リセット及びパワーダウンは MCLK で解除され、その後 LRCKの " $^{\uparrow}$ " に同期して内部回路がパワーアップし、内部のタイミングが動作します。LRCK が入力されるまでパワーダウン状態です。

#### ■ パワーダウン機能

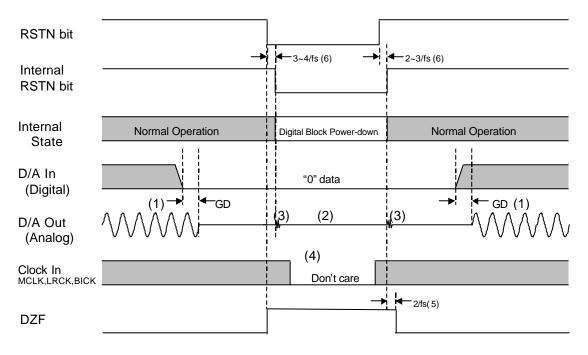

PDNピンを"L"にするとパワーダウン状態になり、アナログ出力はフローティング状態 (Hi-Z) になります。Figure 5 にパワーダウン及びパワーアップ時のシステムタイミング例を示します。

#### 注:

- (1) ディジタル入力に対してアナログ出力は群遅延 (GD) を持ちます。

- (2) パワーダウン時アナログ出力は Hi-Z です。

- (3) PDN信号のエッジ (" $\uparrow \downarrow$ ") でクリックノイズが出力されます。 このノイズはデータが "0" の場合でも出力されます。

- (4) パワーダウン状態(PDN = "L")では各クロック入力(MCLK, BICK, LRCK) を止めることができます。

- (5) クリックノイズ(3) が問題になる場合は、アナログ出力を外部でミュートして下さい。

- (6) パワーダウン状態(PDNピン= "L")では、DZFピンは "L"になります。

Figure 6. パワーダウン/パワーアップ時タイミング例

#### ■ リセット機能

RSTNビットを"0"にすると、DACはリセットされますが、内部レジスタは初期化されません。この時アナログ出力は VCOM電圧になり、DZFL/DZFRピンは"H"になります。Figure 7にRSTNビットによるリセットシーケンスを示します。

#### 注:

- (1) ディジタル入力に対してアナログ出力は群遅延(GD)を持ちます。

- (2) RSTN = "0"時アナログ出力はVCOM電圧(VDD/2)です。

- (3) 内部RSTN信号のエッジ("↓↑")でクリックノイズが出力されます。このノイズはデータが "0"の場合でも出力されます。

- (4) リセット状態 (RSTN = "0")では各クロック入力(MCLK, BICK, LRCK)を止めることができます。

- (5) DZFピンはRSTNビットの立ち下がりエッジで "H"になり、LSI内部のRSTNビットの立ち上がりエッジの 2/fs後 "L"になります。

- (6) RSTNビットを書き込んでからLSI内部のRSTNビットが変化するまでの立ち下がり時に3 ~4/fs かかります。また、立ち上がり時に2 ~ 3/fs かります。

Figure 7. リセットタイミング例

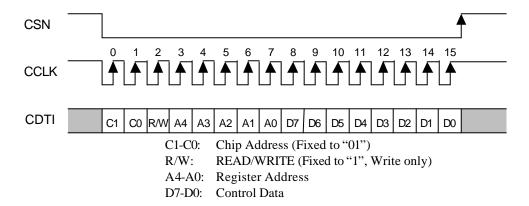

#### ■ モードコントロールインタフェース

AK4382A の各機能はレジスタで設定できます。レジスタ設定は3線式シリアル I/F ピン: CSN, CCLK, CDTI で書き込みを行います。 I/F上のデータは Chip address (2bit, C1/0, "01"固定), Read/Write (1bit, "1"固定, Write only), Register address (MSB first, 5bit)と Control data (MSB first, 8bit)で構成されます。データ送信側はCCLKの "↓" で各ビットを出力し、受信側は "↑" で取り込みます。データの書き込みはCSNの "↑"で有効になります。 CCLKのクロックスピードは5MHz (max)です。アクセスしないときはCSN は "H"に固定して下さい。

PDNピンを "L"にすると内部レジスタ値は初期化されます。また、RSTNビットに "L"を書き込むと内部タイミング回路がリセットされます。但し、このときレジスタの内容は初期化されません。

Figure 8. Control I/F Timing

#### ■ Register Map

| Addr | Register Name | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0    |

|------|---------------|------|------|------|------|------|------|------|-------|

| 00H  | Control 1     | ACKS | 0    | 0    | DIF2 | DIF1 | DIF0 | PW   | RSTN  |

| 01H  | Control 2     | DZFE | DZFM | SLOW | DFS1 | DFS0 | DEM1 | DEM0 | SMUTE |

| 02H  | Control 3     | 0    | 0    | 0    | 0    | 0    | DZFB | 0    | 0     |

| 03H  | Lch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

| 04H  | Rch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

#### Notes:

For addresses from 05H to 1FH, data must not be written.

When PDN pin goes "L", the registers are initialized to their default values.

When RSTN bit goes "0", the only internal timing is reset and the registers are not initialized to their default values. All data can be written to the register even if PW or RSTN bit is "0".

<sup>\*</sup>AK4382Aはデータ読み込みをサポートしません。また、C1/0, R/W は固定 ("011") です。

<sup>\*</sup>PDN="L"時、およびマスタクロックが供給されていない時は、コントロールレジスタへの書き込みはできません。

### ■ Register Definitions

| Addr | Register Name | D7   | D6 | D5 | D4   | D3   | D2   | D1 | D0   |

|------|---------------|------|----|----|------|------|------|----|------|

| 00H  | Control 1     | ACKS | 0  | 0  | DIF2 | DIF1 | DIF0 | PW | RSTN |

|      | default       | 1    | 0  | 0  | 0    | 1    | 0    | 1  | 1    |

RSTN: Internal timing reset control

0: Reset. All registers are not initialized.

1: Normal Operation

When MCLK frequency or DFS changes, the AK4382A should be reset by PDN pin or RSTN bit.

PW: Power down control

0: Power down. All registers are not initialized.

1: Normal Operation

DIF2-0: Audio data interface formats (see Table 7)

Initial: "010", Mode 2

ACKS: Master Clock Frequency Auto Setting Mode Enable

0: Disable, Manual Setting Mode

1: Enable, Auto Setting Mode

Master clock frequency is detected automatically at ACKS bit "1". In this case, the setting of DFS1-0 are ignored. When this bit is "0", DFS1-0 set the sampling speed mode.

| Addr | Register Name | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0    |

|------|---------------|------|------|------|------|------|------|------|-------|

| 01H  | Control 2     | DZFE | DZFM | SLOW | DFS1 | DFS0 | DEM1 | DEM0 | SMUTE |

|      | default       | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0     |

SMUTE: Soft Mute Enable

0: Normal operation

1: DAC outputs soft-muted

DEM1-0: De-emphasis Response (see Table 8)

Initial: "01", OFF

DFS1-0: Sampling speed control

00: Normal Speed Mode

01: Double Speed Mode

10: Quad Speed Mode

When changing between Normal/Double Speed Mode and Quad Speed Mode, some click noise occurs.

SLOW: Slow Roll-off Filter Enable

0: Sharp Roll-off Filter

1: Slow Roll-off Filter

DZFE: Data Zero Detect Enable

0: Disable

1: Enable

Zero detect function can be disabled by DZFE bit "0". In this case, the DZF pins of both channels are always "L".

DZFM: Data Zero Detect Mode

0: Channel Separated Mode

1: Channel ANDed Mode

If the DZFM bit is set to "1", the DZF pins of both channels go to "H" only when the input data at both channels are continuously zeros for 8192 LRCK cycles.

| Addr | Register Name | D7 | D6 | D5 | D4 | D3 | D2   | D1 | D0 |

|------|---------------|----|----|----|----|----|------|----|----|

| 02H  | Control 3     | 0  | 0  | 0  | 0  | 0  | DZFB | 0  | 0  |

|      | default       | 0  | 0  | 0  | 0  | 0  | 0    | 0  | 0  |

DZFB: Inverting Enable of DZF

0: DZF goes "H" at Zero Detection1: DZF goes "L" at Zero Detection

| Addr | Register Name | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|---------------|------|------|------|------|------|------|------|------|

| 03H  | Lch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0 |

| 04H  | Rch ATT       | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0 |

|      | default       | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

$ATT = 20 \log_{10} (ATT_DATA / 255) [dB]$

00H: Mute

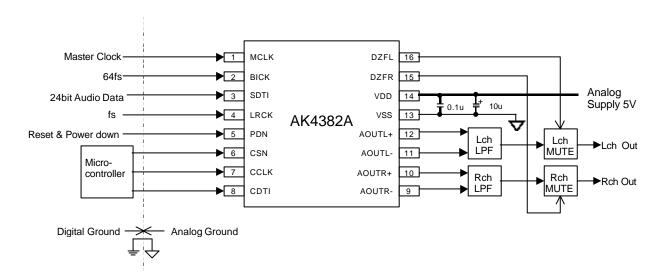

## システム設計

システム接続例をFigure 9 に示します。具体的な回路と測定例については評価用ボード (AKD4382) を参照して下さい。

Figure 9. Typical Connection Diagram

#### Notes:

- LRCK = fs, BICK = 64fs.

- AOUTが容量性負荷を駆動する場合は直列に抵抗を入れて下さい。

- プルダウンピン以外の入力はオープンにしないで下さい。

#### 1. グランドと電源のデカップリング

VDDと VSS にはシステムのアナログ電源を供給し、システムのディジタル電源とは分離して下さい。また、VDD のデカップリングコンデンサ、特に小容量のセラミックコンデンサはできるだけ近づけて接続します。 VDD ピンと VSS ピンの電圧の差がアナログ出力レンジを設定します。

#### 2. アナログ出力

アナログ出力は完全差動出力になっており、出力レンジは2.5Vを中心に $0.55 \times VDD \ Vpp \ (typ)$ 。差動出力は外部で加算されます。 $AOUT+ \& AOUT-の加算電圧はV_{AOUT} = (AOUT+)-(AOUT-)$ です。加算ゲインが1 の場合、出力レンジは $5.5Vpp \ (typ@VDD=5V)$ です。外部加算回路のバイアス電圧は外部で供給されます。入力コードのフォーマットは2's コンプリメント (2 の補数)で $7FFFFFH \ (@24bit)$ に対しては正のフルスケール、 $800000H \ (@24bit)$ に対しては負のフルスケール、 $000000H \ (@24bit)$ での $V_{AOUT}$ の理想値は0V電圧が出力されます。

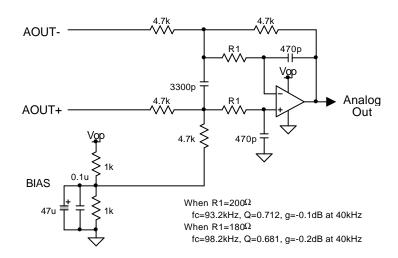

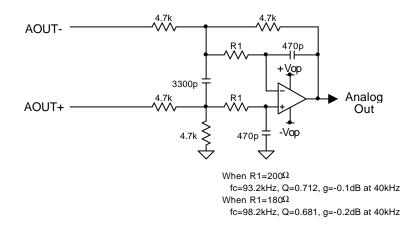

内蔵の $\Delta\Sigma$ 変調器の帯域外ノイズ(シェーピングノイズ)は内蔵のスイッチとキャパシタフィルタ(SCF)で減衰されます。AK4382Aは差動出力であるためDCカット用キャパシタなしでAOUT+/-のDCオフセットを除去することが可能です。Figure 10と11は差動出力をオペアンプで加算する外部 LPF 回路例です。

Figure 10. External 2<sup>nd</sup> order LPF Circuit Example (using op-amp with single power supply)

Figure 11. External 2<sup>nd</sup> order LPF Circuit Example (using op-amp with dual power supplies)

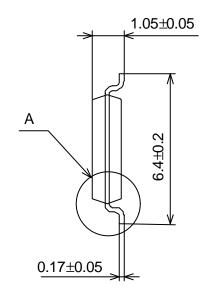

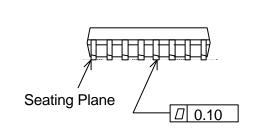

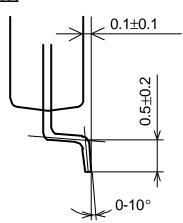

## パッケージ

# 16pin TSSOP (Unit: mm)

#### Detail A

NOTE: Dimension "\*" does not include mold flash.

## ■ 材質・メッキ仕様

パッケージ材質: エポキシ系樹脂

リードフレーム材質: 銅

リードフレーム処理: 半田(無鉛)メッキ

#### マーキング

1) Pin #1 indication

2) Date Code: XXYYY (5 digits)

XX: Lot#

YYY: Date Code

3) Marketing Code : 4382AT

4) Asahi Kasei Logo

#### 重要な注意事項

- 本書に記載された製品、及び、製品の仕様につきましては、製品改善のために予告なく変更することがあります。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社特約店営業担当にご確認下さい。

- ◆ 本書に掲載された情報・図面の使用に起因した第三者の所有する特許権、工業所有権、その他の権利に対する 侵害につきましては、当社はその責任を負うものではありませんので、ご了承下さい。

- 本書記載製品が、外国為替及び、外国貿易管理法に定める戦略物資(役務を含む)に該当する場合、輸出する際に同法に基づく輸出許可が必要です。

- 医療機器、安全装置、航空宇宙用機器、原子力制御用機器など、その装置・機器の故障や動作不良が、直接または間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて高い信頼性を要求される用途に弊社製品を使用される場合は、必ず事前に弊社代表取締役の書面による同意をお取り下さい。

- この同意書を得ずにこうした用途に弊社製品を使用された場合、弊社は、その使用から生ずる損害等の責任を 一切負うものではありませんのでご了承下さい。

- お客様の転売等によりこの注意事項の存在を知らずに上記用途に弊社製品が使用され、その使用から損害等が 生じた場合は全てお客様にてご負担または補償して頂きますのでご了承下さい。