# Image Reject MOPLL with IF AGC Amplifier Preliminary Information

Data Sheet 291305 issue 1 Jun-11

### **DESCRIPTION**

The PS20063 is a 3 band MOPLL with IF AGC amplifier. It down-converts the RF channel to a standard IF with image rejection, simplifying front-end filtering. This is followed by a SAW filter and IF AGC amplification for the digital channel. Each band consists of a low noise preamplifier/mixer and local oscillator with an external varactor tuned tank circuit. An IF level detector is included for control of the RF AGC. The Take Over Point (TOP) and time constant are both programmable.

The PS20063 has excellent signal level handling performance in the presence of high level unwanted signals.

All chip control is via an I C compatible interface.

An alternative part, PS20060, is available without image reject down conversion.

### **APPLICATIONS**

- ATSC and DCR receiver systems

- DVB-T receiver systems

- DVB-C cable receiver systems

- Terrestrial analog receivers

### **Ordering Information**

PS20063C1Q1AT 48 QFN Tape & Reel PS20063C1Q1A5 48 QFN Trays

-20°C to +85°C

# **Equivalent parts:** CE5063 **FEATURES**

- Mixer/oscillator PLL and IF AGC amplifier with image rejection for multi band analog / digital terrestrial tuners and/or cable tuners

- Typically >30dB image rejection

- Low phase noise PLL frequency synthesizer

- AGC output level detect with digital controlled threshold

- >50 dB Desired/Undesired ratio without pre filtering

- · Separate analog and digital IF outputs

- >41 dB IF AGC Control range

- Power down modes to support power reduction initiatives

- Four independent switching ports

- 48 pin QFN Package

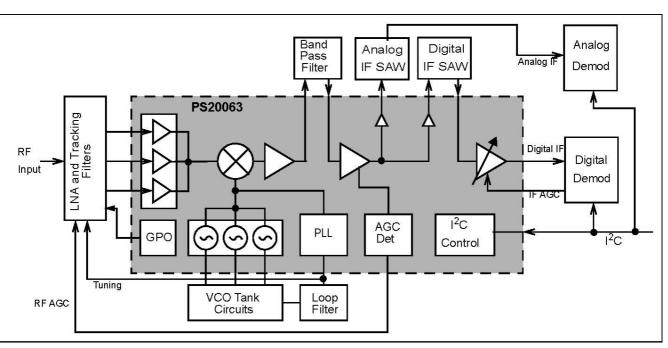

Figure 1 - Basic Block Diagram

# **Table of Contents**

| Features                            | 1  |

|-------------------------------------|----|

| Applications                        |    |

| • •                                 |    |

| Description                         |    |

| Table of Contents                   |    |

| List of Figures                     |    |

| List of Tables                      | 4  |

| 1.0 Functional Description          | 7  |

| 1.1 RF Converter                    |    |

| 1.2 SAW Driver Amplifier            | 8  |

| 1.3 AGC Detector and ADC            |    |

| 1.4 IF AGC Amplifier                |    |

| 1.5 VCO                             | 9  |

| 1.6 PLL Frequency Synthesizer       |    |

| 1.7 General Purpose Switching Ports |    |

| 1.8 I <sup>2</sup> C Interface      | 11 |

| 2.0 Programming                     |    |

| 2.1 Programmable Features           |    |

| 2.2 Register Map                    |    |

| 2.3 Address Register                |    |

| 2.4 PLL Registers                   |    |

| 2.5 Control Register - Byte 5       |    |

| 2.6 Control Register - Byte 6       |    |

| 2.7 Control Register - Byte 7       |    |

| 2.8 Read Mode                       |    |

| 3.0 Applications Information        |    |

| ••                                  |    |

| 4.0 Pln Circuit Information         |    |

| 5.0 Absolute Maximum Ratings        |    |

| 6.0 Operating Range                 | 31 |

| 7.0 Electrical Characteristics      | 32 |

# **List of Figures**

| Figure 1 - Basic Block Diagram                   | . 1 |

|--------------------------------------------------|-----|

| Figure 2 - Pin Diagram                           | . 5 |

| Figure 3 - Detailed Block Diagram                |     |

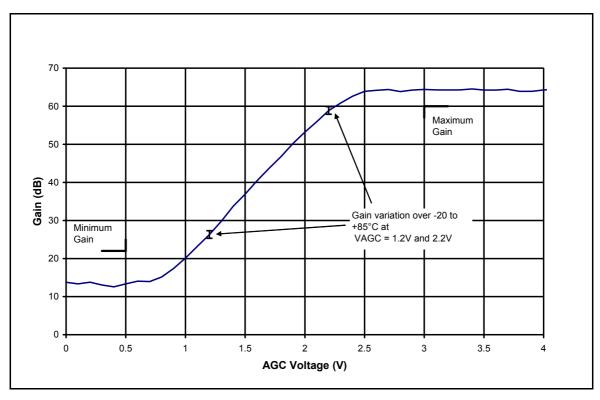

| Figure 4 - Typical AGC Characteristic            | . 9 |

| Figure 5 - Low Band (VHF1) External Tank Circuit | . 9 |

| Figure 6 - Mid Band (VHF3) External Tank Circuit | 10  |

| Figure 7 - High Band (UHF) External Tank Circuit | 10  |

| Figure 8 - Typical Application Circuit (ATSC)    | 21  |

| Figure 9 - Typical Application Circuit (DVBT)    | 22  |

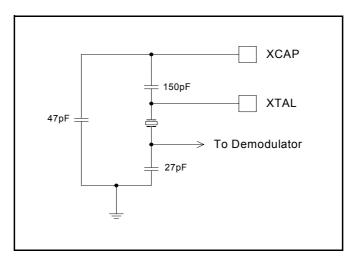

| Figure 10 - Crystal Oscillator Circuit (4 MHz)   | 23  |

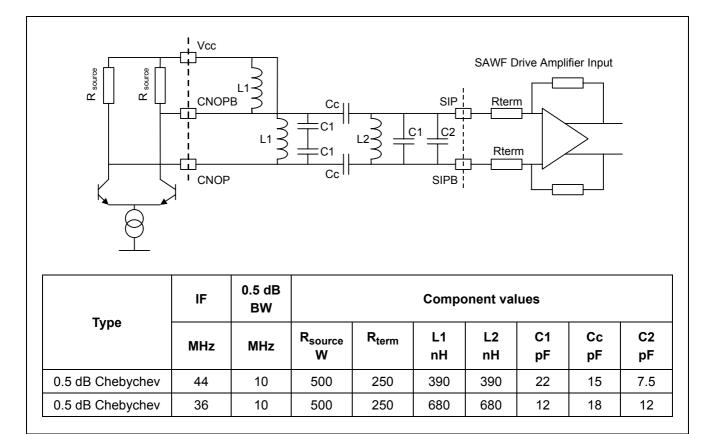

| Figure 11 - Interstage Filter                    | 24  |

PS20063 Data Sheet

# **List of Tables**

| Table 1 - Pin Names                                    | . 5 |

|--------------------------------------------------------|-----|

| Table 2 - Programmable Features                        | 12  |

| Table 3 - Control Registers                            | 13  |

| Table 4 - Address Bit MA1 and MA0 Settings             | 14  |

| Table 5 - Byte 2- LO Divider (MSB)                     | 14  |

| Table 6 - Byte 3 LO Divider (LSB)                      | 14  |

| Table 7 - Byte 4 PLL Control                           | 14  |

| Table 8 - Charge Pump Current Selection                | 15  |

| Table 9 - Reference Divide Ratio Settings              |     |

| Table 10 - Byte 5 Control                              | 16  |

| Table 11 - Band Selection                              |     |

| Table 12 - Internal Circuit Block Control              |     |

| Table 13 - GPPO Output Port Control                    |     |

| Table 14 - Byte 6 Control                              |     |

| Table 15 - AGC Decay Current Setting                   |     |

| Table 16 - AGC Threshold Selection                     |     |

| Table 17 - Byte 7 Control                              |     |

| Table 18 - ADC Input Selection                         |     |

| Table 19 - Test Modes                                  |     |

| Table 20 - Read Data Format (MSB is transmitted first) |     |

| Table 21 - AGC Activity Flag Settings                  |     |

| Table 22 - ADC Output Values                           |     |

| Table 23 - Optimum CP and LO Trim Settings             | 25  |

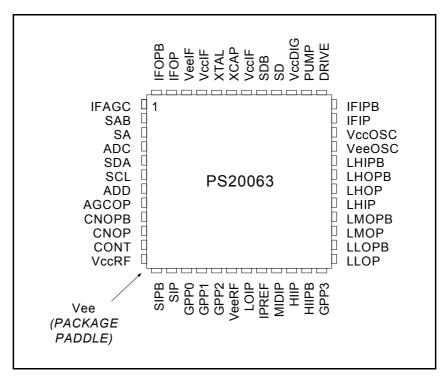

Figure 2 - Pin Diagram

| Pin No. | Port Name | Function                                      |  |

|---------|-----------|-----------------------------------------------|--|

| 1       | IFAGC     | IF amplifier AGC input                        |  |

| 2       | SAB       | Angles CAM filter driver differential autoute |  |

| 3       | SA        | Analog SAW filter driver differential outputs |  |

| 4       | ADC       | External ADC input                            |  |

| 5       | SDA       | I <sup>2</sup> C bus serial data input/output |  |

| 6       | SCL       | I <sup>2</sup> C bus serial clock input       |  |

| 7       | ADD       | I <sup>2</sup> C bus address selection input  |  |

| 8       | AGCOP     | AGC output                                    |  |

| 9       | CNOPB     | Converter differential outputs                |  |

| 10      | CNOP      | Converter differential outputs                |  |

| 11      | CONT      | Paddle (Ground)                               |  |

| 12      | VccRF     | RF section supply                             |  |

| 13      | SIPB      | CAM/ filter driver differential inputs        |  |

| 14      | SIP       | SAW filter driver differential inputs         |  |

| 15      | GPP0      | General purpose switching port                |  |

| 16      | GPP1      | General purpose switching port                |  |

Table 1 - Pin Names

| Pin No. | Port Name | Function                                       |  |  |  |

|---------|-----------|------------------------------------------------|--|--|--|

| 17      | GPP2      | General purpose switching port                 |  |  |  |

| 18      | VeeRF     | RF section ground                              |  |  |  |

| 19      | LOIP      | Low band (VHF1) input                          |  |  |  |

| 20      | IPREF     | Reference input for low and mid band inputs    |  |  |  |

| 21      | MIDIP     | Mid band (VHF3) input                          |  |  |  |

| 22      | HIIP      | LEST Frank (IIIIE) Effects of the              |  |  |  |

| 23      | HIIPB     | High band (UHF) differential inputs            |  |  |  |

| 24      | GPP3      | General purpose switching port                 |  |  |  |

| 25      | LLOP      |                                                |  |  |  |

| 26      | LLOPB     | Low band local oscillator outputs              |  |  |  |

| 27      | LMOP      | Mid houselle of confliction outside            |  |  |  |

| 28      | LMOPB     | Mid band local oscillator outputs              |  |  |  |

| 29      | LHIP      | High band local oscillator input               |  |  |  |

| 30      | LHOP      | High hand lacel accillator autoute             |  |  |  |

| 31      | LHOPB     | High band local oscillator outputs             |  |  |  |

| 32      | LHIPB     | High band local oscillator inverse input       |  |  |  |

| 33      | VeeOSC    | Oscillator section ground                      |  |  |  |

| 34      | VccOSC    | Oscillator supply                              |  |  |  |

| 35      | IFIP      | IT ACC condition differential insula           |  |  |  |

| 36      | IFIPB     | IF AGC amplifier differential inputs           |  |  |  |

| 37      | DRIVE     | PLL Loop amplifier drive output                |  |  |  |

| 38      | PUMP      | PLL Loop amplifier charge pump output          |  |  |  |

| 39      | VccDIG    | Digital section supply                         |  |  |  |

| 40      | SD        | Digital SAW filter driver differential autoute |  |  |  |

| 41      | SDB       | Digital SAW filter driver differential outputs |  |  |  |

| 42      | VccIF     | IF amplifier section supply                    |  |  |  |

| 43      | XCAP      | Reference oscillator feedback input            |  |  |  |

| 44      | XTAL      | Reference oscillator crystal drive             |  |  |  |

| 45      | VccIF     | IF amplifier section supply                    |  |  |  |

| 46      | VeelF     | IF section ground                              |  |  |  |

| 47      | IFOP      | IF ACC amplifier differential outputs          |  |  |  |

| 48      | IFOPB     | IF AGC amplifier differential outputs          |  |  |  |

| Paddle  | Vee       | Global ground                                  |  |  |  |

Table 1 - Pin Names (continued)

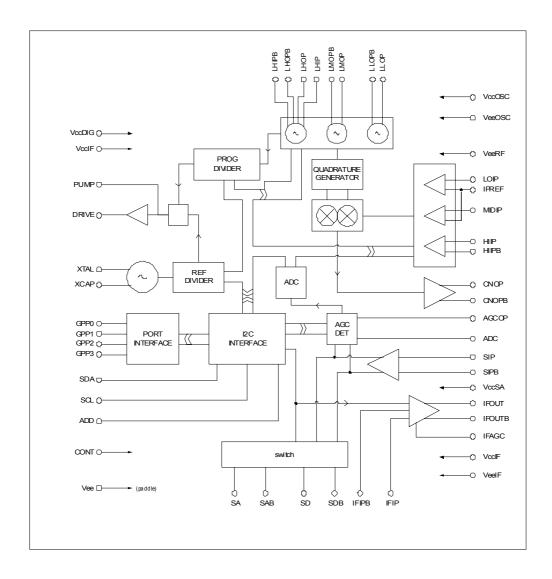

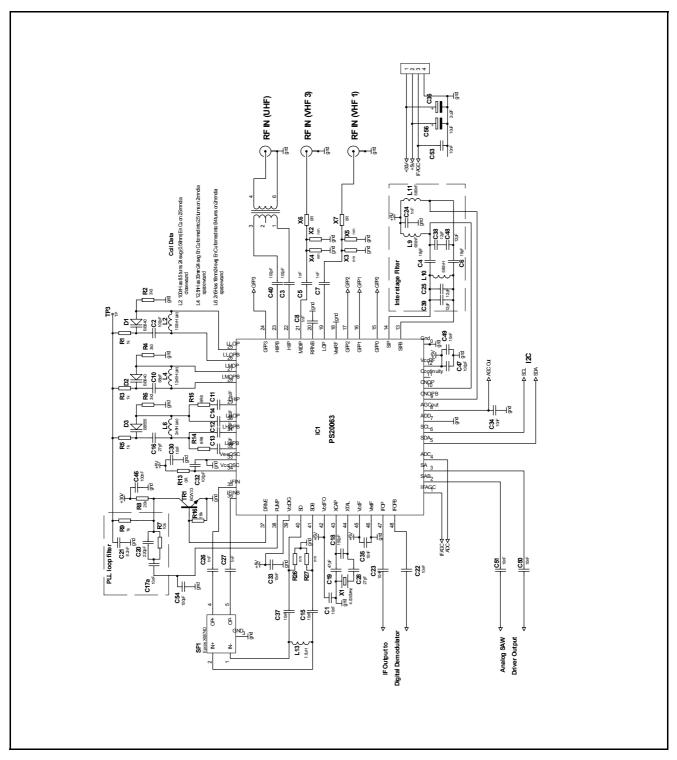

Figure 3 - Detailed Block Diagram

# 1.0 Functional Description

The PS20063 is a three-band RF mixer oscillator with image rejection, with on-board frequency synthesizer and IF AGC amplifier, integrating all tuner active circuitry after the tracking filter into a single package.

It is intended for use in all band terrestrial tuners, and requires a minimum external component count. It contains all elements required for RF down conversion to a standard IF, with the exception of external VCO tank circuits.

In normal applications, the RF input is interfaced to the selected mixer oscillator preamplifier through the tuner prefilter and AGC stages. The PS20063 provides an RF AGC control signal, which can be used to control the RF gain.

The preamplifier output feeds the image rejection mixer stage where the required channel is down converted to the IF frequency. The local oscillator frequency for the down conversion is obtained from the on board PLL and local oscillator, with an external varactor tuned tank.

The downconverted signal is then passed through an external filter into a SAW filter driver amplifier. This provides two output channels for hybrid analog and digital applications.

An AGC IF amplifier is included which provides an output signal to a digital demodulator.

The device is controlled through an I<sup>2</sup>C compatible interface.

### 1.1 RF Converter

The PS20063 contains three input stages to cover the VHF1, VHF3 and UHF frequency bands. The inputs would normally be driven by front end amplifiers and tracking filters. All three inputs are differential, however, the VHF1 and VHF3 inputs would normally be driven single ended. These inputs therefore can share a common input reference pin. The UHF input should be driven with a differential signal. The inputs are all high impedance. The differential converter IF output is then passed through an external interstage filter. This can be tuned for 44 MHz for ATSC applications but can also be used at 36 MHz to be compatible with other TV standards. The recommended filter circuit is shown in Figure 11. The design of this filter provides an impedance transformation as well as rejection of adjacent channels. A 0.5 dB Chebychev filter with 10 MHz bandwidth is recommended. This gives a flat response across the pass band and takes into account normal component tolerances.

### 1.2 SAW Driver Amplifier

The output of the interstage filter then passes to the SAW filter drive amplifier. This provides further amplification and interfaces to the SAW filter. Two SAW filter drive outputs are provided for hybrid analog and digital applications. Both output stages are identical, however, the digital output (SD, SDB) should always be used for digital applications, as the pin out of the device has been optimized to give the best isolation performance in this configuration. Output selection is programmable however it should be noted that the unselected output is not powered off but operates at a lower power level which means that a signal will still be present on the output, but with reduced output drive capability.

The differential outputs will drive a balanced SAW filter with a tuning inductor to resonate with the SAW filter input capacitance. The SAW filter can also be driven without the tuning inductor but this requires the addition of 360 ohm resistors to ground on the SAW driver outputs to increase the output drive capability. This will increase total current consumption by approximately 14 mA.

### 1.3 AGC Detector and ADC

The PS20063 contains a broadband AGC detector circuit which provides an output to provide gain control for the RF frontend gain stages. The detector input signal is derived from the signal level in the SAW driver amplifier. The composite signal at this point is the wanted signal plus adjacent channels (N +/- 1, N +/- 2, N +/- 3). The AGC detector threshold point at which the agc output becomes active can be programmed to one of eight levels via the  $I^2C$  interface. When the composite level reaches the agc threshold, the agc output pin will be active. The AGC attack current is fixed, however, the decay current can be programmed to two levels. The agc output can only drive a high impedance e.g., a dual gate FET. If RF gain control uses a PiN diode then a simple buffer circuit will be required.

An AGC flag output is also available through the I<sup>2</sup>C interface. This indicates when the AGC output is active i.e., less than 4 volts.

The agc output level can also be monitored by an on chip 3 bit ADC. Although the ADC is 3 bits, only 5 levels are available. Alternatively the ADC can be programmed to measure the voltage on an external pin (ADC Pin 4).

### 1.4 IF AGC Amplifier

The AGC amplifies the output of the SAW filter for the digital channel and provides a differential output to the demodulator. The analog gain control signal is normally derived from the demodulator. At least 41 dB of gain control is provided.

The AGC amplifier can be powered down independently of the rest of the device if not required. This mode could be used in analog applications to reduce overall power consumption.

Figure 4 - Typical AGC Characteristic

# 1.5 VCO

Separate VCO's are provided for each band. The oscillator circuits are on chip, however, the tank circuitry is external. All three oscillators are differential. The typical external tank circuits are shown in Figures 5, 6 and 7. It is essential to take care to minimize track lengths and parasitics when designing the PCB layout to obtain best performance. The close-in phase noise of the local oscillator can be optimized at the programmed operating frequency by a programming bit which increases bias current in the VCO.

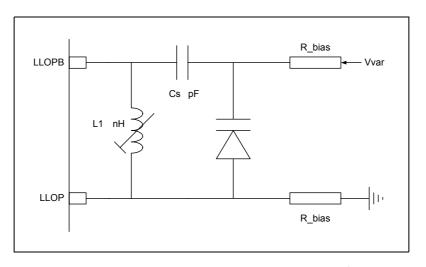

Figure 5 - Low Band (VHF1) External Tank Circuit

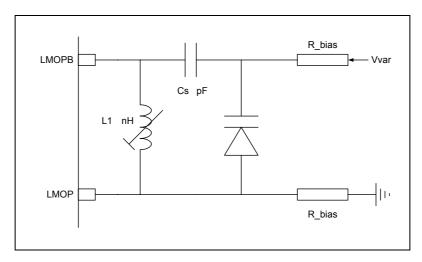

Figure 6 - Mid Band (VHF3) External Tank Circuit

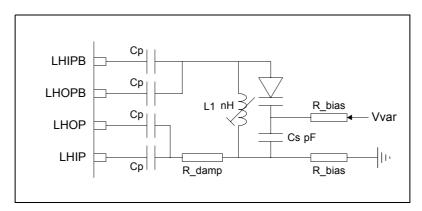

Figure 7 - High Band (UHF) External Tank Circuit

### 1.6 PLL Frequency Synthesizer

The PLL frequency synthesizer section contains all the elements necessary, with the exception of a frequency reference and loop filter to control a varicap tuned local oscillator, to form a complete PLL frequency synthesized source. The device allows operation with a high comparison frequency and is fabricated in high speed logic, which enables the generation of a loop with good phase noise performance. It can be operated with comparison frequencies appropriate for frequency offsets as required in digital terrestrial (DTT) receivers.

The LO input signal from the selected oscillator section is routed to an internal preamplifier, which provides gain and reverse isolation from the divider signals. The output of the preamplifier interfaces directly to the 15-bit programmable divider, which is of MN+A architecture, with a 16/17 dual modulus prescaler. The A counter is 4-bits, and the M counter is 11 bits.

The output of the programmable divider is fed to the phase detector together with the comparison frequency, which is derived either from the on-board crystal controlled oscillator, or from an external reference source. In both cases the reference frequency is divided down to the comparison frequency by the reference divider, which is programmable into 1 of 16 ratios.

The output of the phase detector feeds a charge pump and loop amplifier section, which when used with an external loop filter, integrates the current pulses into the varactor control voltage.

Test modes allow both the divider outputs to be monitored via output port GPP0 for debug and test purposes.

The PLL includes a lock detect circuit. The lock detect output is available by reading the Status byte on the I<sup>2</sup>C interface

### 1.7 General Purpose Switching Ports

The PS20063 has four output switching ports. Three of these ports (GPP[3:1]) incorporate a 10 kohm pull up resistor. The remaining port (GPP0) is an open collector switch. These ports can be used for switching external RF input stages for example. Ports GPP[1:0] can also be used as test outputs for debug purposes.

# 1.8 I<sup>2</sup>C Interface

The PS20063 is controlled by an I<sup>2</sup>C data bus and is compatible with both 3.3 V and 5 V control levels.

Data and Clock are fed in on the SDA and SCL lines respectively as defined by  $I^2C$  bus format. The device can either accept data (write mode), or send data (read mode). The LSB of the address byte (R/W) sets the device into write mode if it is low, and read mode if it is high. The device can be programmed to respond to 1 of 4 addresses, which enables the use of more than one device in an  $I^2C$  bus system. The address is selected by applying a voltage to the 'ADD' input.

When the device receives a valid address byte, it pulls the SDA line low during the acknowledge period, and during following acknowledge periods after further data bytes are received. When the device is programmed into read mode, the controller accepting the data must pull the SDA line low during all status byte acknowledge periods to read another status byte. If the controller fails to pull the SDA line low during this period, the device generates an internal STOP condition, which inhibits further reading.

### 2.0 Programming

The PS20063 is fully programmable through the I<sup>2</sup>C interface. The device can also output data to the controller.

### 2.1 Programmable Features

| Feature                                                                                                                                                      | Description                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| RF programmable divider                                                                                                                                      | Programs PLL main divider                                                                              |  |  |  |  |

| Reference programmable divider                                                                                                                               | Programs PLL reference divider to set required frequency step                                          |  |  |  |  |

| Band selection                                                                                                                                               | Selects RF input and appropriate LO oscillator.                                                        |  |  |  |  |

| AGC Threshold                                                                                                                                                | Sets the Input Power Level Threshold at which the AGC detector starts to generate a control level.     |  |  |  |  |

| AGC Decay Sets the AGC decay current.                                                                                                                        |                                                                                                        |  |  |  |  |

| Charge pump current Selects one of the four charge pump current settings.                                                                                    |                                                                                                        |  |  |  |  |

| IF amplifier function The IF amplifier can be enabled independently of other circuit blocks.                                                                 |                                                                                                        |  |  |  |  |

| SAWF output select                                                                                                                                           | Select the analog or digital SAW driver output.                                                        |  |  |  |  |

| Ports GPP[3:1] These are configured as NPN buffers with 10 kohm pull-up resistors to V <sub>cc</sub> .  Logic '1' = on  Logic '0' = off; default on power up |                                                                                                        |  |  |  |  |

| PORT GPP0                                                                                                                                                    | This is configured as a NPN open collector buffer. Logic '1' = on Logic '0' = off; default on power up |  |  |  |  |

| LO Trim                                                                                                                                                      | Allows adjustment of VCO bias current and LO gain to provide optimum phase noise performance.          |  |  |  |  |

| ADC input Select                                                                                                                                             | Select either the internal AGC detect output level or the external level applied to the ADC input pin. |  |  |  |  |

| Programmable power                                                                                                                                           | The PS20063 has various power saving modes.                                                            |  |  |  |  |

| Test modes                                                                                                                                                   | Test modes to monitor and control internal PLL signals.                                                |  |  |  |  |

**Table 2 - Programmable Features**

### 2.2 Register Map

There are a total of 7 write registers, the first of which is the Address register. The control registers are described in detail in the following section. The MSB of each register is written first.

After reception and acknowledgement of a correct address (Byte 1), the MSB of the following byte determines whether that byte is interpreted as a Byte 2 or Byte 4; a logic '0' indicating Byte 2, and a logic '1' indicating Byte 4. The next data byte will then be interpreted as Byte 3 or Byte 5 respectively. Byte 5 can be followed by Byte 6 and Byte 7 if required. A STOP condition can be generated after any data byte, however, if it occurs during a byte transmission, the previous byte data is retained. To facilitate smooth tuning, the frequency data bytes are only accepted by the device after all 15 bits of frequency data (i.e. Bytes 2 and 3) have been received, or after the generation of a STOP condition. It should also be noted that if it is necessary to program Bytes 6 or 7, then Bytes 4 and 5 must be programmed at the same time

|                      | MSB |     |     |     |     |     |     | LSB | ACK |         |

|----------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|

|                      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |     |         |

| Address              | 1   | 1   | 0   | 0   | 0   | MA1 | MA0 | 0   | Α   | Byte 1  |

| Programmable divider | 0   | D14 | D13 | D12 | D11 | D10 | D9  | D8  | Α   | Byte 2W |

| Programmable divider | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Α   | Byte 3W |

| Control data         | 1   | C1  | C0  | R4  | R3  | R2  | R1  | R0  | Α   | Byte 4W |

| Control data         | BS1 | BS0 | SL1 | SL0 | P3  | P2  | P1  | P0  | Α   | Byte 5W |

| Control Data         | LO1 | LO0 | ATC | IFE | Х   | AT2 | AT1 | AT0 | Α   | Byte 6W |

| Control Data         | SAS | Х   | AGD | ADS | T3  | T2  | T1  | T0  | Α   | Byte 7W |

**Table 3 - Control Registers**

| Α        | Acknowledge bit                          |

|----------|------------------------------------------|

| MA1, MA0 | Address bits                             |

| D14-D0   | Programmable division ratio control bits |

| R4-R0    | Reference division ratio select          |

| C1, C0   | Charge pump current select               |

| BS1-BS0  | Band select bits                         |

| SL1-SL0  | Power down modes                         |

| SAS      | SAWF drive output select                 |

| P3-P0    | P3-P0 port output states                 |

| ADS      | ADC input select                         |

| ATC      | AGC Decay Current                        |

| AGD      | AGC Disable                              |

| AT2:AT0  | AGC Onset threshold Control              |

| LO1:LO0  | LO trim control bits                     |

| T3-T0    | Test mode control bits                   |

| IFE      | IF AGC amplifier enable                  |

| Χ        | Don't Care                               |

Details of the programming registers are shown in the following sections. Default values on power up are also shown.

#### 2.3 Address Register

The PS20063 address (MA1, MA0) are determined by the voltage set at the address pin (ADD) as shown in Table 4.

| Address Select (Byte 1) |     |                                                                                                     |  |  |  |  |  |

|-------------------------|-----|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MA1                     | MA0 | Address Input Voltage Level                                                                         |  |  |  |  |  |

| 0                       | 0   | 0 - 0.1Vcc (Connect to V <sub>ee</sub> )                                                            |  |  |  |  |  |

| 0                       | 1   | 0.2V <sub>cc</sub> – 0.3V <sub>cc</sub> (Open circuit)                                              |  |  |  |  |  |

| 1                       | 0   | $0.4 \text{ V}_{\text{cc}}$ – $0.6 \text{ V}_{\text{cc}}$ (30K $\Omega$ to $\text{V}_{\text{cc}}$ ) |  |  |  |  |  |

| 1                       | 1   | 0.9 V <sub>cc</sub> - 1.0 V <sub>cc</sub> (Connect to V <sub>cc</sub> )                             |  |  |  |  |  |

Table 4 - Address Bit MA1 and MA0 Settings

# 2.4 PLL Registers

Bytes 2,3 and 4 are used to program the PLL.

| Bit Field | Name    | Default | Description                      |

|-----------|---------|---------|----------------------------------|

| 7         | -       | 0       | Must be set to 0 (Byte 2)        |

| 6:0       | D[14:8] | 0       | MSB bits of LO Divider register. |

Table 5 - Byte 2- LO Divider (MSB)

| Bit Field | Name   | Default | Description                      |

|-----------|--------|---------|----------------------------------|

| 7:0       | D[7:0] | 0       | LSB bits of LO Divider register. |

Table 6 - Byte 3 LO Divider (LSB)

The LO frequency will not be updated until both Byte 1 and Byte 2 have been programmed.

| Bit Field | Name   | Default | Description                |

|-----------|--------|---------|----------------------------|

| 7         | -      | 1       | Must be set to 1 (Byte 4)  |

| 6:5       | C[1:0] | 0       | Charge pump current.       |

| 4:0       | R[4:0] | 10011   | Reference divider control. |

Table 7 - Byte 4 PLL Control

The charge pump current values are selected from the following table

:

| C1                             | C0 | Current |  |  |  |

|--------------------------------|----|---------|--|--|--|

|                                |    | μΑ      |  |  |  |

| 0                              | 0  | +-155   |  |  |  |

| 0                              | 1  | +-330   |  |  |  |

| 1                              | 0  | +-690   |  |  |  |

| 1 1 +-1450                     |    |         |  |  |  |

| Default State on power up = 00 |    |         |  |  |  |

**Table 8 - Charge Pump Current Selection**

The reference divider ratio can be selected from the following table:

| R4                                | R3 | R2 | R1 | R0 | Ratio |

|-----------------------------------|----|----|----|----|-------|

| 0                                 | 0  | 0  | 1  | 1  | 16    |

| 0                                 | 0  | 1  | 0  | 0  | 32    |

| 0                                 | 0  | 1  | 0  | 1  | 64    |

| 0                                 | 0  | 1  | 1  | 0  | 128   |

| 0                                 | 1  | 0  | 1  | 1  | 20    |

| 0                                 | 1  | 1  | 0  | 0  | 40    |

| 0                                 | 1  | 1  | 0  | 1  | 80    |

| 0                                 | 1  | 1  | 1  | 0  | 160   |

| 1                                 | 0  | 0  | 1  | 1  | 24    |

| 1                                 | 0  | 1  | 0  | 0  | 48    |

| 1                                 | 0  | 1  | 0  | 1  | 96    |

| 1                                 | 0  | 1  | 1  | 0  | 192   |

| 1                                 | 1  | 0  | 1  | 1  | 28    |

| 1                                 | 1  | 1  | 0  | 0  | 56    |

| 1                                 | 1  | 1  | 0  | 1  | 112   |

| 1                                 | 1  | 1  | 1  | 0  | 224   |

| Default State on power up = 10011 |    |    |    |    |       |

**Table 9 - Reference Divide Ratio Settings**

# 2.5 Control Register - Byte 5

| Bit Field | Name    | Default | Description                  |

|-----------|---------|---------|------------------------------|

| 7:6       | BS[1:0] | 11      | Band Switching               |

| 5:4       | SL[1:0] | 01      | Power-up modes               |

| 3:0       | P[3:0]  | 0       | General Purpose Output ports |

Table 10 - Byte 5 Control

The band switching is controlled as shown below:

| BS1 | BS0 | Band Selected                  |

|-----|-----|--------------------------------|

| 0   | 0   | LO Band                        |

| 0   | 1   | MID Band                       |

| 1   | 0   | HI band                        |

| 1   | 1   | All off                        |

|     |     | Default state on power up = 11 |

**Table 11 - Band Selection**

The various power-up modes are shown below. The IF AGC amplifier is controlled separately by IFE bit (see table 14). The I<sup>2</sup>C interface and crystal oscillator circuit are active in all modes.

|     |     | Power Mode             | Section Status                              |                       |           |                         |

|-----|-----|------------------------|---------------------------------------------|-----------------------|-----------|-------------------------|

| SL1 | SL0 |                        | I <sup>2</sup> C interface<br>and registers | Crystal<br>oscillator | PLL & VCO | Converter and IF stages |

| 0   | Х   | Sleep                  | Enabled                                     | Enabled               | Disabled  | Disabled                |

| 1   | 0   | PLL and<br>VCO enabled | Enabled                                     | Enabled               | Enabled   | Disabled                |

| 1   | 1   | Full                   | Enabled                                     | Enabled               | Enabled   | Enabled                 |

Table 12 - Internal Circuit Block Control

The PS20063 has four output ports. Ports GPP[3:1] each have an internal 10 kohm pull up resistor to Vcc. GPP0 is open collector.

| Function           | Bit | 0                    | 1                 |

|--------------------|-----|----------------------|-------------------|

| GPP0 output Enable | P0  | Off (High Impedance) | On (Current Sink) |

| GPP1 output Enable | P1  | Off                  | On (Current Sink) |

| GPP2 output Enable | P2  | Off                  | On (Current Sink) |

| GPP3 output Enable | P3  | Off                  | On (Current Sink) |

**Table 13 - GPPO Output Port Control**

Tel: +44 1793 518000

### 2.6 Control Register - Byte 6

| Bit Field | Name    | Default | Description                      |

|-----------|---------|---------|----------------------------------|

| 7         | LO1     | 0       | VCO Bias Trim                    |

| 6         | LO0     | 0       | LO Gain Adjust                   |

| 5         | ATC     | 0       | AGC Decay current select         |

| 4         | IFE     | 0       | IF AGC Amplifier enable (1 = On) |

| 3         | X       | 0       | Not used                         |

| 2:0       | AT[2:0] | 0       | AGC Threshold Select             |

Table 14 - Byte 6 Control

The VCO bias trim adjusts the VCO bias to give optimum close-in phase noise. In general this should be set to 1 for the lower third of the VCO frequency range.

The LO gain adjust increases the gain of the LO drive circuit. Setting this bit to '1' can improve the far-out phase noise performance.

The AGC attack current is fixed at 100 μA, however, the agc decay current can be programmed to one of two values as shown below. If the PLL is unlocked (FL = 0), then the ATC control is over-ridden and the AGC decay current is set to  $10\mu A$ . When the PLL locks (FL = 1) the decay current reverts to the programmed ATC value. The decay current is always present even when the attack current is on. This means that if the 10µA decay current is selected, then the effective attack current is reduced to 90µA

| ATC | AGC Decay Current (μA) |  |  |  |

|-----|------------------------|--|--|--|

| 0   | 10.0                   |  |  |  |

| 1   | 0.3                    |  |  |  |

**Table 15 - AGC Decay Current Setting**

The AGC threshold can be programmed using the AT[2:0] bits. Note that the programmed value is dB<sub>μ</sub>V peak. This is the signal level at the SAW driver outputs.

| AT2 | AT1 | AT0 | AGC Threshold<br>(peak signal in dBμV into detector) |

|-----|-----|-----|------------------------------------------------------|

| 0   | 0   | 0   | 120                                                  |

| 0   | 0   | 1   | 118                                                  |

| 0   | 1   | 0   | 116                                                  |

| 0   | 1   | 1   | 114                                                  |

| 1   | 0   | 0   | 112                                                  |

| 1   | 0   | 1   | 110                                                  |

| 1   | 1   | 0   | 107                                                  |

| 1   | 1   | 1   | 104                                                  |

|     |     |     | Default state on power up = 000                      |

**Table 16 - AGC Threshold Selection**

Tel: +44 1793 518000

# 2.7 Control Register - Byte 7

| Bit Field | Name   | Default | Description                                   |

|-----------|--------|---------|-----------------------------------------------|

| 7         | SAS    | 1       | Digital SAW Drive Output Select (1 = Digital) |

| 6         | Х      | 0       | Not used                                      |

| 5         | AGD    | 1       | AGC Detector Enable (0 = Enabled)             |

| 4         | ADS    | 0       | ADC Input select                              |

| 3:0       | T[3:0] | 0       | Test Bits                                     |

Table 17 - Byte 7 Control

The ADC input selection is shown in the table below

| ADS | ADC Function       |  |  |  |

|-----|--------------------|--|--|--|

| 0   | AGC Output         |  |  |  |

| 1   | External ADC input |  |  |  |

**Table 18 - ADC Input Selection**

The test bits T[3:0] allow internal PLL signals to be monitored and also to manually control charge pump current and AGC detector output. This facility may be useful during debug. The test bit selection is shown below. The reserved test modes should not be used.

| Т3 | T2 | T1 | T0 | Test Mode Description                                                          |

|----|----|----|----|--------------------------------------------------------------------------------|

| 0  | 0  | 0  | 0  | Normal operation                                                               |

| 0  | 0  | 0  | 1  | Reserved Test Mode                                                             |

| 0  | 0  | 1  | 0  | AGC Sink, Force $I_{agc}$ = -100 $\mu$ A                                       |

| 0  | 0  | 1  | 1  | AGC Source, Force $I_{agc}$ = 10 $\mu$ A P0 = Output of AGC bias DAC           |

| 0  | 1  | 0  | 0  | Reserved Test Mode                                                             |

| 0  | 1  | 0  | 1  | Reserved Test Mode                                                             |

| 0  | 1  | 1  | 0  | Reserved Test Mode                                                             |

| 0  | 1  | 1  | 1  | Reserved Test Mode                                                             |

| 1  | 0  | 0  | 0  | Reserved Test Mode                                                             |

| 1  | 0  | 0  | 1  | Charge pump sink * Status byte FL set to logic '0'                             |

| 1  | 0  | 1  | 0  | Charge pump source * Status byte FL set to logic '0'                           |

| 1  | 0  | 1  | 1  | Charge pump disabled * Status byte FL set to logic '1'                         |

| 1  | 1  | 0  | 0  | Port P0 = $F_{pd}/2$                                                           |

| 1  | 1  | 0  | 1  | Charge pump sink * Status byte FL set to logic '0' Port P0 = F <sub>comp</sub> |

Table 19 - Test Modes

Tel: +44 1793 518000

| Т3 | T2 | T1 | T0 | Test Mode Description                                                              |

|----|----|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | 1  | 0  | Charge pump source * Status byte FL set to logic '0' Port P0 = F <sub>comp</sub>   |

| 1  | 1  | 1  | 1  | Charge pump disabled * Status byte FL set to logic '1' Port P0 = F <sub>comp</sub> |

Table 19 - Test Modes (continued)

### 2.8 Read Mode

When the device is in read mode, the status byte read from the device takes the form shown in Table 20.

|             | MSB |    |   |   |     |     |     | LSB | ACK |         |

|-------------|-----|----|---|---|-----|-----|-----|-----|-----|---------|

|             | 7   | 6  | 5 | 4 | 3   | 2   | 1   | 0   |     |         |

| Address     | 1   | 1  | 0 | 0 | 0   | MA1 | MA0 | 1   | Α   | Byte 1  |

| Status Byte | POR | FL | 0 | 0 | AGF | V2  | V1  | V0  | Α   | Byte 2R |

Table 20 - Read Data Format (MSB is transmitted first)

The following data read is accessed from the read byte;

**Bit 7 (POR)** is the power-on reset indicator, and this is set to a logic '1' if the  $V_{cc}$  supply to the device has dropped below 3 V (at 25°C), e.g., when the device is initially turned ON. The POR is reset to '0' when the read sequence is terminated by a STOP command. When POR is set high this indicates that the programmed information may have been corrupted and the device reset to power up condition.

**Bit 6 (FL)** is the PLL lock flag and indicates whether the device is phase locked, a logic '1' is present if the device is locked, and a logic '0' if the device is unlocked. The FL bit is set after 64 consecutive comparison cycles in lock.

Bit 3 (AGF) is the AGC detector flag and indicates if RF AGC control is active

| AGF | AGC Activity Flag                                                           |

|-----|-----------------------------------------------------------------------------|

| 0   | AGC active, V <sub>AGC</sub> < 4 V<br>External RF LNA gain is reduced       |

| 1   | AGC not active, V <sub>AGC</sub> >4 V<br>External RF LNA gain is at maximum |

**Table 21 - AGC Activity Flag Settings**

Bits 2:0 (V2:V0) contain the ADC output data. The ADC output is sampled on the ACK clock of the read address byte.

| Input Level (V)    | V2 | V1 | V0 |

|--------------------|----|----|----|

| < 0.32 Vcc         | 0  | 0  | 0  |

| 0.32Vcc to 0.48Vcc | 0  | 0  | 1  |

| 0.48Vcc to 0.64Vcc | 0  | 1  | 0  |

| 0.64Vcc to 0.80Vcc | 0  | 1  | 1  |

| > 0.80Vcc          | 1  | 0  | 0  |

**Table 22 - ADC Output Values**

# 3.0 Applications Information

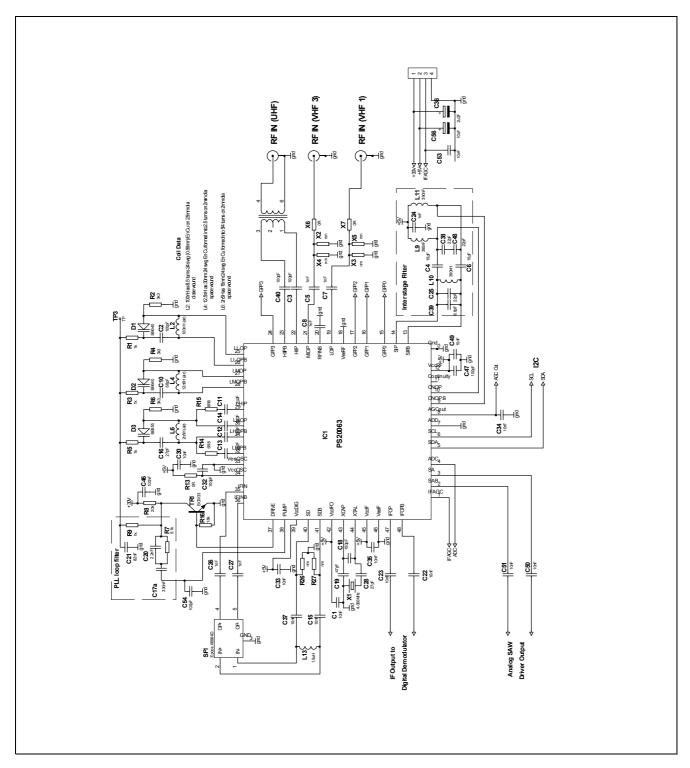

Typical application circuits for the PS20063 are shown in the following diagrams.

Figure 8 - Typical Application Circuit (ATSC)

Figure 9 - Typical Application Circuit (DVBT)

The low (VHF1) and Mid (VHF3) bands are single ended, however, the high band (UHF) should be differential. All IF signals are differential.

It is essential to have good RF layout around the RF stages, i.e., RF inputs and the VCOs. Track lengths around the VCO's should be minimized to reduce track inductance.

The layout should be organized to give good isolation between the IF signal paths. In particular good isolation is required between the outputs and inputs of the IF AGC amplifier. Isolation across the SAW filter is also important to ensure rejection of unwanted adjacent signals. This can be achieved by routing input and output tracks on opposite sides of the board.

It is also important to have good isolation between the high level IF signal and the crystal oscillator circuit to minimize any interactions. Care should be taken when locating IF tuning inductors to ensure there is no radiation to other parts of the circuit.

The crystal oscillator can also provide a clock signal to the demodulator. This can be done by taking the oscillator signal from the crystal series capacitor (27 pF) as shown in the following diagram.

Figure 10 - Crystal Oscillator Circuit (4 MHz)

The interstage filter between the converter outputs provides some additional rejection of adjacent channels (N +/-2). The recommended values are shown in Figure 11. The choice of components is important not only to give a flat response but also to provide an impedance transformation between the converter output and SAW driver input stages.

Figure 11 - Interstage Filter

The optimum charge pump and LO trim settings for the application circuits shown in figure 8 and 9, are shown in table 23 below. These give the optimum phase noise performance for the circuit shown. The changes in charge pump current compensate for frequency and VCO gain variations.

| Frequency Range    | Charge Pump Setting<br>CP | LO Trim<br>LO1 | LO Trim<br>LO0 |

|--------------------|---------------------------|----------------|----------------|

| VHF1 50 -110 MHz   | 01                        | 1              | 1              |

| VHF1 100 -160 MHz  | 10                        | 1              | 1              |

| VHF3 160 - 250 MHz | 10                        | 1              | 1              |

| VHF3 250 - 350 MHz | 01                        | 1              | 1              |

| VHF3 350 - 450 MHz | 10                        | 0              | 1              |

| UHF 450 - 500 MHz  | 00                        | 1              | 1              |

| UHF 500 - 700 MHz  | 01                        | 1              | 1              |

| UHF 700 - 800 MHz  | 10                        | 1              | 1              |

| UHF 800 - 850 MHz  | 11                        | 1              | 1              |

Table 23 - Optimum CP and LO Trim Settings

# 4.0 PIn Circuit Information

| Pin<br>No. | Pin<br>Name | Port<br>Sense     | Function                                                         | Schematic     |

|------------|-------------|-------------------|------------------------------------------------------------------|---------------|

| 1          | IFAGC       | Input             | IF AGC control                                                   | JEAGC 3K VREF |

| 2,         | SAB,<br>SA  | Output,<br>Output | SAW filter driver output A inverse<br>SAW filter driver output A | Vcc SA SAB    |

| 4          | ADC         | Input             | ADC input                                                        | ADC S         |

| 5          | SDA         | Bi-directional    | I <sup>2</sup> C bus serial data input/output                    | SDA Vcc       |

| 6          | SCL         | Input             | I <sup>2</sup> C bus serial clock input                          | Vcc SCL SCL   |

| Pin<br>No. | Pin<br>Name    | Port<br>Sense     | Function                                                    | Schematic                   |

|------------|----------------|-------------------|-------------------------------------------------------------|-----------------------------|

| 7          | ADD            | Input             | I <sup>2</sup> C address select                             | Vcc  63k  ADD  21k          |

| 8          | AGCOP          | Output            | AGC output                                                  | Vcc<br>100 AGCOP<br>1K<br>= |

| 9,         | CNOPB,<br>CNOP | Output,<br>Output | Converter Output inverse<br>Converter Output                | Vcc<br>500<br>CNOPB         |

| 11         | Cont           | -                 | Paddle                                                      | -                           |

| 12         | VccRF          | Supply            | RF section supply                                           | -                           |

| 13,<br>14  | SIPB<br>SIP    | Input,<br>Input   | SAW filter driver input inverse,<br>SAW filter driver input | SIP 250<br>SIPB 1.1K        |

| 15         | GPP0           | Output            | Switching port/Test output 1                                | GPP0<br>=                   |

| Pin<br>No.       | Pin<br>Name            | Port<br>Sense             | Function                                                          | Schematic                          |

|------------------|------------------------|---------------------------|-------------------------------------------------------------------|------------------------------------|

| 16               | GPP1                   | Output                    | Switching port/Test output 2                                      | Vcc<br>10K<br>GPP1<br>GPP2<br>GPP3 |

| 17               | GPP2                   | Output                    | Switching port                                                    | As GPP1 (pin16)                    |

| 18               | VeeRF                  | Supply                    | RF section ground                                                 | -                                  |

| 19,<br>20,<br>21 | LOIP<br>IPREF<br>MIDIP | Input,<br>Input,<br>Input | Low band input, Mid- and Low-band i/p reference, Mid-band input   | LOIP IPREF                         |

| 22,<br>23        | HIIP,<br>HIIPB         | Input,<br>Input           | Hi-band input,<br>Hi-band input inverse                           | HIIP                               |

| 24               | GPP3                   | Output                    | Switching Port                                                    | As GPP1 (pin16)                    |

| 25,<br>26        | LLOP,<br>LLOPB         | Output                    | Low band oscillator output,<br>Low-band oscillator output inverse | LLOPB                              |

| 27,<br>28        | LMOP,<br>LMOPB         | Output,<br>Output         | Mid-band oscillator output, Mid-band oscillator output inverse    | LMOPB                              |

| Pin<br>No.              | Pin<br>Name                       | Port<br>Sense                         | Function                                                                                                                         | Schematic                             |

|-------------------------|-----------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 29,<br>30,<br>31,<br>32 | LHIP,<br>LHOP,<br>LHOPB,<br>LHIPB | Input,<br>Output,<br>Output,<br>Input | High band oscillator input, High-band oscillator output, High-band oscillator output inverse, High-band oscillator input inverse | Vcc<br>350<br>LHOPB<br>LHIPB<br>LHIPB |

| 33                      | VeeOSC                            | Supply                                | LO ground                                                                                                                        | -                                     |

| 34                      | VccOSC                            |                                       | LO supply                                                                                                                        | -                                     |

| 35,<br>36               | IFIP,<br>IFIPB                    | Input,<br>Input                       | IF AGC amp input, IF AGC amp input inverse                                                                                       | IFIP IFIPB                            |

| 37,<br>38               | DRIVE,<br>PUMP                    | Output,<br>Output                     | Loop amplifier drive output,<br>Loop amp charge pump output                                                                      | PUMP DRIVE 340                        |

| 39                      | VccDIG                            | Supply                                | Digital section supply                                                                                                           | -                                     |

| 40,<br>41               | SD,<br>SDB                        | Output,<br>Output                     | SAW filter driver output D,<br>SAW filter driver o/p D inverse                                                                   | Vcc SD SDB                            |

| 42                      | VccIF                             | Supply                                | SAWF output supply                                                                                                               | -                                     |

| 43                      | XCAP                              | Input                                 | Reference osc feedback input                                                                                                     | VCC 1110 XTAL XCAP O 0.2 mA           |

| 44                      | XTAL                              | Output                                | Reference osc crystal drive                                                                                                      | See XCAP (pin 43)                     |

| Pin<br>No. | Pin<br>Name    | Port<br>Sense     | Function                                        | Schematic |

|------------|----------------|-------------------|-------------------------------------------------|-----------|

| 45         | VccIF          | Supply            | IF AGC supply                                   | -         |

| 46         | VeelF          | Supply            | IF AGC ground                                   | -         |

| 47,<br>48  | IFOP,<br>IFOPB | Output,<br>Output | IF AGC amp output,<br>IF AGC amp inverse output | Vcc       |

| Paddle     | Vee            | -                 | -                                               | -         |

#### **Absolute Maximum Ratings** 5.0

All voltages are referred to  $V_{ee}$  at 0 V.

| Characteristic                               | Min. | Max.                 | Units | Conditions                                 |

|----------------------------------------------|------|----------------------|-------|--------------------------------------------|

| Supply voltage                               | -0.3 | 6                    | V     |                                            |

| Supply voltage differential                  |      | 0.4                  | V     | Note 1                                     |

| RF input voltage                             |      | 117                  | dBμV  |                                            |

| Maximum voltage on SDA, SCL                  |      | 5.5                  | V     | V <sub>cc</sub> = 0 to 5.5V                |

| Max voltage on all remaining signal pins     | -0.3 | V <sub>cc</sub> +0.3 | V     | The voltage on any pin must not exceed 6 V |

| Total port current                           |      | 20                   | mA    |                                            |

| Storage temperature                          | -55  | 150                  | οС    |                                            |

| Junction temperature                         |      | 125                  | οС    | Power applied                              |

| Package thermal resistance (chip to ambient) |      | 27                   | °C/W  | Package paddle soldered to ground          |

| ESD protection                               | 2.0  |                      | kV    | All pins except 9,10                       |

| Mil-std 883B method 3015 cat1                | 1.25 |                      | kV    | Pins 9, 10 only                            |

Note 1: The  $V_{CCOSC}$ ,  $V_{CCDIG}$  (Pins 39,42) can be operated at a lower supply voltage than the remaining  $V_{CC}$  pins, but the voltage differential must not exceed the figure quoted in the table above.

#### **Operating Range** 6.0

All voltages are referred to  $V_{ee}$  at 0 V.

| Characteristic                                             | Min. | Max. | Units. | Conditions                                         |

|------------------------------------------------------------|------|------|--------|----------------------------------------------------|

| Supply voltage                                             | 4.5  | 5.5  | V      | Functional operation, specification not guaranteed |

| Supply voltage (V <sub>CCRF</sub> and V <sub>CCIF</sub> )  | 4.75 | 5.25 | V      | Full analification                                 |

| Supply voltage (V <sub>CCDIG</sub> and V <sub>CCOSC)</sub> | 4.60 | 5.25 | V      | Full specification                                 |

| Ambient Temperature                                        | -20  | 85   | °C     |                                                    |

| Low Band Input Frequency                                   | 50   | 170  | MHz    |                                                    |

| Mid Band Input Frequency                                   | 140  | 460  | MHz    |                                                    |

| High Band Input Frequency                                  | 400  | 900  | MHz    |                                                    |

# 7.0 Electrical Characteristics

Test conditions (unless otherwise stated). T =  $25^{\circ}$ C,  $V_{ee}$ = 0 V,  $V_{cc}$  = 5 V, IF Frequency = 44 MHz. All signals are differential with the exception of VHF1 and VHF3 inputs.

| Characteristic                                                    | Min.       | Тур.      | Max. | Units | Conditions                                                                                                            |

|-------------------------------------------------------------------|------------|-----------|------|-------|-----------------------------------------------------------------------------------------------------------------------|

| Supply current                                                    |            | <u> </u>  |      |       |                                                                                                                       |

| Normal operation                                                  |            | 160       | 195  | mA    | Total Current – UHF band<br>All switching ports off                                                                   |

| All sections active                                               |            | 156       | 190  | mA    | Total Current - VHF Bands<br>All switching ports off                                                                  |

| All sections active except                                        |            | 135       |      | mA    | UHF Band. Switching ports off                                                                                         |

| AGC IF amplifier                                                  |            | 131       |      | mA    | VHF Bands. Switching ports off                                                                                        |

| Sleep Mode                                                        |            | 9         |      | mA    | Crystal oscillator and data interface enabled                                                                         |

|                                                                   |            | 50        |      | mA    | PLL and crystal oscillator enabled                                                                                    |

| Composite system to SAW Fit VHF1 Band                             | Iter drive | r outputs |      |       |                                                                                                                       |

| Conversion gain                                                   | 31         | 34        | 37   | dB    | RFin = 54 MHz. Single ended input                                                                                     |

| Conversion gain                                                   | 31         | 34        | 37   | dB    | RFin = 155 MHz. Single ended input                                                                                    |

| Noise Figure                                                      |            | 12.5      | 14   | dB    | Rs = $50 \Omega$ .                                                                                                    |

| OPIP3                                                             | 135        | 146       |      | dBμV  | Two output tones at 110 dBμV                                                                                          |

| Output level causing 1% cross modulation                          | 113        | 120       |      | dBμV  | Note 2                                                                                                                |

| Output level causing 1.5 kHz FM                                   | 113        | 120       |      | dBμV  | Note 3                                                                                                                |

| I <sup>2</sup> C bus transmission induced LO frequency modulation |            | 2.5       |      | kHz   | Transmission repetition rate of 20 msec minimum with no change to previously loaded data, at 100 kHz SCL rate         |

| N+7 Direct modulation of VCO                                      |            |           | -40  | dBc   | Local oscillator sidebands induced by an input signal at 80 dB <sub>µ</sub> V offset from local oscillator by 100 kHz |

| Supply ripple spurious                                            |            |           | -40  | dBc   | Residual FM induced on local oscillator by 20 mV <sub>p-p</sub> ripple on V <sub>cc</sub> at 500 kHz                  |

| Local oscillator leakage to any band input                        |            | 45        |      | dBμV  |                                                                                                                       |

| IPIP2                                                             | 134        | 155       |      | dBμV  | Two input tones at 87 dB <sub>µ</sub> V at 92 MHz and 66 MHz with local oscillator at 110 MHz                         |

| Characteristic                                                       | Min.       | Тур.    | Max. | Units  | Conditions                                                                                                    |

|----------------------------------------------------------------------|------------|---------|------|--------|---------------------------------------------------------------------------------------------------------------|

| IPIP3                                                                | 112        | 120     |      | dBμV   | Desired = 54 MHz at 41 dB $\mu$ V Undesired = 60 and 72 MHz at 87 dB $\mu$ V                                  |

| IPIP3                                                                | 112        | 118     |      | dBμV   | Desired = 162 MHz at 41 dB $\mu$ V Undesired = 168 and 180 MHz at 87 dB $\mu$ V                               |

| P1dB                                                                 | 93         | 106     |      | dBμV   |                                                                                                               |

| Output Impedance                                                     |            | 100     |      | Ω      |                                                                                                               |

|                                                                      |            | 10      |      | nH     |                                                                                                               |

| Phase Noise, SSB                                                     |            |         |      |        | PLL Loop Bandwidth ~ 300 Hz<br>f <sub>comp</sub> = 62.5 kHz                                                   |

| 1 kHz                                                                |            | -76     |      | dBc/Hz |                                                                                                               |

| 10 kHz                                                               |            | -100    | -86  | dBc/Hz |                                                                                                               |

| 100 kHz                                                              |            | -115    | -106 | dBc/Hz |                                                                                                               |

| 10 MHz                                                               |            |         | -135 | dBc/Hz | Noise Floor                                                                                                   |

| Reference spurs                                                      |            | -90     | -50  | dBc    |                                                                                                               |

| Phase Noise, SSB                                                     |            |         |      |        | PLL Loop Bandwidth ~ 3kHz<br>f <sub>comp</sub> = 166.7 kHz                                                    |

| 1 kHz                                                                |            | -90     | -70  | dBc/Hz |                                                                                                               |

| 10 kHz                                                               |            | -95     | -86  | dBc/Hz |                                                                                                               |

| Image Rejection                                                      | 23         | 36      |      | dB     |                                                                                                               |

| Composite system to SAW Fi<br>VHF3 Band                              | Iter drive | outputs |      |        |                                                                                                               |

| Conversion gain                                                      | 31         | 34      | 37   | dB     | RFin = 164 MHz Single ended input                                                                             |

| Conversion gain                                                      | 31         | 34      | 37   | dB     | RFin = 442 MHz Single ended input                                                                             |

| Noise Figure                                                         |            | 12.5    | 14   | dB     | Rs = 50 Ω                                                                                                     |

| OPIP3                                                                | 135        | 146     |      | dBμV   | Two output tones at 110 dBμV                                                                                  |

| Output level causing 1% cross modulation                             | 113        | 120     |      | dBμV   | Note 2                                                                                                        |

| Output level causing 1.5 kHz<br>FM                                   | 113        | 120     |      | dBμV   | Note 3                                                                                                        |

| I <sup>2</sup> C bus transmission induced<br>LO frequency modulation |            | 2.5     |      | kHz    | Transmission repetition rate of 20 msec minimum with no change to previously loaded data, at 100 kHz SCL rate |

| Characteristic                             | Min.         | Тур.     | Max. | Units  | Conditions                                                                                                             |

|--------------------------------------------|--------------|----------|------|--------|------------------------------------------------------------------------------------------------------------------------|

| N+7 Direct modulation of VCO               |              |          | -40  | dBc    | Local oscillator sidebands induced by an input signal at 80 dB <sub>µ</sub> V offset from local oscillator by 100 kHz. |

| Supply ripple spurious                     |              |          | -40  | dBc    | Residual FM induced on local oscillator by 20 mV <sub>p-p</sub> ripple on V <sub>cc</sub> at 500 kHz                   |

| Local oscillator leakage to any band input |              | 45       |      | dBμV   |                                                                                                                        |

| IPIP2                                      | 122          | 143      |      | dBμV   | Two input tones at 89 dB <sub>µ</sub> V at 198 MHz and 390 MHz with local oscillator at 242 MHz                        |

| IPIP3                                      | 112          | 118      |      | dBμV   | Desired = 165 MHz at 45 dB <sub>μ</sub> V<br>Undesired = 171 and 183 MHz at<br>89 dB <sub>μ</sub> V                    |

| IPIP3                                      | 112          | 121      |      | dBμV   | Desired = 438 MHz at 45 dB $_{\mu}$ V Undesired = 444 and 456 MHz at 89 dB $_{\mu}$ V                                  |

| P1dB                                       | -95          | 107      |      | dBμV   |                                                                                                                        |

| Output Impedance                           |              | 100      |      | Ω      |                                                                                                                        |

|                                            |              | 10       |      | nH     |                                                                                                                        |

| Phase Noise, SSB                           |              |          |      |        | PLL Loop Bandwidth ~ 300 Hz<br>f <sub>comp</sub> = 62.5 kHz                                                            |

| 1 kHz                                      |              | -71      |      | dBc/Hz |                                                                                                                        |

| 10 kHz                                     |              | -95      | -86  | dBc/Hz |                                                                                                                        |

| 100 kHz                                    |              | -115     | -106 | dBc/Hz |                                                                                                                        |

| 10 MHz                                     |              |          | -135 | dBc/Hz | Noise Floor                                                                                                            |

| Reference spurs                            |              | -82      | -50  | dBc    |                                                                                                                        |

| Phase Noise, SSB                           |              |          |      |        | PLL Loop Bandwidth ~ 3kHz<br>f <sub>comp</sub> = 166.7 kHz                                                             |

| 1 kHz                                      |              | -87      | -70  | dBc/Hz |                                                                                                                        |

| 10 kHz                                     |              | -92      | -86  | dBc/Hz |                                                                                                                        |

| Image Rejection                            | 23           | 38       |      | dB     |                                                                                                                        |

| Composite system to SAW UHF Band           | Filter drive | routputs |      |        |                                                                                                                        |

| Conversion gain                            | 31           | 34       | 37   | dB     | RFin = 450 MHz                                                                                                         |

| Conversion gain                            | 30           | 34       | 37.5 | dB     | RFin = 866 MHz                                                                                                         |

| Noise Figure                               |              | 11       | 14   | dB     | Rs = $50 \Omega$ , No image correction                                                                                 |

| Characteristic                                                    | Min. | Тур. | Max. | Units  | Conditions                                                                                                                                          |

|-------------------------------------------------------------------|------|------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| OPIP3                                                             | 135  | 146  |      | dBμV   | Two output tones at 110 dBμV                                                                                                                        |

| Output level causing 1% cross modulation                          | 113  | 120  |      | dBμV   | Note 2                                                                                                                                              |

| Output level causing 1.5 kHz FM                                   | 113  | 120  |      | dBμV   | Note 3                                                                                                                                              |

| I <sup>2</sup> C bus transmission induced LO frequency modulation |      | 2.5  |      | kHz    | Transmission repetition rate of 20 msec minimum with no change to previously loaded data, at 100 kHz SCL rate                                       |

| N+7 Direct modulation of VCO                                      |      |      | -30  | dBc    | Local oscillator sidebands induced by an input signal at 80 dB <sub>μ</sub> V offset from local oscillator by 100 kHz. Wanted input signal = 750MHz |

| Supply ripple spurious                                            |      |      | -40  | dBc    | Residual FM induced on local oscillator by 20 mV <sub>p-p</sub> ripple on V <sub>cc</sub> at 500 kHz                                                |

| Local oscillator leakage to any band input                        |      | 60   |      | dBμV   |                                                                                                                                                     |

| IPIP2                                                             | 125  | 159  |      | dBμV   | Two input tones at 89 dB <sub>µ</sub> V at 438 MHz and 882 MHz with local oscillator at 486 MHz                                                     |

| IPIP3                                                             | 114  | 120  |      | dBμV   | Desired = 438 MHz at 45 dB $\mu$ V Undesired = 444 and 456 MHz at 91 dB $\mu$ V                                                                     |

| IPIP3                                                             | 114  | 121  |      | dBμV   | Desired = 858 MHz at 45 dB $\mu$ V Undesired = 864 and 876 MHz at 91 dB $\mu$ V                                                                     |

| P1dB                                                              | 97   | 107  |      | dBμV   |                                                                                                                                                     |

| Output Impedance                                                  |      | 100  |      | Ω      |                                                                                                                                                     |

|                                                                   |      | 10   |      | nH     |                                                                                                                                                     |

| Phase Noise, SSB                                                  |      |      |      |        | PLL Loop Bandwidth ~ 300 Hz<br>f <sub>comp</sub> = 62.5 kHz                                                                                         |

| 1 kHz                                                             |      | -67  |      | dBc/Hz |                                                                                                                                                     |

| 10 kHz                                                            |      | -92  | -86  | dBc/Hz |                                                                                                                                                     |