# **DEVELOPMENT DATA**

This data sheet contains advance information and specifications are subject to change without notice.

# UNIVERSAL DAC (UDAC)

#### **GENERAL DESCRIPTION**

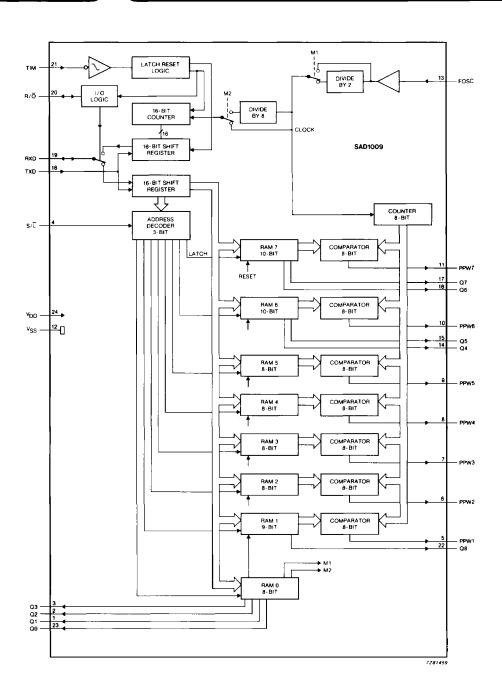

The SAD1009 is intended as a peripheral to a microcontroller-based servo system in video cassette recorders. The device relieves the microcontroller of some of the real time functions. These functions include; generation of programmable pulse width signals (duty factor etc.) and accurate measurement of time period signals (tacho signal etc.). The SAD1009 has nine programmable output ports. All functions of the UDAC are programmable. Commands and data from the microcontroller are loaded via a bidirectional bus using a 16-bit format. Data from the time period measurement is transferred to the microcontroller via the same bidirectional bus, also using a 16-bit format. The clock signal for this device is provided by the quartz oscillator of the microcontroller.

#### **Features**

- Generation of programmable pulse width signals

- Measurement of time period signals

- All functions are programmable

#### QUICK REFERENCE DATA

| parameter             | conditions               | symbol   | min.                | typ. | max. | unit |

|-----------------------|--------------------------|----------|---------------------|------|------|------|

| Supply                |                          |          |                     |      |      |      |

| Supply voltage range  |                          | $v_{DD}$ | 4,75                | 5,0  | 5,25 | V    |

| Inputs                |                          |          |                     |      |      |      |

| Input voltage         |                          |          |                     |      |      |      |

| LOW                   |                          | VIL      | _                   |      | 0,8  | V    |

| HIGH                  |                          | $v_{IH}$ | 2,4                 | -    |      | V    |

| Input leakage current |                          | ±II      | _                   | -    | 1    | μΑ   |

| Input capacitance     |                          | Cl       | _                   | ~    | 7,5  | рF   |

| Outputs               |                          |          |                     |      |      |      |

| Output voltage        |                          |          |                     |      |      |      |

| LOW                   | I <sub>OL</sub> = 1,6 mA | VOL      |                     |      | 0,4  | V    |

| HIGH                  | IOH = -1,0 mA            | Voн      | V <sub>DD</sub> 0,4 | ~    | -    | V    |

| Output sink current   |                          | Io       | _                   | _    | 1,6  | mA   |

| Output source current |                          | -10      | _                   | _    | 1,0  | mA   |

## **PACKAGE OUTLINES**

SAD1009P: 24-lead DIL; plastic (SOT101A).

SAD1009T: 24-lead mini-pack; plastic (SO24; SOT137A).

Fig. 1 Block diagram.

## PINNING

Fig. 2 Pinning diagram.

## Power supply

V<sub>DD</sub> positive supply voltage (+5 V)

VSS ground (0 V)

# Inputs

S/L shift/latch input FOSC oscillator input TXD serial clock

## Special inputs

TIM timer input

# Outputs

Q0 to Q8 programmable output ports

PPW1 to PPW7 programmable pulse width outputs

# Input/outputs

$\begin{array}{cc} \mathsf{RXD} & \mathsf{serial\ data} \\ \mathsf{R}/\overline{\mathsf{O}} & \mathsf{handshake} \end{array}$

#### **FUNCTIONAL DESCRIPTION**

## Loading data

All commands and data are loaded into the SAD1009 via the bidirectional bus (TXD, RXD). The bidirectional bus is compatible with the serial interface of the '8051' microcontroller, using mode 0.

A 16-bit word is used to program a function of the UDAC. The first 3-bits received from the RAM constitute the address and the remaining 13-bits are data (LSB first, MSB last). None of the functions require all 13-bits of data, therefore, 16-bit words contain a number of immaterial bits (x). The programming format is shown in Table 1.

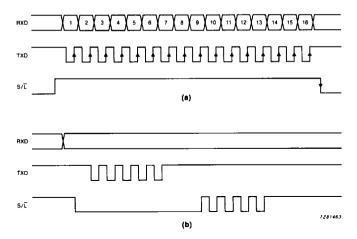

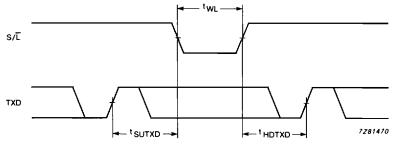

To shift a program word into the input buffer of the UDAC the  $S/\overline{L}$  line (shift/latch not) must be HIGH. The contents of the input buffer are transferred to the appropriate RAM on the HIGH-to-LOW transition of the  $S/\overline{L}$  signal. When  $S/\overline{L}$  is LOW the input buffer is disabled and cannot accept new incoming information. Fig. 3 illustrates the program reception cycle.

Table 1 Programming format

| bit | status | PPW1 | PPW2 | PPW3 | PPW4 | PPW5 | PPW6 | PPW7 |

|-----|--------|------|------|------|------|------|------|------|

| 1   | L      | Н    | L    | Н    | L    | Н    | L    | Н    |

| 2   | L      | L    | Н    | Н    | L    | L    | н    | Н    |

| 3   | L      | L    | L    | L    | н    | н    | н    | н    |

| 4   | RESET  | Q8   | X    | ×    | l x  | ×    | Q4   | Ω6   |

| 5   | X      | X    | X    | ×    | l x  | ×    | Ω5   | Q7   |

| 6   | X      | X    | X    | ×    | l x  | ×    | l x  | Х    |

| 7   | X      | X    | X    | ×    | ×    | ×    | l x  | х    |

| 8   | X      | X    | X    | ×    | X    | ×    | l x  | X    |

| 9   | Ω0     | D8   |

| 10  | Q1     | D7   |

| 11  | Q2     | D6   |

| 12  | Q3     | D5   |

| 13  | X      | D4   |

| 14  | X      | D3   |

| 15  | M1     | D2   |

| 16  | M2     | D1   | Đ1   | D1   | D1   | D1   | D1   | D1   |

#### Where:

X : don't care

D1 to D8: data for programming pulse width, D1 = MSB and D8 = LSB

Fig. 3 Program reception cycle: a) normal reception cycle; b) no information is loaded into the input buffer, the RAMs contents remain unchanged.

## Pulse width modulated outputs

The UDAC has seven pulse width modulated outputs (PPW1 to PPW7). The output PPW1 is slightly different to outputs PPW2 to PPW7, the difference is explained below. Each output produces a pulse width modulated signal with a duty factor programmable in steps of 1/256 and has a repetition frequency of approximately 23 kHz. These pseudo analogue signals are used to control the capstan and reel drives. Motor control can be performed in the following ways:

- convert the pulse width modulated signal into an analogue signal using filtering and analogue power amplification

- by feeding the pulse width modulated signal to the motor via a power switch and a switch mode filter

To conserve power use the second method for control of the capstain and reel motors. For the scanner control two outputs are available, so that by weighted addition a higher resolution can be achieved.

PPW1 is also an 8-bit programmable output, with a repetition frequency of 23 kHz. The difference is the low frequency contents of the signal are reduced by changing the distribution of the HIGH and LOW level portions. This redistribution means that a filter with two poles; each at 43  $\mu$ s, is sufficient to reduce the peak-to-peak ripple to less than 1 LSB. This output is for use in applications where long filter delays are not tolerated.

#### Clock frequency

The clock signal of the UDAC is derived from the quartz oscillator of the microcontroller. The clock frequency should not exceed 6 MHz. The device also contains a programmable 'divide by two' circuit which allows these frequencies to be doubled, thus 6 MHz or 12 MHz microcontrollers can be used. The FOSC signal can be divided by two using bit M1 of RAM 0 (see Table 2).

Table 2 UDAC adjustment

| bit<br>M1 | quartz frequency<br>(MHz) |

|-----------|---------------------------|

| L         | 12                        |

| н         | 6                         |

#### Programmable output ports

A total of nine output ports can be programmed to supply a HIGH or LOW level signal. Four of these outputs (Q4 to Q7) are intended to supply information about the breaking and direction of the capstan and reel motors, therefore these output ports must be programmed at the same time as the pulse widths of PPW6 and PPW7. Output port Q8 is programmed at the same time as PPW1. The other four output ports (Q0 to Q3) are programmed by RAM 0.

#### Measurement of the time period

To facilitate accurate measurement of the time period (falling edge to falling edge) of a signal applied to TIM, the UDAC contains a 16-bit counter and a buffer to store the contents of the previous counter measurement. The counter operates at a frequency of fclock/2 or fclock/16, the counter can be programmed using bit M2 of RAM 0. This timer can record periods of up to 21,8 ms and 175 ms respectively (see Table 3). When the time period is too long and the timer overflows, the microcontroller is loaded with a hex 'FFFF' when it reads the time period after the next pulse.

Table 3 Counter frequency

| M2 | division<br>ratio | time period<br>(max.) | frequency | resolution |

|----|-------------------|-----------------------|-----------|------------|

| L  | 2                 | 21,8 ms               | 46 Hz     | 333 ns     |

| н  | 6                 | 175 ms                | 5,7 Hz    | 2,67 μs    |

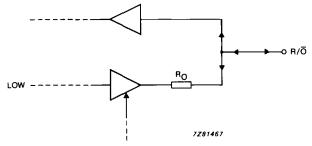

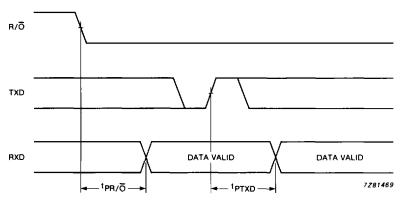

Data from the timer can be transferred to the microcontroller via a bidirectional bus when the handshaking signal pin  $R/\overline{O}$  is pulled LOW by the microcontroller. The LSB is transferred first and the MSB last. After the data has been transferred pin  $R/\overline{O}$  remains in a LOW state (pulled down by the UDAC) until a new measurement of the time period is concluded. Note that each measurement of a time period can only be read once. After the next input pulse the 'data ready' state is signalled to the microcontroller by releasing the  $R/\overline{O}$  pin, so that the microcontroller reads a HIGH level on this pin.

#### Note

During the 'data not ready' state the  $R/\overline{O}$  is in a low impedance state and during the 'data ready' state the  $R/\overline{O}$  is in a high impedance state (= HIGH). To speed up the transition from LOW-to-HIGH, the high impedance state is preceded by a short period of low impedance HIGH state.

#### Reset

The device can be reset by software by loading a LOW into the  $\overline{\text{RESET}}$  bit of RAM 0. The effect of this reset is as follows:

- RAM 0; not influenced

- RAM 1; duty factor = 50%, Q8 = LOW

- RAM 2 to 5; duty factor = 50%

- RAM 6 to 7; duty factor = 0 and Q4 to Q7 = LOW

The reset is de-activated automatically on the next LOW-to-HIGH transition of  $S/\bar{L}$ . This allows new program information to be loaded and transferred to any RAM without having finished the reset. Due to RAM 0 not being influenced by the reset, the data required after the reset can be loaded along with the reset command.

# SAD1009

**RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | conditions | symbol           | min.       | max.                  | unit |

|-------------------------------------|------------|------------------|------------|-----------------------|------|

| Supply voltage range                |            | V <sub>DD</sub>  | _          | 7                     | V    |

| Input voltage range                 | note 1     | V <sub>I</sub>   | -0,5       | V <sub>DD</sub> + 0,5 | ٧    |

| Input voltage at $S/\overline{L}$   |            | V4-12            | -0,5       | V <sub>DD</sub> + 2,0 | V    |

| D.C. current into any input         |            | ±1 <sub>1</sub>  | _          | 10                    | mA   |

| D.C. current from any output        |            | ±ΙΟ              |            | 10                    | mA   |

| D.C. current into V <sub>DD</sub>   |            | ±II              | _          | 25                    | mA   |

| D.C. current into VSS               |            | ±II              | _          | 25                    | mA   |

| Total power dissipation             | note 2     | P <sub>tot</sub> | -          | 200                   | mW   |

| Storage temperature range           |            | T <sub>stg</sub> | <b>-55</b> | +150                  | oC   |

| Operating ambient temperature range |            | T <sub>amb</sub> | -20        | +70                   | oC   |

|                                     | t .        |                  |            |                       |      |

## Notes to ratings

- 1. Input voltage should not exceed 7 V unless otherwise specified.

- 2. Diminishes by 5 mW/K from 60 °C.

# **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices (see 'Handling MOS Devices').

# D.C. CHARACTERISTICS

$V_{DD}$  = 4,75 to 5,25 V;  $T_{amb}$  = -20 to 70 °C, unless otherwise specified

| parameter                                                      | conditions                                                                   | symbol                                                                  | min.                      | typ.             | max.                 | unit               |

|----------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------|------------------|----------------------|--------------------|

| Supply                                                         |                                                                              |                                                                         |                           |                  |                      |                    |

| Supply voltage range                                           |                                                                              | V <sub>DD</sub>                                                         | 4,75                      | 5,0              | 5,25                 | V                  |

| Supply current range                                           | VO = VDD, IO = 0 mA<br>on all outputs; V <sub>I</sub> = VSS<br>on all inputs | IDD                                                                     | -                         | 100              | _                    | μΑ                 |

| TXD, RXD, $S/\overline{L}$ , $R/\overline{O}$                  |                                                                              |                                                                         |                           |                  |                      |                    |

| Input voltage LOW HIGH Input leakage current Input capacitance | note 1                                                                       | V <sub>IL</sub><br>V <sub>IH</sub><br>±I <sub>I</sub><br>C <sub>I</sub> |                           | _<br>_<br>_<br>_ | 0,8<br>-<br>1<br>7,5 | V<br>V<br>μA<br>pF |

| RXD, R/O, Q0 to Q7                                             |                                                                              |                                                                         |                           |                  |                      |                    |

| Output voltage<br>LOW<br>HIGH                                  | note 2<br>  OL = 1,6 mA<br>  OH = -1,0 mA                                    | V <sub>OL</sub>                                                         | -<br>V <sub>DD</sub> -0,4 | _<br>            | 0,4                  | V                  |

| Output sink current                                            |                                                                              | 10                                                                      | _                         | _                | 1,6                  | mA                 |

| Output source current                                          |                                                                              | -10                                                                     | _                         | _                | 1,0                  | mA                 |

| FOSC                                                           |                                                                              |                                                                         |                           |                  |                      |                    |

| Input voltage<br>LOW<br>HIGH                                   |                                                                              | V <sub>IL</sub><br>Vih                                                  | _<br>                     |                  | 0,8<br>-             | V                  |

| Input leakage current                                          |                                                                              | ±lj                                                                     | _                         | _                | 1                    | μΑ                 |

| Input capacitance                                              |                                                                              | Ci                                                                      | _                         | _                | 7,5                  | pF                 |

# D.C. CHARACTERISTICS (continued)

| parameter             | conditions                                                  | symbol           | min.                 | typ. | max.                | unit   |

|-----------------------|-------------------------------------------------------------|------------------|----------------------|------|---------------------|--------|

| RXD                   | used as input                                               |                  |                      |      | 4.0                 |        |

| Input leakage current |                                                             | ±II              | _                    | _    | 10                  | μΑ     |

| TIM                   |                                                             |                  |                      |      |                     | ,      |

| Input voltage         |                                                             |                  |                      |      |                     |        |

| LOW<br>LOW            | V 5.V . 00.00                                               | VIL              | -                    | _    | 0,3xV <sub>DD</sub> |        |

| HIGH                  | V <sub>DD</sub> = 5 V at 20 °C                              | VIL              | 0.7:1/               | 1,8  |                     | V<br>V |

| HIGH                  | V <sub>DD</sub> = 5 V at 20 °C                              | V <sub>IH</sub>  | 0,7xV <sub>DD</sub>  | 2,9  | _                   | V      |

| Hysteressis           | used as input                                               | V <sub>hys</sub> |                      | 730  | _                   | mV     |

| R/Ō                   | used as input                                               |                  |                      |      |                     |        |

| Output resistance     |                                                             | RO               | 500                  | _    | 1000                | Ω      |

| Input leakage current |                                                             | ±II              | _                    | _    | 10                  | μΑ     |

| R/Ō                   | used as output; open<br>drain output; note 3;<br>see Fig. 7 |                  |                      |      |                     |        |

| Output voltage        |                                                             |                  | ,                    |      |                     |        |

| LOW                   | IOL = 0,4 mA                                                | VOL              | ·                    | _    | 0,8                 | v      |

| HIGH                  | I <sub>OH</sub> =0,4 mA                                     | Vон              | V <sub>DD</sub> 0,8  | _    | _                   | V      |

| PPW1 to PPW7          |                                                             |                  |                      |      |                     |        |

| Output voltage        |                                                             |                  |                      |      |                     |        |

| LOW                   | IOL = 4 mA                                                  | VOL              | _                    | -    | 0,4                 | V      |

| HIGH                  | IOH =4 mA                                                   | ∨он              | V <sub>DD</sub> -0,4 | _    |                     | ٧      |

| Output sink current   |                                                             | 10               | _                    | j –  | 4                   | mΑ     |

| Output source current |                                                             | -10              | _                    | –    | 4                   | mΑ     |

## Notes to the d.c. characteristics

- 1. This value applies to TXD and  $S/\overline{L}$ , the input leakage current for RXD and  $R/\overline{O}$  is shown above.

- 2. This value applies to RXD and Q0 to Q7, the output voltage for  $R/\overline{O}$  is shown above.

- 3. After a LOW-to-HIGH transition of the  $R/\overline{O}$  output, the port is held HIGH for approximately one clock cycle. This low impedance HIGH period is followed by the high impedance OFF-state.

# DEVELOPMENT DATA

# A.C. CHARACTERISTICS

| parameter                        | conditions                   | symbol           | min. | typ.       | max. | unit |

|----------------------------------|------------------------------|------------------|------|------------|------|------|

| RXD, $R/\overline{O}$ , Q0 to Q7 |                              |                  |      |            |      |      |

| Output transition time           | C <sub>L</sub> = 50 pF       |                  |      |            | i    |      |

| LOW-to-HIGH                      | _                            | tTLH             | _    | -          | 30   | ns   |

| HIGH-to-LOW                      | :                            | <sup>t</sup> THL | -    | -          | 30   | ns   |

| FOSC                             |                              |                  |      |            | i    |      |

| Maximum pulse                    |                              |                  | i    | !          |      |      |

| frequency                        | M1 = L                       | f <sub>max</sub> | -    | -          | 12   | MHz  |

|                                  | M1 = H                       | fmax             | _    | _          | 6    | MHz  |

| Minimum pulse width              |                              | !                | !    |            |      |      |

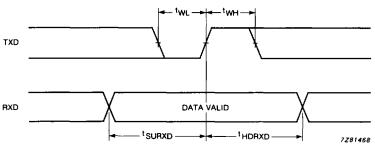

| LOW                              |                              | tWL              | 20   | -          | -    | ns   |

| HIGH                             |                              | tWH              | 20   | -          | -    | ns   |

| TXD                              |                              |                  |      |            | İ    |      |

| Pulse frequency                  |                              | f <sub>max</sub> | _    | _          | 6    | MHz  |

| Pulse width                      |                              |                  |      | ĺ          | i    | :    |

| LOW                              |                              | twL              | 50   | _          | _    | ns   |

| HIGH                             |                              | twH              | 50   | _          | _    | ns   |

| RXD                              |                              |                  |      |            |      | 1    |

| אאט                              | used as input;<br>see Fig. 5 |                  | ļ    |            | İ    |      |

| Set-up time                      | see rig. 5                   |                  | İ    |            |      |      |

| RXD to TXD                       |                              | tsurxd           | 50   | -          | _    | ns   |

| Hold time                        |                              | COMME            | ļ    |            |      | i    |

| RXD to TXD                       |                              | tHDRXD           | 50   |            | _    | ns   |

| RXD                              | used as output;              |                  |      |            |      |      |

| 1170                             | see Fig. 6                   |                  |      |            | 1    |      |

| Propagation delay                | ,                            |                  |      | !          |      |      |

| TXD to RXD                       |                              | tPRXD            | _    | _          | 50   | ns   |

| R/oto RXD                        |                              | tPR/O            | -    | -          | 50   | ns   |

| S/L                              | see Fig. 7                   | :                |      |            |      |      |

| Pulse width LOW                  | 3                            | Í                |      |            |      |      |

| Set-up time                      |                              |                  | !    |            |      |      |

| TXD to S/E                       |                              | tSUTXD           | 50   | _          | _    | ns   |

| Hold time                        |                              | 30170            |      |            |      | 1    |

| TXD to S/L                       | İ                            | tHDTXD           | 50   | _          | _    | ns   |

| Propagation delay                |                              | טאוטחי           |      |            |      | 1    |

| S/L to Q0 - Q7                   |                              | tp               | i –  | _          | 50   | ns   |

|                                  |                              | d,               |      |            |      | 1.0  |

| TIM                              |                              |                  |      |            |      |      |

| Pulse width                      |                              |                  | 700  |            |      | 1    |

| LOW                              | M2 = LOW                     | tWL              | 700  | -          | -    | ns   |

| LOW                              | M2 = HIGH                    | twL              | 5,4  | -          | 1-   | μs   |

| HIGH                             |                              | twH              | 100  | <b> </b> - | -    | ns   |

Fig. 4 Equivalent R/O output port.

Fig. 5 RXD input waveform.

Fig. 6 RXD output waveform.

Fig. 7 S/L input waveform.