### **Features and Benefits**

- Output disconnect during shutdown

- I µA shutdown current

- 2.7 to 9 V input

- Operate with 1 or 2 Li+ battery input supply

- Output voltage up to 23 V

- 1.2 MHz switching frequency

- 1.5 A switch current limit

- Internal overvoltage and overtemperature protection, and soft start

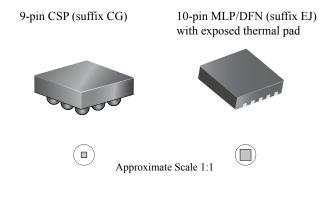

### Package:

### Description

The A8480 is a 1.2 MHz optimized boost converter with internal soft-start and compensation to support WLED, flash/torch, and display bias applications. The input voltage range of 2.7 to 9 V supports either 1 or 2 Li-ion battery applications. The high voltage integrated double-diffused MOSFET(DMOS) allows output voltages as high as 23 V with a switch current limit of 1.5 A, this increases the maximum quantity of LEDs that can be used in series.

To maximize battery life in the application, the output can be completely disconnected from the battery voltage to virtually eliminate leakage current in the system. For system protection, the A8480 has internal overtemperature and overvoltage protection.

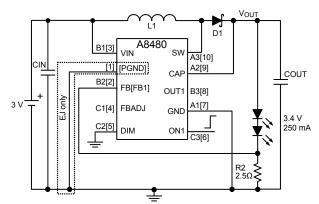

The A8480 is available in both 1.6 mm  $\times$  1.6 mm, 0.5 mm nominal height CSP, and 3 mm  $\times$  3 mm, 0.75 mm nominal height MLP/DFN packages.

Applications include:

- WLED flash/torch

- WLED backlight

- OLED bias supplies

- LCD bias supplies

- General purpose boost converter

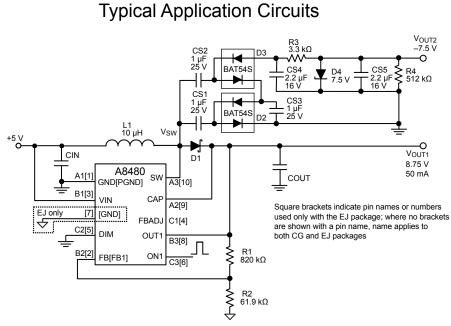

### **Typical Applications**

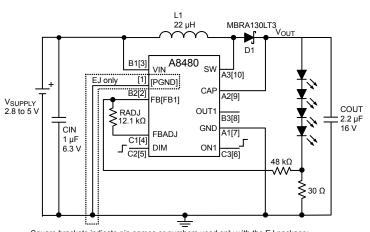

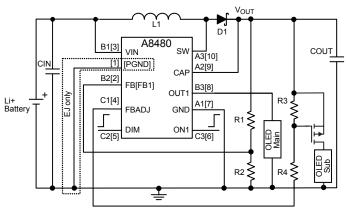

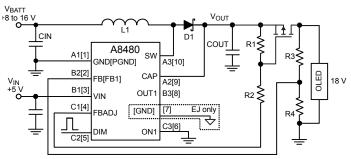

Square brackets indicate pin names or numbers used only with the EJ package; where no brackets are shown with a pin name, name applies to both CG and EJ packages

Figure 1. Using the A8480 to drive a flash (100 mA) or torch (20 mA)

## Boost Regulator for Display Bias or LED Driver

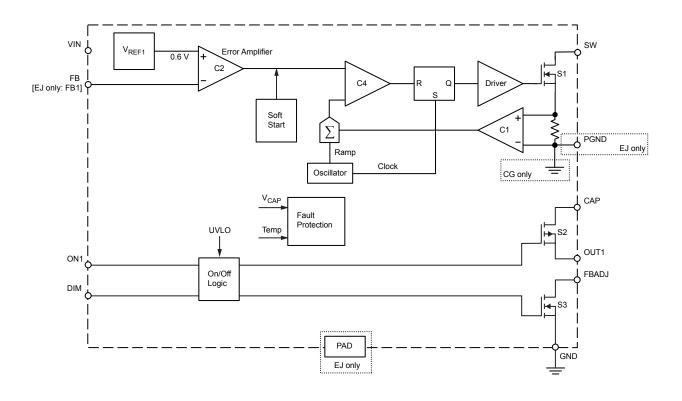

### **Functional Block Diagram**

#### **Absolute Maximum Ratings**

| Input or Output Voltage                            |                    |

|----------------------------------------------------|--------------------|

| SW, CAP, OUT1, FBADJ pins                          | -0.3 to 26 V       |

| VIN pin, V <sub>IN</sub>                           |                    |

| All other pins, $V_x$                              | y+0.3 V (7 V max.) |

| Operating Ambient Temperature, T <sub>A</sub>      | 40°C to 85°C       |

| Maximum Junction Temperature, T <sub>J</sub> (max) | 150°C              |

| Storage Temperature, T <sub>stg</sub>              | 55°C to 150°C      |

#### Package Thermal Characteristics

EJ package:  $R_{\theta JA} = 45$  °C/W, on a 4-layer board. Additional information is available on the Allegro Web site.

Packages are lead (Pb) free. EJ package has 100% matte tin leadframe plating.

#### Selection Guide

| Part Number   | Package                   | Packing <sup>a</sup> |

|---------------|---------------------------|----------------------|

| A8480ECGLT-Tb | 9-bump chip scale package | Tape and Reel        |

| A8480EEJTR-T  | 10-pin MLP/DFN package    | 1500 pieces per reel |

<sup>a</sup>Contact Allegro for additional packing options.

<sup>b</sup>Contact Allegro factory for availability.

(10

(<u>9</u> (8

(7

6

### **Pin-out Diagrams**

CG Package (Top View)

#### EJ Package (Top View)

PAD

#### **Terminal List Table**

| Number |     | Nama  | Description                                                                                                                                                                                                                                                                                  |  |  |  |

|--------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CG     | EJ  | Name  | Description                                                                                                                                                                                                                                                                                  |  |  |  |

| _      | 1   | PGND  | Power ground connection; use to avoid interference with signal ground.                                                                                                                                                                                                                       |  |  |  |

| A1     | _   | GND   | Power and signal ground connection; connect directly to the ground plane.                                                                                                                                                                                                                    |  |  |  |

| -      | 7   | GND   | Signal ground reference; connect directly to the ground plane.                                                                                                                                                                                                                               |  |  |  |

| A2     | 9   | CAP   | This is the connection to the output capacitor for the boost regulator output.                                                                                                                                                                                                               |  |  |  |

| A3     | 10  | SW    | This is the connection between the internal boost switch and the external inductor.<br>Because rapid changes of current occur at this pin, the board traces connected to this pin<br>should be minimized and the inductor and diode should be connected as close to this pin<br>as possible. |  |  |  |

| B1     | 3   | VIN   | This is the power input supply connection to the circuit. A bypass capacitor tying this pin to GND must be connected close to this pin.                                                                                                                                                      |  |  |  |

| B2     | _   | FB    | This is the feedback pin for controlling voltage on the OUT1 pin. The nominal reference                                                                                                                                                                                                      |  |  |  |

| -      | 2   | FB1   | voltage on this pin is 600 mV. In order to minimize noise, connect the feedback resistor network close to this pin.                                                                                                                                                                          |  |  |  |

| B3     | 8   | OUT1  | This is the voltage-controlled output pin for the OLED drive. An internal switch disconnects the OLED during shutdown.                                                                                                                                                                       |  |  |  |

| C1     | 4   | FBADJ | Open collector output driven by DIM. This can be used to provide dimming by connecting an additional feedback circuit or it can be used to drive external output.                                                                                                                            |  |  |  |

| C2     | 5   | DIM   | Logic input. Driving DIM puts the FBADJ open collector output low.                                                                                                                                                                                                                           |  |  |  |

| C3     | 6   | ON1   | This is the enable pin for OUT1.                                                                                                                                                                                                                                                             |  |  |  |

| _      | PAD | _     | Exposed thermal pad. Connect to GND plane for enhanced thermal performance.                                                                                                                                                                                                                  |  |  |  |

# Boost Regulator for Display Bias or LED Driver

| Characteristics                  | Symbol                  | Test Conditions                                                 | Min. | Тур. | Max. | Units |

|----------------------------------|-------------------------|-----------------------------------------------------------------|------|------|------|-------|

| Input Voltage Range              | V <sub>IN</sub>         |                                                                 | 2.7  | _    | 9    | V     |

| Quiescent Input Current          | I <sub>IN(Q)</sub>      | DIM=ON1=0                                                       | -    | -    | 1    | μA    |

| Undervoltage Lockout Threshold   | V <sub>UVLO</sub>       | V <sub>IN</sub> rising                                          | 2.25 | 2.45 | 2.60 | V     |

| Feedback Reference Voltage       | V <sub>FB</sub>         |                                                                 | 584  | 610  | 636  | mV    |

| Feedback Voltage Line Regulation |                         | 2.7 V≤V <sub>IN</sub> ≤9 V                                      | -    | 0.1  | -    | %/V   |

| Feedback Input Current           | I <sub>FB</sub>         |                                                                 | -    | 45   | 100  | nA    |

| Switch Current Limit             | I <sub>SWLim</sub>      |                                                                 | -    | 1.5  | _    | Α     |

| Switch Frequency                 | f <sub>SW</sub>         |                                                                 | 1    | 1.2  | 1.4  | MHz   |

| Switch Maximum Duty Cycle*       | DC                      |                                                                 | 85   | 90   | -    | %     |

| Switch S1 On Resistance          | R <sub>DS1(on)</sub>    | I <sub>SW</sub> = 0.5 A                                         | -    | 225  | -    | mΩ    |

| Switch Leakage Current           | I <sub>SW(lkg)</sub>    | V <sub>SW</sub> = 5 V                                           | -    | -    | 1    | μA    |

| FBADJ MOSFET On Resistance       | R <sub>DSF(on)</sub>    | V <sub>DIM</sub> > V <sub>IH</sub>                              | -    | 10   | _    | Ω     |

| FBADJ MOSFET Leakage Current     | I <sub>FBADJ(lkg)</sub> | V <sub>DIM</sub> < V <sub>IL</sub> , V <sub>FBADJ</sub> = 0.6 V | -    | 1    | -    | μA    |

| ON1, DIM Input Threshold Low     | V <sub>IL</sub>         |                                                                 | -    | -    | 0.4  | V     |

| ON1, DIM Input Threshold High    | V <sub>IH</sub>         |                                                                 | 1.5  | -    | -    | V     |

| ON1, DIM Input Bias Current      | I <sub>IB</sub>         |                                                                 | -    | 65   | -    | μA    |

| Output Overvoltage Rising Limit  | V <sub>OVPR</sub>       |                                                                 | -    | 24.5 | 25.5 | V     |

| Thermal Shutdown Threshold       | T <sub>SHDN</sub>       |                                                                 | _    | 160  | _    | °C    |

| Thermal Shutdown Hysteresis      | T <sub>SHDNhys</sub>    |                                                                 | -    | 10   | _    | °C    |

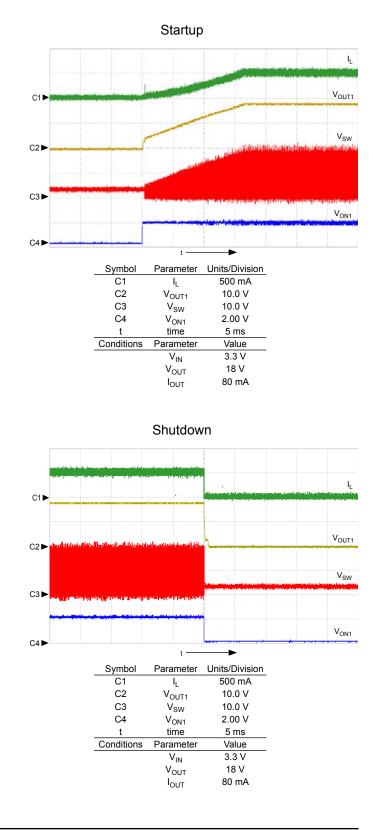

| Soft-Start Period                | t <sub>SS</sub>         | V <sub>OUT</sub> = 10 V                                         | _    | 2    | -    | ms    |

#### ELECTRICAL CHARACTERISTICS at T<sub>A</sub>=25°C, VIN=ON1=DIM=3.0 V (unless noted otherwise)

\*Guaranteed by design.

## Boost Regulator for Display Bias or LED Driver

Allegro MicroSystems, Inc. 5 115 Northeast Cutoff Worcester, Massachusettel Weltata Sheet 4U.com 1.508.853.5000; www.allegromicro.com

# Boost Regulator for Display Bias or LED Driver

### **Functional Description**

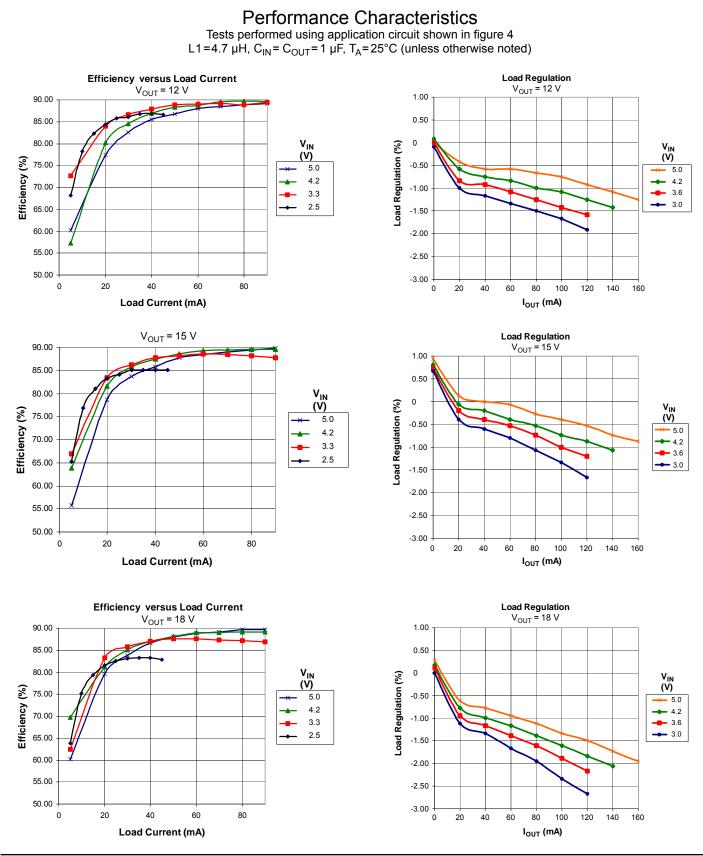

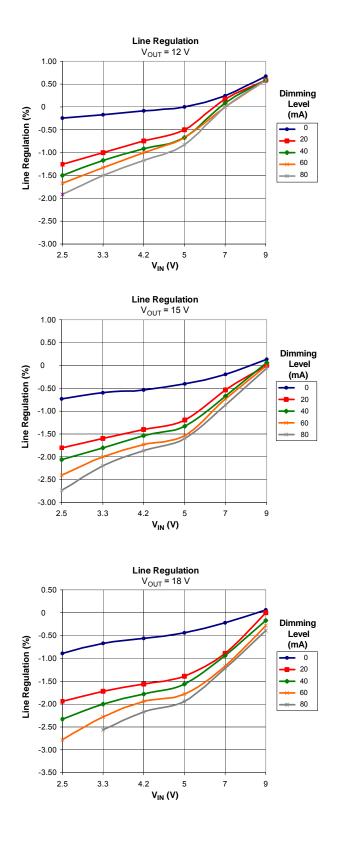

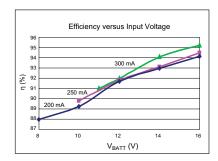

The A8480 is a boost converter with output disconnect. The boost stage boosts input battery voltage to a sufficient level to drive an OLED or a set of series-connected WLEDs. This stage uses 1.2 MHz constant frequency, current mode control. Typical application circuits are shown in figure 1, and the Typical Applications section.

When OUT1 is enabled and  $V_{IN}$  is greater than  $V_{IN}$ (min), the boost stage is ramped-up with soft start, with switch, S2, completely turned on.

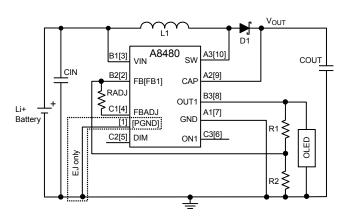

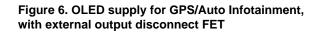

The constant voltage drive for OLED is provided through the OUT1 pin. The internal switch between the CAP and OUT1 pins disconnects the OLED when OUT1 is disabled.

For driving OLEDs, output voltage is sensed by the FB1 pin through a voltage divider network. Output voltage (V) is set as:

$$V_{\rm OUT1} = 0.61 \times \frac{R_1 + R_2}{R_2}$$

(1)

When DIM is high and RFBADJ is used (R2 is configured in parallel with RFBADJ in the circuit; see figure 4a), the output voltage is set as follows:

$$V_{\text{OUT1}} = 0.61 \times \frac{R_1 + \left(\frac{R_2 \times R_{\text{FBADJ}}}{R_2 + R_{\text{FBADJ}}}\right)}{\frac{R_2 \times R_{\text{FBADJ}}}{R_2 + R_{\text{FBADJ}}}}$$

(2)

The A8480 provides protection against output overvoltage on the CAP pin, overload, and overtemperature. Also, it has an input undervoltage lockout to avoid malfunction and battery drain.

At light loads, instantaneous inductor current drops to zero. This is known as discontinuous mode operation and will result in some low frequency ripple. In discontinuous mode, the voltage at the SW pin will ring, due to the resonant LC circuit formed by the inductor and the switch and diode capacitance. This ringing is low frequency and is not harmful. It can be damped with a resistor across the inductor, but this will reduce efficiency and is not recommended.

#### **Dual OLED Application**

The A8480 can be easily used as a dual OLED driver. In this application, the main OLED can be connected to OUT1 and the sub OLED can be connected between the output of the boost stage, at  $V_{OUT}$ , and the FBADJ pin, as in the application shown in figure 5. The sub OLED is controlled by the DIM pin. Pulling the DIM pin high turns on the internal switch S3, which pulls the FBADJ pin low, allowing the sub OLED to turn on. Figure 5 shows that the sub OLED is grounded as well.

## **Applications Information**

### **Component Selection**

The component values shown in the application circuits will be sufficient for most applications (typical application circuits are shown in figure 1, and the Typical Applications section). To reduce the output ripple, the output inductor may be increased in value, but in most cases this will result in excessive board area and cost.

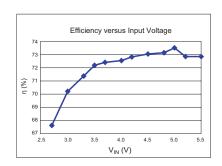

### Inductor Selection

The inductor is the most important component in the power supply design because it affects the steady-state performance, transient response, and loop stability. The inductance value, DC resistance, and the saturation current should be considered when choosing the inductor. The DC current of the inductor can be calculated by:

$$I_{\rm L_DC} = \frac{V_{\rm OUT} \times I_{\rm OUT}}{V_{\rm IN} \times \eta}$$

(3)

and the inductance value can be calculated by:

$$L_{\min} = \frac{V_{i\min}}{\Delta_i \times \eta} \times \left(1 - \frac{V_{i\min}}{V_{OUT}}\right) \times \frac{1}{f}$$

(4)

where  $\Delta i = (20\% \text{ to } 40\%) \times I_{L_{DC}}$  is the peak-to-peak ripple current.

Smaller inductance values force the converter into discontinuous mode, which will reduce the maximum output current. Larger inductance values reduce the gain and phase margin, which will result in instability of the loop.

The inductor should have low winding resistance, typically  $< 0.2 \Omega$  and low 1.2 MHz core loss for better efficiency.

The inductor should have a saturation current higher than 1.5 A, in order to provide 20 V at the OUT1 pin, and 100 mA at 2.7  $V_{IN}$ . For high temperature operation, a suitable derating factor should be considered. Several inductor manufacturers, including: Coilcraft, Murata, Panasonic, Sumida, Taiyo Yuden, and TDK, have and are developing suitable small-size inductors.

### **Diode Selection**

The diode should have a low forward voltage to reduce conduction losses and a low capacitance to reduce switching losses. Schottky diodes can provide both of these features, if carefully selected. The forward voltage drop is a natural advantage for Schottky diodes and decreases as the current rating increases. However, as the current rating increases, the diode capacitance also increases, so the optimum selection is usually the lowest current rating above the circuit maximum.

The diode RMS current rating should be:

$$I_{\text{DIODE(RMS)}} = I_{\text{OUT}} \times (1-D)^{1/2}$$

(5)

Diode PIV should be higher than the output voltage on the CAP pin.

### **Capacitor Selection**

1

The input capacitor selection is based on the input voltage ripple. It can be calculated as:

$$C_{\rm IN}(\rm min) = \frac{\Delta i}{8 \times f_{\rm SW} \times V_{\rm IN(ripple)}}$$

(6)

where  $V_{IN(ripple)}$  is the input ripple.

The output capacitor selection is based on the output ripple requirement. It can be calculated by:

$$C_{\rm OUT} = \frac{V_{\rm OUT} - V_{\rm IN}}{V_{\rm OUT}} \times \frac{1}{f} \times \frac{I_{\rm OUT}}{V_{\rm ripple(pp)}}$$

(7)

where V<sub>ripple</sub> is the peak-to-peak output ripple.

In addition, the ESR-related output ripple can be calculated by:

$$V_{\text{ripple(ESR)}} = I_{\text{OUT}} \times ESR$$

. (8)

If a ceramic capacitor is selected, the ESR-related ripple can be neglected, due to the low ESR. If a tantalum electrolytic capacitor is selected, this portion of ripple voltage has to be considered.

During load transient response, a larger output capacitance always helps to supply or absorb additional current, which results in lower overshoot and undershoot voltage.

Because the capacitor values are low, ceramic capacitors are the best choice for this application. To reduce performance variation over temperature, low drift types such as X7R and X5R should be used. Recommended specifications are shown in the table below. Suitable capacitors are available from TDK, Taiyo Yuden, Murata, Kemet, and AVX.

The output capacitor is placed on the CAP pin only. An additional capacitor can be added on the OUT1 pin, but it is not needed for proper operation and it cannot replace the capacitor on the CAP pin.

## Boost Regulator for Display Bias or LED Driver

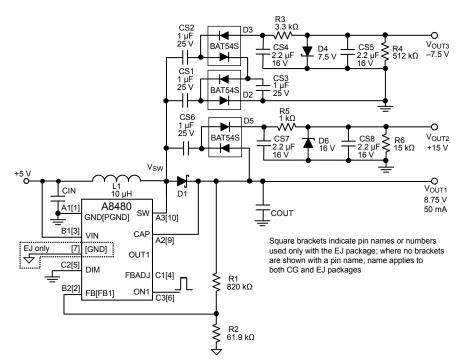

Figure 2a. Dual outputs ( $V_{OUT}$  and  $-V_{OUT}$ )

Figure 2b. Triple outputs ( $V_{OUT}$ ,  $-V_{OUT}$ , and  $2V_{OUT}$ )

# Boost Regulator for Display Bias or LED Driver

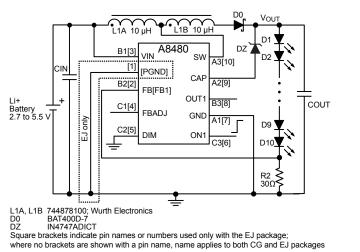

#### Figure 3. Using the A8480 to drive 10 white LEDs (WLED)

Square brackets indicate pin names or numbers used only with the EJ package; where no brackets are shown with a pin name, name applies to both CG and EJ packages

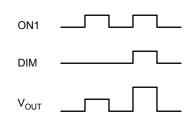

Figure 4b. Timing diagram for circuit shown in figure 4a.

## Boost Regulator for Display Bias or LED Driver

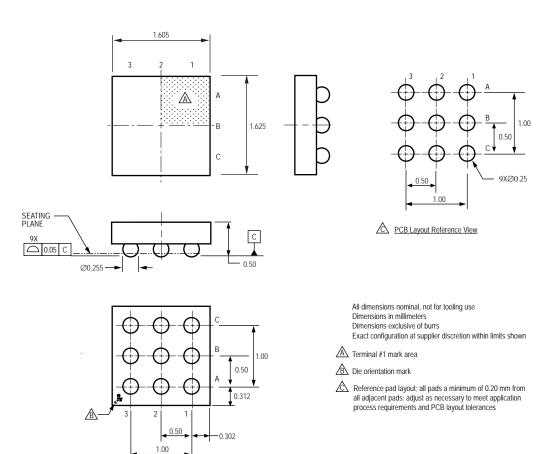

Square brackets indicate pin names or numbers used only with the EJ package; where no brackets are shown with a pin name, name applies to both CG and EJ packages

Square brackets indicate pin names or numbers used only with the EJ package; where no brackets are shown with a pin name, name applies to both CG and EJ packages

Square brackets indicate pin names or numbers used only with the EJ package; where no brackets are shown with a pin name, name applies to both CG and EJ packages

#### Figure 7. A8480 driving high current flash/torch LEDs

Package CG, 9-Pin CSP

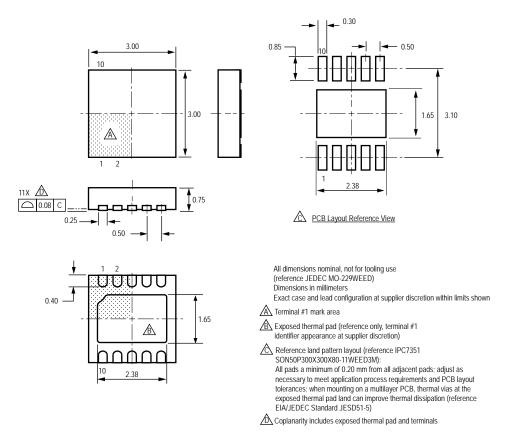

Package EJ, 10-Pin MLP/DFN

Copyright ©2007, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com