# Fast Transient Response, 3A Dual Supply Very Low Dropout Linear Regulator

### DESCRIPTION

The MP2040 is a very low dropout, dual supply linear regulator. The use of two supplies allows the BIAS to control an NMOS device. The NMOS device supplies power to the load via the IN. In this way the input supply can be just above the desired output, yet still provide very good regulation performance due to the higher bias supply. The BIAS operates from a 3.3V to 5.5V input and regulates the output voltage to as low as 0.9V, and as high as 3.3V.

The MP2040 can supply up to 3A of load current with a typical dropout voltage of 150mV. The BIAS runs the internal reference and drive circuitry, while the output current comes directly from the IN for high efficiency regulation.

Other features of MP2040 include thermal overload and current limit protection, power good indicator, stability with ultra low ESR ceramic capacitors as low as 1uF, and fast transient response. The MP2040 is available in 10-pin QFN (3mm x 3mm), and in QFN (5mm x 5mm) packages.

### **FEATURES**

- Wide 1.1V to 5V Input Voltage Range

- Stable with Very Small Ceramic Capacitors

- 150mV Dropout at 3A Output

- 2% Accurate Output Voltage

- Adjustable Output Range of 0.9V to 3.3V

- Low Noise: 80µV<sub>RMS</sub> (10Hz to 100kHz)

- Very fast transient response

- PSRR

- o 40dB at 100kHz

- Better Than 0.001%/mA Load Regulation

- Stable With Low-ESR Output Capacitors

- Internal Thermal Protection

- Current Limit Protection

- 0.1µA Typical Quiescent Current at Shutdown

- Power Good Indicator

## **APPLICATIONS**

- Industrial Process & Control Equipment

- Telecom Equipment

- PAID Storage

- DSP/ASIC/µC Post Regulation for Switching Power Supplies

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

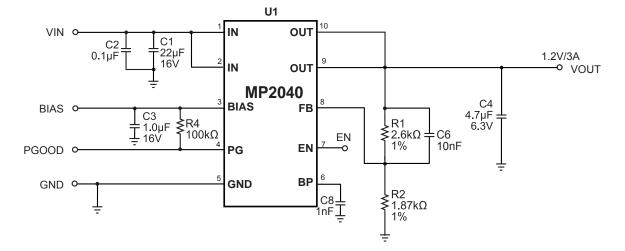

## TYPICAL APPLICATION

© 2010 MPS. All Rights Reserved.

## ORDERING INFORMATION

| Part Number | Package   | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|-------------|-----------|-------------|----------------------------------------|

| MP2040DQ*   | 3x3 QFN10 | 7D          | -40°C to +85°C                         |

| MP2040DU**  | 5x5 QFN32 | MP2040DU    | -40°C to +85°C                         |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP2040DQ–Z).

For RoHS compliant packaging, add suffix -LF (e.g. MP2040DQ-LF-Z)

\*\* For Tape & Reel, add suffix -Z (e.g. MP2040DU-Z).

For RoHS compliant packaging, add suffix -LF (e.g. MP2040DU-LF-Z)

## **PACKAGE REFERENCE**

| , , DOULD I E III) ()                      |                                                  |

|--------------------------------------------|--------------------------------------------------|

| V <sub>BIAS</sub> , V <sub>IN</sub> to GND | 0.3V to +6V                                      |

| FB, EN, to GND                             | 0.3V to 6V                                       |

| V <sub>OUT</sub>                           | 0.3V to $V_{\text{IN}}$ + 0.3 or 6V              |

| PGOOD                                      | -0.3V to $V_{\text{BIAS}}$ + 0.3 or 6V           |

| BYPASS                                     | 0.3V to $V_{\text{BIAS}}$ +0.3 or 6V             |

| Continuous Power Diss                      | sipation (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                            | 2.5W                                             |

| QFN32 5X5                                  | 3.47W                                            |

| Junction Temperature.                      | 150°C                                            |

|                                            | 260°C                                            |

| Storage Temperature .                      | 65°C to +150°C                                   |

| Recommended Ope                            | erating Conditions <sup>(3)</sup>                |

|                                            | 1.1V to 5.5V                                     |

| Thermal Resistance <sup>(4)</sup> | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |

|-----------------------------------|-------------------------|-------------------------|

| QFN10 3X3                         | 50                      | 12 °C/W                 |

| QFN32 5X5                         | 36                      | 8 °C/W                  |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 1.5V,  $V_{BIAS}$  = 3.6V,  $V_{OUT}$  = 1.2V,  $C_{OUT}$  = 1 $\mu$ F,  $C_{IN}$  = 0.1 $\mu$ F,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                           | Symbol | Condition                                                                                                                 | Min   | Тур   | Max   | Units |

|-------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>IN</sub> Operating Voltage   |        |                                                                                                                           | 1.1   |       | 5.5   | V     |

| V <sub>BIAS</sub> Operating Voltage |        | I <sub>OUT</sub> = 2A                                                                                                     | 3.3   |       | 5.5   | V     |

| V <sub>BIAS</sub> Operating Current |        |                                                                                                                           |       | 3.5   |       | mA    |

| FB Regulation Voltage               |        |                                                                                                                           | 0.5   | 0.51  | 0.52  | V     |

|                                     |        | $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                                   | 0.495 | 0.51  | 0.525 |       |

| Dropout Voltage                     |        | $I_{OUT} = 3A$ , $V_{BIAS} = 3.6V$                                                                                        |       | 150   |       | mV    |

| V <sub>IN</sub> Line Regulation     |        | $I_{OUT} = 1 mA,$<br>$V_{IN} = 1.5 \text{ to } 5V$<br>$V_{BIAS} = 5V V_{OUT} = 1.2V$                                      |       | 1     |       | mV    |

| V <sub>BIAS</sub> Line Regulation   |        | $I_{OUT} = 1 \text{mA},$<br>$V_{BIAS} = 3.6 \text{V to } 5.5 \text{V } V_{OUT} = 1.2 \text{V}$<br>$V_{IN} = 1.5 \text{V}$ |       | 2     |       | mV    |

| Load Regulation                     |        | I <sub>OUT</sub> = 1mA to 1A                                                                                              |       | 0.001 |       | %/mA  |

| PSRR (V <sub>IN</sub> )             |        | $V_{IN} > V_{OUT} + 0.5V$ , $C_{OUT} = 4.7\mu F$ , $V_{IN}(AC) = 100 \text{mV}$ , $f = 100 \text{kHz}$ $V_{B} = 5V$       |       | 40    |       | dB    |

| Power Good Threshold                |        |                                                                                                                           |       | 440   |       | mV    |

| Power Good Delay                    |        |                                                                                                                           |       | 80    |       | μs    |

| Current Limit (5)                   |        |                                                                                                                           |       | 3.6   |       | Α     |

| Soft Start                          |        | BYPASS=open                                                                                                               |       | 280   |       | μs    |

| Power Good Voltage                  |        | I <sub>sink</sub> =230µA                                                                                                  |       | 0.39  |       | V     |

| EN Input High Voltage               |        |                                                                                                                           | 1.5   |       |       | V     |

| EN Input Low Voltage                |        |                                                                                                                           |       |       | 0.8   | V     |

| EN Input Bias Current               |        | V <sub>EN</sub> = 1.2V                                                                                                    | -1    |       | +1    | μA    |

| Thermal Protection                  |        |                                                                                                                           |       | 135   |       | °C    |

| Thermal Protection Hysteresis       |        |                                                                                                                           |       | 15    |       | °C    |

### Notes:

3

<sup>5)</sup> Guaranteed by Designer.

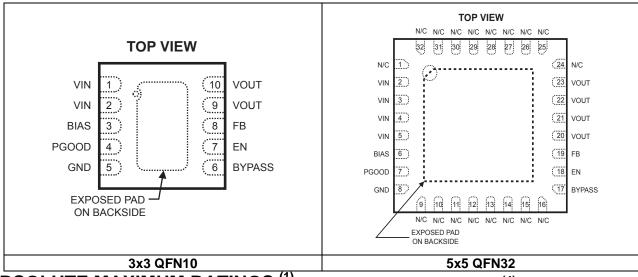

# **PIN FUNCTIONS**

# QFN3X3 10pins

| Pin#  | Name   | Description                                                                                                                                       |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 10 | VOUT   | Regulator Output. OUT is the output of the linear regulator, By pass OUT to GND with a 4.7µF or greater capacitor.                                |

| 3     | BIAS   | Bias Voltage. Bypass to ground with a 1µF or greater capacitor, VB>=VIN.                                                                          |

| 8     | FB     | Feedback Input. Connect a resistive voltage divider from OUT to FB to set the output voltage. OUT feedback threshold is 0.51V.                    |

| 7     | EN     | Enable Input. Drive EN high to turn on the MP2040, drive EN low to turn it off. For automatic startup, connect EN to IN.                          |

| 5     | GND    | Ground, exposed pad.                                                                                                                              |

| 1, 2  | VIN    | Power Source Input. IN supplies power to the load at the output (through the power transistor). Bypass IN to GND with a 1µF or greater capacitor. |

| 4     | PGOOD  | Open drain output. High indicated V <sub>OUT</sub> > <b>90%</b> final value.                                                                      |

| 6     | BYPASS | Connect a 1nF to this pin. Do not load this pin resistively.                                                                                      |

# QFN5x5 32pins

| Pin#                                                                                      | Name   | Description                                                                                                                                       |  |

|-------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 20, 21,22,<br>23                                                                          | VOUT   | Regulator Output. OUT is the output of the linear regulator, By pass OUT to GND with a 4.7µF or greater capacitor.                                |  |

| 6                                                                                         | BIAS   | Bias Voltage. Bypass to ground with a 1µF or greater capacitor, VB>=VIN.                                                                          |  |

| 19                                                                                        | FB     | Feedback Input. Connect a resistive voltage divider from OUT to FB to set the output voltage. OUT feedback threshold is 0.51V.                    |  |

| 18                                                                                        | EN     | Enable Input. Drive EN high to turn on the MP2040, drive EN low to turn it off. For automatic startup, connect EN to IN.                          |  |

| 8                                                                                         | GND    | Ground, exposed pad.                                                                                                                              |  |

| 2, 3, 4, 5                                                                                | VIN    | Power Source Input. IN supplies power to the load at the output (through the power transistor). Bypass IN to GND with a 1µF or greater capacitor. |  |

| 7                                                                                         | PGOOD  | Open drain output. High indicated V <sub>OUT</sub> > <b>90%</b> final value.                                                                      |  |

| 17                                                                                        | BYPASS | Connect a 1nF to this pin. Do not load this pin resistively.                                                                                      |  |

| 1, 9, 10,<br>11, 12,<br>13, 14,<br>15, 16,<br>24, 25,<br>26, 27,<br>28, 29,<br>30, 31, 32 | NC     | These are no connection pins.                                                                                                                     |  |

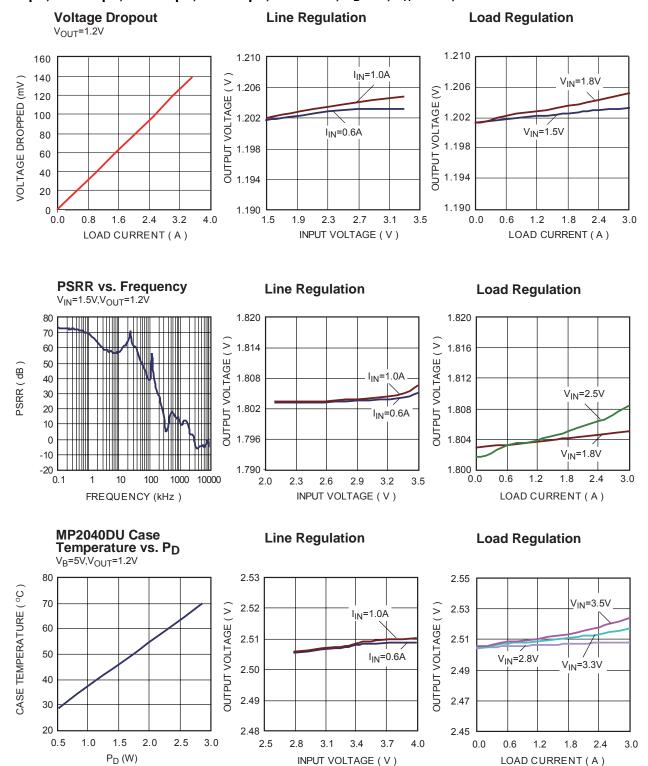

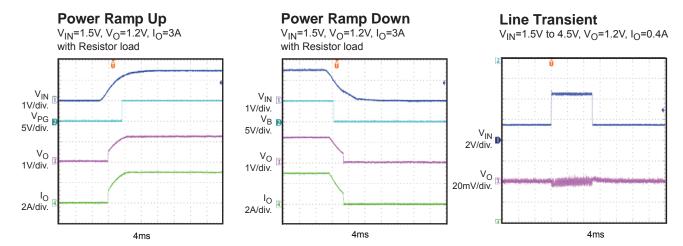

# TYPICAL PERFORMANCE CHARACTERISTICS

C1=22μF, C2=0.1μF, C3=1.0μF, C4=4.7μF, C6=22nF, V<sub>B</sub>=5V, T<sub>A</sub>=25°C, unless otherwise noted

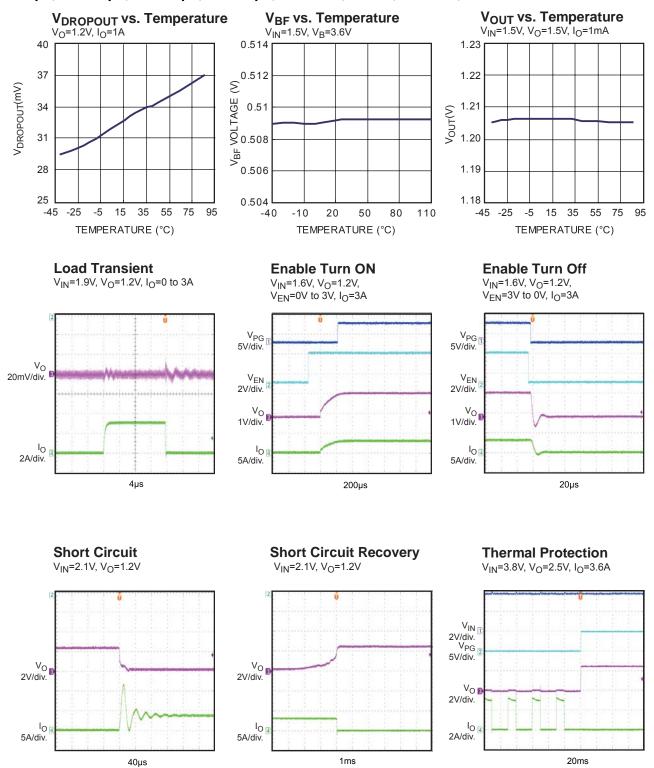

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

C1=22μF, C2=0.1μF, C3=1.0μF, C4=4.7μF, C6=22nF, V<sub>B</sub>=5V, T<sub>A</sub>=25°C, unless otherwise noted

6

# TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

C1=22 $\mu$ F, C2=0.1 $\mu$ F, C3=1.0 $\mu$ F, C4=4.7 $\mu$ F, C6=22nF, V<sub>B</sub>=5V, T<sub>A</sub>=25 $^{\circ}$ C, unless otherwise noted

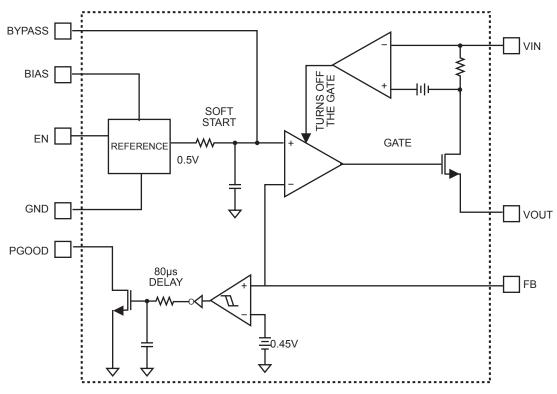

## **BLOCK DIAGRAM**

Figure 1—Block Diagram of Low Dropout Regulator

## **OPERATION**

### MP2040 Theory of Operation

The MP2040 linear dropout regulator provides adjustable output voltages from 0.9V to 3.3V at currents up to 3A. This LDO is protected against short circuits, and it has thermal shut down protection with 15°C hystheresis.

### **Utilizing Two Power Supplies**

In order to maximize the efficiency MP2040 uses two power supplies. One power supply is connected to the BIAS pin and it is used to power up the internal circuitries including band gap reference and the rest of control circuitries. The other power supply is connected to the VIN pins which are the drain of pass device. This power supply can be set close to output voltage of LDO. The output pins are the source of the pass device. The smaller voltage drop across the pass device translates to the smaller power loss in pass device. Thus, the part operates with higher efficiency.

#### Internal Current Limit

The MP2040 has an internal current limit set at almost 3.8A. Internal current limit is very well controlled over process variations and ambient temperature.

#### **Enable**

The enable (EN) pin is active high. The enable pin has a built-in hystheresis. If this pin is held below 0.8V then part shuts down and draws less than 1uA from  $V_{BIAS}$  supply.

If not used then connect this pin to V<sub>BIAS</sub>.

#### **Under Voltage Lockout**

The Bias voltage is monitored by a circuit that prevents the LDO start up when the bias voltage is below 2.35V. This circuitry has an approximate hystheresis of 90mV.

#### **Soft Start**

MP2040 incorporates internal soft start function. This internal function reduces the start up current surge into the output capacitor. This allows the gradual built up of output voltage to its final set value. The internal soft start cap is held to ground if there is a fault condition. The fault conditions are UVLO, Thermal shut down, and disable. The internal soft start time is almost 280µ

#### **Power Good**

The Power Good pin is an open drain output and can be connected to Bias voltage via a pull up resistor. Open drain transistor turns off and PG pin voltage value becomes  $V_{\text{BIAS}}$  when  $V_{\text{FB}}$  exceeds 450mV. Also PG pin can sink at least 230 $\mu$ A while being low.

### **Setting the Output Voltage**

The MP2040 has an adjustable output voltage, set by using a resistive voltage divider from the output voltage to FB pin. The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \times R_2 / (R_1 + R_2)$$

Where  $V_{FB}$  is the feedback threshold voltage ( $V_{FB}$ =0.5V), and  $V_{OUT}$  is the output voltage.  $R_1$  connects between  $V_{OUT}$  and  $V_{FB}$ , and  $R_2$  connects between  $V_{FB}$  and ground.

Thus the output voltage is:

$$V_{OUT} = 0.5 \times (R_1 + R_2)/R_2$$

$R_2$  can be as high as  $100k\Omega$ , but a typical value is  $10k\Omega$ . Using that value,  $R_1$  is determined by:

$$R_1=R_2 \times (V_{OUT}-V_{FB})/V_{FB}$$

For example, for a 1.8V output voltage,  $R_2$  is  $10k\Omega$ , and  $R_1$  is  $26k\Omega$ . You can select  $26k\Omega$  (1%) resistor for  $R_1$ .

#### **Power Dissipation**

Most of the power dissipation is due to power dissipation in PASS device. For example, assume  $V_{\text{BIAS}}$ =5.0V,  $V_{\text{IN}}$ =2.0V,  $V_{\text{OUT}}$ =1.8V, and  $I_{\text{OUT}}$ =3A:

$$P_D (P_{ASS}) = (V_{IN}-V_{OUT}) \times I_{OUT}$$

$P_D (P_{ASS}) = (2.0V-1.8V) \times 3A=0.6W$

$P_{BIAS}$  =  $V_{BIAS}$  x  $I_{GND}$ = 5V x (220 $\mu$ A) = 1.25mW. This is negligible compared to  $P_{D}$  ( $P_{ASS}$ ) =0.6W

For QFN 3X3  $\theta_{JA}$  is 50°C/W.

0.6W power is dissipated when 3A output current goes through PASS device with  $V_{\text{IN}}$ =2.0V, and  $V_{\text{OUT}}$ =1.8V.

This gives a rise in die temperature for 0.6 x 50°C/W=30°CThis is a safe operating point assuming a junction temperature of 135°C at an 85°C ambient temperature.

A heat sink needs to be utilized for a better temperature performance.

### APPLICATION INFORMATION

#### PG

The power good pin is an open drain output a pull up resistor ( $100k\Omega$  recommended). The pull up resistor can be tied to a supply within the voltage range of the pin (0 to 5.5V). For example, the pull up resistor can be tied to the input voltage that is monitored by an IC powered from this input voltage. If the output voltage is 10% below its regulation point, the PG pin becomes low

## **Bypass Capacitors**

For lower noise, the reference voltage can be bypassed by an external capacitor. A low ESR capacitor, such as the ceramic type, will provide the best performance.

It also can function as an external soft start, the soft start time:

Tss=1000 x C<sub>RP</sub>

### **Performance Transient Response**

For a 3A transient response, suggests increasing the input capacitance should be increased to  $22\mu F$  or higher to get better performance. This will also avoid glitches on the PG pin due to excessive undershoot. Also increase the input voltage 0.4V above the  $V_{\text{OUT}}$ , to improve the load transient response.

## **Maximum Output Voltage and Load Current**

If the  $V_{\text{OUT}}$  is set to 3.3V then the maximum output current will be decreased to 2.5A. The maximum bias voltage limits the  $V_{\text{OUT}}$ .  $V_{\text{OUT}}$  must be at least 2.5V less than  $V_{\text{B}}$ ;

$$V_{OUT}=V_B$$

-2.5V

### **Bias Input Voltage**

The bias input is designed for low drop application. The bias pin must be at least 3.3V,

and at least 2.5V higher than the output voltage. If the  $V_{IN}$  supply voltage meets these requirements, the bias pin can be tied to  $V_{IN}$ .

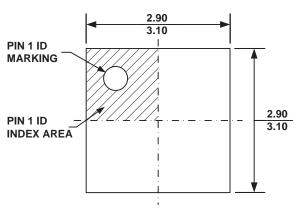

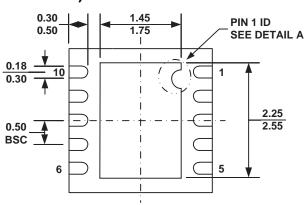

# **PACKAGE INFORMATION**

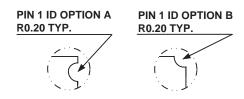

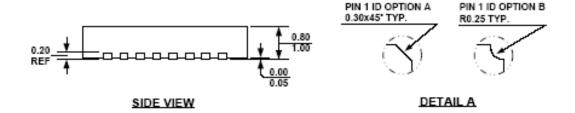

# **QFN10 (3mm x 3mm)**

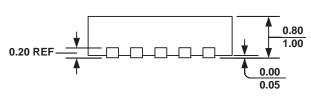

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**DETAIL A**

#### **RECOMMENDED LAND PATTERN**

## **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFORMS TO JEDEC MO-229, VARIATION VEED-5.

- 5) DRAWING IS NOT TO SCALE.

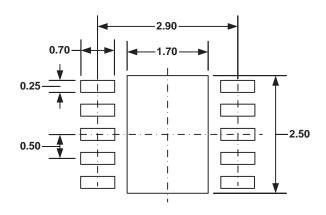

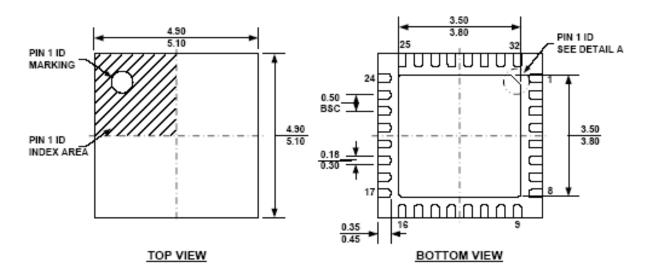

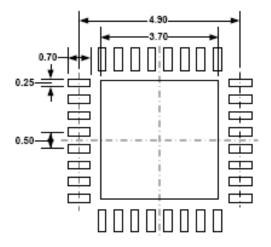

# **QFN32 (5mm x 5mm)**

#### RECOMMENDED LAND PATTERN

## NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFIRMS TO JEDEC MO-220, VARIATION VHHC-2.

- 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.