## MONOLITHIC CLOCK SYNCHRONIZER (SERIES 3D6701)

FEATURES

- Synchronizes free-running clock to external gate signal

- Input frequency range: 30MHz through 100MHz

- Phase resolution: 200ps typical

- **Output frequency:** Programmable from  $F_{IN}$  to  $F_{IN}/256$

- Output period jitter: Equal to jitter of clock source

- All-silicon, low-power CMOS technology

- TTL/CMOS compatible inputs and outputs

- Vapor phase, IR and wave solderable

FUNCTIONAL DESCRIPTION

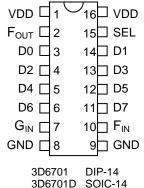

space-saving 16-pin SOIC package.

Auto-insertable (DIP pkg.)

One major drawback to using a crystal oscillator for frequency generation is that the phase of the generated clock signal cannot be synchronized to an external timing event. A delay-line oscillator (eg, the 3D7701), while supporting this feature, cannot provide the stability and jitter performance of a crystal. The 3D6701 clock synchronizer provides the best of both worlds. The device accepts two inputs – a stable frequency source and a gate signal – and matches the phase of the clock to the gate. It also provides 8 bits of frequency scaling at the device output. The 3D6701 can be operated at 5V or 3.3V, and is offered in both a 16-pin DIP and a

For mechanical dimensions, click here.

For package marking details, click here.

#### **PIN DESCRIPTIONS**

| F <sub>IN</sub> | Clock Input         |

|-----------------|---------------------|

| G <sub>IN</sub> | Gate Input          |

| D0-D7           | Divisor Inputs      |

| SEL             | VDD Select Input    |

| FOUT            | Sync Oscillator Out |

| VDD             | +3.3 or +5 Volts    |

| GND             | Ground              |

©2014 Data Delay Devices

# PINOUT

data

Compliant

devices

#### THEORY OF OPERATION

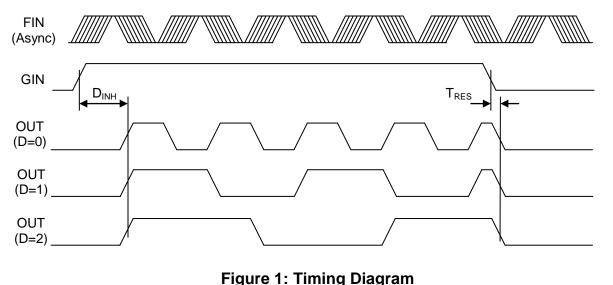

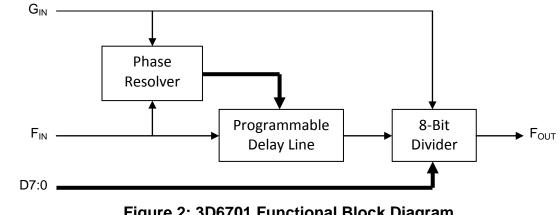

The 3D6701 clock synchronizer architecture is shown in Figure 2. The F<sub>IN</sub> input is assumed to come from a stable clock source, such as a crystal oscillator. A rising edge on the GIN input initiates the phase detection process. Once the phase of the clock with respect to the gate has been resolved, a delay line is adjusted to match the phases of the two signals.

There is a finite resolution to the phase detection process (typically under 500ps), so that, from one gate trigger to the next, there will remain some residual gate-to-output jitter. However, for a given gate, the jitter from one clock cycle to the next is equal to the jitter of the reference clock itself.

The 3D6701 also contains a programmable divider that reduces the output frequency by an amount given by the D7:0 inputs. FOUT is given by  $F_{IN}$  / (D+1), so that the output frequency may range from  $F_{IN}$  (D=0) to  $F_{IN}$  / 256 (D=255). When G<sub>IN</sub> returns low, the output returns to a low level and remains there until the next rising edge of G<sub>IN</sub>.

The performance of CMOS integrated circuits is strongly dependent on power supply stability. It is essential that the power supply pins be adequately bypassed and filtered. In addition, the power bus should be of as low an impedance construction as possible. Power planes are preferred.

When operating at 3.3V, tie the SEL input to GND. When operating at 5.0V, tie the SEL input to VDD.

Figure 2: 3D6701 Functional Block Diagram

#### **DEVICE SPECIFICATIONS**

| TABLE 1: | ABSOLUT | E MAXIMUM | RATINGS |

|----------|---------|-----------|---------|

|----------|---------|-----------|---------|

| PARAMETER           | SYMBOL            | MIN  | MAX                  | UNITS | NOTES  |

|---------------------|-------------------|------|----------------------|-------|--------|

| DC Supply Voltage   | V <sub>DD</sub>   | -0.3 | 7.0                  | V     |        |

| Input Pin Voltage   | V <sub>IN</sub>   | -0.3 | V <sub>DD</sub> +0.3 | V     |        |

| Input Pin Current   | I <sub>IN</sub>   | -1.0 | 1.0                  | mA    | 25C    |

| Storage Temperature | T <sub>STRG</sub> | -55  | 150                  | С     |        |

| Lead Temperature    | $T_{LEAD}$        |      | 300                  | С     | 10 sec |

### **DEVICE SPECIFICATIONS (Cont'd)**

#### TABLE 2: DC ELECTRICAL CHARACTERISTICS

(-40C to 85C, 3.0V to 5.25V)

| PARAMETER                 | SYMBOL          | MIN | TYP   | MAX  | UNITS | NOTES                                         |

|---------------------------|-----------------|-----|-------|------|-------|-----------------------------------------------|

| Static Supply Current*    | I <sub>DD</sub> |     | 20.0  |      | mA    |                                               |

| High Level Input Voltage  | V <sub>IH</sub> | 2.0 |       |      | V     |                                               |

| Low Level Input Voltage   | V <sub>IL</sub> |     |       | 0.8  | V     |                                               |

| High Level Input Current  | I <sub>IH</sub> |     |       | 1.0  | μΑ    | $V_{IH} = V_{DD}$                             |

| Low Level Input Current   | I               |     |       | 1.0  | μA    | $V_{IL} = 0V$                                 |

| High Level Output Current | I <sub>OH</sub> |     | -35.0 | -4.0 | mA    | V <sub>DD</sub> =4.75V, V <sub>OH</sub> =2.4V |

| Low Level Output Current  | I <sub>OL</sub> | 4.0 | 15.0  |      | mA    | $V_{DD}$ =4.75V, $V_{OL}$ =0.4V               |

\*I<sub>DD</sub> will vary slightly for different input clock frequencies

#### TABLE 3: AC ELECTRICAL CHARACTERISTICS

| PARAMETER           | SYMBOL               | MIN | TYP | MAX | UNITS | NOTES                  |

|---------------------|----------------------|-----|-----|-----|-------|------------------------|

| Input Frequency     | F <sub>IN</sub>      | 30  |     | 80  | MHz   |                        |

| Duty Cycle          | DC(F <sub>IN</sub> ) | 40  |     | 60  | %     |                        |

| Gate Frequency      | G <sub>IN</sub>      |     |     | 1   | MHz   |                        |

| Gate Inactive (Low) | G <sub>IN,LOW</sub>  | 200 |     |     | ns    |                        |

| Gate-to-Out Delay   | D <sub>INH</sub>     |     | 157 |     | ns    | F <sub>IN</sub> =50MHz |

|                     |                      |     | 136 |     | ns    | F <sub>IN</sub> =62MHz |

|                     |                      |     | 120 |     | ns    | F <sub>IN</sub> =80MHz |

| Gate-to-Out Delay   | $\Delta D_{INH}$     |     | 420 |     | ps    | F <sub>IN</sub> =50MHz |

| Jitter              |                      |     | 460 |     | ps    | F <sub>IN</sub> =62MHz |

|                     |                      |     | 780 |     | ps    | F <sub>IN</sub> =80MHz |

| FOUT Period Jitter  |                      |     |     | 50  | ps    |                        |

| Reset Time          | T <sub>RES</sub>     |     | 10  |     | ns    |                        |

(-40C to 85C, 3.0V to 3.6V)

#### TABLE 4: AC ELECTRICAL CHARACTERISTICS

(-40C to 85C, 4.75V to 5.25V)

| PARAMETER                      | SYMBOL               | MIN | TYP | MAX | UNITS | NOTES                  |

|--------------------------------|----------------------|-----|-----|-----|-------|------------------------|

| Input Frequency                | F <sub>IN</sub>      | 50  |     | 100 | MHz   |                        |

| Duty Cycle                     | DC(F <sub>IN</sub> ) | 40  |     | 60  | %     |                        |

| Gate Frequency                 | G <sub>IN</sub>      |     |     | 2   | MHz   |                        |

| Gate Inactive (Low)            | G <sub>IN,LOW</sub>  | 125 |     |     | ns    |                        |

| Gate-to-Out Delay              | D <sub>INH</sub>     |     | 138 |     | ns    | F <sub>IN</sub> =50MHz |

|                                |                      |     | 118 |     | ns    | F <sub>IN</sub> =62MHz |

|                                |                      |     | 106 |     | ns    | F <sub>IN</sub> =80MHz |

| Gate-to-Out Delay              | $\Delta D_{INH}$     |     | 640 |     | ps    | F <sub>IN</sub> =50MHz |

| Jitter                         |                      |     | 700 |     | ps    | F <sub>IN</sub> =62MHz |

|                                |                      |     | 520 |     | ps    | F <sub>IN</sub> =80MHz |

| F <sub>OUT</sub> Period Jitter |                      |     |     | 50  | ps    |                        |

| Reset Time                     | T <sub>RES</sub>     |     | 10  |     | ns    |                        |

### SILICON DELAY LINE AUTOMATED TESTING

OUTPUT:

R<sub>load</sub>:

Cload:

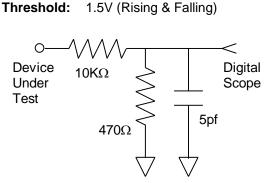

#### **TEST CONDITIONS**

#### INPUT:

| Ambient Temperature:  | 25°C ± |

|-----------------------|--------|

| Supply Voltage (Vcc): | 5.0V ± |

| Input Pulse:          | High = |

|                       | Low =  |

Source Impedance: Rise/Fall Time:  $25^{\circ}C \pm 3^{\circ}C$   $5.0V \pm 0.1V$ High =  $3.0V \pm 0.1V$ Low =  $0.0V \pm 0.1V$   $50\Omega$  Max. 3.0 ns Max. (measured between 0.6 and 2.4V)

$10K\Omega\pm10\%$

5pf ± 10%

**NOTE:** The above conditions are for test only and do not in any way restrict the operation of the device.

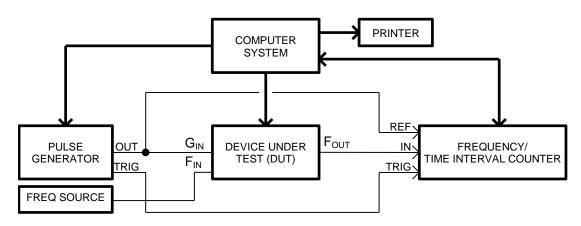

Figure 3: Test Setup

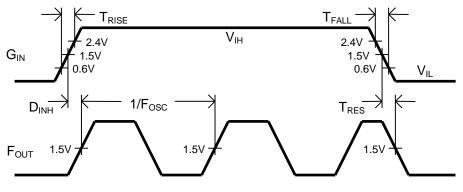

Figure 4: Timing Diagram