# FLASH AND CellularRAM<sup>™</sup> COMBO MEMORY

# MT28C256532W18T MT28C256564W18T

Low Voltage, Wireless Temperature

#### **Features**

Stacked die Combo package

- · Includes two 128Mb Flash devices

- Choice of either one 32Mb or one 64Mb CellularRAM™ device

#### Basic configuration

#### Flash

- · Flexible multibank architecture

- 8 Meg x 16 Async/Page/Burst interface

- Support for true concurrent operations with no latency

#### CellularRAM

- Low power, high-density design

- 2 Meg x 16 or 4 Meg x 16 configurations

- Burst

#### F\_VCC, VCCQ, F\_VPP, C\_VCC voltages

- 1.70V (MIN)/1.95V (MAX) F\_VCC, C\_VCC

- 1.70V (MIN)/2.24V (MAX) VCCQ

- 1.80V (TYP) F VPP (in-system PROGRAM/ERASE)

- 12V ±5% (HV) F\_VPP tolerant (factory programming compatibility)

#### Fast programming Algorithm (FPA)

#### Enhanced suspend options

- ERASE-SUSPEND-to-READ within same bank

- PROGRAM-SUSPEND-to-READ within same bank

- ERASE-SUSPEND-to-PROGRAM within same bank

Each Flash contains two 64-bit chip protection registers for security purposes

100,000 ERASE cycles per block

Cross-compatible command set support

- · Extended command set

- Common Flash interface (CFI) compliant

#### **Options**

#### Flash Timing

- 60ns<sup>1</sup>

- 70ns

#### Flash Burst Frequency

- 66 MHz<sup>1</sup>

- 54 MHz

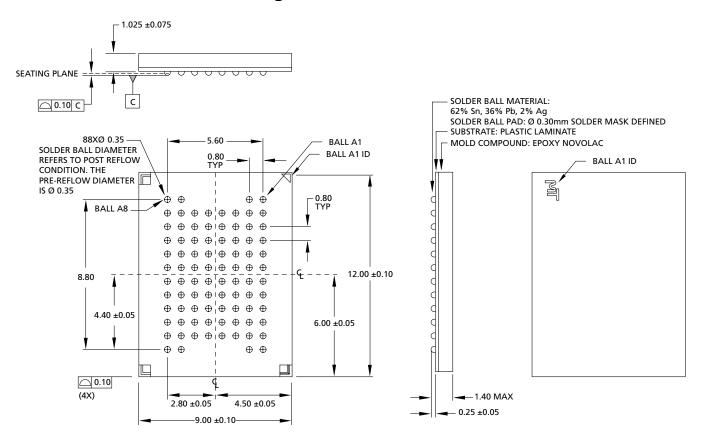

### Figure 1: 88-Ball FBGA

#### Flash Boot Block Configuration

- Top/Top

- Top/Bottom

- Bottom/Top

- Bottom/Bottom

#### CellularRAM Timing

- 70ns

- 85ns

#### CellularRAM Burst Frequency

• 66 MHz

#### I/O Voltage Range

VCCO 1.70V-2.24V

#### **Operating Temperature Range**

• Wireless Temperature (-25°C to +85°C)

#### Package

- 88-ball FBGA (Standard) 8 x 10 grid with eight support balls

- 88-ball FBGA (Lead-free) 8 x 10 grid with eight support balls<sup>2</sup>

NOTE: 1. Contact factory for availability.

2. Contact factory for details.

# **Table of Contents**

| Features                                  | 1  |

|-------------------------------------------|----|

| General Description                       | 5  |

| Flash Configurations                      | 5  |

| Device Marking                            |    |

| Part Numbering Information                | 88 |

| MultiChip Packaging Considerations        |    |

| Unique IDs, State Machines, and Registers | 10 |

| Command Codes                             |    |

| READ Operation                            |    |

| WRITE Operation                           |    |

| Flash Reset                               |    |

| Power Consumption                         |    |

| Flash Electrical Specifications           |    |

| Data Sheet Designation                    |    |

| Revision History                          |    |

# **PRELIMINARY**

# 256Mb MULTIBANK BURST FLASH 32Mb/64Mb BURST CellularRAM COMBO

# **List of Figures**

| 88-Ball FBGA      | ]                                                                          |

|-------------------|----------------------------------------------------------------------------|

| Flash Memory Map  | 6                                                                          |

| Block Diagram     | 7                                                                          |

| Part Number Chart | 8                                                                          |

| 88-Ball FBGA      | 7                                                                          |

|                   | 88-Ball FBGA Flash Memory Map Block Diagram Part Number Chart 88-Ball FBGA |

# **PRELIMINARY**

# 256Mb MULTIBANK BURST FLASH 32Mb/64Mb BURST CellularRAM COMBO

### **List of Tables**

| Table 1: | Cross-Reference for Abbreviated Device Marks | 88 |

|----------|----------------------------------------------|----|

| Table 2: | Valid Part Number Combinations               | 8  |

| Table 3: | Ball Descriptions                            |    |

| Table 4: | Truth Table                                  |    |

| Table 5: | Absolute Maximum Ratings                     |    |

| Table 6: | Recommended Operating Conditions             | 12 |

| Table 7: | Capacitance                                  |    |

| Table 8: | AC Characteristics                           | 12 |

| Table 9: | CFI                                          |    |

### **Device General Description**

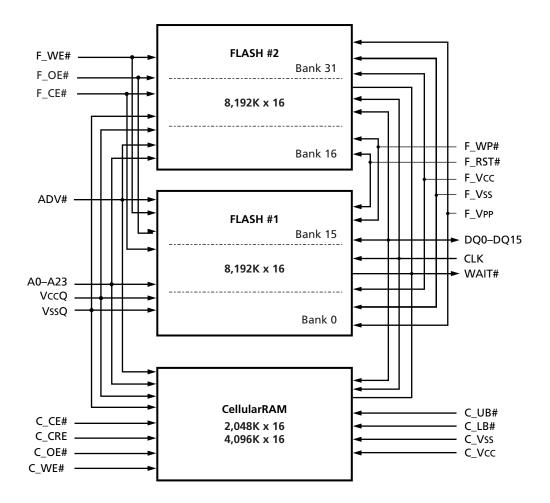

The MT28C256532W18T/MT28C256564W18T combination Flash and CellularRAM is a high-performance, high-density, memory solution that can significantly improve system performance. This memory solution is comprised of two 128Mb Flash devices and one 32Mb or one 64Mb CellularRAM device.

It is important to note that the specifications contained in this document supersede the specifications listed in the referenced individual Flash and Cellular-RAM data sheets.

## **Flash General Description**

The Flash architecture features a multipartition configuration that supports READ-While-PROGRAM/ERASE operations with no latency. An 8Mb partition size enables optimal design flexibility.

Two Flash devices are stacked to achieve the 256Mb density. Both Flash die share a dedicated CE# and OE# control.

The stacked Flash device enables soft protection for blocks, as read only, by configuring soft protection registers with dedicated command sequences. For security purposes, two user-programmable 64-bit chip protection registers are provided for each Flash device.

The embedded WORD PROGRAM and BLOCK ERASE functions are fully automated by an on-chip write state machine (WSM). An on-chip device status register can be used to monitor the WSM status and determine the progress of the PROGRAM/ERASE tasks.

Each Flash device has a read configuration register (RCR) that defines how the Flash interacts with the memory bus. For device specifications and additional documentation concerning Flash, please refer to the MT28F1284W18 data sheet at www.micron.com/flash.

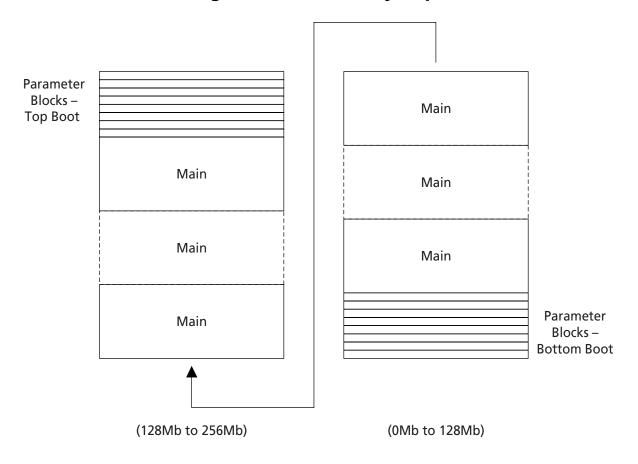

# Flash Configurations

Each Flash memory implements a multibank architecture (16 banks of 8Mb each) to allow concurrent operations. Any address within a block address range selects that block for the required READ, PROGRAM, or ERASE operation.

Each Flash memory features eight 8K-word sectors (8 x 65,536 bits), designated as parameter blocks, and the remaining part is organized in main blocks of 64K

words each (524,288 bits). The parameter blocks are addressed either by the low order addresses (bottom boot) or by the higher order addresses (top boot).

The two Flash devices can be supplied with any combination of top or bottom boot (e.g., top/top, bottom/bottom, top/bottom, or bottom/top). Please see Figures 1 and 2 for more information.

### CellularRAM General Description

The CellularRAM architecture features high-speed CMOS, dynamic random-access memories developed for low-power portable applications The CellularRAM device is available in either 32Mb or 64Mb densities.

To operate seamlessly on a burst Flash bus, CellularRAM products have incorporated a transparent self-refresh mechanism. The hidden refresh requires no additional support from the system memory controller and has no significant impact on device read/write performance.

The refresh configuration register (RCR) is used to control how refresh is performed on the CellularRAM array. These registers are automatically loaded with default settings during power-up and can be updated any time during normal operation. Special attention has been focused on standby current consumption during self-refresh.

CellularRAM products include three system-accessible mechanisms used to minimize standby current. Partial array refresh (PAR) limits refresh to the portion of the memory array being used. Temperature compensated refresh (TCR) is used to adjust the refresh rate according to the ambient temperature. The refresh rate can be decreased at lower temperatures to minimize current consumption during standby. Deep sleep mode halts the refresh operation altogether and is used when no vital information is stored in the device. These three refresh mechanisms are adjusted through the refresh configuration register (RCR).

For device specifications and additional documentation concerning CellularRAM memory, please refer to the MT45W2MW16BFB and MT45W4MW16BFB CellularRAM data sheets at www.micron.com/cellularram.

**Figure 1: Flash Memory Map**

#### NOTE:

Figure 1 shows a TB (top/bottom) dual Flash configuration.

Figure 2: Block Diagram

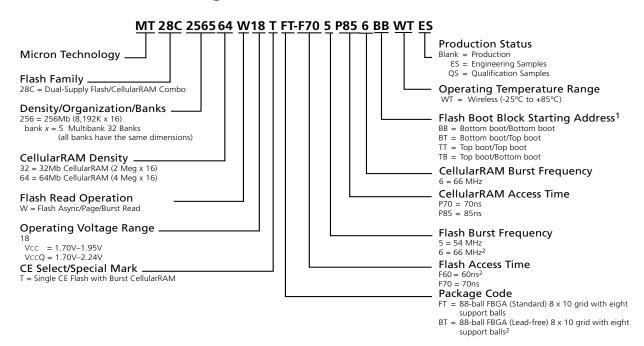

# **Part Numbering Information**

Micron's combination memory devices are available with several different combinations of features (see Figure 3).

**Figure 3: Part Number Chart**

#### NOTE:

- 1. The first character in this field refers to Flash die #2. The second character in this field refers to Flash die #1.

- 2. Contact factory for availability.

#### **Valid Part Number Combinations**

After building the part number from the part number chart above, please go to Micron's Part Marking Decoder Web site at www.micron.com/decoder to verify that the part number is offered and valid. If the device required is not on this list, please contact the factory.

## **Device Marking**

Due to the size of the package, the Micron standard part number is not printed on the top of each device. Instead, an abbreviated device mark comprised of a five-digit alphanumeric code is used. The abbreviated device marks are cross-referenced to the Micron part numbers at www.micron.com/decoder. To view the location of the abbreviated mark on the device, please refer to customer service note CSN-11, "Product Mark/ Label," at www.micron.com/csn.

# **Table 1: Ball Descriptions**

| 88-BALL FBGA<br>NUMBERS                                                 | SYMBOL   | TYPE   | DESCRIPTIONS                                               |  |

|-------------------------------------------------------------------------|----------|--------|------------------------------------------------------------|--|

| G1, F1, E1, D1, B1,                                                     | A0-A23   | Input  | Addresses:                                                 |  |

| C1, F2, E2, F6, D7,                                                     |          |        | Flash: A0–A23.                                             |  |

| E7, B8, C8, D8, F7,                                                     |          |        |                                                            |  |

| E8, F8, D2, B2, B3,                                                     |          |        | CellularRAM: A0–A20 (32Mb).<br>CellularRAM: A0–A21 (64Mb). |  |

| E6, B7, C7, C3<br>K1                                                    | F 6F#    | 1      | Flash Chip Enable.                                         |  |

|                                                                         | F_CE#    | Input  | ·                                                          |  |

| J2                                                                      | F_OE#    | Input  | Flash Output Enable.                                       |  |

| F5                                                                      | F_WE#    | Input  | Flash Write Enable.                                        |  |

| E4                                                                      | F_WP#    | Input  | Flash Write Protect.                                       |  |

| E5                                                                      | ADV#     | Input  | Address Valid (burst operation only).                      |  |

| C6                                                                      | CLK      | Input  | Clock (burst operation only).                              |  |

| F4                                                                      | F_RST#   | Input  | Flash Reset.                                               |  |

| C2                                                                      | C_LB#    | Input  | CellularRAM Lower Byte Control.                            |  |

| F3                                                                      | C_UB#    | Input  | CellularRAM Upper Byte Control.                            |  |

| D5                                                                      | C_WE#    | Input  | CellularRAM Write Enable.                                  |  |

| H1                                                                      | C_OE#    | Input  | CellularRAM Output Enable.                                 |  |

| D6                                                                      | C_CE#    | Input  | CellularRAM Chip Enable.                                   |  |

| K8                                                                      | C_CRE    | Input  | CellularRAM Deep Sleep Mode and Configuration Mode.        |  |

| H2, H3, G3, H4, J5,<br>G5, J6, H7, G2, J3,<br>G4, J4, H5, G6, H6,<br>J7 | DQ0-DQ15 | I/O    | Flash/CellularRAM Data Input/Output.                       |  |

| G7                                                                      | WAIT#    | Output | WAIT#. See "WAIT Ball Operation" on page 10.               |  |

| L7                                                                      | F_Vss    | Supply | Flash Core Ground.                                         |  |

| D4                                                                      | F_VPP    | Supply | Flash VPP.                                                 |  |

| B5, B6, K6, L4                                                          | F_Vcc    | Supply | Flash Core Power Supply.                                   |  |

| B4, C4, L5, L1, L8                                                      | C_Vss    | Supply | CellularRAM Core Ground.                                   |  |

| K5                                                                      | C_Vcc    | Supply | CellularRAM Core Power Supply.                             |  |

| J8, K7, L3                                                              | VccQ     | Supply | Flash/CellularRAM I/O Supply.                              |  |

| L2, L6                                                                  | VssQ     | Supply | Flash/CellularRAM I/O Ground.                              |  |

| A1, A2, A7, A8, C5,<br>G8, H8, J1, K2, K3,<br>K4, M1, M2, M7,<br>M8     | NC       | -      | No Connect. Not internally connected to the die.           |  |

| D3, E3                                                                  | RFU      | -      | Reserved for Future Use (A24, A25).                        |  |

# **Boot Configurations**

The possible configurations for Flash die are shown in Table 2 below. This table shows the possible configurations of the two Flash devices for either top boot or bottom boot.

Table 2: Possible Boot Configurations for Flash Die

| CONFIGURATION | F_CE#  | ORDER CODE |

|---------------|--------|------------|

| Top/Top       | Тор    | TT         |

| Top/Bottom    | Bottom | ТВ         |

| Bottom/Top    | Тор    | ВТ         |

| Bottom/Bottom | Bottom | BB         |

### **MultiChip Packaging Considerations**

Multichip packaging presents unique challenges when controlling complex memory devices.

The MT28C256532W18 and MTC256564W18 devices combine two Micron Flash devices with a single CellularRAM device.

# Unique IDs, State Machines, and Registers

Each Flash device has a separate command state machine (CSM) and status register (SR) and read configuration register (RCR). The read configuration register (RCR) settings are separate and can be different for the upper and lower device. Each Flash device has its own OTP, CFI, and device code. Depending on the boot configuration of each Flash device, the OTP, CFI, and device code information may differ.

The CellularRAM memory has a refresh configuration register (RCR) that defines how the device performs self refresh, and a bus configuration register (BCR) to define the interface configuration.

#### **Command Codes**

All Flash command codes are independent within each device. Care must be taken when crossing the array boundary between the upper and lower Flash device and the CellularRAM device to ensure that only one device is enabled at one time.

In a two-cycle command sequence such as word program (0x40/data), it is required that both commands be issued to the same device.

It is not recommended that simultaneous READ, simultaneous WRITE, or simultaneous ERASE operations occur on both Flash devices.

### **READ Operation**

All READ operations are limited to the address boundaries of each device. The Flash device boundary is encountered when A23 changes logic states.

Addresses with A23 = 0 access Flash #1.

Addresses with A23 = 1 access Flash #2.

A new READ operation must be started when crossing the device boundary.

### **WRITE Operation**

The WRITE operation is limited to the address boundaries of each device. The Flash device boundary is encountered when A23 changes logic states.

Addresses with A23 = 0 access Flash #1.

Addresses with A23 = 1 access Flash #2.

A new WRITE operation must be started when crossing the device boundary.

### **Flash Reset**

The reset control is shared by both Flash die. Bringing F\_RST# conrol LOW will reset both the upper and lower device.

## **WAIT Ball Operation**

It is important to note that the Flash and Cellular-RAM devices share the WAIT ball functionality and must be configured correctly for proper burst mode operation. The Flash and CellularRAM devices use different registers to configure the WAIT polarity and have opposite default values.

The WAIT ball polarity for the Flash device is configured by programming bit 10 in the read configuration register (RCR). The default is active LOW.

The WAIT ball polarity for the CellularRAM device is configured by programming bit 10 in the bus configuration register (BCR). The default is active HIGH.

Both the Flash and CellularRAM WAIT ball polarities must be set to the same active level for proper operation

### **Power Consumption**

Multiple chip packaging requires that power calculations consider the active operation of the upper and lower Flash device as well as that of the CellularRAM device. Total power consumed will be the sum of the currents associated with the state of each device.

Table 3: **Truth Table**

|        |                       |       | FLASH S                 | IGNALS <sup>2</sup> |        | SHARED | SIGNALS             |                                             | Cell                                 | ularRAM S  | SIGNALS          |                 | MEMORY                   | OUTPUT       |

|--------|-----------------------|-------|-------------------------|---------------------|--------|--------|---------------------|---------------------------------------------|--------------------------------------|------------|------------------|-----------------|--------------------------|--------------|

|        | MODES                 | F_CE# | F_OE#                   | F_WE#               | F_RST# | ADV#   | WAIT#               | C_CE#                                       | C_CRE                                | C_OE#      | C_UB/LB#         | C_WE#           | MEMORY<br>BUS<br>CONTROL | DQ0-<br>DQ15 |

|        | Read                  | L     | L                       | Н                   | Н      | L      | Active <sup>1</sup> | Cell                                        | CellularRAM memory must be in High-Z |            |                  | ah-7            | Flash                    | Dout         |

| #      | Write                 | L     | Н                       | L                   | Н      | Х      | Asserted            | CCII                                        | alai NAIVI                           | incinory i | ilast be ill ill | 911 2           | Flash                    | DIN          |

|        | Standby               | Н     | Х                       | Х                   | Н      | Х      | High-Z              |                                             |                                      |            |                  |                 | Other                    | High-Z       |

| FLASH  | Output<br>Disable     | L     | Н                       | Н                   | Н      | Х      | Active <sup>1</sup> | CellularRAM memory any mode allowable Other |                                      |            |                  | High-Z          |                          |              |

|        | Reset                 | Х     | Х                       | Х                   | L      | Х      | High-Z              | ,                                           |                                      |            |                  | None            | High-Z                   |              |

|        | Read                  | L     | L                       | Н                   | Н      | L      | Active <sup>1</sup> | CellularRAM memory must be in High-Z        |                                      |            |                  | Flash           | Dout                     |              |

| #2     | Write                 | L     | Н                       | L                   | Н      | Х      | Asserted            | CellularkAM memory must be in high-z        |                                      |            |                  | Flash           | DIN                      |              |

|        | Standby               | Н     | Х                       | Х                   | Н      | Х      | High-Z              |                                             |                                      |            |                  | Other           | High-Z                   |              |

| FLASH  | Output<br>Disable     | L     | Н                       | Н                   | Н      | Х      | Active <sup>1</sup> | CellularRAM memory any mode allowable Other |                                      |            |                  | Other           | High-Z                   |              |

|        | Reset                 | Х     | Х                       | Х                   | L      | Х      | High-Z              | None                                        |                                      |            |                  | None            | High-Z                   |              |

| RY     | Read                  | EI    | Flash must be in High-Z |                     |        | L      | Active <sup>1</sup> | L H L L H                                   |                                      |            | Н                | Cellular<br>RAM | Douт                     |              |

| MEMORY | Write                 | FI    | asii iiiust k           | e in riigii         | I-Z    | L      | Active <sup>1</sup> | L H H L L                                   |                                      |            | Cellular<br>RAM  | DIN             |                          |              |

|        | Standby               |       |                         |                     |        | Х      | Х                   | Н                                           | Н                                    | Х          | Х                | Х               | Other                    | High-Z       |

| arRAM  | Output<br>Disable     | Fla   | sh any mo               | de allowa           | ihle   | Х      | Х                   | L H H X H Oth                               |                                      |            | Other            | High-Z          |                          |              |

| Cellul | Deep<br>Sleep<br>Mode | 110   | sir arry mo             | ac anowa            | ibie   | Х      | Х                   | Н                                           | L                                    | Х          | Х                | х               | Other                    | High-Z       |

#### NOTE:

- 1. WAIT status is only valid for burst mode operation. WAIT should be ignored for all other operating modes.

2. If A23 = 0, then Flash #1 is selected; and if A23 = 1, then Flash #2 is selected.

# **Electrical Specifications**

# **Table 4: Absolute Maximum Ratings**

Note 1

| PARAMETERS/CONDITIONS       | MIN | МАХ  | UNITS | NOTES |

|-----------------------------|-----|------|-------|-------|

| Operating Temperature Range | -25 | +85  | °C    |       |

| Storage Temperature Range   | -55 | +125 | °C    |       |

| Soldering Cycle             |     | +260 | °C    | 2     |

#### NOTE:

- 1. Stresses greater than those listed in Table 4 may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. See technical note TN-00-15, "Recommended Soldering Techniques," for more information.

## **Table 5: Recommended Operating Conditions**

| PARAMETER                            | SYMBOL | MIN  | TYP | MAX  | UNITS |

|--------------------------------------|--------|------|-----|------|-------|

| Vcc Supply Voltage (F_Vcc and C_Vcc) | Vcc    | 1.70 | _   | 1.95 | V     |

| I/O Supply Voltage                   | VccQ   | 1.70 | _   | 2.24 | V     |

# **Table 6: Capacitance**

$T_A = +25$ °C; f = 1 MHz

| PARAMETER/CONDITION | SYMBOL | TYP | MAX | UNITS |

|---------------------|--------|-----|-----|-------|

| Input Capacitance   | CIN    | 13  | 17  | pF    |

| Output Capacitance  | Соит   | 18  | 20  | pF    |

| Clock Capacitance   | CCLK   | 20  | 22  | pF    |

#### **Table 7: DC Characteristics**

It is important to note that the specifications contained in this document supersede the specifications listed in the referenced individual Flash and CellularRAM data sheets. All currents are in RMS unless otherwise noted.

| PARAMETER                                                                                                       | SYMBOL | ТҮР        | MAX        | UNITS | NOTES |

|-----------------------------------------------------------------------------------------------------------------|--------|------------|------------|-------|-------|

| VCC Standby Current<br>with 32Mb CellularRAM<br>with 64Mb CellularRAM                                           | Iccs   |            | 210<br>220 | μА    | 4     |

| Vcc Standby Current with CellularRAM Device in deep power-down mode with 32Mb CellularRAM with 64Mb CellularRAM | ISBZZ  | 110<br>110 |            | μА    | 1, 4  |

| Vcc Program Suspend Current<br>with 32Mb CellularRAM<br>with 64Mb CellularRAM                                   | Iccws  |            | 210<br>220 | μА    | 2, 4  |

| Vcc Erase Suspend Current<br>with 32Mb CellularRAM<br>with 64Mb CellularRAM                                     | ICCES  |            | 210<br>220 | μА    | 2, 4  |

| VCC Automatic Power Save Current<br>with 32Mb CellularRAM<br>with 64Mb CellularRAM                              | ICCAPS |            | 210<br>220 | μА    | 3, 4  |

#### NOTE:

- 1. C\_CRE ball HIGH, CR4 bit in the CellularRAM refresh configuration register set to zero. Measured at 25°C, this standby current is the sum of the Flash standby current and the CellularRAM deep-power down mode current.

- 2. ICCES and ICCWS values are valid when the device is deselected. Any READ operation performed while in suspend mode will have an additional current draw of suspend current.

- 3. Automatic power save (APS) mode reduces Icc to approximately Iccs levels.

- 4. Currents are measured using CellularRAM full array self-refresh. Currents may be further reduced by using the TCR or PAR features.

#### Table 8: CFI

It is important to note that the specifications contained in this document supersede the specifications listed in the referenced individual Flash and CellularRAM data sheets.

| OFFSET | DATA       | DESCRIPTION         |

|--------|------------|---------------------|

| 78     | 32Mb: 0020 | CellularRAM Density |

|        | 64Mb: 0040 |                     |

Figure 4: 88-Ball FBGA

#### NOTE:

1. All dimensions in millimeters.

#### **Data Sheet Designation**

**Preliminary:** This data sheet contains initial characterization limits that are subject to change upon full of characterization of production devices.

For additional documentation concerning Flash and CellularRAM features, functional descriptions, programming, and timing, please refer to the table below.

| DEVICE      | PART NUMBER                  | LINK                       |

|-------------|------------------------------|----------------------------|

| Flash       | MT28F1284W18                 | www.micron.com/flash       |

| CellularRAM | MT45W2MW16BFB, MT45W4MW16BFB | www.micron.com/cellularram |

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

E-mail: prodmktg@micron.com, Internet: http://www.micron.com, Customer Comment Line: 800-932-4992

Micron, the M logo, and the Micron logo are trademarks and/or service marks of Micron Technology, Inc.

CellularRAM is a trademark of Micron Technology, Inc., inside the U.S. and a trademark of Infineon Technologies outside the U.S.

All other trademarks are the property of their respective owners.

### **PRELIMINARY**

# 256Mb MULTIBANK BURST FLASH 32Mb/64Mb BURST CellularRAM COMBO

# **Revision History**

| Rev C, Preliminary                                                     | 2/04  |

|------------------------------------------------------------------------|-------|

| Updated standby current specifications in the DC Characteristics Table |       |

| Rev B, Preliminary                                                     | 11/03 |

| Original document, Rev. A                                              | 7/03  |