## MC12015 MC12016 MC12017

#### 225 MHz DUAL MODULUS PRESCALER

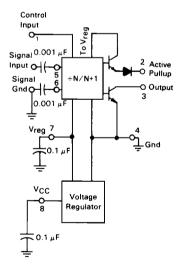

The MC12015, MC12016 and MC12017 are two-modulus prescalers which will divide by 32 and 33, 40 and 41, and 64 and 65 respectively. An internal regulator is provided to allow these devices to be used over a wide range of power-supply voltages. The devices may be operated by applying a supply voltage of 5.0 Vdc  $\pm$  10% at pin 7 or by applying an unregulated voltage source from 5.5 Vdc to 9.5 Vdc to pin 8.

- 225 MHz Toggle Frequency

- ◆ Low-Power 7.5 mA Max at 6.8 V

- Control Input and Output are Compatible with Standard CMOS

- Connecting Pins 2 and 3 Allows Driving One TTL Load

- Supply Voltage 4.5 V to 9.5 V

### MECL PLL COMPONENTS

225 MHz DUAL MODULUS PRESCALER

P SUFFIX PLASTIC PACKAGE CASE 626

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751

#### MAXIMUM RATINGS

| WAZINOW RATINGS             |                           |             |      |  |  |

|-----------------------------|---------------------------|-------------|------|--|--|

| Characteristic              | Symbol                    | Range       | Unit |  |  |

| Regulated Voltage, Pin 7    | V <sub>reg</sub>          | 8.0         | Vdc  |  |  |

| Power Supply Voltage, Pin 8 | Vcc                       | 10.0        | Vdc  |  |  |

| Operating Temperature Range | T <sub>A</sub> -40 to +85 |             | °C   |  |  |

| Storage Temperature Range   | T <sub>stg</sub>          | -65 to +175 | °C   |  |  |

# ELECTRICAL CHARACTERISTICS ( $v_{CC}$ = 5.5 to 9.5, $v_{reg}$ = 4.5 to 5.5 V $T_A$ = -40°C to +85°C)

| Characteristic                                        | Symbol           | Min | Тур | Max      | Unit |

|-------------------------------------------------------|------------------|-----|-----|----------|------|

| Toggle Frequency<br>(Sine wave input)                 | f <sub>max</sub> | 225 | _   |          | MHz  |

|                                                       | fmin             | _   | -   | 35       | MHz  |

| Supply Current                                        | lcc              |     | 6.0 | 7.8      | mA   |

| Control Input High<br>(÷32, 40 or 64)                 |                  | 2.0 |     | _        | ٧    |

| Control Input Low<br>(÷33, 41 or 65)                  |                  | _   | _   | 0.8      | ٧    |

| Output Voltage High*<br>(I <sub>source</sub> = 50 μA) | VOH              | 2.5 | _   | _        | ٧    |

| Output Voltage Low*<br>(I <sub>Sink</sub> = 2 mA)     | V <sub>OL</sub>  | _   | -   | 0.5      | ٧    |

| Input Voltage Sensitivity<br>35 MHz                   | V <sub>in</sub>  | 400 |     | 800      |      |

| 50-225 MHz                                            |                  | 200 | _   | 800      | mVPI |

| PLL Response Time<br>(Notes 1 and 2)                  | †PLL             |     | _   | tout -70 | ns   |

#### Notes:

- tp\_L = the period of time the PLL has from the prescaler rising output transition (50%) to the modulus control input edge transition (50%) to ensure proper modulus selection.

- 2. tout = period of output waveform

## PRESCALER BLOCK DIAGRAM

- Vreg @ pin 7 is not guaranteed to be between 4.5 and 5.5 V when Vcc is being applied to pin 8.

- Pin 7 is not to be used as a source of regulated output voltage.

<sup>\*</sup>Pin 2 connected to Pin 3