# RC9696/14 V.32 bis 14400 bps 2-Wire Modem

# INTRODUCTION

The Rockwell RC9696/14 is a 14400 bps 2-wire, full-duplex, synchronous/asynchronous, V.32 bis modern data pump module. It operates over the public switched telephone network (PSTN) through the appropriate line termination.

The modem satisfies the requirements specified in CCITT recommendations V.32 bis, V.32, V.17/V.33, V.29, V.27 ter, V.22 bis, V.22, V.23, and V.21; is compatible with Bell 212A and Bell 103 modems; and supports Group 3 facsimile (fax).

The RC9696/14 can operate at 14400, 12000, 9600, 7200, 4800, 2400, 1200, 600, or 300 bps depending upon the selected configuration.

The RC9696/14 is designed for use in high speed data applications. User programmable features allow the modem operation to be tailored to support a wide range of functional requirements.

The dual-in-line pin (DIP) connection allows direct installation onto a host module. The modem's small size (less than 13 square inches), low power consumption, serial/parallel host interface, and DIP connection simplify system development and reduce system production cost.

Detailed hardware and software interface information is described in the RC9696/14 and RC1496/14 Modem Designer's Guide (Order No. 856).

## **FEATURES**

- 2-wire full-duplex compatibilities

- -CCITT V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21

- -Bell 212A and 103

- 2-wire half-duplex compatibilities

- -CCITT V.17/V.33, V.29, V.27 ter, and V.21 channel 2

- · Group 3 (G3) facsimile send/receive compatible

- · Parallel synchronous

- · Serial synchronous

- · Serial asynchronous up to 9600 bps

- Trellis-coded modulation (TCM) at 14400, 12000, 9600, and 7200 bps

- · Programmable near and far end echo cancellation

- · Bulk delay for satellite transmission

- · Auto-dial and auto-answer capability

- TTL and CMOS compatible DTE interface

- -CCITT V.24 (RS-232-C) (data/control)

- -Microprocessor bus (data/configuration/control)

- Dynamic Range: -43 dBm to 0 dBm

- · Programmable compromise equalizer in transmitter

- · Automatic adaptive equalizer in receiver

- · Diagnostic capability

- V.13 signalling

- V.54 Inter-DCE signalling

- V.54 local analog and remote digital loopback

- Small Size: 82 mm x 100 mm (3.23 in. x 3.94 in.)

- Low power consumption: 1.9 W (typical)

RC9696/14 Modern

# TECHNICAL SPECIFICATIONS

# **CONFIGURATIONS, SIGNALING RATES AND DATA** RATES

The selectable modem configurations, along with the corresponding signaling (baud) rates and data rates, are listed in Table 1.

#### **TONE GENERATION**

Under control of the host processor, the modem can generate single or dual voice-band tones from 0 Hz to 4800 Hz with a resolution of 0.15 Hz and an accuracy of ±0.01%. Tones over 3000 Hz are attenuated. DTMF tone generation allows the modem to operate as a programmable DTMF dialer.

## **DATA ENCODING**

The data encoding conforms to CCITT recommendations V.32 bis, V.32, V.17/V.33, V.29, V.27 ter, V.22 bis, V.22, V.23, and V.21; and to Bell 212A and 103.

### **EQUALIZERS**

Equalization functions are provided that improve performance when operating over low quality lines.

Compromise Equalizer: A 40-tap digital finite impulse response (FIR) filter in the transmitter provides compromise equalization. The filter taps can be changed in DSP RAM for varying line conditions. The default equalizer tap coefficients compensate for half the amplitude distortion of a 3002 unconditioned line and for half the group delay distortion of a 3002 unconditioned line. The filter can be enabled or disabled using the CEQ bit in the Chip 0 interface memory.

A 40-tap digital FIR filter in the receiver provides compromise equalization for V.23 1200 and 600 configurations only. The filter is identical to the transmitter compromise filter and can be programmed via the DSP RAM. This feature is enabled and disabled using the CEQ23 bit in the Chip 1 interface memory.

Automatic Adaptive Equalizer: A 64-tap automatic adaptive equalizer is provided in the receiver. The equalizer can be configured as either a T or a T/2 equalizer using the EQT2 bit in the Chip 2 interface memory.

### TRANSMITTED DATA SPECTRUM

When the compromise equalizer is disabled, the transmitter spectrum is shaped by raised cosine filter functions:

| Configuration                  | Raised Cosine Filter Function |

|--------------------------------|-------------------------------|

| V.32 bis/V.32, V.17/V.33, V.29 | Square root of 12.5%          |

| V.27 ter                       | Square root of 50%            |

| V.22 bis/V.22, Bell 212A       | Square root of 75%            |

Table 1. Configurations, Signaling Rates and Data Rates

|                                       |                         | Carrier Frequency Data Rate |                 | Baud           | Bits per Symbol |     | 0                       |

|---------------------------------------|-------------------------|-----------------------------|-----------------|----------------|-----------------|-----|-------------------------|

| Configuration Modulation <sup>1</sup> | Modulation <sup>1</sup> | (Hz)<br>±0.01%              | (bps)<br>±0.01% | (Symbols/Sec.) | Data            | TCM | Constellation<br>Points |

| V.32 bis 14400 TCM                    | TCM                     | 1800                        | 14400           | 2400           | 6               | 1   | 128                     |

| V.32 bis 12000 TCM                    | TCM                     | 1800                        | 12000           | 2400           | 5               | 1   | 64                      |

| V.32 bis 7200 TCM                     | TCM                     | 1800                        | 7200            | 2400           | 3               | 1   | 16                      |

| V.32 9600 TCM                         | TCM                     | 1800                        | 9600            | 2400           | 4               | 1   | 32                      |

| V.32 9600                             | QAM                     | 1800                        | 9600            | 2400           | 4               | 0   | 16                      |

| V.32 4800                             | QAM                     | 1800                        | 4800            | 2400           | 2               | 0   | 4                       |

| V.17/V.33 14400 TCM                   | TCM                     | 1700 or 1800                | 14400           | 2400           | 6               | 1   | 128                     |

| V.17/V.33 12000 TCM                   | TCM                     | 1700 or 1800                | 12000           | 2400           | 5               | 1   | 64                      |

| V.17/V.33 9600 TCM                    | TCM                     | 1700 or 1800                | 9600            | 2400           | 4               | 1   | 32                      |

| V.17/V.33 7200 TCM                    | TCM                     | 1700 or 1800                | 7200            | 2400           | 3               | 1   | 16                      |

| V.29 9600                             | QAM                     | 1700                        | 9600            | 2400           | 4               | 0   | 16                      |

| V.29 7200                             | QAM                     | 1700                        | 7200            | 2400           | 3               | 0   | 8                       |

| V.29 4800                             | QAM                     | 1700                        | 4800            | 2400           | 2               | 0   | 4                       |

| V.27 4800                             | DPSK                    | 1800                        | 4800            | 1600           | . 3             | 0   | 8                       |

| V.27 2400                             | DPSK                    | 1800                        | 2400            | 1200           | 2               | 0   | 4                       |

| V.22 bis 2400                         | QAM                     | 1200/2400                   | 2400            | 600            | 4               | 0   | 16                      |

| V.22 bis 1200                         | QAM                     | 1200/2400                   | 1200            | 600            | 2               | 0   | 4                       |

| V.22 1200                             | QAM                     | 1200/2400                   | 1200            | 600            | 2               | 0   | 4                       |

| V.22 600                              | QAM                     | 1200/2400                   | 600             | 600            | 1               | 0   | 2                       |

| Bell 212A                             | QAM                     | 1200/2400                   | 1200            | 600            | 2               | 0   | 4                       |

| Bell 103                              | FSK                     | 1170/2125                   | 0-300           | 300            | 1               | 0   | -                       |

| V.23 1200                             | FSK                     | 1700/420                    | 1200/75         | 1200           | 1               | 0   | -                       |

| V.23 600                              | FSK                     | 1500/420                    | 600/75          | 600            | 1               | 0   | -                       |

| V.21                                  | FSK                     | 1080/1750                   | 0-300           | 300            | 1               | 0   | -                       |

| V.21 channel 2                        | FSK                     | 1750                        | 300             | 300            | 1               | 0   | -                       |

| Tone Transmit                         |                         |                             | +               |                |                 |     | 1                       |

Notes:

1. Modulation legend:

TCM: Trellis-Coded Modulation

Quadrature Amplitude Modulation QAM:

FSK: Frequency Shift Keying DPSK: Differential Phase Shift Keying

## RTS - CTS RESPONSE TIME

The response times of CTS relative to a corresponding transition of RTS are listed in Table 2.

#### TRANSMIT LEVEL

The transmitter output level is selectable from -0.5 dBm to -15.5 dBm in 1 dB steps and is accurate to  $\pm0.5$  dB. The output level can also be fine tuned to a value within a 1 dB step by changing a gain constant in RAM.

# TRANSMITTER TIMING

Transmitter timing is selectable between internal (±0.01%), external or loopback.

### SCRAMBLER/DESCRAMBLER

The modem incorporates a self-synchronizing scrambler/ descrambler in accordance with the applicable CCITT recommendation.

#### **ANSWER TONE**

The transmitter generates a 2100 Hz answer tone for 3.6 seconds at the beginning of the answer handshake when the NV25 bit is a zero. This is applicable to V.32 bis, V.32, V.22 bis, V.22, V.23, and V.21. The V.32 bis/V.32 answer tone has 180° phase reversals every 0.45 seconds to disable network echo cancellers.

#### RECEIVE LEVEL

The receiver satisfies performance requirements for received line signal levels from 0 dBm to -43 dBm. The received line signal level is measured at the Receiver Analog (RXA) input.

Table 2. RTS-CTS Response Time

|                              | RTS-CT              | RTS-CTS Response <sup>1</sup> |                                   |  |  |  |

|------------------------------|---------------------|-------------------------------|-----------------------------------|--|--|--|

| Configuration                | Constant<br>Carrier | Controlled<br>Carrier         | Turn-Off<br>Sequence <sup>3</sup> |  |  |  |

| V.32 bis, V.32               | ≰2 ms               | N/A                           | N/A                               |  |  |  |

| V.17/V.33 Long               | N/A                 | 1393 ms <sup>2</sup>          | 15 ms <sup>4</sup>                |  |  |  |

| V.17/V.33 Short              | N/A                 | 142 ms <sup>2</sup>           | 15 ms <sup>4</sup>                |  |  |  |

| V.29                         | N/A                 | 253 ms <sup>2</sup>           | 12 ms                             |  |  |  |

| V.27 4800 Long               | N/A                 | 708 ms <sup>2</sup>           | 7 ms <sup>4</sup>                 |  |  |  |

| V.27 4800 Short              | N/A                 | 50 ms <sup>2</sup>            | 7 ms <sup>4</sup>                 |  |  |  |

| V.27 2400 Long               | N/A                 | 943 ms <sup>2</sup>           | 10 ms <sup>4</sup>                |  |  |  |

| V.27 2400 Short              | N/A                 | 67 ms <sup>2</sup>            | 10 ms <sup>4</sup>                |  |  |  |

| V.22 bis, V.22,<br>Bell 212A | ≤2 ms               | 270 ms                        | N/A                               |  |  |  |

| V.21                         | 500 ms              | 500 ms                        | N/A                               |  |  |  |

| V.23, Bell 103               | 210 ms              | 210 ms                        | N/A                               |  |  |  |

#### Notes:

- Times listed are CTS turn-on. The CTS OFF-to-ON response time is host programmable in DSP RAM.

- Add echo protector tone duration plus 20 ms when echo protector tone is used during turn-on.

- Turn-off sequence consists of transmission of remaining data and scrambled ones for controlled carrier operation. CTS turn-off is less than 2 ms for all configurations.

- Plus 20 ms of no transmitted energy.

- N/A = not applicable.

#### RECEIVER TIMING

The timing recovery circuit can track a  $\pm 0.035\%$  (V.22 bis) or  $\pm 0.01\%$  (other than V.22 bis) frequency error in the associated transmit timing source.

## **CARRIER RECOVERY**

The carrier recovery circuit can track a ±7 Hz frequency offset in the received carrier with less than a 0.2 dB degradation in bit error rate (BER).

#### CLAMPING

Received Data (RXD) is clamped to a constant mark whenever the Received Line Signal Detector (RLSD) is off. RLSD can be clamped off by a bit in the receiver sample rate device interface memory (RLSDE).

#### **ECHO CANCELLER**

A data echo canceller with near-end and far-end echo cancellation is included for 2-wire full-duplex V.32 operation. The combined echo span of near and far cancellers is host programmable with a default value of 53.3 ms (53.3 ms is also the maximum programmable value). The proportion allotted to each end is host programmable with default values of 23.3 ms for near-end and 30 ms for far-end. The delay between near-end and far-end echoes can be up to 1.7 seconds. The canceller can compensate for ±7 Hz frequency offset in the far-end echo. The echo canceller error signal may be monitored through the transmitter DSP interface memory.

# ASYNC/SYNC, SYNC/ASYNC CONVERSION

An asynchronous-to-synchronous converter is provided in the transmitter and a synchronous-to-asynchronous converter is provided in the receiver. The converter operates in serial mode only. The asynchronous character format is 1 start bit, 5 to 8 data bits, an optional parity bit, and 1 or 2 stop bits. Valid character size, including all bits, is 7, 8, 9, 10, or 11 bits per character. Two ranges of signaling rates are provided:

- Basic: +1% to -2.5%

- Extended overspeed: +2.3% to -2.5%

When the transmitter's converter is operating at the basic signaling rate, no more than one stop bit will be deleted per 8 consecutive characters. When operating at the extended rate, no more than one stop bit will be deleted per 4 consecutive characters. Break is handled in the transmitter and receiver as described in V.14.

Asynchronous characters are accepted by the transmitter on the TXD serial input and issued by the receiver on the RXD serial output. To configure the converters, the host must set up interface memory bits EXOSO, PENO, STBO and WDSZO bits before setting ASYNO for the transmitter and EXOS1, PEN1, STB1 and WDSZ1 bits before setting ASYN1 for the receiver. The converter is not used in V.21, V.23, or Bell 103 mode.

### V.54 INTER-DCE SIGNALLING

The modem supports V.54 inter-DCE signalling procedures in synchronous and asynchronous configurations. Transmission and detection of the preparatory, acknowledgement, and termination phases as defined in V.54 are provided. Three control bits in the transmitter allow the host to send the appropriate bit patterns (V54T, V54A, and V54P). Three control bits in the receiver are used to enable one of three bit pattern detectors (V54TE, V54AE, and V54PE). A status bit in the receiver indicates when the selected pattern detector has found the corresponding bit pattern (V54DT).

# V.13 REMOTE RTS SIGNALLING

The modem supports V.13 remote RTS signalling procedures. Transmission and detection of signalling bit patterns in response to a change of state in the RTS bit or the RTS input signal are provided. A control bit in the transmitter enables V.13 signalling (RRTSE). A control bit in the receiver enables detection of V.13 patterns (RTSDE). A status bit in the receiver is used to indicate the state of the remote RTS signal (RTSDT). This feature may be used to clamp/unclamp the local RLSD and RXD signals in response to a change in the remote RTS signal in order to simulate controlled carrier operation in a constant carrier environment.

# **AUTO-DIALING AND AUTO-ANSWERING CONTROL**

#### **General Description**

The host can perform auto-dialing and auto-answering. These functions include DTMF or pulse dialing, ringing detection and a comprehensive supervisory tone detection scheme. The major parameters of these functions are host programmable, enabling the host to customize the modem to work on the PSTN.

# **Supervisory Tone Detection**

Three parallel tone detectors (A, B, and C) are provided for supervisory tone detection. The signal path to these detectors is separate from the main received signal path. Therefore, the tone detect signal does not pass through the highpass section of the analog receive bandpass filter, enabling the tone detection to be largely independent of the receiver status.

The tone detection bandwidth depends on the configuration:

| Receiver Configuration     | Tone Detection Bandwidth |

|----------------------------|--------------------------|

| V.32 bis, V.32, V.17/V.33, | 0–3400 Hz                |

| V.29, V.27 ter, V.23       |                          |

| V.22 bis, V.22, Bell 212A, | 0-2800 Hz                |

| Bell 103 Originate         |                          |

| V.22 bis, V.22, Bell 212A, | 0–1700 Hz                |

| Bell 103 Answer            |                          |

| V.21 Originate             | 0-2200 Hz                |

| V.21 Answer                | 0–1300 Hz                |

There are, however, some restrictions depending on the receiver configuration and status:

- When DATA1 bit (see Table 8) is a 0, all three tone detectors are enabled.

- When DATA1 bit is a 1 and the receiver is in synchronous mode (except V.32 bis 14400 or 12000), tone detectors A and B are enabled and tone detector C is disabled.

- When DATA1 bit is a 1, the receiver is in asynchronous mode, V.32 bis 14400 or 12000, and the TDAE bit is a 1, tone detector A is enabled and tone detectors B and C are disabled.

- All three tone detectors are disabled during a V.32 bis/V.32 handshake.

Each tone detector consists of two cascaded second order IIR biquad filters. The coefficients are host programmable. Each fourth order filter is followed by a level detector which has host programmable turn-on and turn-off thresholds allowing hysteresis. Tone detector C is preceded by a prefilter and squarer. This circuit is useful for detecting a tone with frequency equal to the difference between two tones that may be simultaneously present on the line. The squarer may be disabled by the SQDIS bit in interface memory causing tone detector C to be an eighth order filter.

# Supervisory Tone Detectors, Default Characteristics

The default bandwidths and thresholds of the tone detectors are as follows:

| Tone Detector | Bandwidth    | Turn-On<br>Threshold | Threshold<br>Turn-Off |

|---------------|--------------|----------------------|-----------------------|

| Α             | 245 - 650 Hz | -25 dBm              | -31 dBm               |

| В             | 360 440 Hz   | -25 dBm              | -31 dBm               |

| C Prefilter   | 0 – 500 Hz   | N/A                  | N/A                   |

| С             | 50 – 110 Hz  | *                    | *                     |

<sup>\*</sup>Tone Detector C will detect a difference tone within its bandwidth when the two tones present are in the range -1 dBm to -26 dBm.

# **GENERAL SPECIFICATIONS**

The power requirements and environmental requirements are listed in Tables 3 and 4, respectively. The module dimensions are listed in Table 5.

Table 3. Modern Power Requirements

| Voltage | Tolerance | Current (Typical)<br>@ 25°C | Current (Maximum)<br>@ 0°C |

|---------|-----------|-----------------------------|----------------------------|

| +5 VDC  | ±5%       | 300 mA                      | 585 mA                     |

| +12 VDC | ±5%       | 3 mA                        | 6 mA                       |

| -12 VDC | ±5%       | 30 mA                       | 36 mA                      |

Note 1. Input voltage ripple ≤ 0.1 volts peak-to-peak. The amplitude of any frequency between 20 kHz and 150 kHz must be less than 500 microvolts peak.

Table 4. Modem Environmental Specifications

| Parameter          | Specification                                                                                 |

|--------------------|-----------------------------------------------------------------------------------------------|

| Temperature        |                                                                                               |

| Operating          | 0°C to +70°C (32°F to 158°F)                                                                  |

| Storage            | -40°C to +80°C (-40°F to 176°F) (Stored in heat sealed antistatic bag and shipping container) |

| Relative Humidity: | Up to 90% noncondensing, or a wet bulb temperature up to 35°C, whichever is less.             |

| Altitude           | -200 feet to +10,000 feet                                                                     |

Table 5. Modern Mechanical Dimensions

| Parameter         | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Board Structure:  | Single PC board with a row of 30 pins and a row of 31 pins in a dual in-line pin configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Dimensions:       | , and the same and |  |

| Width             | 3.228 in. (82 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Length            | 3.937 in. (100 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Component Height  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Top (max.)        | 0.300 in. (7.62 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Bottom (max.)     | 0.130 ln. (3.3 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Weight (max.):    | 3.6 oz. (100 g)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Pin Length (max.) | 0.535 ±0.015 in. (13.6 ± 0.4 mm), gold plated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                   | 0.433 ±0.015 in. (11.0 ± 0.4 mm), gold plated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                   | 0.315 ±0.015 in. (8.0 ± 0.4 mm), gold plated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

# HARDWARE INTERFACE SIGNALS

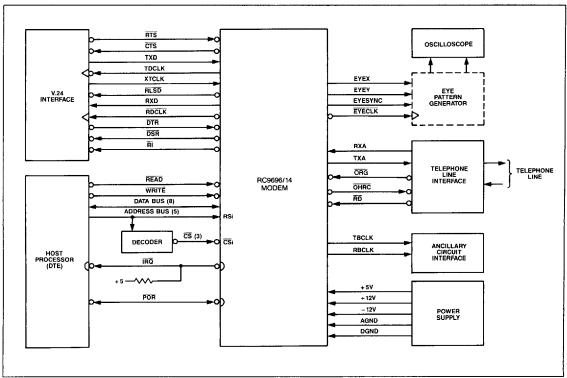

The functional interconnect diagram (Figure 1) shows the typical modem connection in a system. In this diagram, any point that is active low is represented by a small circle at the signal point.

Edge triggered inputs are denoted by a small triangle (e.g., TDCLK). Open-Collector (open-source or open-drain) outputs are denoted by a small half-circle (e.g., IRQ). Active low signals are overscored (e.g., POR).

A clock intended to activate logic on its rising edge (low-to-high transition) is called active low (e.g., RDCLK), while a clock intended to activate logic on its falling edge (high-to-

low transition) is called active high, (e.g., TDCLK). When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

The hardware interconnect signals shown in Figure 1 are organized into six functional groups: overhead, microprocessor interface, V.24 interface, ancillary, analog, and diagnostic. These signals, along with their connector pin numbers and interface circuit types, are listed in Table 6. The digital interface characteristics are defined in Tables 7 and 8, respectively. The hardware interface signals are described in Table 9.

Figure 1. RC9696/14 Functional Interconnect Diagram

Table 6. Hardware Interface Signals

| DVERHEAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Name         | Туре    | Pin No.    | Description               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|------------|---------------------------|

| +5V PWR 1, 45, 61 +5 Volt Supply +12V PWR 32 +12 Volt Supply -12V PWR 36 -12 Volt Supply DGND GND 29, 37, 53 Digital Ground AGND GND 30, 31 Analog Ground MICROPROCESSOR INTERFACE  D7 IA/OB 3 Data Bus Line 7 D6 IA/OB 4 Data Bus Line 6 D5 IA/OB 5 Data Bus Line 6 D5 IA/OB 6 Data Bus Line 6 D5 IA/OB 7 Data Bus Line 3 D2 IA/OB 8 Data Bus Line 2 D1 IA/OB 9 Data Bus Line 1 D0 IA/OB 10 Data Bus Line 1 D0 IA/OB 10 Data Bus Line 1 RS4 IA 15 Register Select Line 4 RS3 IA 16 Register Select Line 3 RS2 IA 17 Register Select Line 2 RS1 IA 18 Register Select Line 1 RS0 IA 19 Register Select Line 0 CS0 IA 20 Chip Select  CS1 IA 21 Chip Select Receiver  Sample Rate Device  CS2 IA 14 Read Enable WRITE IA 12 Write Enable IRQ OC 11 Interrupt Request  V24 INTERFACE  RDCLK OA 46 Transmit Data Clock TTCLK IA 51 External Transmit Clock ATCLK IA 51 External Transmit Clock TTS OA 49 Clear-to-Send TXD IA 48 Transmitter Data RXD OA 26 Receiver Data RLSD OA 27 Received Line Signal Detector DTR IA 40 Data Set Ready | OVERHEAD     |         |            | •                         |

| +5V PWR 1, 45, 61 +5 Volt Supply +12V PWR 32 +12 Volt Supply -12V PWR 36 -12 Volt Supply DGND GND 29, 37, 53 Digital Ground AGND GND 30, 31 Analog Ground MICROPROCESSOR INTERFACE  D7 IA/OB 3 Data Bus Line 7 D6 IA/OB 4 Data Bus Line 6 D5 IA/OB 5 Data Bus Line 6 D5 IA/OB 7 Data Bus Line 2 D1 IA/OB 9 Data Bus Line 2 D1 IA/OB 9 Data Bus Line 2 D1 IA/OB 9 Data Bus Line 1 D0 IA/OB 10 Data Bus Line 1 D0 IA/OB 10 Pata Bus Line 1 RS3 IA 16 Register Select Line 3 RS2 IA 17 Register Select Line 3 RS2 IA 17 Register Select Line 1 RS0 IA 19 Register Select Line 1 RS0 IA 19 Register Select Line 0 CS1 IA 20 Chip Select Receiver Sample Rate Device  CS2 IA 13 Chip Select Receiver  Baud Rate Device  READ IA 14 Read Enable WRITE IA 12 Write Enable IRQ OC 11 Interrupt Request  V24 INTERFACE  RDCLK OA 46 Transmit Data Clock XTCLK IA 51 External Transmit Clock ATTS IA 48 Transmitter Data RXD OA 26 Receiver Data RXD OA 27 Received Line Signal Detector DTR IA 40 Data Set Ready                                  | POR          | IB/OB   | 2          | Power-On-Reset            |

| +12V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | +5V          | PWR     | 1, 45, 61  |                           |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | +12V         | PWR     |            |                           |

| DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -12V         | PWR     | 36         |                           |

| MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DGND         | GND     | 29, 37, 53 |                           |

| MICROPROCESSOR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AGND         | GND     |            |                           |

| D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MICROPROCE   | SSOR IN | TERFACE    |                           |

| D6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D7           | IA/OB   | 3          | Data Bus Line 7           |

| D5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D6           |         | -          |                           |

| D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D5           |         | 5          |                           |

| D3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D4           |         |            |                           |

| D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D3           |         | 7          |                           |

| D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D2           |         |            |                           |

| DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D1           | IA/OB   |            | <del>-</del> <del>-</del> |

| RS4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D0           | IA/OB   | 10         |                           |

| RS3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RS4          | IA      | 15         |                           |

| RS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RS3          | IA      | 16         | •                         |

| RS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RS2          | IA      | 17         |                           |

| RS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RS1          | IA      | 18         |                           |

| CS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RS0          | IA      | 19         | •                         |

| Transmitter Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CS0          | IA      | 20         |                           |

| Sample Rate Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |         |            | •                         |

| CS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CS1          | IA      | 21         | Chip Select Receiver      |

| CS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ĺ            |         |            | Sample Rate Device        |

| READ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CS2          | IA      | 13         |                           |