# HM63941 Series

### 4K × 9-Bit CMOS Parallel In-Out FIFO Memory

#### **■ DESCRIPTION**

The HM63941 is a First-In, First-Out memory that utilizes a high performance static RAM array with internal algorithm that controls, monitors and declares status of the memory by empty flag, full flag and almost-full flag, to prevent data overflow or underflow.

Expansion logic warrants unlimited expansion capability in width and depth. Both read and write are independent from each other and their corresponding pointers are designed to select the proper locations out of the entire array serially without address information to load or unload data.

Data is toggled in and out of the device through the use of the write enable  $(\overline{W})$  and read enable  $(\overline{R})$  pins. The device has a read/write cycle time of 35/45/60ns. Organization of HM63941 provides a 9-bit data bus. the ninth bit could be used for control or parity for error checking at the option of the user. The HM63941 is fabricated using the Hitachi CMOS 1.3micron technology. The device is available in DIP.

### **FEATURES**

- · First-In, First-Out Dual Port Memory

- 4k × 9 Organization

- Low-Power CMOS 1.3micron Technology

- · Asynchronous and Simultaneous Read and Write

- Fully Expandable in Depth and/or Width

- Single 5V (± 10%) Power Supply

- . Empty and Full Warning Flags

- Almost-Full Flag

#### **ORDERING INFORMATION**

| Type Name   | Access Time | Package            |

|-------------|-------------|--------------------|

| HM63941P-25 | 25ns        |                    |

| HM63941P-35 | 35ns        | 28-pin Plastic DIP |

| HM63941P-45 | 45ns        | ,                  |

### PIN ARRANGEMENT

| l .              |        |                     |

|------------------|--------|---------------------|

| ₩ 🗆              | 1      | 28 🔲 Vcc            |

| D8 [             | 2      | 27 🔲 D4             |

| D3 [             | 3      | 26 🔲 D5             |

| D <sub>2</sub> [ | 4      | 25 🔲 D <sub>6</sub> |

| D1 [             | 5      | 24 🔲 D7             |

| Do [             | 6      | 23 🗍 FL/RT          |

| X1 🗀             | 7      | 22 🔲 RS             |

| FF [             | 8      | 21 🔲                |

| Q <sub>0</sub> [ | 9      | 20 XO/AF            |

| Q1 [             | 10     | 19 🔲 Q7             |

| Q2 [             | 11     | 18 🔲 Q <sub>6</sub> |

| Q3 [             | 12     | 17 🔲 Q5             |

| Q8 [             | 13     | 16 🔲 Q4             |

| Vss 🗀            | 14     | 15 🔲 🖪              |

| [ '              |        |                     |

|                  | (Top V | 'iew)               |

#### **■ PIN DESCRIPTION**

| Pin Name                       | Function         |

|--------------------------------|------------------|

| D <sub>0</sub> -D <sub>8</sub> | Data inputs      |

| RS                             | Reset            |

| $\overline{\mathbf{w}}$        | Write enable     |

| R                              | Read enable      |

| FL                             | First load       |

| RT                             | Retransmit       |

| XI                             | Expansion-in     |

| <del>X</del> O                 | Expansion-out    |

| ĀĒ                             | Almost-full flag |

| FF                             | Full flag        |

| ĒF                             | Empty flag       |

| Q <sub>0</sub> -Q <sub>8</sub> | Data outputs     |

#### **■ ABSOLUTE MAXIMUM RATINGS**

| Item                           | Symbol            | Rating                 | Unit |

|--------------------------------|-------------------|------------------------|------|

| Terminal Voltage(1)            | V <sub>T</sub>    | $-0.5^{(2)}$ to $+7.0$ | V    |

| Power Dissipation              | P <sub>T</sub>    | 1.0                    | W    |

| Operating Temperature          | T <sub>opr</sub>  | 0 to +70               | °C   |

| Storage Temperature            | T <sub>stg</sub>  | -55 to +125            | °C   |

| Storage Temperature Under Bias | T <sub>bias</sub> | -10 to +85             | °C   |

NOTES: 1. Relative to V<sub>SS</sub>.

2. -3.5V for pulse width  $\leq 10$ ns.

### **■ ELECTRICAL CHARACTERISTICS**

### • Recommended DC Operating Conditions ( $T_a = 0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter      | Symbol          | Min.    | Typ. | Max. | Unit |

|----------------|-----------------|---------|------|------|------|

| Supply Voltage | v <sub>cc</sub> | 4.5     | 5.0  | 5.5  | V    |

|                | V <sub>SS</sub> | 0       | 0    | 0    | V    |

| T . T . I.     | V <sub>IH</sub> | 2.0     |      | 6.0  | V    |

| Input Voltage  | V <sub>IL</sub> | -0.5(1) | _    | 0.8  | V    |

**NOTE:** 1. -3.0V for pulse width  $\leq 10$ ns.

## **DC CHARACTERISTICS** ( $T_a = 0$ °C to +70°C, $V_{CC} = 5V \pm 10\%$ )

| Parameter                      | Symbol           | Test Conditions                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------|------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| Input Leakage Current          | ILI              | $V_{CC} = 5.5V, V_{in} = 0V - V_{CC}$                                                | _    | _    | 2    | μΑ   |

| Output Leakage Current         | I <sub>LO</sub>  | $\overline{R} = V_{IH}, V_{out} = 0V - V_{CC}$                                       | _    |      | 2    | μΑ   |

| On antina Power Symply Cymont  | I <sub>CC1</sub> | Average Operating Current                                                            | _    | _    | 80   | mA   |

| Operating Power Supply Current | I <sub>CC2</sub> | $\overline{R} = \overline{W} = \overline{RS} = \overline{FL}/\overline{RT} = V_{IH}$ |      | _    | 10   | mA   |

| Standby Power Supply Current   | I <sub>SB</sub>  | All Inputs $\geq V_{CC} - 0.2V$ or $\leq V_{CC}$                                     | _    | _    | 1    | mA   |

| Output High Voltage            | V <sub>OH</sub>  | $I_{OH} = -4mA$                                                                      | 2.4  |      |      | V    |

| Output Low Voltage             | V <sub>OL</sub>  | $I_{OL} = 8mA$                                                                       | ]    |      | 0.4  | V    |

### **EXECUTANCE** $(T_a = 25^{\circ}C, f = 1MHz)$

| Parameter          | Symbol           | Test Conditions | Тур. | Max. | Unit |

|--------------------|------------------|-----------------|------|------|------|

| Input Capacitance  | C <sub>in</sub>  | $V_{in} = 0V$   | _    | TBD  | pF   |

| Output Capacitance | C <sub>out</sub> | $V_{out} = 0V$  |      | TBD  | pF   |

### **AC CHARACTERISTICS** ( $T_a = 0$ °C to 70°C, $V_{CC} = 5 \pm 10\%$ )

### Test Conditions

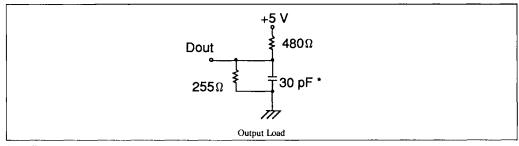

• Input Pulse Levels: V<sub>SS</sub> to 3.0V

• Input and Output Timing Reference Level: 1.5V

- Input Rise and Fall Times: 5ns

- Output Load: See Figure

<sup>\*</sup>Including scope and jig.

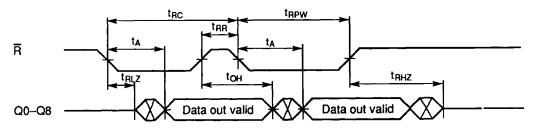

## • Read Cycle

| Parameter                 | Symbol           | Symbol HM63941-25 |      | HM63941-35 |      | HM63941-45 |      | Unit    |

|---------------------------|------------------|-------------------|------|------------|------|------------|------|---------|

| Farameter                 | Symbol           | Min.              | Max. | Min.       | Max. | Min.       | Max. | 1 01111 |

| Read Cycle Time           | t <sub>RC</sub>  | 35                |      | 45         | -    | 60         |      | ns      |

| Access Time               | t <sub>A</sub>   |                   | 25   | _          | 35   |            | 45   | ns      |

| Read Recovery Time        | t <sub>RR</sub>  | 10                |      | 10         | _    | 15         |      | ns      |

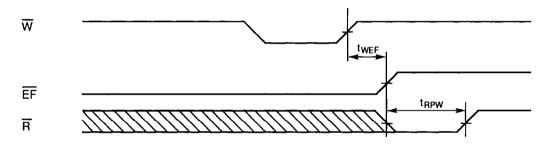

| Read Pulse Width          | t <sub>RPW</sub> | 25                |      | 35         | T    | 45         | _    | ns      |

| Read Low to DB Low Z      | t <sub>RLZ</sub> | 5                 |      | 5          | -    | 10         | _    | ns      |

| Read High to DB High Z    | t <sub>RHZ</sub> |                   | 15   |            | 20   | _          | 25   | ns      |

| Data Valid from Read High | toн              | 5                 | _    | 5          | _    | 5          |      | ns      |

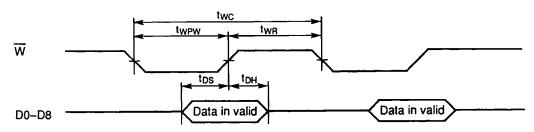

## • Write Cycle

| Parameter           | County of        | HM63941-25 |      | HM63941-35 |      | HM63941-45 |      | Unit |

|---------------------|------------------|------------|------|------------|------|------------|------|------|

| Parameter           | Symbol           | Min.       | Max. | Min.       | Max. | Min.       | Max. | Onit |

| Write Cycle Time    | t <sub>WC</sub>  | 35         | _    | 45         | _    | 60         | _    | ns   |

| Write Recovery Time | t <sub>WR</sub>  | 10         |      | 10         | -    | 15         |      | ns   |

| Write Pulse Width   | t <sub>WPW</sub> | 20         |      | 35         | _    | 45         | _    | ns   |

| Data Setup Time     | t <sub>DS</sub>  | 15         |      | 20         | _    | 25         |      | ns   |

| Data Hold Time      | t <sub>DH</sub>  | 0          |      | 0          |      | 5          |      | ns   |

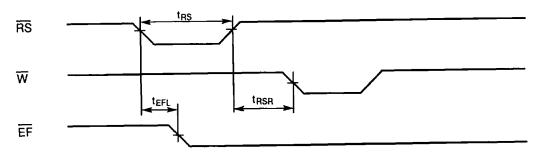

## • Reset Cycle

| Parameter           | Same bal         | HM63941-25 |      | HM63941-35 |      | HM63941-45 |      | Unit |

|---------------------|------------------|------------|------|------------|------|------------|------|------|

| Parameter           | Symbol           | Min.       | Max. | Min.       | Max. | Min.       | Max. | Unit |

| Reset Cycle Time    | tRSC             | 35         |      | 45         |      | 60         |      | ns   |

| Reset Pulse Width   | t <sub>RS</sub>  | 25         | _    | 35         | _    | 45         | _    | ns   |

| Reset Recovery Time | t <sub>RSR</sub> | 10         |      | 10         |      | 15         |      | ns   |

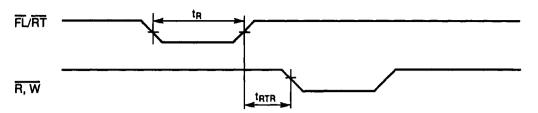

### • Retransmit Cycle

| Darameter                | Symbol           | HM63941-25 |      | HM63941-35 |      | HM63941-45 |      | Linit |

|--------------------------|------------------|------------|------|------------|------|------------|------|-------|

| Parameter                | Symbol           | Min.       | Max. | Min.       | Max. | Min.       | Max. | Unit  |

| Retransmit Cycle Time    | t <sub>RTC</sub> | 35         | _    | 45         | T -  | 60         | _    | ns    |

| Retransmit Pulse Width   | t <sub>RT</sub>  | 20         | _    | 35         | _    | 45         | -    | ns    |

| Retransmit Recovery Time | t <sub>RTR</sub> | 10         |      | 10         |      | 15         |      | ns    |

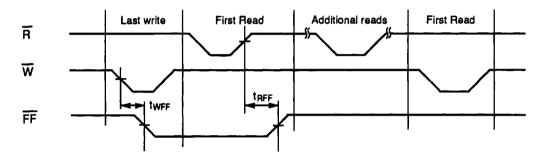

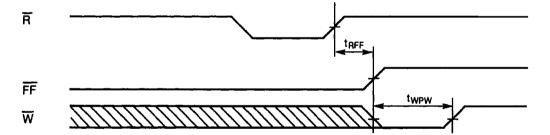

## • Flag Timing

| D                             | C                | HM63941-25 |      | HM63941-35 |      | HM63941-45 |      | Unit |

|-------------------------------|------------------|------------|------|------------|------|------------|------|------|

| Parameter                     | Symbol           | Min.       | Max. | Min.       | Max. | Min.       | Max. | Cin  |

| Reset to Empty Flag Low       | t <sub>EFL</sub> | _          | 30   |            | 45   |            | 60   | ns   |

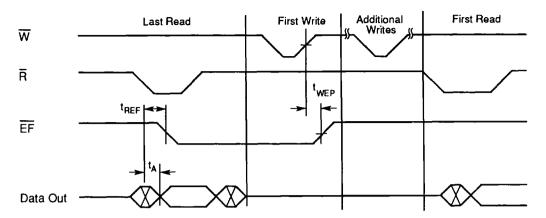

| Read Low to Empty Flag Low    | t <sub>REF</sub> |            | 25   |            | 35   | *****      | 45   | ns   |

| Read High to Full Flag High   | t <sub>RFF</sub> |            | 25   |            | 35   |            | 45   | ns   |

| Write High to Empty Flag High | tweF             |            | 25   | _ ·        | 35   | _          | 45   | ns   |

| Write Low to Full Flag Low    | t <sub>WFF</sub> |            | 25   |            | 35   |            | 45   | ns   |

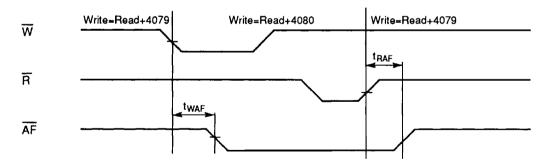

| Write Low to Almost-Full Low  | t <sub>WAF</sub> | _          | 30   |            | 40   |            | 55   | ns   |

| Read High to Almost-Full High | t <sub>RAF</sub> |            | 30   |            | 40   | -          | 55   | ns   |

#### SIGNAL DESCRIPTIONS

### Inputs

• Reset (RS)

The device is reset whenever  $\overline{RS}$  input is taken to low state, for minimum reset pulse width. When device is reset, both read and write pointers are set to the first location. A reset cycle is required after power on. Both read enable  $(\overline{R})$  and write enable  $(\overline{W})$  inputs must be in the high state during reset. Empty flag  $(\overline{EF})$  will go low and full flag  $(\overline{FF})$  and almost-full  $(\overline{AF})$  will go high during reset cycle.

• Write enable (W)

Write cycle is initiated at the falling edge of  $\overline{W}$ , if the full flag ( $\overline{FF}$ ) is not set, provided that data setup and hold time requirements relative to the rising edge of ( $\overline{W}$ ) are met. Data is stored in the device sequentially and independently of any simultaneous read operation. To inhibit further write operations and prevent internal data overflow full flag ( $\overline{FF}$ ) will go low.

Read enable (R)

Read cycle is initiated at the falling edge of  $\overline{R}$ , if the empty flag ( $\overline{EF}$ ) is not set. Data is accessed on a first-in, first-out basis independently of simultaneous write operation. As read enable ( $\overline{R}$ ) goes high, all outputs will return to high impedance state, till next read operation. After the last data has been read from the FIFO, the empty flag ( $\overline{EF}$ ) will go low, preventing further read operations with output kept in high impedance state. Empty flag ( $\overline{EF}$ ) will go high during a valid write cycle ( $t_{WEF}$ ), thereafter a valid read can start.

- First load/retransmit (FL/RT)

For depth expansion mode, this pin is grounded to indicate that it is the first device, while this pin of the rest of devices should connect to V<sub>CC</sub> for correct operation. In single device mode, this pin resets the read pointer to the beginning of the FIFO memory, therefore data can be reread from the beginning. Both R and W should be kept high while RT is taken low.

- Expansion-in (XI)

For single device mode expansion-in (XI) is grounded. For depth expansion mode, expansion-in (XI) should be connected to expansion-out (XO) of previous device.

- Data In (D<sub>0</sub> to D<sub>8</sub>)

Data inputs for 9-bit wide data.

#### Outputs

• Full Flag (FF)

The full flag (FF) will go low when FIFO is full, inhibiting further write operations until one or more read operations are completed or the FIFO is reset.

Empty flag (EF)

The empty flag (EF) will go low when the FIFO becomes empty, inhibiting further read opera

- tions, until one or more write operations are completed, or FIFO is set to retransmit.

- Expansion-out (XO)/Almost-full flag (ĀF)

This output has dual functionality depending how

it is used. In depth expansion configuration

expansion-out (XO) is connected to next

expansion-in (XI). The expansion-out (XO) of the

last FIFO is connected to the expansion-in (XI) of

the first FIFO. In this way the first FIFO indicates

the next FIFO that it will receive the next data. In

like manner, any FIFO which becomes full will indicate the next FIFO that it will receive the next data.

The second function of this output is in stand

alone and/or parallel expansion configurations to

indicate the system user that the FIFO is almost

full.

- Data outputs (Q<sub>0</sub> to Q<sub>8</sub>) Data outputs for 9-bit wide data. These outputs are in high impedance state when  $\overline{R}$  is in high state

#### **VARIOUS OPERATIONS MODE**

- Single device mode

If only one FIFO is used, the expansion-in (XI) pin should be grounded.

- Width expansion mode

Width expansion by 9-bit increments may be

achieved when separately paralleling the data inputs and the data outputs. In this configuration

any flags of any device may be used. To avoid

output contention of the flags for short periods of

time, the flag outputs should not be wired together.

- Depth expansion mode

Multiple of FIFOs could provide multiple of 4k x 9

as (N) x (4k) by 9-bits wide, where N is the number of FIFOs connected in depth expansion

mode

The following arrangement must be provided.

- First load (FL) of the first FIFO should be connected to ground.

- 2. All other (FL) should be connected to V<sub>CC</sub>.

- Connect the expansion-out (XO) of each FIFO to expansion-in (XI) of the next FIFO serially and XO of the last FIFO to XI of the first FIFO.

- Connect all the empty flag (EF) together to OR gate and connect all the full flag (FF) together to OR gate to obtain two separate valid empty flag (EF) and full flag (FF) outputs.

- (RT) and (AF) will not be available in this mode.

- Compound expansion mode

Combination of width and depth expansion modes will provide larger FIFO arrays.

### **■ TIMING WAVEFORM**

## • Read Cycle

### • Write Cycle

## • Reset Cycle

**NOTES:** 1.  $\overline{W} = \overline{R} = V_{IH}$  during reset.

2.  $t_{RSC} = t_{RST}$ ,  $t_{RSR}$ .

### Retransmit Cycle

## • Full-Flag Cycle (From Last Write to First Read)

## • Full-Flag Cycle (Effective Write Pulse Width After FF High)

### • Empty-Flag Cycle (From Last Write to First Read)

## • Empty-Flag Cycle (Effective Read Pulse Width After EF High)

### • Almost-Full Flag Cycle

# **NOTES**