# **NEC Microcomputers, Inc.**

# FLOPPY DISK CONTROLLER

### DESCRIPTION

The µPD372D is a single LSI floppy disk controller chip which contains the circuitry to read, write, track seek, load and unload the head, generate and detect CRC characters, and perform all other floppy disk operations. It is completely compatible with the IBM, Minifloppy \*TM, hard sector, and other formats and controls up to 4 floppy disk drives. The  $\mu PD372D$  may be interfaced directly to a host processor; or to a controller processor first, which in turn is interfaced to the host. These processors do not necessarily have to be of the 8080A type.

Data transfers to and from the  $\mu PD372D$  are done through addressable internal registers. These internal regsiters allow a large variety of system architectures to be configured; they provide status information on the drive, as well as perform data transfers between the drive and the processor.

The  $\mu PD372D$  issues interrupts to the processor upon detection of an address mark and then when each subsequent data byte is available during either reading or writing. An 8-bit bi-directional data bus and 5 register select lines provide access to the 9 internal registers' contents. An internal interval timer is provided which facilitates performing such drive timing functions as: stepping rate, head settling time, track settling time, etc.

\*TMShugart Associates.

- FEATURES Compatible with IBM 3740 format

- Also compatible with other formats including Minifloppy and hard sector

- Controls up to four floppy disk drives

- Can perform overlap seeks

- Input and output TTL compatible (except for  $\phi$ 1 and  $\phi$ 2)

- Interfaces to most microprocessors including 8080A

- Standard power supplies (+12V, +5V and -5V)

- Controls most floppy disk drives including:

CALCOMP 140, 142 ORBIS 74, 76/77 PERSCI 70, 75 CDC BR803

REMEX RFS 7400 INNOVEX 210, 410 SHUGART SA400 (Minifloppy) PERTEC FD400

WANGCO 82 (Minifloppy) POTTER DD4740 SHUGART SA900, SA800 GSI MDD50 (Minifloppy)

**GSI 110**

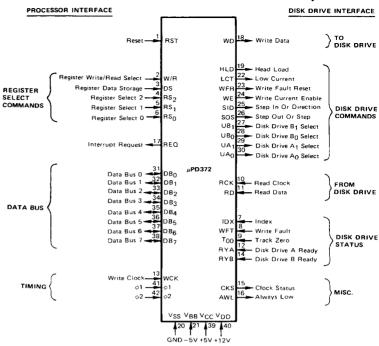

### PIN CONFIGURATION

| HST 🗖 1             | $\overline{}$ | 42 -2              |

|---------------------|---------------|--------------------|

| w B 🗖 🖰             |               | 41 🗖 1             |

| DS 🗖 3              |               | 40 🗖 ∨DD           |

| RS <sub>2</sub> 🗖 4 |               | 39 🗖 VCC           |

| RS₁ 🗖 :             |               | 38 🗖 DB7           |

| нs <sub>0</sub> 🗖 6 |               | 37 🗖 DB6           |

| IDX 🗖 7             |               | 36 🗖 DB5           |

| WET 🖂 8             |               | 35 🗖 DB4           |

| T00 □ °             |               | 34 🗖 DB3           |

| RCK 🔲 10            |               | 33 🏳 DB2           |

| RD 🔲 ''             | $\mu$ PD      | 32 🗖 OB i          |

| BYA 🗖 12            | 372           | 31 DB <sub>0</sub> |

# μPD372

| Temperature Under Bias                                    | ABSOLUTE MAXIMUM |

|-----------------------------------------------------------|------------------|

| Storage Temperature                                       | RATINGS*         |

| All Output Voltages                                       |                  |

| All Input Voltages1.0 to +8 Volts <sup>12</sup>           |                  |

| Clock Voltage                                             |                  |

| Supply Voltage VDD1.0 to +16 Volts (Control of the volts) |                  |

| Supply Voltage VCC                                        |                  |

| Supply Voltage V <sub>BB</sub>                            |                  |

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$$^*\Gamma_a = 25^{\circ}C$$

Note: ①  $V_{BB} = -5V \pm 5\%$

$$T_a$$

=  $-70^{\circ}$ C,  $V_{DD}$  = +12V ± 5%,  $V_{CC}$  = +5V ± 5%,  $V_{BB}$  =  $-5$ V ± 5%,  $V_{SS}$  = 0V

DC CHARACTERISTICS

|                                            |                         | LIMITS  |     |                 | TEST |                           |  |

|--------------------------------------------|-------------------------|---------|-----|-----------------|------|---------------------------|--|

| PARAMETER                                  | SYMBOL                  | MIN TYP |     | MAX             | UNIT | CONDITIONS                |  |

| High Level Input<br>Voltage                | V <sub>IH</sub>         | +3.0    |     | v <sub>cc</sub> | ٧    |                           |  |

| Low Level Input<br>Voltage                 | V <sub>IL</sub>         | 0       |     | +0.8            | \ \  |                           |  |

| High Level Output<br>Voltage               | V <sub>ОН</sub>         | +3.5    |     |                 | V    | I <sub>OH</sub> = -1.0 mA |  |

| Low Level Output                           | V <sub>OL1</sub> ①      |         |     | +0.5            | V    | I <sub>OL</sub> = +1.7 mA |  |

| Voltage                                    | V <sub>OL2</sub> ®      |         |     | +0.5            | ٧    | 1 <sub>OL</sub> = +3.3 mA |  |

| High Level Clock<br>Voltage                | $V_{\phi H}$            | +9      |     | V <sub>DD</sub> | ٧    |                           |  |

| Low Level Clock<br>Voltage                 | $V_{\phi L}$            | 0       |     | +0.8            | ٧    |                           |  |

| High Level Input<br>Leakage Current        | LIH                     |         |     | +10             | μА   | V <sub> </sub> = +3.0V    |  |

| Low Level Input<br>Leakage Current         | LIL                     |         |     | -10             | μΑ   | V <sub>1</sub> = +0.8V    |  |

| High Level Clock<br>Leakage Current        | I <sub>L</sub> $\phi$ H |         |     | +10             | μΑ   | $V_{\phi} = +9.0V$        |  |

| Low Level Clock<br>Leakage Current         | <sup>1</sup> LφL        |         |     | -10             | μА   | V <sub>φ</sub> = +0.8V    |  |

| High Level Output<br>Leakage Current       | ILOH                    |         |     | +10             | μА   | V <sub>O</sub> = +3.5V    |  |

| Low Level Output<br>Leakage Current        | LOL                     |         |     | -10             | μА   | V <sub>O</sub> = +0,5V    |  |

| Power Supply<br>Current (V <sub>DD</sub> ) | l <sub>DD</sub>         |         | +20 |                 | mA   |                           |  |

| Power Supply<br>Current (V <sub>CC</sub> ) | ¹cc                     |         | +23 |                 | mA   |                           |  |

| Power Supply<br>Current (V <sub>BB</sub> ) | ІВВ                     |         |     | 2               | mA   |                           |  |

Notes:  $\bigcirc$  CKS, REQ, UA<sub>0</sub>, UA<sub>1</sub>, UB<sub>0</sub>, UB<sub>1</sub>, DB<sub>0</sub>-DB<sub>7</sub>.

② WD, HLD, LCT, WE, WFR, SOS, SID.

256

|                                                   |                             |        | LIMIT           |      |      |                                 |

|---------------------------------------------------|-----------------------------|--------|-----------------|------|------|---------------------------------|

| PARAMETER                                         | SYMBOL                      | MIN    | ΤΥP             | MAX  | UNIT | TEST CONDITIONS                 |

| Clock Period                                      | tcy                         | 480    |                 | 2000 | ns   |                                 |

| Clock Rise and Fall Times                         | 1, 14                       | 0      |                 | 50   | ns   |                                 |

| 1 Pulse Winith                                    | 1, 1                        | 60     |                 |      | ns   |                                 |

| · 2 Pulse Width                                   | L,2                         | 90     |                 |      | ns   |                                 |

| - 1 to -2 Delay                                   | <sup>1</sup> D1             | 0      |                 |      | ns   |                                 |

| 2 to 1 Delay                                      | 'D <sub>2</sub>             | 70     |                 |      | ns   |                                 |

| Delay 1 to 2 Leading Edges                        | <sup>1</sup> D <sub>3</sub> | 100    |                 |      | ns   |                                 |

| Data Out Delay from 17                            | TOD1                        |        |                 | 90   | ns   | 1 TTL and C <sub>i</sub> : 30 p |

| Data Out Delay                                    | ¹OD2                        | 1      |                 | 200  | ns   | 1 TTL and C <sub>1</sub> = 30 p |

| from og ②                                         | _                           |        |                 | 200  | ns   | 2 TTL and C <sub>i</sub> = 50 p |

| WD Delay Time                                     | 10D3                        |        |                 | 120  | ns   | 2 TTL and C <sub>i</sub> = 50 p |

| Data Out Delay from<br>DS : W/R - RS <sub>2</sub> | 'OD4                        |        |                 | 200  | пs   |                                 |

| Data Setup Time to 01                             | 1151                        | 150    |                 |      | ns   |                                 |

| Data Setup Time to2                               | ¹IS <sub>2</sub>            | 120    | !               |      | ns   |                                 |

| Data Hold Time from on                            | THI                         | 10     |                 |      | ns   |                                 |

| Data Hold Time from 2                             | 1H2                         | 10     |                 |      | ns   |                                 |

| WD pulse width                                    | TWD                         | tp3:40 | <sup>†</sup> Da |      | ns   |                                 |

Notes: ① CKS, AWL, REO, UA<sub>0</sub>, UA<sub>1</sub>, UB<sub>0</sub>, UB<sub>1</sub>.

Input pulse width

- ② HLD, LCT, WFR, WE, SOS, SID.

- 3 IDX, RYA, RYB, RST, WFT, TOO, WCK, RCK.

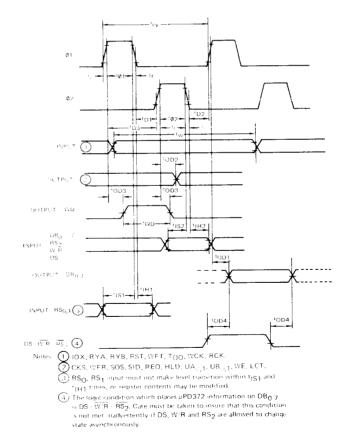

## TIMING WAVEFORMS

# $\mu$ PD372 -200 ns Raw Data from Floppy Drive (Pin 10) RCK (Pin 11) RD RD must be Stable Notes: ① $t_{CY} = \phi 1$ Clock Period

②  $T_1 \ge t_{CY} + 160 \text{ ns}$ ③  $T_2 \ge t_{CY} + 160 \text{ ns}$  READ CLOCK (RCK) AND READ DATA (RD) REQUIRED BY µPD372

PIN IDENTIFICATION

|       |                                                                        | PIN                            | INPUT/           |            |                                                                           |  |  |

|-------|------------------------------------------------------------------------|--------------------------------|------------------|------------|---------------------------------------------------------------------------|--|--|

| NO.   | SYMBOL                                                                 | NAME                           | ОИТРИТ           | CONNECTION | FUNCTION                                                                  |  |  |

| 1     | RST                                                                    | Reset                          |                  |            | Initializes internal registers, counters and F/F's                        |  |  |

| 2     | W/R                                                                    | Register Write/<br>Read Select |                  |            | W/R = 1 implies DB <sub>0-7</sub> data written into $\mu$ PD372 registers |  |  |

| 3     | DS                                                                     | Data Strobe                    |                  | Processor  | DB <sub>0-7</sub> Write and read strobe                                   |  |  |

| 4-6   | RS <sub>O</sub><br>RS <sub>1</sub><br>RS <sub>2</sub>                  | Register Select                |                  |            | Internal Register Select                                                  |  |  |

| 7     | IDX                                                                    | Index                          | Input            |            | Pulse Signal that indicates start of Disk track                           |  |  |

| 8     | WFT                                                                    | Write Fault                    |                  |            | Write Fault Signal                                                        |  |  |

| 9     | T <sub>00</sub>                                                        | Track 00                       |                  | FDD        | Indicates that Head is positioned on<br>Track 00                          |  |  |

| 10    | RCK                                                                    | Read Clock                     |                  |            |                                                                           |  |  |

| 11    | RD                                                                     | Read Data                      |                  |            |                                                                           |  |  |

| 12    | RYA                                                                    | Ready A                        |                  |            | Indicates that FDD A is Ready                                             |  |  |

| 13    | WCK                                                                    | Write Clock                    |                  | Processor  |                                                                           |  |  |

| 14    | RYB                                                                    | Ready B                        |                  | FDD        | Indicates that FDD B is Ready                                             |  |  |

| 15    | CKS                                                                    | Clock States                   |                  |            |                                                                           |  |  |

| 16    | AWL                                                                    | Always Low                     |                  |            | Always a logic zero                                                       |  |  |

| 17    | REQ                                                                    | Request                        |                  | Processor  | Interrupt Request                                                         |  |  |

| 18    | WD                                                                     | Write Data                     |                  |            | Serial Write Data (Clock & Data<br>Bits)                                  |  |  |

| 19    | HLD                                                                    | Head Load                      |                  |            | Command which causes R/W head to contact disk                             |  |  |

| 22    | LCT                                                                    | Law Current                    | Output           |            | Command to lower write current for inner tracks                           |  |  |

| 23    | WER                                                                    | Write Fault Reset              | -0.00            | FDD        | Signal to reset write fault latch                                         |  |  |

| 24    | WE                                                                     | Write Enable                   | İ                | t          |                                                                           |  |  |

| 25    | SID                                                                    | Step in or Direction           |                  |            | R/W head step contro!                                                     |  |  |

| 26    | sos                                                                    | Step Out or Step               |                  | Ţ          | R/W head step control                                                     |  |  |

| 27-30 | UA <sub>0</sub> , UA <sub>1</sub><br>UB <sub>0</sub> , UB <sub>1</sub> | FDD Select                     |                  |            | FDD Unit Select                                                           |  |  |

| 31-38 | DB <sub>0-7</sub>                                                      | Data Bus                       | Input/<br>Output | Processor  | Bi-directional data bus                                                   |  |  |

258

# PIN IDENTIFICATION (CONT.)

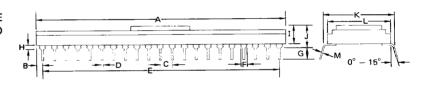

# PACKAGE OUTLINE µPD372D

| ITEM | MILLIMETERS | INCHES   |

|------|-------------|----------|

| Α    | 53.5 MAX    | 2.1 MAX  |

| В    | 1.35        | 0.05     |

| С    | 2.54        | 0.10     |

| D    | 50.80       | 2.0      |

| F    | 1.27        | 0.05     |

| G    | 2.54 MAX    | 0.10 MIN |

| н    | 1.0 MIN     | 0.04 MIN |

| 1    | 4.2 MAX     | 0.17 MAX |

| J    | 5.2 MAX     | 0.21 MAX |

| К    | 15.24       | 0.60     |

| L    | 13.50       | 0.53     |

| M    | 0.3         | 0.012    |

| ВІТ | SYMBOL          | NAME                         | FUNCTION                                                             |

|-----|-----------------|------------------------------|----------------------------------------------------------------------|

|     |                 | WRITE REGIS                  | STER 0                                                               |

| 0   |                 | Not Used                     |                                                                      |

| 1   | WFR             | Write Fault Reset            | Resets Pin 23 to Zero                                                |

| 2   | LCT             | Low Current                  | Sets Pin 22, Should be Zero for TRKS > 43                            |

| 3   | HLD             | Head Load                    | Sets Pin 19, Loading FDD Head                                        |

| 4   |                 | Not Used                     |                                                                      |

| 5   |                 | Not Used                     |                                                                      |

| 6   | MBL             | Must Be Low                  |                                                                      |

| 7   | RST             | Reset                        | Software Reset, Same Effect as Pin 1                                 |

|     |                 | WRITE REGIS                  | STER 1                                                               |

| 0   | UAO             | Unit An Select               | Device Select Pin 30                                                 |

| 1   | UA <sub>1</sub> | Unit A <sub>1</sub> Select   | Device Select Pin 29                                                 |

| 2   | UAS             | Unit A Strobe                | Strobe for Enabling UA <sub>0</sub> and OA <sub>1</sub> to be Loaded |

| 3   | CB3             | Clock Bit 3                  | Enables Clock Pulse #3 to be Written                                 |

| 4   | CB <sub>4</sub> | Clock Bit 4                  | Enables Clock Pulse =4 to be Written                                 |

| _ 5 | CB <sub>5</sub> | Clock Bit 5                  | Enables Clock Pulse #5 to be Written                                 |

| 6   |                 | Not Used                     |                                                                      |

| 7   | CBS             | Clock Bit Strobe             | Enables Clock Bits to be Loaded                                      |

|     |                 | WRITE REGIS                  | TER 2                                                                |

| 0   | WD <sub>0</sub> | Write Data Bit 0             |                                                                      |

| 1   | WD <sub>1</sub> | Write Data Bit 1             |                                                                      |

| 2   | WD2             | Write Data Bit 2             |                                                                      |

| 3   | WD3             | Write Data Bit 3             |                                                                      |

| 4   | WD4             | Write Data Bit 4             |                                                                      |

| 5   | WD <sub>5</sub> | Write Data Bit 5             |                                                                      |

| 6   | WD <sub>6</sub> | Write Data Bit 6             |                                                                      |

| 7   | WD7             | Write Data Bit 7             |                                                                      |

|     |                 | WRITE REGIS                  | TER 3                                                                |

| 0   | CCW             | Cyclic Check Words           | One During R/W, Zero for CRC Reset                                   |

| 1   | CCG             | Cyclic Check Generator Start | Starts CRC Generator in Write Mode                                   |

| 2   | WER             | Write Enable Reset           | Resets Pin 24 to Zero                                                |

| 3   | IXS             | Index Start                  | Enable Index Hole Detection                                          |

| 4   | WES             | Write Enable Set             | Sets Pin 24 to One                                                   |

| 5   | STT             | Start                        | Enables Read and Write Operations to Occur                           |

| 6   | WCS             | Write Clock Set              | Write Clock Selected                                                 |

| 7   | RCS             | Read Clock Set               | Read Clock Selected                                                  |

|     |                 | WRITE REGIS                  | TER 4                                                                |

| 0   | UB <sub>0</sub> | Unit Bo Select               | Device Select Pin 28                                                 |

| 1   | UB <sub>1</sub> | Unit B <sub>1</sub> Select   | Device Select Pin 27                                                 |

| 2   | UBS             | Unit B Strobe                | Strobe for Enabling UBg, UB <sub>1</sub> to be Loaded                |

| 3   |                 | Not Used                     |                                                                      |

| 4   |                 | Not Used                     |                                                                      |

| 5   | SOS             | Step Out or Step             | Sets Pin 26 to One                                                   |

| 6   | SID             | Step In or Direction         | Sets Pin 25 to One                                                   |

| 7   | STS             | Step Strobe                  | Enables SOS and SID to be Loaded                                     |

|     |                 | WRITE REGIS                  | TER 5                                                                |

| 07  |                 | This Register Not Used       |                                                                      |

|     |                 | WRITE REGIS                  | TER 6                                                                |

| 0   | DRR             | Data Register Reset          | Resets DRQ (RR <sub>0</sub> Bit 0)                                   |

| 1   | IRR             | Index Request Reset          | Resets IRQ (RR <sub>0</sub> Bit 1)                                   |

| 2   | TRR             | Timer Request Reset          | Resets TRQ (RR <sub>0</sub> Bit 2)                                   |

| 3   |                 | Not Used                     | ,                                                                    |

| 4   |                 | Not Used                     |                                                                      |

| 5   |                 | Not Used                     |                                                                      |

| 6   |                 | Not Used                     |                                                                      |

| 7   |                 | Not Used                     |                                                                      |

|     |                 |                              |                                                                      |

# INTERNAL REGISTER IDENTIFICATION (CONT.)

| ВІТ | SYMBOL          | NAME                          | FUNCTION                                              |

|-----|-----------------|-------------------------------|-------------------------------------------------------|

|     |                 | READ REGI                     | STER 0                                                |

| 0   | DRQ             | Data Request                  | Read Data Byte from RR2 or Write Data Byte into WR2   |

| 1   | IRQ             | Index Request                 | Set by Physical Index Pulse                           |

| 2   | TRQ             | Timer Request                 | Set by Every 512th Write CLK Pulse                    |

| 3   | ERR             | Error                         | Logical OR of WFT + RYA + COR                         |

| 4   | UBn             | Drive Bo Selected             |                                                       |

| 5   | UB <sub>1</sub> | Drive B <sub>1</sub> Selected |                                                       |

| 6   | RYB             | Drive B Ready                 | Ready Signal from Pin 14                              |

| 7   | ALH             | Always High                   | Always Contains a Logical One                         |

|     |                 | READ REG                      | ISTER 1                                               |

| 0   | UA <sub>0</sub> | Drive An Selected             |                                                       |

| 1   | UA <sub>1</sub> | Drive A1 Selected             |                                                       |

| 2   | WFT             | Write Fault                   | Indicates Status of Pin 8                             |

| 3   | RYA             | Drive A Ready                 | Indicates Status of Pin 12                            |

| 4   | COR             | Command Overrun               | Processor Did Not Respond in Time to a DRQ            |

| 5   | DER             | Data Error                    | CRC Error During Read                                 |

| 6   | т <sub>00</sub> | Track Zero                    | Indicates Status of Pin 9                             |

| 7   | WRT             | Write Mode                    | Indicates which Clock WCK or RCK has been<br>Selected |

|     |                 | READ REG                      | ISTER 2                                               |

| 0   | RD <sub>0</sub> | Read Data Bit 0               |                                                       |

| 1   | RD1             | Read Data Bit 1               |                                                       |

| 2   | RD <sub>2</sub> | Read Data Bit 2               |                                                       |

| 3   | RD3             | Read Data Bit 3               |                                                       |

| 4   | RD4             | Read Data Bit 4               |                                                       |

| 5   | RD <sub>5</sub> | Read Data Bit 5               |                                                       |

| 6   | RD <sub>6</sub> | Read Data Bit 6               |                                                       |

| 7   | RD7             | Read Data Bit 7               |                                                       |

ADDRESSABLE Data is transferred to the  $\mu PD372's$  internal addressable registers by signals W/R INTERNAL REGISTERS (Write=1, Read=0), DS (Data Strobe) and RS<sub>0</sub>-RS<sub>2</sub> (Register Select 0, 1 and 2). Timing constraints for these signals are shown in the Timing Diagram. Diagram below shows register allocations and functional content.

| REGI            | STER | ADD             | RESS            | REGISTER        |     | BIT NUMBERS     |                 |                 |     |                 |                 |                 |

|-----------------|------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|

| W/R             | R\$2 | RS <sub>1</sub> | RS <sub>0</sub> | NAME            | 7   | 6               | 5               | 4               | 3   | 2               | 1               | 0               |

| WRITE REGISTERS |      |                 |                 |                 |     |                 |                 |                 |     |                 |                 |                 |

| 1               | 0    | 0               | 0               | wR <sub>0</sub> | RST | MBL             | ×               | Х               | HLD | LCT             | WFR             | X               |

| 1               | 0    | 0               | 1               | WR <sub>1</sub> | CBS | ×               | CB <sub>5</sub> | CB4             | CB3 | UAS             | UA <sub>1</sub> | UA <sub>0</sub> |

| 1               | 0    | 1               | 0               | WR <sub>2</sub> | WD7 | WD6             | WD <sub>5</sub> | WD4             | WD3 | WD <sub>2</sub> | WD <sub>1</sub> | WD0             |

| 1               | 0    | 1               | 1               | WR3             | RCS | wcs             | STT             | WES             | TXS | WER             | CCG             | ccw             |

| 1               | 1    | 0               | 0               | WR4             | STS | SID             | SOS             | ×               | ×   | UBS             | UB <sub>1</sub> | UB <sub>0</sub> |

| 1               | 1    | 1               | 0               | WR <sub>6</sub> | ×   | , x             | . ×             | ×               | ×   | TRR             | IRR             | DRR             |

|                 |      | READ REGISTERS  |                 |                 |     |                 |                 |                 |     |                 |                 |                 |

| 0               | 0    | 0               | 0               | RR <sub>0</sub> | ALH | RYB             | UB <sub>1</sub> | UB <sub>0</sub> | ERR | TRQ             | IRQ             | DRQ             |

| 0               | 0    | 0               | 1               | RR1             | WRT | T <sub>00</sub> | DER             | COR             | RYA | WFT             | UA <sub>1</sub> | UA <sub>0</sub> |