# **Signetics**

## SG3526 Switched-Mode Power Supply Control Circuit

**Product Specification**

#### **Linear Products**

#### DESCRIPTION

Specifically designed for use in fixedfrequency switching regulators and other power control applications, this Switched-Mode Power Supply Control Circuit can be used to implement singleended or push-pull switching regulators of either polarity, both transformerless and transformer-coupled.

Included in this monolithic integrated circuit is a temperature-compensated voltage reference, sawtooth oscillator, error amplifier, pulse width modulator, pulse metering and steering logic, and two 200mA source/sink power drivers. Also included are housekeeping functions such as soft-start and low supply voltage lockout, digital current limiting, double-pulse inhibit, a data latch for single-pulse metering, adjustable dead time, and provision for symmetry correction inputs.

The output cirtcuit has been redesigned to eliminate the current spiking problem associated with source/sink drivers. The output stage has been designed so that in the transition from source-to-sink, or sink-to-source, the conducting device is shut off one transistor delay before the other device is turned on. This output correction allows the designer to utilize the speed of the other features of this controller at system frequencies up to 400kHz.

For ease of interface, all digital inputs are TTL and CMOS compatible. Active LOW logic allows wired-OR connections for maximum flexibility.

The low-cost SG3526 is rated for continuous operation over the junction temperature range of 0°C to +125°C. It is furnished in either the Cerdip package or a dual in-line plastic package with copper alloy lead frame for improved heat dissipation.

#### **FEATURES**

- 7.4 to 35V operation

- Dual 200mA source/sink outputs

- Cycle-by-cycle operation of all features up to 400kHz

- No current spikes on V<sub>C</sub> line at source-to-sink or sink-to-source transitions

- Stabilized power supply

- Current limiting

- Temperature-compensated reference source

- Sawtooth generator

- · Low supply voltage protection

- External synchronization

- Double-pulse suppression

- Programmable dead time

- Programmable soft start

- 18-pin dual in-line plastic package, 18-pin Cerdip hermetic package, or 20-pin plastic SO

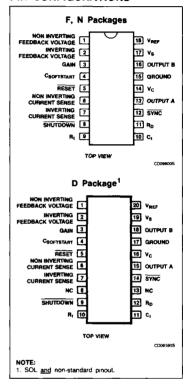

#### PIN CONFIGURATIONS

#### **ORDERING CODE**

| DESCRIPTION            | AMBIENT TEMPERATURE | ORDER CODE |

|------------------------|---------------------|------------|

| 20-pin Plastic SOL DIP | 0 to +70°C          | SG3526D    |

| 18-pin Cerdip          | 0 to +70°C          | SG3526F    |

| 18-pin Plastic DIP     | 0 to +70°C          | SG3526N    |

SG3526

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL          | PARAMETER                                                                        | RATING                  | UNIT                             |

|-----------------|----------------------------------------------------------------------------------|-------------------------|----------------------------------|

| Vs              | Supply voltage                                                                   | 40                      | ٧                                |

| V <sub>C</sub>  | Collector supply voltage                                                         | 40                      | V                                |

| V <sub>IN</sub> | Logic input voltage range, Pins 5, 8, 12                                         | -0.3 to +5.5            | V                                |

| V <sub>IN</sub> | Analog input voltage range, Pins 1, 2, 6, 7                                      | -0.3V to V <sub>S</sub> | V                                |

| lo              | Output current                                                                   | ± 250                   | mA                               |

| IREF            | Reference load current                                                           | 50                      | mA                               |

| I <sub>IN</sub> | Logic sink current                                                               | 15                      | mA                               |

| PD              | Package power dissipation (Plastic DIP) <sup>2</sup> (SO), (Cerdip) <sup>2</sup> | 1.9<br>1.4              | W <sup>1</sup><br>W <sup>1</sup> |

| Ts              | Storage temperature range                                                        | -65 to +150             | °C                               |

#### NOTES:

- 1. Maximum junction temperature,  $T_{JMAX} = 150^{\circ}C$ . Rating is for  $T_A = 25^{\circ}C$ . 2. Plastic  $\theta_{JA} = 66^{\circ}C/W$ ; Cerdip  $\theta_{JA} = 88^{\circ}C/W$ ; SO  $\theta_{JA} = 85^{\circ}C/W$ .

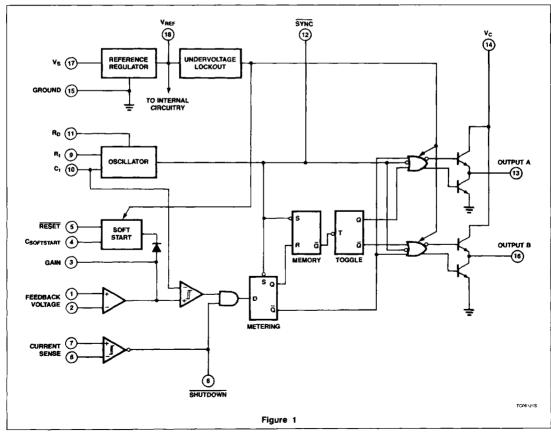

#### **BLOCK DIAGRAM**

SG3526

## **DC ELECTRICAL CHARACTERISTICS** All specs over operating junction temperature range, $V_S = 15V$ , unless otherwise noted.

| SYMBOL            | CHARACTERISTICS                     | TEST              |                                                                            | LIMITS |      |          |                   |

|-------------------|-------------------------------------|-------------------|----------------------------------------------------------------------------|--------|------|----------|-------------------|

| SYMBOL            | CHARACTERISTICS                     | PINS              | TEST CONDITIONS                                                            | Min    |      | Max      | UNIT              |

| Reference         | , Pin 18                            |                   |                                                                            |        |      |          |                   |

| V <sub>REF</sub>  | Reference voltage                   | 18                | T <sub>J</sub> = +25°C                                                     |        | 5.00 |          |                   |

|                   | Temperature stability               | 18                |                                                                            |        | 0.2  | 0.4      | mV/°C             |

|                   | Total output variation              | 18                | 7.4V < V <sub>S</sub> < 35V, 0 < I <sub>L</sub> < 10mA                     | 4.85   | 5.00 | 5.15     | V                 |

|                   | Line regulation                     | 18                | 7.4V < V <sub>S</sub> < 35V, I <sub>L</sub> = 0mA                          |        | 0.6  | 2        | mV/V              |

|                   | Load regulation                     | 18                | 0mA < I <sub>L</sub> < 10mA                                                |        | 0.4  | 2.5      | mV/m/             |

|                   | Short circuit current               | 18                | V <sub>REF</sub> = 0V                                                      | -25    | -75  | -125     | mA                |

|                   | Output noise voltage                | 18                | 10Hz ≤ f ≤ 80kHz                                                           |        | 100  |          | μV <sub>RMS</sub> |

| Low supp          | ly shutdown, Internal and Pin 5     |                   |                                                                            |        |      |          |                   |

|                   | Comparator threshold voltage        |                   |                                                                            | 3.8    | 4.2  | 4.8      | ٧                 |

|                   | Hysteresis                          |                   |                                                                            |        | 0.2  |          | ٧                 |

|                   | Reset voltage out                   | 5                 | When shutdown for LOW V <sub>S</sub>                                       |        | 0.2  | 0.4      | ٧                 |

|                   | Reset voltage out                   | 5                 | When not shutdown                                                          | 2.4    | 4.8  |          | ٧                 |

|                   | Reset sink current                  | 5                 | When shutdown, V <sub>IL</sub> = 0.4V                                      |        | -190 | -360     | μА                |

|                   | Reset source current                | 5                 | When not shutdown, VIH = 2.4V                                              |        | -110 | -200     | μΑ                |

| Oscillator,       | Pins 9, 10, 11 and SYNC, Pin 1:     | 21                |                                                                            | ·      |      | <u> </u> |                   |

| -                 | Minimum frequency range             | 9, 10, 11 &<br>12 | $R_T = 150k, C_T = 20\mu F, R_D = 0\Omega$                                 |        |      | 1.0      | Hz                |

|                   | Maximum frequency range             |                   | $R_T = 2k$ , $C_T = 300pF$ , $R_D = 0\Omega$ ,<br>$T_J = 125$ °C           | 400    |      |          | kHz               |

|                   | Initial accuracy                    | 9, 10             | $R_T = 4.12k$ , $C_T = 0.01 \mu F$ , $R_D = 0\Omega$ , $T_J = 25^{\circ}C$ | 36.8   | 40   | 43.2     | kHz               |

| V <sub>COSC</sub> | Voltage stability <sup>2</sup>      | 9, 10             | 7.4V < V <sub>S</sub> < 35V                                                |        | 0.02 | 0.04     | %/V               |

| Tcosc             | Temperature stability <sup>2</sup>  | 9, 10             |                                                                            |        | 0.04 | 0.06     | %/°C              |

|                   | Sawtooth peak voltage               | 10                | V <sub>S</sub> = 35V                                                       | 2.0    | 3.0  | 3.5      | ٧                 |

|                   | Sawtooth valley voltage             | 10                | V <sub>S</sub> = 7.4V                                                      | 0.5    | 1.0  | 1.5      | ٧                 |

|                   | Sync. in HIGH level                 | 12                | ISOURCE = 40µA                                                             | 2.4    | 4.0  |          | V                 |

|                   | Sync. in LOW level                  | 12                | I <sub>SINK</sub> = 3.6mA                                                  |        | 0.2  | 0.4      | V                 |

|                   | Sync. in bias current, HIGH         | 12                | V <sub>IH</sub> = 2.4V                                                     |        | -105 | -200     | μА                |

|                   | Sync. in bias current, LOW          | 12                | V <sub>IL</sub> = 0.4V                                                     |        | -180 | -360     | μА                |

|                   | Min sync. in pulse width to trigger | 12                |                                                                            | 200    | 150  |          | ns                |

### Я

## Switched-Mode Power Supply Control Circuit

SG3526

## DC ELECTRICAL CHARACTERISTICS (Continued) All specs over operating junction temperature range, V<sub>S</sub> = 15V, unless otherwise noted.

| SYMBOL            | CHARACTERISTICS                  | TEST    | TEST CONDITIONS                                      | LIMITS |      |      | UNIT |

|-------------------|----------------------------------|---------|------------------------------------------------------|--------|------|------|------|

| SIMBOL            | CHARACTERISTICS                  | PINS    | resi conditions                                      | Min    | Тур  | Max  | UNIT |

| Error amp         | o, Pins 1, 2 and 3 <sup>3</sup>  |         |                                                      |        |      |      |      |

| Vos               | Input offset voltage             | 1, 2    |                                                      | _      | 2.0  | 10   | mV   |

| 1 <sub>B</sub>    | Input bias current               | 1, 2    |                                                      | ì      | 210  | 1000 | nA   |

| los               | Input offset current             | 1, 2    |                                                      |        | 5    | 200  | nA   |

| Avol              | DC open-loop gain                | 1, 2, 3 |                                                      | 60     | 68   |      | dB   |

| V <sub>OH</sub>   | High output voltage              | 3       | I <sub>SOURCE</sub> = 100µA                          | 3.6    | 4.2  |      | v    |

| V <sub>OL</sub>   | Low output voltage               | 3       | I <sub>SINK</sub> = 100μA                            |        | 0.11 | 0.4  | ٧    |

| CMRR              | Common-mode rejection ratio      | 1, 2, 3 | H <sub>S</sub> = 2k                                  | 70     | 110  |      | dB   |

| PSRR              | Power supply rejection ratio     | 1, 2, 3 | V <sub>S</sub> = 10V to 20 V                         | 90     | 110  |      | ₫B   |

|                   | Small-signal bandwidth           | 1, 2, 3 |                                                      |        | 1.0  |      | MHz  |

|                   | Feedback resistor range          | 2, 3    |                                                      | 50     |      | 1000 | kΩ   |

|                   | Output sink current              | 3       |                                                      | 70     | 100  |      | μΑ   |

|                   | Output source current            | 3       |                                                      | 70     | 100  |      | μA   |

| PWM com           | parator, Internal and Pin 3 1    |         |                                                      |        |      |      |      |

|                   | Minimum duty cycle               |         | V <sub>COMP</sub> = 0.4V                             |        |      | 0    | %    |

|                   | Maximum duty cycle               |         | V <sub>COMP</sub> = 3.6V                             | 45     | 49   |      | %    |

|                   | Dead time accuracy               |         | $R_T = 4.12k$ , $C_T = 0.01 \mu F$ , $R_D = 0\Omega$ |        | 1.5  |      | μs   |

|                   | Prop. delay, PWM comp to output  |         |                                                      |        | 250  |      | ns   |

|                   | Bias current, duty cycle control | 3       |                                                      |        | 1    |      | μΑ   |

| Soft-start,       | Pins 4 and 5                     |         |                                                      |        |      |      |      |

|                   | Soft-start trip voltage          | 4       | V <sub>RESET</sub> = 0.4V                            |        | 22   | 50   | mV   |

|                   | Soft-start charge current        | 4       | V <sub>RESET</sub> = 2.4V                            | -180   | -120 | -85  | μΑ   |

| V <sub>LOW</sub>  | Reset voltage, OFF               | 5       | I <sub>SINK</sub> = 3.6mA                            |        | 0.2  | 0.4  | V    |

| V <sub>HIGH</sub> | Reset voltage, ON                | 5       | I <sub>SOURCE</sub> = 40 µA                          | 2.4    | 4.0  |      | ٧    |

|                   | Reset bias current, HIGH         | 5       | V <sub>IN</sub> ≠ 2.4V                               |        | -110 | -200 | μА   |

|                   | Reset bias current, LOW          | 5       | V <sub>IN</sub> = 0.4V                               |        | -200 | -360 | μΑ   |

| Remote O          | N/OFF (shutdown), Pin 8          |         |                                                      |        |      |      |      |

|                   | Off (LOW)                        | 8       | I <sub>SINK</sub> = 3.6mA                            |        | 0.2  | 0.4  | ٧    |

|                   | On (HIGH)                        | 8       | I <sub>SOURCE</sub> ≠ 40µA                           | 2.4    | 4.0  |      | ٧    |

|                   | Input current, shutdown HIGH     | 8       | V <sub>IN</sub> = 2.4V                               |        | -100 | -200 | μΑ   |

|                   | Input current, shutdown LOW      | 8       | V <sub>IN</sub> = 0.4V                               |        | -190 | -360 | μΑ   |

|                   | Delay to output(s)               | 8       |                                                      |        | 400  |      | ns   |

| Current lin       | mit comparator, Pins 6 and 7     |         | •                                                    | •      | •    |      |      |

|                   | Common-mode range                | 6, 7    | V <sub>S</sub> = 18V                                 | 0      |      | 15   | V    |

|                   | Sense voltage for Min duty cycle | 6, 7    |                                                      | 70     | 100  | 140  | mV   |

|                   | Input bias current               | 6, 7    | V <sub>CM</sub> = 0V to 15V                          | _      | -3   | -20  | μΑ   |

|                   | Voltage gain                     | 6, 7    |                                                      | -      | 68   |      | ₫B   |

|                   | Delay to outputs                 | 6, 7    | 100mV overdrive                                      |        | 700  |      | ns   |

SG3526

#### DC ELECTRICAL CHARACTERISTICS (Continued) All specs over operating junction temperature range, $V_S = 15V$ , unless otherwise noted.

| CVIADOL         |                                       | TEST                                          |                                                   | LIMITS  |      |      |     |  |

|-----------------|---------------------------------------|-----------------------------------------------|---------------------------------------------------|---------|------|------|-----|--|

| SYMBOL          | CHARACTERISTICS                       | PINS                                          | TEST CONDITIONS                                   | Min Typ |      | Max  | Max |  |

| Output st       | age, Pins 13, 14 and 16               |                                               |                                                   |         |      |      |     |  |

| V <sub>OH</sub> | High output voltage                   |                                               | I <sub>SOURCE</sub> = 20mA, V <sub>C</sub> = 15V  | 12.8    | 13.5 |      | V   |  |

|                 |                                       | 13, 14, 16                                    | I <sub>SOURCE</sub> = 100mA, V <sub>C</sub> = 15V | 12.5    | 13.3 |      | ٧   |  |

|                 |                                       |                                               | I <sub>SOURCE</sub> = 200mA, V <sub>C</sub> = 15V | 12.0    | 13.2 |      | V   |  |

|                 |                                       |                                               | I <sub>SINK</sub> = 20mA, V <sub>C</sub> = 15V    |         | 0.15 | 0.3  | ٧   |  |

| $V_{OL}$        | Low output voltage                    | 13, 14, 16                                    | I <sub>SINK</sub> = 100mA, V <sub>C</sub> = 15V   |         | 1.25 | 1.8  | V   |  |

| 0.              |                                       |                                               | I <sub>SINK</sub> = 200mA, V <sub>C</sub> = 15V   |         | 2.20 | 3.00 | V   |  |

|                 | Output leakage                        | 13, 14, 16                                    | V <sub>C</sub> = 40V                              | 1       | 45   | 100  | μΑ  |  |

|                 | I <sub>SINK</sub> Max                 | 13, 14, 16                                    | V <sub>C</sub> = 15V                              | 200     | 250  |      | mA  |  |

|                 | ISOURCE Max                           | 13, 14, 16                                    | V <sub>C</sub> = 15V                              | 200     | 250  |      | mA  |  |

| t <sub>R</sub>  | Rise time 13, 14, 16 C <sub>L</sub> = | C <sub>L</sub> = 1000pF, V <sub>C</sub> = 15V |                                                   | 300     |      | ns   |     |  |

| יחי             | THE WITTE                             | 10, 14, 10                                    | $C_L = 0pF, V_C = 15V$                            |         | 50   |      | ns  |  |

| t <sub>E</sub>  | Fall time                             | 13, 14, 16                                    | C <sub>L</sub> = 1000pF, V <sub>C</sub> = 15V     |         | 200  |      | ns  |  |

| 4               |                                       | 10, 13, 10                                    | C <sub>L</sub> = 0pF, V <sub>C</sub> = 15V        |         | 50   |      | ns  |  |

| Supply cu       | rrent <sup>4</sup>                    | <u> </u>                                      |                                                   | •       |      | •    | •   |  |

| lcc             | Shutdown LOW                          | 17                                            | 7.4V < V <sub>S</sub> < 35V                       |         | 24   | 30   | mA  |  |

| Operating       | frequency for cycle-by-cycle          | peration of all p                             | rotect features                                   |         |      |      |     |  |

|                 | Maximum frequency                     | 1                                             |                                                   | 400     | 500  | i    | kHz |  |

#### RECOMMENDED OPERATING CONDITIONS

| 0/4001         |                               | LIM   | LIMITS |      |  |

|----------------|-------------------------------|-------|--------|------|--|

| SYMBOL         | PARAMETER                     | Min   | Max    | UNIT |  |

| Vs             | Logic supply voltage          | 7.4   | 35     | V    |  |

| V <sub>C</sub> | Collector voltage             | 4.5   | 35     | V    |  |

| l <sub>o</sub> | Output load current           | 0     | ± 200  | mA   |  |

| 1 <sub>L</sub> | Reference load current        | 0     | 10     | mA   |  |

| fosc           | Oscillator frequency          | 1Hz   | 400    | kHz  |  |

| Ŕţ             | Oscillator timing resistance  | 2     | 150    | kΩ   |  |

| Ct             | Oscillator timing capacitance | 150pF | 20     | μF   |  |

| DT             | Programmed dead time          | 3     | 50     | %    |  |

| T <sub>A</sub> | Ambient temperature range     | 0     | + 70   | °C   |  |

| TJ             | Junction temperature range    | 0     | + 125  | °C   |  |

<sup>1.</sup>  $f_{OSC}$  = 40kHz (R<sub>T</sub> = 4.12k, C<sub>T</sub> = 0.01 $\mu$ F, R<sub>D</sub> = 0 $\Omega$ ) unless otherwise noted.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup>  $V_{CM} = 0V$  to 5.2V. 4.  $R_T = 4.12k\Omega$ .

### THEORY OF OPERATION

#### Internal Reference

The internal reference is capable of maintaining 1% accuracy over the specified operating temperature range. The reference voltage is 5.00V at Pin 18. Short-circuit current is typically 50mA. The reference output remains stable within 30mV over an input range of 8 to 35V. Complete regulation characteristics versus line and load (see Figure 1) are listed in the Electrical Characteristics section of the data sheet. The maximum recommended load on the reference supply is 20mA.

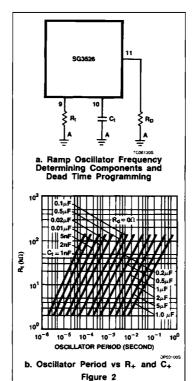

#### THE RAMP OSCILLATOR

The ramp oscillitor is a self-sustained, fixed-frequency circuit with programmability provided by selecting the value of an external resistor and capacitor as shown in Figure 2. An internal current source is set by the resistor R<sub>1</sub> to a certain value of charging current sufficient to generate a stable ramp over a range of 1Hz to 400kHz.

#### THE ERROR AMPLIFIER

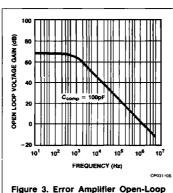

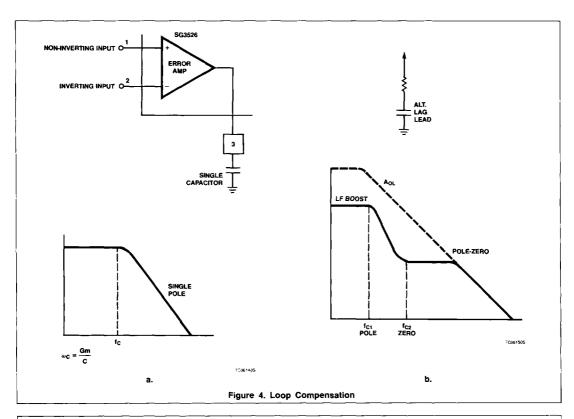

The error amplifier is a transconductance-type with open-loop unity gain bandwidth of 1MHz. Typical source/sink current is  $100\mu$ A. Open-loop DC gain is 68dB with a single dominant pole at 500Hz. (See Figure 3 for detailed response.) Compensation is achieved by simple 'C' (100pF) or RC network for lag-lead compensation. This network is placed in shunt to ground from Pin 3 (refer to Figure 4). Common-mode voltage is 5V for a standard positive supply and ground for negative supply.

#### The Pulse Width Modulator

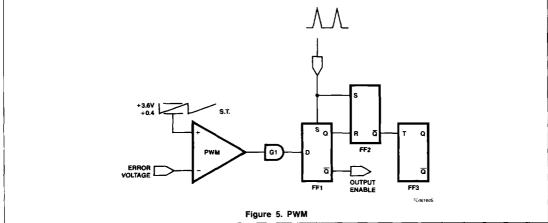

The pulse width modulator consists of a highspeed comparator with non-inverting input tied to the ramp generator and inverting input driven by the error amplifier output. (See Figure 5.) The resultant output forms a gated input to the metering flip-flop of which the 'Q' output feeds the 'R' input on the memory latch, and 'Q' output enables the main output gates (G2, G3). Alternate half-cycles are then enabled at the output (Pins 13 and 16) by the action of the toggle flip-flop. Initiation of the beginning of each half of the duty cycle is triggered by the start of the ramp, and termination occurs at the point in time where error output meets ramp voltage. It is with this sequence of control events that glitch-free output is guaranteed.

Pulse delay times in the PWM loop are specified in the data sheet. Maximum operating frequency must take such delay times into account in order to guarantee reliable functioning of the controller under a closed-loop

Gain vs Frequency

condition. The Signetics SG3526 is rated at a typical maximum frequency of 500kHz.

#### PWM GAIN

The DC gain of the pulse width modulator is determined by the ratio of input voltage to the primary power switching circuit to the active

ramp voltage differential. This is given as 3.6V and 0.4V with a differential of 3.2V.

#### Example:

The DC supply voltage to the power converter is 48V.

Therefore, PWM Gain =

$$\frac{48}{32}$$

= 15

(For further information on loop response calculations, please refer to references 1, 2.)

#### THE OUTPUT DRIVER STAGE

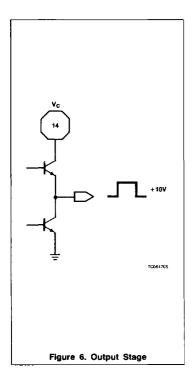

The output driver circuit has been carefully designed to prevent cross-conduction current spikes by eliminating any overlap conduction within the totem-pole structure. The source and sink capacity is rated at 200mA. In addition, supply voltage on the driver transistors is rated at 35V with no risk of destroying the IC due to excessive power dissipation. Note the output waveform in Figure 6 shows a full 10V drive level at the rated 200mA load current. This capability means that a Power MOS gate capacity of 4000pF can be driven with a voltage rise time of  $0.2\mu s$  for a 10V output.

#### PROTECTIVE FUNCTIONS

#### **Dead Time Control**

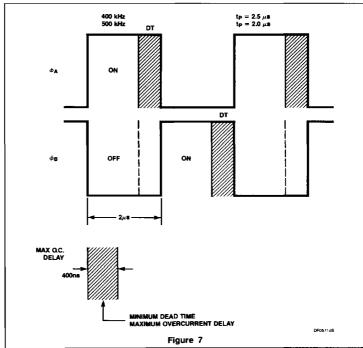

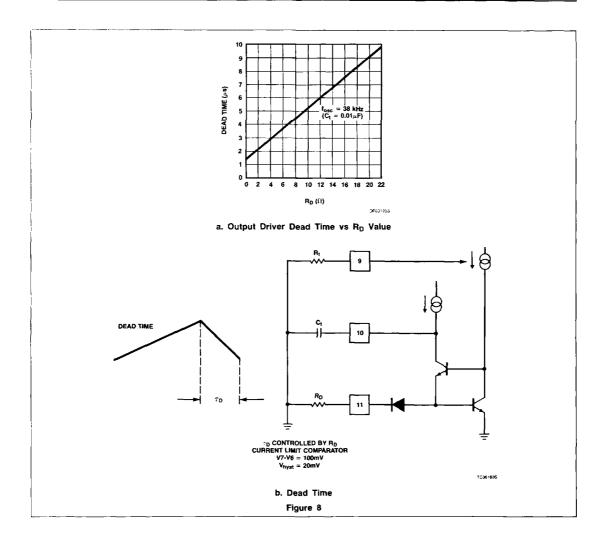

The dead time control circuit, incorporated as an integral part of the ramp oscillator, is provided to allow the designer the ability to control the minimum off time between alternate half-cycles. (See Figures 7 and 8.) The value of R<sub>D</sub>, as shown in the graph, allows the programming of this delay time from a minimum (Pin 11 grounded) of 1.5 $\mu$ s to a maximum of 9.7 $\mu$ s for a resistance of 22 $\Omega$  tied from Pin 11 to ground (Figure 8b). Obviously, dead time in the oscillator must conform to the limitations imposed by the operating frequency.

#### **Overcurrent Limit**

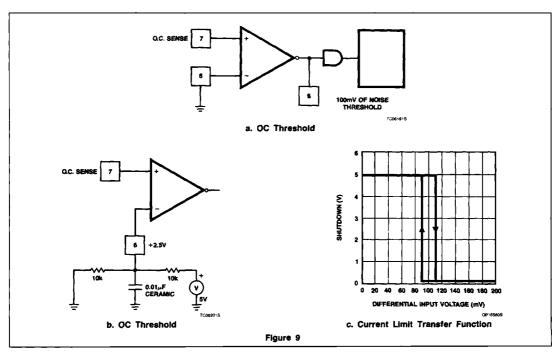

The overcurrent limit function is an integral part of the PWM circuit and, as such, inputs on Pins 6 and 7 will control the cycle-by-cycle operation of the output stage on both halves of the duty cycle. The overcurrent comparator is specifically designed to propagate a highspeed shutdown signal to turn off the output metering flip-flop in the event of an overcurrent of predetermined magnitude. The overcurrent sense inputs must be treated with care in respect to lead length and shunt capacity in order to obtain the maximum speed of response. Some typical circuit configurations are shown in Figure 9a. Note that either Pin 6 or 7 may be used as threshold reference voltage anywhere within the common-mode voltage range of the comparator. As shown, a simple technique is to ground Pin 6 and to program Pin 7 high (≥ 100mV) for shutdown. Very little noise immunity is allow-

SG3526

ed in this case. An improved method is to set Pin 6 at some positive voltage level (such as +2.5V) and thus provide an average noise threshold of 2.5V +100mV as shown in Figure 9b. This particular circuit provides a considerable improvement in noise immunity. Note that care must be taken in providing a low impedance reference at Pin 6. The overcurrent sense comparator provides a typical hysteresis of 20mV with a threshold of 100mV (Figure 9c). The typical delay time to deactivate the output drive is 700ns at  $T_{\rm J} = 25^{\circ}C$  rising to 1200ns at  $T_{\rm J} = 125^{\circ}C$ .

#### Soft-Start

This circuit provides a programmed ramp-up of the duty cycle at power-on, after remote shutdown (reset Pin 5) or low supply sense. A capacitor from Pin 4 to ground is charged towards the turn-on threshold by a  $100\mu A$  source. Time constants for various values of capacitance are plotted for the designer's convenience as shown in Figure 10. The softsart function is inititated by holding the reset below 0.2V which causes C to discharge. The Reset function, when low, also holds the error amplifier output low, initiating a minimum duty cycle at the output drivers. Low voltage shutdown occurs when  $V_S$  (Pin 17) drops below 4.0V.

#### **External Synchronization**

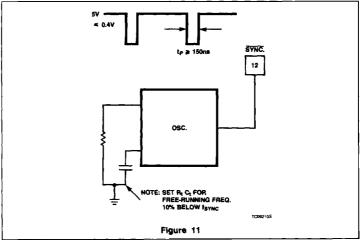

An external sync pulse may be injected into Pin 12 in order to provide synchronous operation of a switched-mode controller as shown in Figure 11. The required voltage level is active LOW with a threshold of 0.4V typical and a minimum pulse width of 150ns. A periodic signal at a rate approximately 10% higher than the free-running frequency of the ramp oscillator is required.

#### THERMAL CONSIDERATIONS

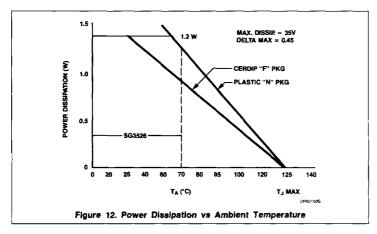

The power dissipation of the SG3526 must be considered in the design procedure in order to insure operation within the allowable device limits, particularly when maximum operating frequency is desired. The graph provided in Figure 12 will serve as a guide to staying within the device thermal limits in any design. Device dissipation is determined by summing all of the various current-voltage products, both pulsed and DC, noting the package type and the ambient operating temperature, then plotting this total device power on the respective derating graph.

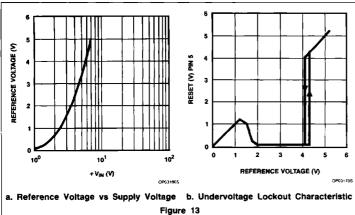

#### UNDERVOLTAGE LOCKOUT

Should supply voltage in Pin 17 drop low enough to affect the internal reference regu-

lator, an output inhibit circuit is activated. In addition, the voltage on Pin 5 (Reset) will be brought to a low state in order to signal remote sensing indicators. This characteristic is shown graphically in Figures 13a and b.

#### SYMMETRY CORRECTION

Should an external symmetry monitoring and correction circuit be required where drive unbalance may be critical, Pin 8, the shuthown function, is available to program either half of the output cycle off. This is accomplished by applying a TTL low signal with a pulse synchronized to the clock frequency. Keep in mind that the typical delay from Pin 8 is either output before shutdown is 400ns.

#### **DOUBLE PULSE PROTECTION**

The memory flip-flop must be reset by the PWM signal. This set-reset sequence provides insurance that alternate sync pulses initiate alternate A-B output cycle, preventing double pulses at the output.

#### CAUTION: Supply Decoupling -

Pin 17, the supply input to the internal regulator, should be decoupled from Pin 14 in order to prevent pulsed switching currents from interacting with outputs.

8-223

SG3526

SG3526

8

SG3526

#### **REFERENCES:**

- Advances in Switched-Mode Power Conversion, Volumes I and II, R.D.Middlebrook and Slobodan Cuk; Telsa Co., Pasadena, CA, 1983.

- Stability Analysis Made Simple, H. Dean Venable; Venable Industries, Rancho Palos Verdes, CA, 1981.