# H3248 2048 x 4 CMOS EEPROM

## **MICROELECTRONICS CENTER**

#### DESCRIPTION

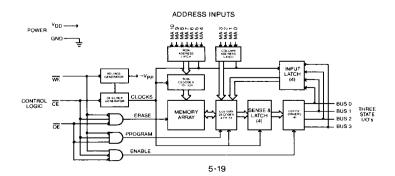

Hughes H3248 is a CMOS Electrically Erasable and Programmable ROM (EEPROM) organized as 2048 x 4. Read, write and erase operations are performed with a single 5V power supply using TTL level control signals.

All data modification is accomplished with  $\overline{WE}$  at a logic low level. Erasing or writing is controlled by appropriate control signals on  $\overline{CE}$  and  $\overline{OE}$  and by information presented on the address lines. Addresses and data are internally latched to free the system bus for other tasks during the write period.

A chip erase operation is performed when both  $\overline{OE}$  and  $\overline{WE}$  are at logic low. With a logic low on address line A10, a chip enable low pulse will execute a chip erase.

The H3248 is available in a variety of plastic and ceramic dual-in-line packages. Commercial (HC3248), Industrial (HI3248) and Military (HB3248) versions are available.

#### **FEATURES**

- 2048 x 4 CMOS EEPROM

- · Single 5V power supply-read, write and erase

- · Very low power dissipation CMOS

- · On chip address and data latches

- · Chip Erasable

- · 3-line control architecture

- 10-vear data retention

- 10,000 erase/write cycles

#### PIN CONFIGURATION

\*No connection to this pin allowed (Internal pull-up to V<sub>DD</sub>).

### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

DC Supply Voltage Range ..... -0.3 to +7 Volts (All voltages referenced to GND terminal)

Input Voltage Range ..... -0.3 to VDD + 0.3V

Storage Temperature Range ... -65°C to +150°C

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Erase/Write functions above VDD = 5.5V will adversely affect endurance.

# RECOMMENDED OPERATING CONDITIONS

|                   |                 | All Modes       |

|-------------------|-----------------|-----------------|

| Supply Voltage    |                 | 5±5% Volts      |

| Temperature Range | Plastic Package | -40°C to +85°C  |

|                   | Ceramic Package | -55°C to +125°C |

## DC OPERATING CHARACTERISTICS

Vpp = 5.5V Unless Otherwise Specified

| Symbol           |                                 |      | +28°E |      | -4076 | lo +85°C | -66°C1 | 9+128°C | Units |                                                        |

|------------------|---------------------------------|------|-------|------|-------|----------|--------|---------|-------|--------------------------------------------------------|

|                  |                                 | May. | 112   |      | Min   | Man      | HAX    | Max     |       | Conditions                                             |

| IDDS             | V <sub>DD</sub> Standby Current | -    | 2     | 100  | -     | 100      | -      | 100     | μА    | $\overline{CE} = \overline{OE} = \overline{WE} = 5.5V$ |

| IDDA             | V <sub>DD</sub> Active Current  | -    | 750   | 1000 | -     | 1000     | -      | 1000    | μΑ    | <u>CE</u> = <u>OE</u> = 0<br><u>WE</u> = 5.5V          |

| IDPP             | V <sub>DD</sub> Program Current | -    | 1     | 2    | -     | 2        | -      | 2       | mA    | WE = 0V                                                |

| VOL              | Output Low Voltage              | -    | 0.25  | 0.45 | _     | 0.45     | -      | 0.45    | ٧     | V <sub>DD</sub> = 5V<br>I <sub>O</sub> = 2.1 mA        |

| VOH              | Output High Voltage             | 3.0  | 4.5   | -    | 3.0   | -        | 3.0    | -       | ٧     | $V_{DD} = 5V$ $I_{O} = -400\mu A$                      |

| VIL              | Input Low Voltage               | -    | _     | 0.8  | -     | 0.8      | -      | 0.8     | v     | V <sub>DD</sub> = 5V                                   |

| VιΗ              | Input High Voltage              | 3.0  | -     | -    | 3.0   | -        | 3.0    | _       | v     | V <sub>DD</sub> = 5V                                   |

| ILI              | Input Leakage Current           | -    | -     | ±10  | -     | ±10      | -      | ±10     | μА    | V <sub>IN</sub> = 0 or V <sub>DD</sub>                 |

| l <sub>L</sub> O | Output Leakage Current          | -    | -     | ±10  | _     | ±10      | -      | ±10     | μА    | V <sub>O</sub> = 0 or V <sub>DD</sub>                  |

#### Notes

- 1. Endurance is the maximum number of erase/write cycles per byte.

- 2. Retention is the amount of time the data is retained in memory without power being supplied.

## AC OPERATING CHARACTERISTICS

H3248

Read: VDD = 5V ±5% Unless Otherwise Specified

| Section          | Program (1)                                            |       | +26°C |       |     | a ien C | -30%)   | o ylate t |    | Transport        |

|------------------|--------------------------------------------------------|-------|-------|-------|-----|---------|---------|-----------|----|------------------|

|                  |                                                        | A Dr. | (4)   | Sibs. | Ma  | No.     | e de la |           |    | Completed        |

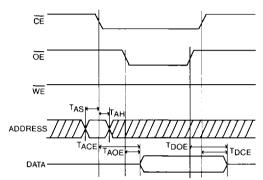

| <sup>t</sup> ASU | Address Set-Up Time                                    | 475   | -     | -     | 550 | -       | 625     | -         | ns | WE = VL          |

| t <sub>A</sub> H | Address Hold Time                                      | 100   | 50    | -     | 125 | -       | 150     | -         | ns | WE = VL          |

| †ACE             | Access Time from CE                                    | -     | 500   | 700   | -   | 825     | -       | 925       | ns | WE = VL, OE = VL |

| <sup>t</sup> OE  | Output Enable Time                                     | -     | 250   | 400   | -   | 450     | -       | 500       | ns | WE = VL, OE = VL |

| tDCE             | CE to High Impedance                                   | 0     | -     | _     | 0   | -       | 0       | -         | ns | -                |

| tDOE             | OE to High Impedance                                   | 0     | -     | -     | 0   | _       | 0       | _         | ns | CE = VL, WE = VL |

| tОН              | Output Hold from OE, CE, or WE which ever occurs first | 0     | _     | _     | 0   | -       | o       | -         | ns | -                |

| tCEH             | CE High Time                                           | 1.1   | 0.5   | -     | 1.4 | -       | 1.4     | -         | μS | -                |

| IDYN             | V <sub>DD</sub> Dynamic Current                        | -     | 0.5   | 1.0   | -   | 1.2     | -       | 1.2       | mA | f = 100 KHz      |

**Read Test Conditions**

Output Load:  $C_L = 50 \text{ pF}$ Input Levels:  $V_H = 3.2 \text{ Volts}, V_L = 0.45 \text{ Volts}$

Timing Measurement Reference Levels: Input = Output = 50%

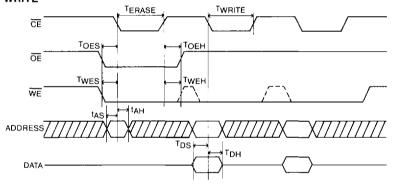

# Erase and Write, VDD = 5V Unless Otherwise Specified

| Symbol          |                                   |     | -25°C |   | -sort | The or series |     | 2.2 | Veille | carcillars            |

|-----------------|-----------------------------------|-----|-------|---|-------|---------------|-----|-----|--------|-----------------------|

| †WRITE          | Byte Write Pulse Width            | 1   | -     | - | 1     | -             | 1   | -   | ms     | WE = VL               |

| tas .           | Byte Write Address<br>Set-Up Time | 400 | -     | - | 475   | -             | 550 | -   | ns     | WE = VL               |

| †AH             | Byte Write Address<br>Hold Time   | 100 | -     | - | 125   | _             | 150 | -   | ns     | $\overline{WE} = V_L$ |

| tDS             | Byte Write Data<br>Set-Up Time    | 100 | -     | - | 125   | -             | 150 | -   | ns     | WE = VL               |

| <sup>†</sup> DH | Byte Write Data<br>Hold Time      | 100 | -     | - | 125   | -             | 150 | -   | ns     | WE = VL               |

**Programming Test Conditions**

Input Levels:  $V_H = 3.2$  Volts,  $V_L = 0.45$  Volts

Timing Measurement Reference Levels: Input = Output = 50%

# TIMING DIAGRAM

# **READ CYCLE**

# **ERASE / WRITE**

#### **OPERATING MODES**

The H3248 has three modes of operation: Read, Chip Erase and Byte Write, all enabled when the chip is enabled ( $\overline{CE} = low$ ). In the Read Mode the H3248 functions as a normal CMOS ROM. When the Write Enable input ( $\overline{WE}$ ) is lowered to V<sub>IL</sub>, the Erase or Write Mode is enabled. In the Erase Mode, all bytes are reset to a logic low (GND). In the Write Mode, bits of addressed byte may be programmed to a logic high. An Erase Operation is required before re-writing over previously Programmed data. Detailed procedures for each mode follow:

**READ MODE:** The circuit reads addresses on the falling edge of  $\overline{CE}$  and latches the accessed data until  $\overline{CE}$  goes high again. The latched data will appear at the outputs whenever  $\overline{CE}$  is low,  $\overline{WE}$  is high, and  $\overline{OE}$  is low.

**ERASE MODE:** A Chip Erase (all 0's in memory) is accomplished by setting  $\overline{\text{WE}}$  and  $\overline{\text{OE}}$  low, and then pulsing  $\overline{\text{CE}}$  low.

**WRITE MODE:** A Write consists of programming 1's into bits that contain a 0. A byte is written by setting  $\overline{\text{WE}}$  and  $\overline{\text{OE}}$  low, and pulsing  $\overline{\text{CE}}$  low. The address and data lines must be valid when  $\overline{\text{CE}}$  falls. Data and addresses are latched while  $\overline{\text{CE}}$  is low.

#### SUMMARY OF OPERATING MODES

Logic 1 = High, Logic 0 = Low, X = Do not care

| STATE              | a a | WE . | <b>. o</b> € | VO BUS      |

|--------------------|-----|------|--------------|-------------|

| Standby (selected) | 1   | х    | x            | Floating    |

| Read               | 0   | 1    | 0            | Data Output |

| Erase (Block)      | 0   | 0    | 0            | Floating    |

| Write              | 0   | 0    | 1            | Data Input  |

## PIN DESCRIPTIONS

A 0 - A 9: Address inputs which select one of 1024 bytes of memory for either Read or Program. The addresses need to be valid during the falling edge of  $\overline{CE}$ .

$I/O_0$  -  $I/O_7$ : Bidirectional three-state data lines that are Data outputs during a Read operation and Data inputs during a Write operation.

**GND:** Negative supply terminal and V = 0 reference.

Vpp: Positive supply terminal.

WE: Write Enable. A Logic Low enables all Data modifications. Erasing or Writing is controlled by appropriate control signals on CE and OE.

**OE**: Output Enable. A Logic High disables the Data Output Drivers in normal operation. During programming operations, a Logic Low selects the Erase Mode.

CE: Chip Enable. A Logic Low at this input latches the input address during a Read operation and latches both addresses and data inputs during a Write operation. For the read operation, accessed data is latched and valid as long as CE is held at a Logic Low. A programming operation is initiated on the falling edge of CE and terminated on the rising edge of CE.

| Information furnished by Hughes is believed to be accurate and reliable. I                                                                       | However, no responsibility is assumed by Hughes for its |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| use; nor for any infringements or patents or other rights of third parties implication or otherwise under any patent or patent rights of Hughes. | which may result from its use. No license is granted by |

| Hughes Microelectronics Center                                                                                                                   |                                                         |

| 500 Superior Avenue, Box H<br>Newport Baech, CA 92658-8903<br>Tele: (714) 759-2727<br>FAX: (714) 759-2720                                        | 12/88<br>Printed in U.S.A.                              |

|                                                                                                                                                  |                                                         |