## Dual Ultra High-Speed FET Driver

#### **FEATURES**

- · 25ns Rise and Fall into 1000pF

- 15ns Propagation Delay

- 1.5A Source or Sink Output Drive

- Operation with 5V to 35V Supply

- High-Speed Schottky NPN Process

- 8-PIN MINIDIP Package

####

| input cupply voltage, vec       | <del></del> <b>.</b> |

|---------------------------------|----------------------|

| Output Current (Source or Sink) |                      |

| Steady State                    | +/-500mA             |

| Peak Transient                  | +/-1 <i>.</i> 5A     |

| Inputs                          |                      |

| Maximum Forced Voltage          | 0.3V to 7V           |

| Maximum Forced Current          | +/- 10mA             |

| Power Dissipation               | <i></i> 1W           |

| Operating Junction Temperature  | -55°C to +150°C      |

Note 1: Unless otherwise indicated, voltages are reference to ground and currents are positive into, negative out of, the specified terminals. All reliability information for this device has been gathered at an ambient air temperature of 125°C, and a supply voltage of 25V.

Note 2: Consult Unitrode Integrated Circuits databook for information regarding thermal specifications and limitations of packages.

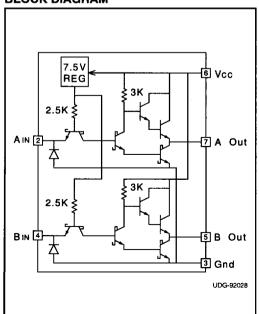

#### **BLOCK DIAGRAM**

#### DESCRIPTION

The UC1711 family of FET drivers are made with an all-NPN Schottky process in order to optimize switching speed, temperature stability, and radiation resistance. The cost for these benefits is a quiescent supply current which varies with both output state and supply voltage. For lower power requirements, refer to the the UC1709 family which is both pin compatible with, and functionally equivalent to the UC1711.

These devices implement inverting logic with TTL compatible inputs, and output stages which will either source, or sink in excess of 1.5A of load current with minimal cross-conduction charge. Due to their monolithic construction, the channels are well matched and can be paralleled for doubled output current capability.

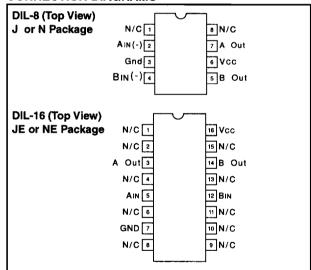

#### CONNECTION DIAGRAMS

### PLCC-20 (Top View) QP Package

|            | 3 | 2  | 1      | 20 | 19 |    | l |

|------------|---|----|--------|----|----|----|---|

| (4         |   |    | $\cup$ |    |    | 18 | þ |

| ₫ 5        |   |    |        |    |    | 17 | þ |

| ₫6         |   |    |        |    |    | 16 | þ |

| <b>(</b> 7 |   |    |        |    |    | 15 | þ |

| (8         | _ |    |        |    |    | 14 | þ |

|            | 9 | 10 | 11     | 12 | 13 |    |   |

|            |   |    |        |    |    |    |   |

| PACKAGE PIN FUNCTION |         |  |

|----------------------|---------|--|

| FUNCTION             | PIN     |  |

| N/C                  | 1       |  |

| Ain                  | 2       |  |

| N/C                  | 3 - 5   |  |

| GND                  | 6       |  |

| N/C                  | 7-9     |  |

| Bin                  | 10      |  |

| N/C                  | 11 - 13 |  |

| B Out                | 14      |  |

| N/C                  | 15      |  |

| Vcc                  | 16      |  |

| N/C                  | 17      |  |

| A Out                | 18      |  |

| N/C                  | 19      |  |

| N/C                  | 20      |  |

# **ELECTRICAL CHARACTERISTICS:** Unless otherwise stated specifications hold for T<sub>A</sub> = 0 to 70°C for the UC3711, and T<sub>A</sub> = -55 to 125°C for the UC1711, Vcc = 15V. T<sub>A</sub> = T<sub>J</sub>.

| PARAMETER                          | TEST CONDITIONS               | MIN  | TYP  | MAX | UNITS |

|------------------------------------|-------------------------------|------|------|-----|-------|

| Input Supply                       |                               |      |      |     |       |

| Supply Current (Note 3)            | Both inputs = 0V; Vcc = 15V   |      | 11   | 15  | mA    |

|                                    | Both inputs = 5V; Vcc = 15V   |      | 20   | 27  | mA    |

|                                    | Both inputs = 0V; Vcc = 35V   |      | 15   | 20  | mA    |

|                                    | Both inputs = 5V; Vcc = 35V   |      | 41   | 56  | mA    |

| Logic Inputs                       |                               |      |      |     |       |

| Logic 0 Input Voltage              |                               |      |      | 8.0 | ν     |

| Logic 1 Input Voltage              |                               | 2.2  |      |     | V     |

| Input Current                      | VIN = 0V                      | -5.0 | -2.7 |     | mA    |

|                                    | VIN = 5V                      |      | 0.5  | 2.0 | mA    |

| Output Stages                      |                               |      |      |     |       |

| Output High Level                  | ISOURCE = 20mA, below Vcc     |      | 1.5  | 2.0 | ٧     |

|                                    | ISOURCE = 200mA, below Vcc    |      | 2.0  | 3.0 | ν     |

| Output Low Level                   | Isink = 20mA                  |      | .25  | 0.4 | V     |

| ·                                  | ISINK = 200mA                 |      | 0.4  | 1.0 | V     |

| Switching Characteristics (Note 4) |                               |      |      |     |       |

| Rise Time Delay, TPLH              | CLOAD = 0                     |      | 10   | 40  | ns    |

|                                    | CLOAD = 1000pF, (Note 5)      |      | 15   | 50  | ns    |

|                                    | CLOAD = 2200pF                |      | 20   | 55  | ns    |

| Fall Time Delay, TPHL              | CLOAD = 0                     |      | 3    | 20  | ns    |

|                                    | CLOAD = 1000pf, (Note 5)      |      | 5    | 20  | ns    |

|                                    | CLOAD = 2200pF                |      | 5    | 20  | ns    |

| Rise Time, TLH                     | CLOAD = 0, (Note 5)           |      | 12   | 25  | ns    |

|                                    | CLOAD = 1000pF, (Note 5)      |      | 25   | 40  | ns    |

|                                    | CLOAD = 2200pF                |      | 40   | 55  | ns    |

| Fall Time, THL                     | CLOAD = 0, (Note 5)           |      | 7    | 15  | กร    |

|                                    | CLOAD = 1000pF, (Note 5)      |      | 25   | 40  | ns    |

|                                    | CLOAD = 2200pF                |      | 40   | 55  | ns    |

| Total Supply Current               | Freq = 200kHz, 50% Duty-cycle |      |      |     |       |

|                                    | Both Channels Switching       |      |      |     |       |

|                                    | CLOAD = 0                     |      | 17   | 23  | mA    |

|                                    | CLOAD = 2200pF                |      | 29   | 35  | mA    |

Note 3: Supply currents at other input supply votages can be calculated by extrapolating the 15V and 35V supply currents. The impedance of the chip at the Vcc pin is linear for supply voltages from 8V to 35V, the approximate value of this impedance is 4.3k for both inputs low, 0.94k for both inputs high, and 1.54k for one input high and one low.

Note 4: Switching test conditions are, VCC = 15V, Input voltage waveform levels are 0V and 5V, with transition times of <3ns. The timing terms are defined as: TPHL Propagation delay 50% VIN to 90% VOUT; TPLH Propagation delay 50% VIN to 10% VOUT; THL 90% VOUT to 10% VOUT; TLH 10% VOUT to 90% VOUT.

Note 5: This specification not tested in production. Unless otherwise stated specifications hold for TA = 0 to  $70^{\circ}C$  for the UC3711, and TA = -55 to  $125^{\circ}C$  for the UC1711, VCC = 15V. TA = TJ.