# 3.3V, 3.2Gbps VCSEL Driver

## **FEATURES**

- 155Mbps to 3.2Gbps Laser Diode Driver for VCSELs\*

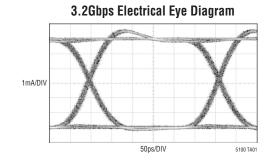

- 60ps Rise and Fall Times, 10ps Deterministic Jitter

- Eye Diagram is Stable and Consistant Across Modulation Range and Temperature

- 1mA to 12mA Modulation Current

- Easy Board Layout, Laser can be Remotely Located if Desired

- No Input Matching or AC Coupling Components Needed

- On-Chip ADC for Monitoring Critical Parameters

- Digital Setup and Control with I<sup>2</sup>C<sup>TM</sup> Serial Interface

- Emulation and Set-Up Software Available\*\*

- Operates Standalone or with a Microprocessor

- On-Chip DACs Eliminate External Potentiometers

- Constant Current or Automatic Power Control

- First and Second Order Temperature Compensation

- On-Chip Temperature Sensor

- Extensive Eve Safety Features

- Single 3.3V Supply

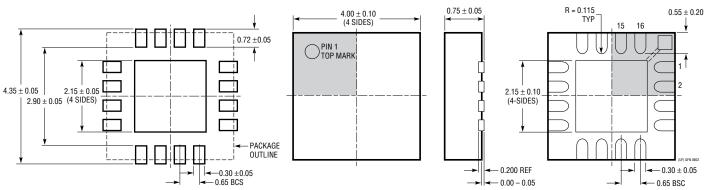

- 4mm × 4mm QFN Package

## **APPLICATIONS**

- Gigabit Ethernet and Fibre Channel Transceivers

- SFF and SFP Transceiver Modules

- Proprietary Fiber Optic Links

### DESCRIPTION

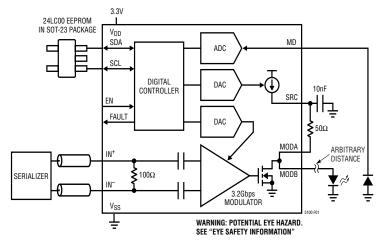

The LTC®5100 is a 3.2Gbps VCSEL driver offering an unprecedented level of integration and high speed performance. The part incorporates a full range of features to ensure consistently outstanding eye diagrams. The data inputs are AC coupled, eliminating the need for external capacitors. The LTC5100 has a precisely controlled  $50\Omega$  output that is DC coupled to the laser, allowing arbitrary placement of the IC. No coupling capacitors, ferrite beads or external transistors are needed, simplifying layout, reducing board area and the risk of signal corruption. The unique output stage of the LTC5100 confines the modulation current to the ground system, isolating the high speed signal from the power supply to minimize RFI.

The LTC5100 supports fully automated production with its extensive monitoring and control features. Integrated 10-bit DACs eliminate the need for external potentiometers. An onboard 10-bit ADC provides the laser current and voltage, as well as monitor diode current and temperature. Status information is available from the  $I^2C$  serial interface for feedback and statistical process control.

An internal digital controller compensates laser temperature drift and provides extensive laser safety features.

7, LTC and LT are registered trademarks of Linear Technology Corporation.

I<sup>2</sup>C is a trademark of Philips Electronics N.V.

\*Vertical Cavity Surface Emitting Laser \*\*Downloadable from www.linear.com

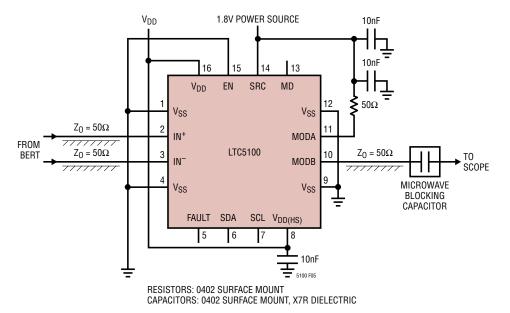

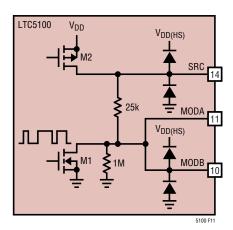

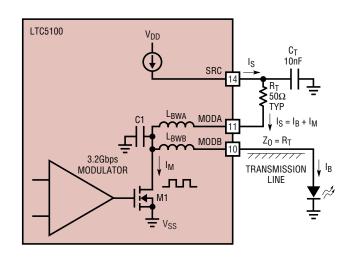

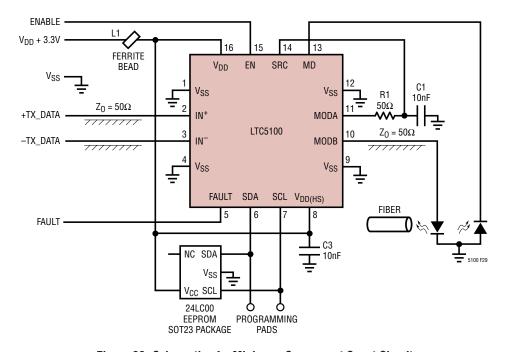

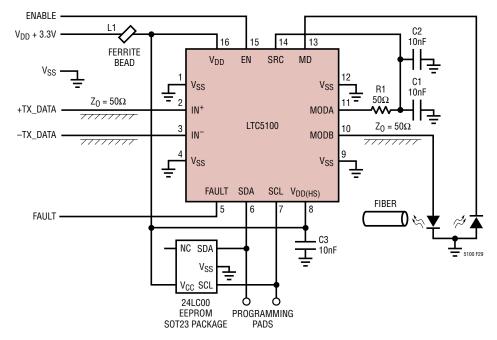

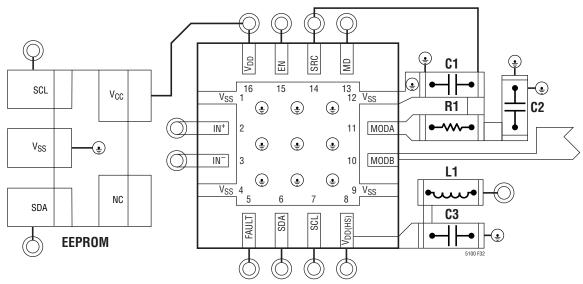

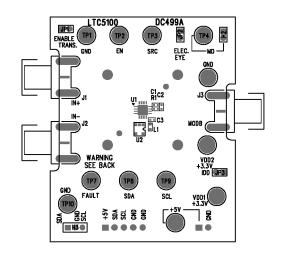

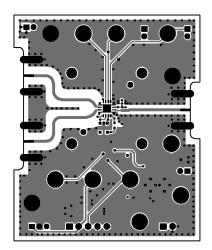

# TYPICAL APPLICATION

Figure 1. VCSEL Transmitter with Automatic Power Control

# **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                         |

|------------------------------------------------------------------|

| V <sub>DD</sub> , V <sub>DD(HS)</sub>                            |

| $IN^+$ , $IN^-$ (CmI_en = 1) (Note 6)                            |

| Peak Voltage $V_{DD(HS)} - 1.2V$ to $V_{DD(HS)} + 0.3V$          |

| Average Voltage $V_{DD(HS)} - 0.6V$ to $V_{DD(HS)} + 0.3V$       |

| $IN^+$ , $IN^-$ (Cml_en = 0) (Note 4)0.3V to $V_{DD(HS)} + 0.3V$ |

| Cml_en = 0 (Note 4)                                              |

| Peak Difference Between IN+ and IN ±2.5V                         |

| Average Difference Between IN+ and IN ±1.25V                     |

| MODA, MODB (Transmitter Disabled) –0.3V to 2.75V                 |

| MODA, MODB                                                       |

| (Transmitter Enabled) $V_{DD(HS)} - 2.75V$ to 2.75V              |

| EN, SDA, SCL, FAULT $-0.3V$ to $V_{DD} + 0.3V$                   |

| MD, SRC $-0.3V$ to $V_{DD}$                                      |

| Ambient Operating Temperature Range −40°C to 85°C                |

| Storage Temperature Range65°C to 125°C                           |

|                                                                  |

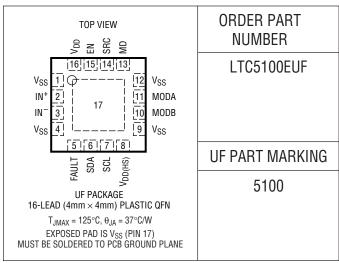

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

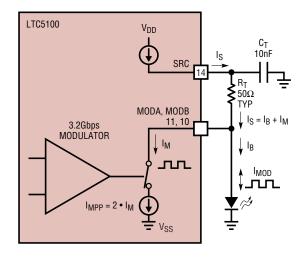

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}\text{C}$ ;  $V_{DD} = V_{DD(HS)} = 3.3\text{V}$ ,  $I_S = 24\text{mA}$ ;  $I_M = 12\text{mA}$  ( $I_{MPP} = 24\text{mA}$ );  $49.9\Omega$ , 1% resistor from SRC (Pin 14) to MODA (Pin 11);  $50\Omega$ , 1% load AC coupled to MODB (Pin 10); 10nF, 10% capacitor from SRC (Pin 14) to  $V_{SS}$ ; CmI en = 0, Lpc en = 1, transmitter enabled, unless otherwise noted. Test circuit in Figure 5.

| PARAMETER                                                                                          | RAMETER CONDITIONS                                                                                                    |   |                     |                     |                            | UNITS                |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|---------------------|---------------------|----------------------------|----------------------|

| Power Supply                                                                                       |                                                                                                                       |   |                     |                     |                            |                      |

| V <sub>DD</sub> , V <sub>DD(HS)</sub> Operating Voltage                                            |                                                                                                                       | • | 3.135               | 3.3                 | 3.465                      | V                    |

| V <sub>DD</sub> + V <sub>DD(HS)</sub> Quiescent Current,<br>Excluding the SRC Pin Current (Note 2) | V <sub>DD</sub> = 3.465V                                                                                              |   |                     |                     |                            |                      |

|                                                                                                    | Transmitter Disabled, Power_down_en = 1                                                                               |   |                     | 4.5                 |                            | mA                   |

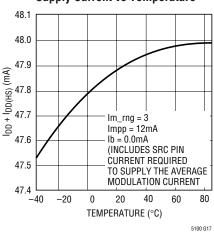

|                                                                                                    | Transmitter Enabled, Is_rng = Im_rng = 3<br>Impp = 24mA                                                               |   |                     | 54                  |                            | mA                   |

| High Speed Data Inputs (IN+ and IN- Pins) (Test                                                    | Circuit, Figure 5)                                                                                                    |   |                     |                     |                            |                      |

| Input Signal Amplitude                                                                             | Peak-to-Peak Differential Voltage (The Single-<br>Ended Peak-to-Peak Voltage is One Half the<br>Differential Voltage) |   | 5                   | 500 to 240          | 0                          | mV <sub>P-P</sub>    |

| Common Mode Input Signal Range (Note 3)                                                            | Cml_en = 0 (Note 4)                                                                                                   |   | 0                   |                     | V <sub>DD(HS)</sub>        | V                    |

| Differential Input Resistance                                                                      |                                                                                                                       |   |                     | 80 to 120           |                            | Ω                    |

| Common Mode Input Resistance                                                                       | Cml_en = 0 (Note 5)                                                                                                   |   |                     | 50                  |                            | kΩ                   |

| Open-Circuit Voltage                                                                               | Cml_en = 0 (Note 5)                                                                                                   |   |                     | 1.65                |                            | V                    |

| SRC Pin Current, I <sub>S</sub>                                                                    |                                                                                                                       |   | -                   |                     |                            |                      |

| Full-Scale I <sub>S</sub> Current                                                                  | Is_rng = 0<br>  Is_rng = 1<br>  Is_rng = 2<br>  Is_rng = 3                                                            |   | 6<br>12<br>18<br>24 | 9<br>18<br>27<br>36 |                            | mA<br>mA<br>mA<br>mA |

| Minimum Operating Current (Note 7)                                                                 |                                                                                                                       |   | 1/16 of F           | ull-Scale I         | <sub>S</sub> Current       |                      |

| Resolution                                                                                         |                                                                                                                       |   |                     | 10                  |                            | Bits                 |

| SRC Pin Voltage Range                                                                              |                                                                                                                       |   | 1.2                 |                     | V <sub>DD</sub> –<br>200mV | V                    |

|                                                                                                    |                                                                                                                       |   |                     |                     |                            | 5100f                |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ;  $V_{DD} = V_{DD(HS)} = 3.3V$ ,  $I_S = 24mA$ ;  $I_M = 12mA$  ( $I_{MPP} = 24mA$ );  $49.9\Omega$ , 1% resistor from SRC (Pin 14) to MODA (Pin 11);  $50\Omega$ , 1% load AC coupled to MODB (Pin 10); 10nF, 10% capacitor from SRC (Pin 14) to  $V_{SS}$ ;  $CmI_{en} = 0$ ,  $Lpc_{en} = 1$ , transmitter enabled, unless otherwise noted. Test circuit in Figure 5.

| PARAMETER                                                 | CONDITIONS                                                          | MIN                                                                                     | TYP                                                                                     | MAX | UNITS                |

|-----------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|----------------------|

| Laser Bias Current, I <sub>B</sub>                        |                                                                     |                                                                                         |                                                                                         |     |                      |

| Full-Scale Current (Note 8)                               | Is_rng = 0<br>Is_rng = 1<br>Is_rng = 2<br>Is_rng = 3                | 6 - I <sub>M</sub><br>12 - I <sub>M</sub><br>18 - I <sub>M</sub><br>24 - I <sub>M</sub> | 9 – I <sub>M</sub><br>18 – I <sub>M</sub><br>27 – I <sub>M</sub><br>36 – I <sub>M</sub> |     | mA<br>mA<br>mA<br>mA |

| Absolute Accuracy                                         | SRC Pin and MODA, MODB Pin Currents Within Specified Voltage Ranges |                                                                                         | ±25                                                                                     |     | %                    |

| Resolution                                                |                                                                     |                                                                                         | 10                                                                                      |     | Bits                 |

| Linear Tempco Resolution                                  |                                                                     |                                                                                         | 122                                                                                     |     | ppm/°C               |

| Linear Tempco Range                                       |                                                                     |                                                                                         | ±15625                                                                                  |     | ppm/°C               |

| Second Order Tempco Resolution                            |                                                                     |                                                                                         | 3.81                                                                                    |     | ppm/°C2              |

| Second Order Tempco Range                                 |                                                                     |                                                                                         | ±488                                                                                    |     | ppm/°C2              |

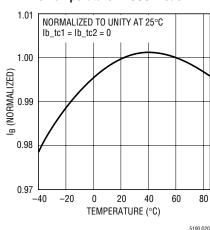

| Temperature Stability                                     | Ib_tc1 = 0, Ib_tc2 = 0                                              |                                                                                         | ±500                                                                                    |     | ppm/°C               |

| Off-State Leakage                                         | Transmitter Disabled, V <sub>SRC</sub> = 1.2V                       |                                                                                         |                                                                                         | 50  | μΑ                   |

| MODA, MODB Pin Current, I <sub>M</sub>                    |                                                                     |                                                                                         |                                                                                         |     |                      |

| Full Scale, Peak-to-Peak Modulation Current (Note 9)      | Im_rng = 0<br>Im_rng = 1<br>Im_rng = 2<br>Im_rng = 3                | 6<br>12<br>18<br>24                                                                     | 9<br>18<br>27<br>36                                                                     |     | mA<br>mA<br>mA<br>mA |

| Minimum Operating Current (Note 10)                       |                                                                     |                                                                                         | I-Scale Peak<br>Iulation Curr                                                           |     |                      |

| Resolution (Note 11)                                      |                                                                     |                                                                                         | 9                                                                                       |     | Bits                 |

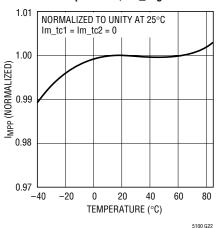

| Current Stability                                         | Im_tc1 = 0, Im_tc2 = 0                                              |                                                                                         | ±500                                                                                    |     | ppm/°C               |

| Voltage Range                                             | Peak Transient Voltage on MODA and MODB                             | 1.2                                                                                     |                                                                                         | 2.7 | V                    |

| Absolute Accuracy of the Modulation Current               |                                                                     |                                                                                         | ±25                                                                                     |     | %                    |

| Linear Tempco Resolution                                  |                                                                     |                                                                                         | 122                                                                                     |     | ppm/°C               |

| Linear Tempco Range                                       |                                                                     |                                                                                         | ±15625                                                                                  |     | ppm/°C               |

| Second Order Tempco Resolution                            |                                                                     |                                                                                         | 3.81                                                                                    |     | ppm/°C2              |

| Second Order Tempco Range                                 |                                                                     |                                                                                         | ±484                                                                                    |     | ppm/°C2              |

| Maximum Bit Rate                                          |                                                                     |                                                                                         | 3.2                                                                                     |     | Gbps                 |

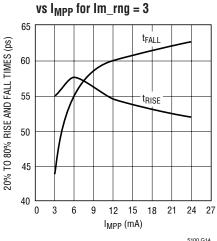

| Modulation Current Rise and Fall Times                    | 20% to 80% Measured with K28.5 Pattern at 2.5Gbps                   |                                                                                         | 60                                                                                      |     | ps                   |

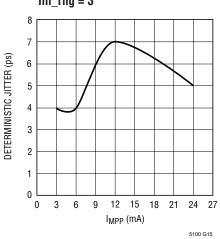

| Deterministic Jitter, Peak-to-Peak (Note 12)              | Measured with K28.5 Pattern at 3.2Gbps                              |                                                                                         | 10                                                                                      |     | ps                   |

| Random Jitter, RMS (Note 13)                              |                                                                     |                                                                                         | 1                                                                                       |     | ps <sub>RMS</sub>    |

| Pulse Width Distortion                                    |                                                                     |                                                                                         | 10                                                                                      |     | ps                   |

| Automatic Power Control (Note 14)                         |                                                                     |                                                                                         |                                                                                         |     |                      |

| Minimum Operating Current for the Monitor Diode (Note 15) |                                                                     |                                                                                         | % of Full Sca<br>itor Diode Cu                                                          |     |                      |

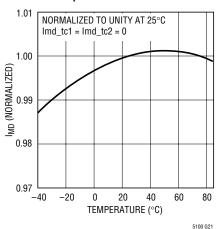

| Temperature Stability                                     | Imd_tc1 = 0, Imd_tc2 = 0                                            |                                                                                         | ±500                                                                                    |     | ppm/°C               |

| Monitor Diode Bias Voltage (Note 16)                      | I <sub>MD</sub> ≤ 1600μA                                            |                                                                                         | 1.45                                                                                    |     | V                    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ;  $V_{DD} = V_{DD(HS)} = 3.3V$ ,  $I_S = 24mA$ ;  $I_M = 12mA$  ( $I_{MPP} = 24mA$ );  $49.9\Omega$ , 1% resistor from SRC (Pin 14) to MODA (Pin 11);  $50\Omega$ , 1% load AC coupled to MODB (Pin 10); 10nF, 10% capacitor from SRC (Pin 14) to  $V_{SS}$ ;  $CmI_{en} = 0$ ,  $Lpc_{en} = 1$ , transmitter enabled, unless otherwise noted. Test circuit in Figure 5.

| PARAMETER                                             | CONDITIONS                            | MIN TYP MAX                          | UNITS     |

|-------------------------------------------------------|---------------------------------------|--------------------------------------|-----------|

| Automatic Power Control (Note 14)                     |                                       |                                      |           |

| Temperature Compensation (Note 17)                    |                                       |                                      |           |

| Linear Tempco Resolution                              |                                       | 254 • Imd_nom/1024                   | ppm/°C    |

| Linear Tempco Range                                   |                                       | ±32300 • Imd_nom/1024                | ppm/°C    |

| ADC                                                   | · · · · · · · · · · · · · · · · · · · |                                      |           |

| Resolution                                            |                                       | 10                                   | Bits      |

| Source Current Measurement, I <sub>S</sub> (SRC Pin C | urrent)                               |                                      |           |

| Full Scale                                            | Is_rng = 0                            | 9                                    | mA        |

|                                                       | Is_rng = 1                            | 18                                   | mA        |

|                                                       | Is_rng = 2                            | 27                                   | mA        |

|                                                       | Is_rng = 3                            | 36                                   | mA        |

| Accuracy                                              |                                       | ±3% of Full Scale                    |           |

| Accessed Management Management of                     | (N-1-40)                              | ±25% of Reading                      |           |

| Average Modulation Current Measurement,               |                                       |                                      |           |

| Full Scale                                            | Im_rng = 0                            | 9                                    | mA<br>m A |

|                                                       | Im_rng = 1<br>Im_rng = 2              | 18<br>27                             | mA<br>mA  |

|                                                       | Im_rng = 3                            | 36                                   | mA        |

| Accuracy                                              |                                       | ±3% of Full Scale<br>±25% of Reading |           |

| Laser Diode Voltage Measurement                       |                                       |                                      |           |

| Full Scale                                            |                                       | 3.5                                  | V         |

| Accuracy                                              |                                       | ±150mV ±10% of Reading               |           |

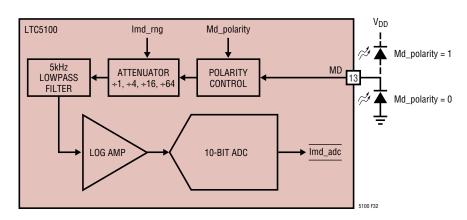

| Monitor Diode Current Measurement (Note 1             | 9)                                    |                                      |           |

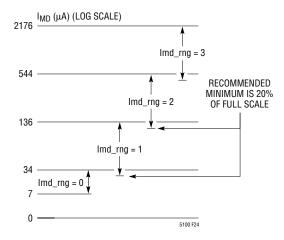

| Full Scale                                            | Imd_rng = 0                           | 34                                   | μΑ        |

|                                                       | Imd_rng = 1                           | 136                                  | μΑ        |

|                                                       | Imd_rng = 2                           | 544                                  | μA        |

|                                                       | Imd_rng = 3                           | 2176                                 | μA        |

| Zero Scale                                            | ADC Code = 0                          | 1/8 of Full Scale                    |           |

| Resolution Relative to Reading                        |                                       | 0.2                                  | %         |

| Accuracy                                              |                                       | ±25% of Reading                      |           |

| Temperature Measurement                               |                                       |                                      |           |

| Full Scale                                            | Celsius                               | 239                                  | °C        |

| Sensitivity                                           |                                       | 0.500                                | °C/LSB    |

| Termination Resistor Voltage Measurement              |                                       |                                      |           |

| Full Scale                                            | Is_rng = 0                            | 400                                  | mV        |

|                                                       | Is_rng = 1                            | 800                                  | mV        |

|                                                       | Is_rng = 2                            | 1200                                 | mV        |

| A                                                     | Is_rng = 3                            | 1600                                 | mV        |

| Accuracy                                              | 10)                                   | ±30mV ±10% of Reading                |           |

| Safety Shutdown, Undervoltage Lockout (UV             |                                       |                                      | T         |

| Undervoltage Detection                                | V <sub>DD</sub> Decreasing            | 2.8                                  | V         |

| Undervoltage Detection Hysteresis                     |                                       | 150                                  | mV        |

5100f

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ;  $V_{DD} = V_{DD(HS)} = 3.3V$ ,  $I_S = 24mA$ ;  $I_M = 12mA$  ( $I_{MPP} = 24mA$ );  $49.9\Omega$ , 1% resistor from SRC (Pin 14) to MODA (Pin 11);  $50\Omega$ , 1% load AC coupled to MODB (Pin 10); 10nF, 10% capacitor from SRC (Pin 14) to  $V_{SS}$ ;  $CmI_{en} = 0$ ,  $Lpc_{en} = 1$ , transmitter enabled, unless otherwise noted. Test circuit in Figure 5.

| PARAMETER                                             | CONDITIONS                                                                                                                                                                     | MIN TYP M | AX UNITS |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|

| Bias Current Limit, I <sub>B(LIMIT)</sub>             |                                                                                                                                                                                |           |          |

| Set Point Resolution                                  |                                                                                                                                                                                | 7         | Bits     |

| Set Point Range                                       | Is_rng = 0                                                                                                                                                                     | 9         | m/       |

|                                                       | Is_rng = 1                                                                                                                                                                     | 18        | m/       |

|                                                       | Is_rng = 2<br>  Is_rng = 3                                                                                                                                                     | 27<br>36  | m/<br>m/ |

| Optical Power Limit                                   | Automatic Power Control Mode Only, Apc_en = 1                                                                                                                                  |           | 1111     |

| Overpower Limit                                       | Expressed in % Over the Imd Set Point                                                                                                                                          | 50        | 9/       |

| Underpower Limit                                      | Expressed in % Under the Imd Set Point                                                                                                                                         | -50       | 9/       |

| Safety Shutdown Response Time                         | Time from the Fault Occurance to Reduction of the Laser Bias Current to 10% of Nominal                                                                                         | 100       | μ        |

| FAULT Output, Open-Drain Mode, Flt_drv_m              |                                                                                                                                                                                |           | I        |

| Output Low Voltage                                    | I <sub>OL</sub> = 3.3mA                                                                                                                                                        | 0         | .4 \     |

| Output High Leakage Current                           | V <sub>FAULT</sub> = 2.4V                                                                                                                                                      | 1         | 0 μ/     |

| FAULT Output, Open-Drain Mode with 330µJ              |                                                                                                                                                                                |           |          |

| Output Low Voltage                                    | I <sub>OL</sub> = 3.3mA                                                                                                                                                        | 0         | .4 \     |

| Output High Current                                   | V <sub>FAULT</sub> = 2.4V                                                                                                                                                      | -280      | μA       |

| FAULT Output, Open-Drain Mode with 500µJ              | A Internal Pull Up, Flt_drv_mode = 2                                                                                                                                           | -         |          |

| Output Low Voltage                                    | I <sub>OL</sub> = 3.3mA                                                                                                                                                        | 0         | .4       |

| Output High Current                                   | V <sub>FAULT</sub> = 2.4V                                                                                                                                                      | -425      | μl       |

| FAULT Output, Complementary Drive Mode,               | , Flt_drv_mode = 3                                                                                                                                                             |           |          |

| Output High Voltage                                   | $I_{OH} = -3.3 \text{mA}$                                                                                                                                                      | 2.4       | \        |

| Output Low Voltage                                    | I <sub>OL</sub> = 3.3mA                                                                                                                                                        | 0         | .4 \     |

| EN Input, Ib_gain or (Apc_gain in APC Mode            | e) = 16, lm_gain = 4, ls_rng = 0, lm_rng = 0                                                                                                                                   | •         | ·        |

| Input Low Voltage                                     |                                                                                                                                                                                | 0         | .8 \     |

| Input High Voltage                                    |                                                                                                                                                                                | 2         | 1        |

| Input Low Current                                     | En_polarity = 0 (EN Active Low), V <sub>EN</sub> = 0V                                                                                                                          | -10       | μ/       |

| Input High Current                                    | En_polarity = 0 (EN Active Low), V <sub>EN</sub> = V <sub>DD</sub>                                                                                                             | -10 to 10 | μ/       |

| Input Low Current                                     | En_polarity = 1 (EN Active High), V <sub>EN</sub> = 0V                                                                                                                         | -10 to 10 | μ/       |

| Input High Current                                    | En_polarity = 1 (EN Active High), V <sub>EN</sub> = V <sub>DD</sub>                                                                                                            | 10        | μA       |

| Transmit Enable Time                                  | Time from Active Transition on EN to 95% of Nominal Laser Power and 95% of Full Modulation. First Time Transmission is Enabled After Power On or with Rapid_restart_en = 0     | 100       | m        |

| Transmit Re-Enable Time                               | Time from Active Transition on EN to 95% of Nominal Laser Power and 95% of Full Modulation. When Transmission is Re-Enabled After the First Time and with Rapid_restart_en = 1 | 1         | m        |

| Transmit Disable Time                                 | Time from Inactive Transition on EN to 5% of Nominal Laser Power                                                                                                               | 10        | μ        |

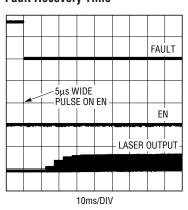

| Minimum Pulse Width Required to Clear a Latched Fault |                                                                                                                                                                                | 10        | μ        |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{DD} = V_{DD(HS)} = 3.3V$ ,  $I_S = 24mA$ ;  $I_M = 12mA$  ( $I_{MPP} = 24mA$ );  $49.9\Omega$ , 1% resistor from SRC (Pin 14) to MODA (Pin 11);  $50\Omega$ , 1% load AC coupled to MODB (Pin 10); 10nF, 10% capacitor from SRC (Pin 14) to  $V_{SS}$ ;  $CmI_{en} = 0$ ,  $Lpc_{en} = 1$ , transmitter enabled, unless otherwise noted. Test circuit in Figure 5.

| PARAMETER                                                                                                     | CONDITIONS                                                  | MIN                      | TYP  | MAX                      | UNITS |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| SCL, SDA                                                                                                      |                                                             |                          |      |                          |       |

| SCL, SDA Input Low Voltage, V <sub>IL</sub>                                                                   |                                                             | -0.5                     |      | 0.3 •<br>V <sub>DD</sub> | V     |

| SCL, SDA Input High Voltage, V <sub>IH</sub>                                                                  |                                                             | 0.7 •<br>V <sub>DD</sub> |      | V <sub>DD</sub> + 0.5    | V     |

| SCL, SDA Input Low Current (Note 21)                                                                          | V <sub>SDA</sub> , V <sub>SCL</sub> = 0.1 • V <sub>DD</sub> |                          | -100 |                          | μА    |

| SCL, SDA Input High Current (Note 21)                                                                         | V <sub>SDA</sub> , V <sub>SCL</sub> = 0.9 • V <sub>DD</sub> |                          | -100 |                          | μΑ    |

| SCL, SDA Output Low Voltage                                                                                   | I <sub>OL</sub> = 3mA                                       | 0                        |      | 0.4                      | V     |

| Hysteresis                                                                                                    |                                                             |                          | 280  |                          | mV    |

| Serial Interface Timing (Note 20)                                                                             |                                                             |                          |      |                          |       |

| SCL Clock Frequency                                                                                           |                                                             |                          |      | 100                      | kHz   |

| Hold Time (Repeated) START Condition. After This<br>Period the First Clock Pulse is Generated                 |                                                             | 4                        |      |                          | μS    |

| Low Period of the SCL Clock                                                                                   |                                                             | 4.7                      |      |                          | μS    |

| High Period of the SCL Clock                                                                                  |                                                             | 4                        |      |                          | μS    |

| Set-Up Time for a Repeated START Condition                                                                    |                                                             | 4.7                      |      |                          | μS    |

| Data Hold Time                                                                                                |                                                             | 0                        |      | 3.45                     | μS    |

| Data Set-Up Time                                                                                              |                                                             | 250                      |      |                          | ns    |

| Input Rise Time of Both SDA and SCL Signals                                                                   |                                                             |                          |      | 1000                     | ns    |

| Output Fall Time of SCL and SDA from $V_{IH(MIN)}$ to $V_{IL(MAX)}$ with a Bus Capacitance from 10pF to 400pF |                                                             |                          |      | 300                      | ns    |

| Set-Up Time for STOP Condition                                                                                |                                                             | 4                        |      |                          | μS    |

| Bus Free Time Between a STOP and START Condition                                                              |                                                             | 4.7                      |      |                          | μS    |

| Capacitive Load for Each Bus Line                                                                             |                                                             |                          |      | 400                      | pF    |

| Noise Margin at the LOW Level for Each Connected Device (Including Hysteresis)                                |                                                             | 0.1 •<br>V <sub>DD</sub> |      |                          | V     |

| Noise Margin at the HIGH Level for Each Connected Device (Including Hysteresis)                               |                                                             | 0.2 •<br>V <sub>DD</sub> |      |                          | V     |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

**Note 2:** The quiescent  $V_{DD}$  and  $V_{DD(HS)}$  currents refer to the current with zero SRC pin current (i.e., the laser is operating with zero bias current and zero modulation current). The total power supply current is the quiescent current plus the SRC pin current,  $I_S$ , plus any current sinked from  $IN^+$  and  $IN^-$ .

**Note 3:** The peak transient voltage at the IN $^+$  and IN $^-$  pins must not exceed the range of -300mV to  $V_{DD(HS)} + 300$ mV.

**Note 4:** When Cml\_en = 0 (not in CML mode), the termination is  $100\Omega$  differential with 50k common mode to  $V_{DD(HS)}/2$ .

**Note 5:** The common mode input resistance is measured relative to  $V_{DD(HS)}/2$  with the inputs tied together.

**Note 6:** When Cml\_en = 1 (CML mode), the termination is nominally  $50\Omega$  to  $V_{DD(HS)}$  on each of the IN<sup>+</sup> and IN<sup>-</sup> pins.

**Note 7:** The SRC pin current can be programmed to near zero in each range, but the recommended minimum operating level is 1/16 of full scale.

**Note 8:** The laser bias current is the average current delivered to the laser. It is equal to the SRC pin current minus the average modulation current at the MODA and MODB pins, or  $I_B = I_S - I_M$ . Full scale for the bias current therefore depends on  $I_S$ -rng and the actual modulation current.

**Note 9:** The MODA and MODB pins are connected on-chip. The modulation current refers to the sum of the currents on these pins.  $I_M$  refers to the total average current at the MODA and MODB pins.  $I_{MPP}$  refers to the total peak-to-peak modulation current at the MODA and MODB pins.  $I_{MPP}$  differs from the laser modulation current,  $I_{MOD}$ .  $I_{MPP}$  splits between the laser and the termination resistor according to  $I_{MOD} = I_{MPP} \bullet R_T/(R_T + R_{LD})$ , where  $R_T$  is the value of the termination resistor and  $R_{LD}$  is the dynamic resistance of the laser diode.

LINEAR TECHNOLOGY

# **ELECTRICAL CHARACTERISTICS**

**Note 10:** The modulation current can be programmed to near zero in each range, but the high speed performance is not guaranteed for currents less than the specified minimum.

**Note 11:** The effective resolution of the modulation current is 9 bits because the modulation servo system uses only one-half of the 10-bit ADC range.

**Note 12:** As defined in ANSI x3.230, Annex A, deterministic jitter is the peak-to-peak deviation of the 50% crossings of the modulation signal when compared to the ideal time crossings. The specification for the LTC5100 pertains to the electrical modulation signal. The K28.5 pattern is the repeating sequence 00111110101100000101.

**Note 13:** Random jitter is the standard deviation of the 50% crossings of the electrical modulation signal as measured by an oscilloscope. It is measured with a 1GHz square wave after quadrature subtraction of the random jitter of the pulse generator and oscilloscope. Peak-to-peak random jitter is defined as 14 times the RMS random jitter.

**Note 14:** The LTC5100 digitizes and servo controls the logarithm of the monitor diode current. Many of the characteristics of the APC system, such as range and resolution, are determined by the ADC.

**Note 15:** The minimum practical operating current for the monitor diode is determined by servo settling time considerations.

**Note 16:**  $I_{MD}$  must be less than  $25\mu A$ ,  $100\mu A$ ,  $400\mu A$  and  $1600\mu A$  corresponding to Imd\_rng = 0, 1, 2, 3.

**Note 17:** The temperature coefficients of the monitor diode current depend on the  $I_{MD}$  setting because of the logarithmic relationship between the set point and the monitor diode current. Imd\_nom is the digital code setting for the nominal monitor diode current. Imd\_nom lies between 0 and 1023.

**Note 18:** The ADC digitizes the average modulation current, which is 50% of the peak-to-peak current for a 50% duty cycle signal.

**Note 19:** The LTC5100 ADC digitizes the logarithm of the monitor diode current. This implies that the ADC resolution is a constant percentage of reading and that the monitor diode current is non-zero when the ADC reads zero. See the Design Notes for further information.

**Note 20:** Serial interface timing is guaranteed by design from  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

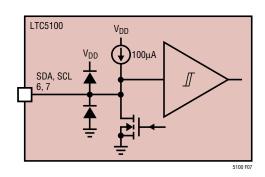

**Note 21:** The LTC5100 has  $100\mu$ A nominal pull-up current sources on the SCL and SDA pins to eliminate the need for external pull-up resistors when connected to a single EEPROM device. The LTC5100 meets the maximum rise time specification of 1000ns with external I<sup>2</sup>C bus capacitances up to 25pF. Example: 10pF EEPROM + 150mm trace ~ 25pF.

Note 22:  $V_{DD}$  and  $V_{DD(HS)}$  must be tied together on the PC board.

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD} = V_{DD(HS)} = 3.3V$ ,  $T_A = 25^{\circ}C$ ,  $Cml_en = 0$ ,  $Lpc_en = 1$ , transmitter enabled, unless otherwise noted. Test circuit shown in Figure 5.

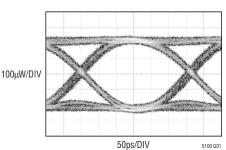

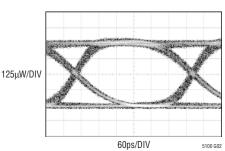

# Optical Eye Diagram at 3.2Gbps with 850nm VCSEL

EMCORE MODE LC-TOSA VCSEL 2<sup>15</sup> PRBS, 7dB EXTINCTION RATIO, 300µW AVG PWR, 2.4GHz 4TH ORDER BESSEL-THOMPSON LOWPASS FILTER

# Optical Eye Diagram at 2.5Gbps with 850nm VCSEL

EMCORE MODE LC-TOSA VCSEL 2<sup>15</sup> PRBS, 10dB EXTINCTION RATIO, 300µW AVG PWR, 1.87GHz 4TH ORDER BESSEL-THOMPSON LOWPASS FILTER

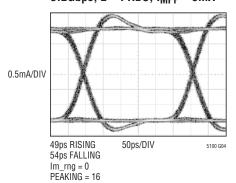

### Effect of Peaking Control on the Electrical Eye Diagram

3.2Gbps, 2<sup>23</sup> PRBS, Im\_rng = 2, I<sub>MPP</sub> = 12mA, PEAKING = 4, 8, 16, 30

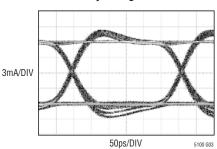

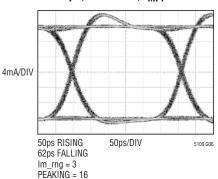

# Electrical Eye Diagram at 25°C 3.2Gbps, 2<sup>23</sup> PRBS, I<sub>MPP</sub> = 3mA

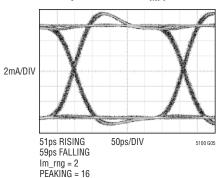

Electrical Eye Diagram at 25°C 3.2Gbps, 2<sup>23</sup> PRBS, I<sub>MPP</sub> = 12mA

Electrical Eye Diagram at 25°C 3.2Gbps, 2<sup>23</sup> PRBS, I<sub>MPP</sub> = 24mA

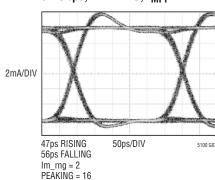

Electrical Eye Diagram at -40°C, 3.2Gbps, 2<sup>23</sup> PRBS, I<sub>MPP</sub> = 12mA

Electrical Eye Diagram at 85°C, 3.2Gbps, 2<sup>23</sup> PRBS, I<sub>MPP</sub> = 12mA

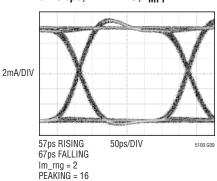

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD} = V_{DD(HS)} = 3.3V$ ,  $T_A = 25^{\circ}C$ ,  $Cml_en = 0$ ,  $Lpc_en = 1$ , transmitter enabled, unless otherwise noted. Test circuit shown in Figure 5.

# Rise and Fall Times vs I<sub>M</sub> at the Midpoint of Each Im\_rng

# Rise and Fall Times vs I<sub>MPP</sub> for Im rnq = 3

Deterministic Jitter vs I<sub>MPP</sub> for Im rna = 3

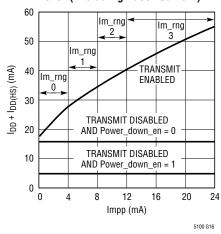

#### Supply Current vs Modulation Level (Excluding Laser Current)

**Supply Current vs Temperature**

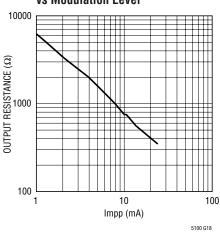

Modulator Output Resistance vs Modulation Level

# Laser Bias Current vs Temperature in CCC Mode

Monitor Diode Current vs Temperature in APC Mode

Laser Modulation Current vs Temperature, Im rng = 1

5100f

# TYPICAL PERFORMANCE CHARACTERISTICS

$V_{DD} = V_{DD(HS)} = 3.3V$ ,  $T_A = 25$ °C,  $Cml_en = 0$ ,  $Lpc_en = 1$ , transmitter enabled, unless otherwise noted.

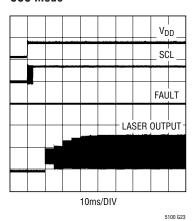

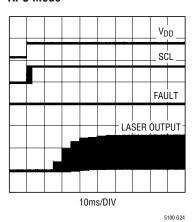

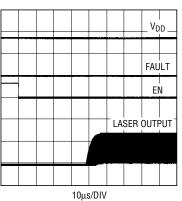

### Hot Plug with EN Active in **CCC Mode**

### Hot Plug with EN Active in **APC Mode**

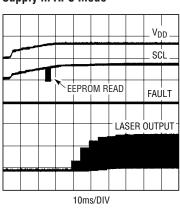

Start-Up with Slow Ramping Supply in APC Mode

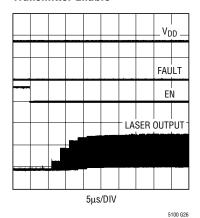

**Transmitter Enable**

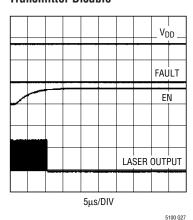

**Transmitter Disable**

Transmitter Enable, Rapid Restart

5100 G25

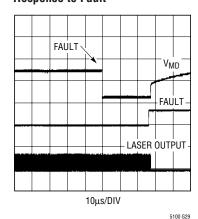

Response to Fault

**Fault Recovery Time**

5100 G30

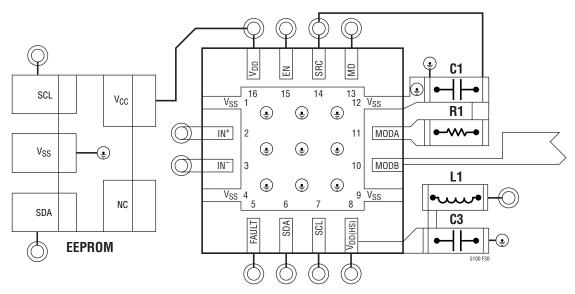

# PIN FUNCTIONS

**V<sub>SS</sub>** (**Pins 1, 4, 9, 12, 17**): Ground for Digital, Analog and High Speed Circuitry. These pins are internally connected. Connect Pins 1, 4, 9 and 12 to the ground plane with minimal trace lengths. Place a minimum of four vias (preferably nine vias) to the ground plane in the Exposed Pad area. Most of the high speed modulation current is returned through the Exposed Pad (Pin 17).

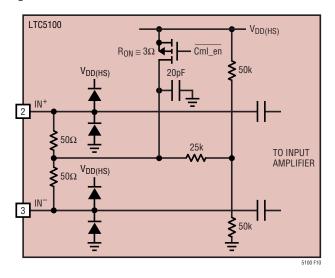

IN+, IN- (Pins 2, 3): High Speed Laser Modulation Inputs. The inputs are differential with internal termination resistors. The input amplifier is internally AC coupled. With current mode logic (CML) enabled, the inputs are independently terminated to  $V_{DD(HS)}$  with  $50\Omega$  resistors. With CML disabled, the inputs provide  $100\Omega$  differential termination and permit rail-to-rail common mode range. The input pins can be AC coupled with external capacitors. When externally AC coupled, the input pins self-bias to  $V_{DD(HS)}/2$ . The Cml\_en bit selects the termination mode.

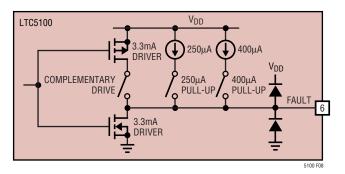

**FAULT (Pin 5):** Signals One of Five Safety Fault Conditions: laser overcurrent, overpower, underpower, power supply undervoltage and memory load error. The pin can be programmed active high or active low with the Flt\_pin\_polarity bit. The FAULT pin can be programmed to four different drive modes with the Flt\_dry\_mode bits.

**SDA**, **SCL** (**Pins 6**, **7**): Serial Interface Data and Clock Signals. The pins are open drain with a  $100\mu$ A internal pullup current. An external pull-up resistor can be added to drive larger capacitive loads.

**V**<sub>DD(HS)</sub> (**Pin 8**): Power Input for the High Speed Laser Modulation Circuitry. Filter this pin with a ferrite bead and bypass the pin directly to the ground plane with a 10nF ceramic capacitor.

MODA, MODB (Pins 11, 10): High Speed Laser Modulation Outputs. MODA and MODB are connected on-chip and driven by an open-drain output transistor. One of these pins should be connected to the laser. The other should be connected to a termination resistor. See the Applications Information section for details.

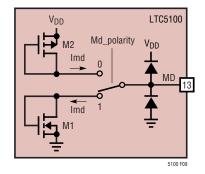

**MD** (**Pin 13**): Monitor Diode Input for Automatic Power Control of the Laser Bias Current. The MD pin allows connection to the cathode or anode of the monitor diode. The Md\_polarity bit selects the polarity of the monitor diode.

**SRC (Pin 14):** Current Source for Biasing the Laser. See the Applications Information section for details.

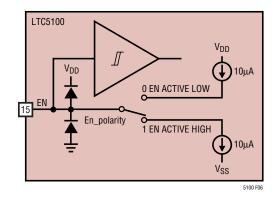

**EN (Pin 15):** Transmitter Enable and Disable Input. This input is TTL compatible and can be programmed for active high or active low operation with the En\_polarity bit. An internal  $10\mu\text{A}$  current source disables the transmitter if the EN pin becomes disconnected. This safety feature operates whether the EN pin is active high or active low.

$V_{DD}$  (Pin 16): Power Input for Digital and Low Speed Analog Circuitry. Connect this pin to  $V_{DD(HS)}$  (Pin 8) with a short trace. No bypassing is needed at the  $V_{DD}$  pin if the trace length to the  $V_{DD(HS)}$  bypass capacitor is less than 10mm long.

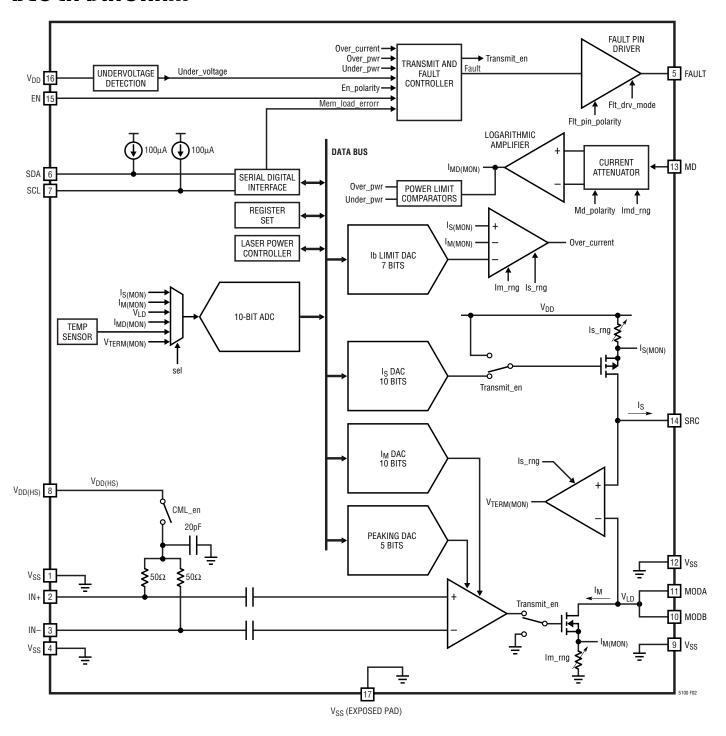

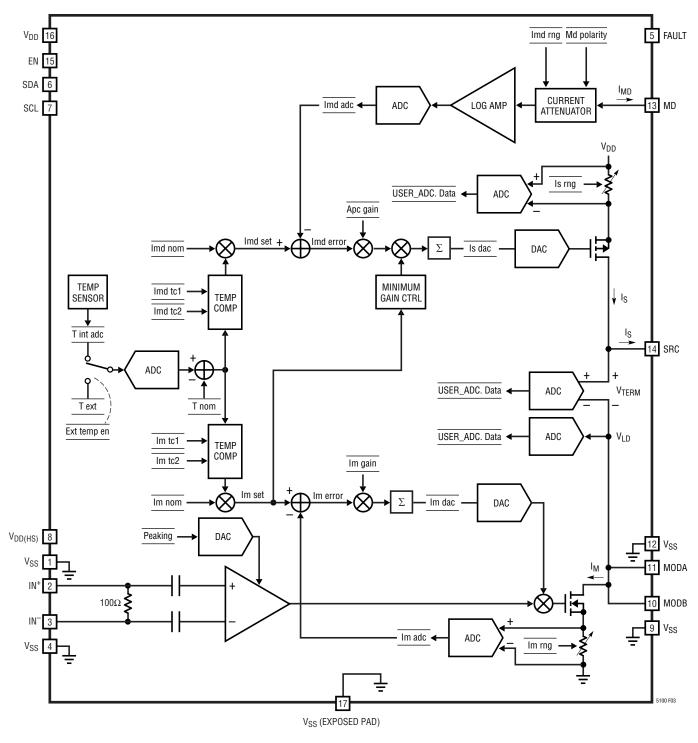

# **BLOCK DIAGRAM**

Figure 2. Block Diagram

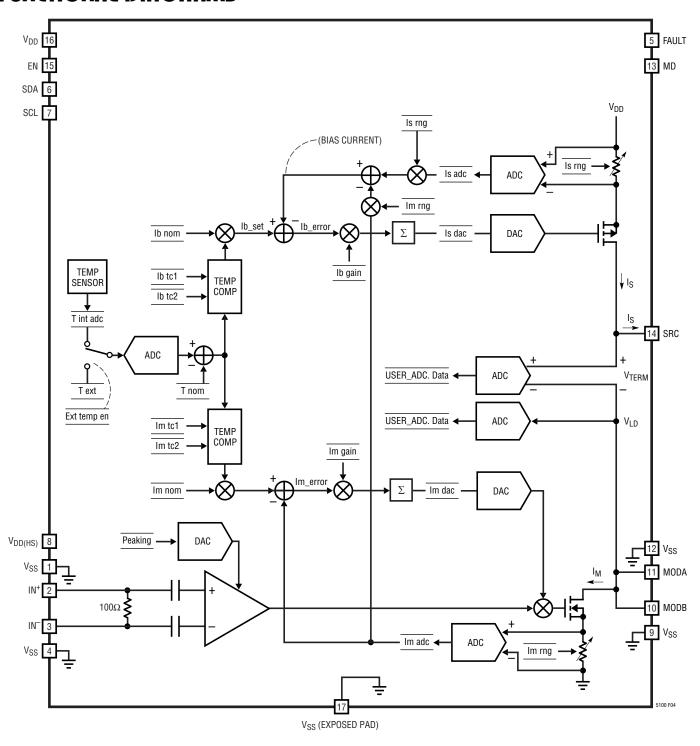

# **FUNCTIONAL DIAGRAMS**

Figure 3. Functional Diagram—Automatic Power Control Mode

# **FUNCTIONAL DIAGRAMS**

Figure 4. Functional Diagram—Constant Current Control Mode

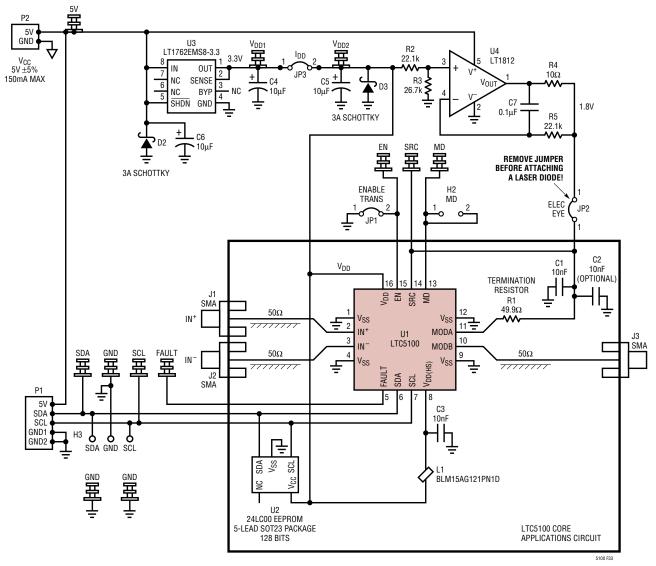

# **TEST CIRCUIT**

Figure 5. Test Circuit

# **EQUIVALENT INPUT AND OUTPUT CIRCUITS**

Figure 6. Equivalent Circuit for the EN Pin

Figure 8. Equivalent Circuit for the FAULT Pin. All Switches are Open in Open-Drain Mode

Figure 7. Equivalent Circuit for the SDA and SCL Pins

Figure 9. Equivalent Circuit for the MD Pin

# **EQUIVALENT INPUT AND OUTPUT CIRCUITS**

Figure 10. Equivalent Circuit for the IN+ and IN- Pins

Figure 11. Equivalent Circuit for the SRC, MODA and MODB Pins

## **OPERATION**

### **OVERVIEW**

(Refer to Figure 1 and the Block Diagram in Figure 2)

The LTC5100 is optimized to drive common cathode VCSELs in high speed fiber optic transceivers. The chip incorporates several features that make it very compact and easy-to-use while delivering exceptional high speed performance. Only a capacitor, a resistor and a small EEPROM (excluding laser diode and power supply filtering) are needed to build a complete fiber optic transmitter. Digital control over the I<sup>2</sup>C serial interface allows fully automated laser setup to improve manufacturing efficiency. The LTC5100's extensive set of eye safety features meet GBIC and SFF requirements but go beyond the standards with open-pin protection, redundant transmitter enable controls and other interlocks.

10-bit integrated DACs set laser bias and modulation levels, eliminating the cost and space of digital potentiometers. A multiplexed ADC allows monitoring of temperature and laser operating conditions in production or field operation. Laser bias and modulation currents are digitally temperature compensated to second order for tight control of average power and extinction ratio. The LTC5100

provides both constant current and automatic power control of the laser bias current. In automatic power control mode, special circuitry maintains constant settling time in spite of variations in the laser slope efficiency and monitor diode response characteristics.

The high speed inputs of the LTC5100 are internally terminated in  $50\Omega$  and internally AC coupled, eliminating all external components at the inputs. The modulation output is DC coupled to the laser and presents a high quality resistive drive impedance to deliver very fast and clean eye diagrams in spite of laser impedance variations. The modulation output is capable of driving significant lengths of transmission line, allowing the LTC5100 to be placed at an arbitrary distance from the laser. This feature allows for packaging flexibility within the module.

The LTC5100 minimizes electromagnetic interference (EMI) with several architectural features. The unique design of the driver output forces the high speed modulation current to circulate only in the laser and ground system. The high speed amplifier chain and the digital circuitry are internally filtered and decoupled to further reduce power supply noise generation.

LINEAR

### LASER BIAS AND MODULATION

### **Modulator Architecture**

The LTC5100 drives common cathode lasers using a method called "shunt switching". As shown in Figure 12, shunt switching involves sourcing DC current into the laser diode and shunting part of that current with a high speed current switch to produce the required modulation. The SRC pin provides the DC current and the MODA, MODB pins (which are connected on chip) provide the high speed modulation current. This technique results in a very fast, single-ended driver that confines the high speed modulation current to the laser and ground system. The LTC5100 actually uses a modified shunt switching scheme in which the source current is delivered through a "termination" resistor, R<sub>T</sub>, that is bypassed to ground with a large capacitor. The resistor brings three advantages to the modulation stage. First, it gives the modulator a precise resistive output impedance to damp ringing and absorb reflections from the laser. Second, the resistor isolates the capacitance of the SRC pin from the high speed signal path, further improving modulation speed. Third, the resistor and capacitor heavily filter the high speed output signal so that it does not modulate the power supply and cause radiation or interference. On-chip decoupling of the high speed amplifiers further reduces power supply noise generation.

Figure 12. Simplified Laser Bias and Modulation Circuit

### **Terminology and Basic Calculations**

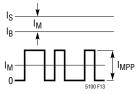

Figure 12 through Figure 16 define terminology that is used throughout this data sheet. The current delivered by the SRC pin is called  $I_S$ . The *average* modulation current delivered by the chip at the MODA, MODB pins is called  $I_M$ . The laser bias current,  $I_B$ , is defined as the average current in the laser.  $I_B$  is the difference between the source current and average modulation current.

The <code>peak-to-peak</code> modulation current delivered by the chip is called  $I_{MPP}$ .  $I_{MPP}$  is twice the value of  $I_{M}$  because the high speed data is assumed to have a 50% duty cycle. The peak-to-peak modulation current is divided between the termination resistor and the laser. The peak-to-peak modulation amplitude <code>in the laser</code> is called  $I_{MOD}$ . The relationship between  $I_{MPP}$  and  $I_{MOD}$  depends on the relative values of the termination resistor and the laser dynamic resistance.

Figure 13. Components of the LTC5100 Source and Modulation Currents (The Laser Bias Current is Also Shown)

The relationships between the source, bias, and modulation currents are as follows.

$$I_{B} = I_{S} - I_{M} \tag{1}$$

$$I_{MPP} = 2 \bullet I_{M} \tag{2}$$

$$I_{MOD} = \frac{R_T}{(R_T + R_{LD})} \bullet I_{MPP}$$

(3)

where

R<sub>T</sub> is the termination resistor value.

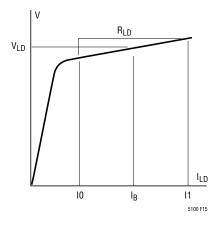

$R_{LD}$  is the dynamic resistance of the laser, defined in Figure 15.

The expression for I<sub>B</sub> in Equation 1 shows that the maximum achievable laser bias current is a function of the maximum source current, I<sub>S</sub>, and the average modulation

current,  $I_M$ . The maximum value of  $I_S$  is given in the Electrical Characteristics and the value of  $I_M$  depends on the laser characteristics and the termination resistor value.

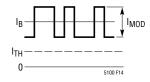

The logic "1" and "0" current levels in the laser are given by:

$$I1 = I_B + \frac{I_{MOD}}{2} \tag{4}$$

$$I0 = I_B - \frac{I_{MOD}}{2} \tag{5}$$

Figure 14. Components of the Laser Bias and Modulation Currents

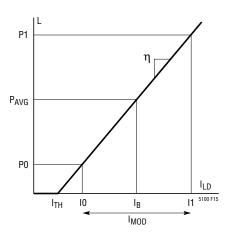

The power levels corresponding to I1 and I0 are P1 and P0, as shown in Figure 16.

$$P1 = \eta(I1 - I_{TH}) \tag{6}$$

$$P0 = \eta(I0 - I_{TH}) \tag{7}$$

where  $\eta$  is the slope efficiency and Ith is the laser threshold current, defined in Figure 16.

The average optical power and extinction ratio are given by:

$$P_{AVG} = \frac{P1 + P0}{2} \tag{8}$$

$$ER = \frac{P1}{P0} \tag{9}$$

The average voltage on the laser diode relative to ground is  $V_{LD}$  (see Figure 12 and Figure 15). The voltage on the SRC pin is:

$$V_S = V_{LD} + I_S \cdot R_T$$

$$= V_{LD} + (I_B + I_M) \cdot R_T$$

(10)

The value  $V_S$  is important because  $V_S$  must not exceed the limits given in the Electrical Characteristics.

Figure 15. Approximate VI Curve for a Laser Diode

Figure 16. Approximate LI Curve for a Laser Diode

The voltage across the termination resistor is:

$$V_{TERM} = V_{SRC} - V_{MODA}$$

$$= Is \bullet R_{T}$$

(11)

The LTC5100 can digitize the voltage across the termination resistor using the on-chip ADC, which can give a more accurate measurement of Is than that given by digitizing the current internally. See the Electrical Characteristics for details.

### **Temperature Compensation**

The LTC5100 digitally compensates the temperature drift of the laser bias current, laser modulation current and

TECHNOLOGY TECHNOLOGY

monitor photodiode current. In each case the fundamental calculation is the same. The LTC5100's digital controller multiplies the nominal value of the quantity ( $I_B$ ,  $I_M$  or  $I_{MD}$ ) by a quadratic function of temperature. Temperature measurements are supplied either by an on-chip temperature sensor or by an external microprocessor, according to the setting of Ext\_temp\_en. The general temperature compensation formula is:

$$I = I_nom \cdot (TC2 \cdot 2^{-18} \cdot \Delta T^2 + TC1 \cdot 2^{-13} \cdot \Delta T + 1)$$

(12)

where I is the digital representation of the laser bias current, modulation current or monitor diode current ( $I_B$ ,  $I_M$  or  $I_{MD}$ ).

When using the internal temperature sensor (Ext\_temp\_en = 0), the temperature measurements are taken by the onchip ADC, and  $\Delta T$  is the change in the LTC5100 die temperature relative to a user defined nominal temperature:

$$\Delta T = T \text{ int } adc - T \text{ nom}$$

(13)

When using an external temperature source (Ext\_temp\_en = 1), the temperature measurements are provided in digital form by a microprocessor or host computer and  $\Delta T$  is the change in temperature relative to a user defined nominal temperature:

$$\Delta T = T_{ext} - T_{nom}$$

(14)

T\_int\_adc, T\_ext, and T\_nom are 10-bit, unsigned numbers scaled at 0.5K/LSB. The maximum temperature that can be represented is therefore  $2^{10} \cdot 0.5^{\circ}$ K = 512°K or 239°C.

TC1 and TC2 are the first and second order temperature coefficients. They correspond to the registers Im\_tc1 and Im\_tc2 for modulation current, Ib\_tc1 and Ib\_tc2 for bias current and Imd\_tc1 and Imd\_tc2 for monitor diode current. In each case TC1 and TC2 are 8-bit signed numbers in two's complement format. The range of the temperature coefficients is therefore –128 to +127. When TC1 is multiplied by its weighting coefficient of  $2^{-13}$  in Equation 12, the effective value of the first order temperature coefficient is 122ppm/°C per LSB. The full-scale range is approximately  $\pm 15500$  ppm/°C. When TC2 is multiplied by its weighting coefficient of  $2^{-18}$  in Equation 12, the effective value of the second order temperature coefficient is 3.81ppm/°C² per LSB. The full-scale range is approximately  $\pm 484$  ppm/°C².

Note that Equation 12 is applied to the digital representation of the currents, not the physical current themselves. This is a particularly important point where monitor diode current is concerned, because the digital representation of the monitor diode current is the logarithm of the current. Thus the temperature compensation is of the logarithm of the monitor diode current and not the current itself.

### **Notation Used for Registers and Bit Fields**

The LTC5100 has a large set of registers, many of which are subdivided into fields of bits. Register names are given in all capitals (SYS\_CONFIG) and bit fields are given in mixed case (Apc\_en). For example, the bit that enables Automatic Power Control mode is contained in the System Configuration register. This bit is denoted by:

In many cases this bit field will simply be referred to as "Apc en."

The functional diagrams of Figure 3 and Figure 4 show registers and bit fields within registers between horizontal bars. For example, the "Data" field in the ADC register is shown as:

### USER\_ADC.Data

A write operation to this register is shown as:

A register read operation is shown as:

# Range Selection for the Source and Modulation Currents

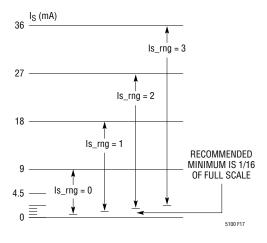

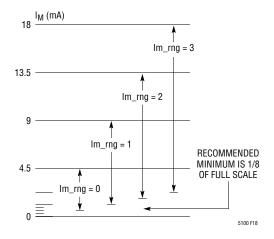

The source and modulation currents each have four ranges of operation to optimize ADC and DAC resolution as well as high frequency performance. The source current range is controlled by two bits called Is\_rng. Similarly, the modulation current range is controlled by two bits called Im\_rng. The maximum current that can be delivered is proportional to the range, so the current output is 1, 2, 3 or 4 times the typical base value of 9mA for the source current and 4.5mA for the average modulation current or 9mA peakto-peak.

5100f

Figure 17 depicts the current ranges for the source current. The guaranteed full scale is 6mA per range. The minimum operating level should be limited to 1/16 of full scale to avoid the coarse relative quantization seen in any ADC or DAC when operated at low levels. The source range, Is\_rng, should be selected as low as possible such that the source current, I<sub>S</sub>, stays within the guaranteed current limits over temperature, considering the laser temperature characteristics. From Equation 1 we can see that the source current is the sum of the laser bias and the average modulation currents:

$$I_{S} = I_{B} + I_{M} \tag{15}$$

Is\_rng should be chosen to support the total current required for laser bias and modulation, taking temperature changes in  $I_B$  and  $I_M$  into account.

Figure 17. Ranges for the Source Current

Figure 18. Ranges for the Modulation Current

Figure 18 depicts the current ranges for the average modulation current. This is the average modulation current at the MODA and MODB pins of the chip (recall that the MODA and MODB pins are connected on-chip). The peakto-peak modulation at the pins of the chip is twice the average. Guaranteed full scale is 3mA average or 6mA pp per range. The minimum operating level should be limited to 1/8 of full scale to preserve the quality of the eye diagram. Operating below 1/8 full scale causes increased overshoot and undershoot. The modulation range, Im rng, should be selected as low as possible such that the modulation current,  $I_{M}$ , stays within the guaranteed current limits over temperature. The modulation current varies over temperature to compensate the loss in slope efficiency typical of most VCSELs. Therefore, the choice of Im rng should take temperature changes into account.

### **High Speed Aspects of the Modulation Output**

The LTC5100 modulation output presents a resistive drive impedance with very low reflection coefficient. This output design suppresses ringing and reflections to maintain the quality of the eye diagrams in spite of laser impedance variations. The reflection coefficient is sufficiently low that the LTC5100 can drive the laser over an arbitrary length of transmission line, as shown in Figure 19. A well designed transmission line stretching the entire length of a typical transceiver module goes virtually unnoticed in this system. The only practical limitation on interconnect length to the laser is high frequency line loss.

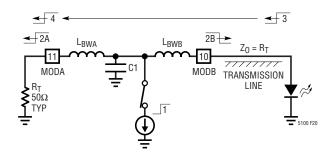

Figure 19. High Speed Details of the Modulation Output

5100f

Figure 19 shows how the LTC5100 achieves a low reflection coefficient. The unavoidable capacitance of the high speed driver transistor, bond pads and ESD protection circuitry (C1) is compensated by the inductance of the bond wires ( $L_{BWA}$  and  $L_{BWB}$ ).

The high speed behavior of the circuit in Figure 19 can be understood in greater detail by examining the simplified circuit in Figure 20. In Figure 20 the switched current source (M1 in Figure 19) launches a current step (1) toward the termination resistor (2A) and toward the transmission line (2B) connected to the laser. The laser is typically mismatched to the line impedance and reflects a portion of the incident wave (3) back toward the MODB pin. There it encounters an L-C-L structure composed of the bond wires and driver capacitance. This structure is carefully designed as a lumped element approximation to the transmission line impedance. It therefore transmits wave (3) through the IC package without reflecting energy back toward the laser. The traveling wave passes through the chip largely unimpeded (4) and is absorbed by the matched termination resistor, R<sub>T</sub>.

The matched termination is provided by the termination resistor,  $R_T$ , decoupled by capacitor  $C_T$ .  $C_T$  forms an AC short across the entire frequency range contained in the modulation data.

The termination resistor,  $R_T$ , need not be  $50\Omega$ .  $50\Omega$  is best for electrical testing because it matches the impedance of most high frequency instruments.  $R_T$  can be made smaller,  $35\Omega$ , for example, to more closely match a laser with low dynamic impedance or to allow more voltage headroom at the SRC pin. This may be necessary for lasers that run at high voltages or high bias currents.  $R_T$  can be made larger,  $70\Omega$  for example, to more closely match a laser with high

Figure 20. Wave Propagation in the Laser Interconnect

dynamic impedance or if a narrow, high impedance PC board trace is needed to connect to the laser.

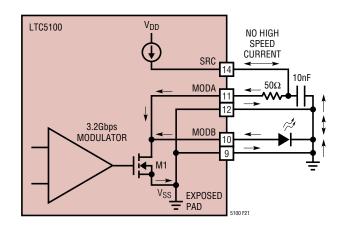

Figure 21 shows that the high speed modulation current is confined to the ground system, laser and back termination network. No high speed current circulates in the power supply where it could cause radiation and interference problems.

### **HIGH SPEED DATA INPUTS**

The high speed data inputs, IN+ and IN-, are internally terminated in  $50\Omega$  and internally AC coupled, eliminating the need for external termination resistors and AC coupling capacitors. Figure 10 shows the equivalent circuit for the high speed data pins. By default, the high speed data inputs are terminated differentially with  $100\Omega$  for compatibility with LVDS, PECL and similar differential signaling standards (Cml  $\,$  en = 0). Alternately, the inputs can be programmed for  $50\Omega$  single-ended termination to the power supply for biasing a current mode logic (CML) driver. To select CML compatibility, program Cml ento 1. Although internally AC coupled, the inputs are biased with high valued resistors (50k equivalent) to  $V_{DD(HS)}/2$ , so the LTC5100 remains compatible with external AC coupling capacitors. When externally AC coupled, the inputs selfbias to approximately  $V_{DD(HS)}/2$ .

Internal AC coupling gives the LTC5100 rail-to-rail input common mode capability. The inputs can be driven as much as 300mV beyond the rail during peak excursions. The AC coupling circuit is a distributed highpass filter with

Figure 21. High Speed Current Flow in the Modulation Output

• 51001

approximately second order characteristics. The design maximizes the flatness of the step response over extended periods, giving optimal performance during long strings of ones or zeros in the data.

# MODULATION CURRENT CONTROL IN APC AND CCC MODES

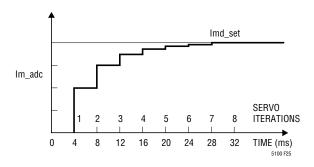

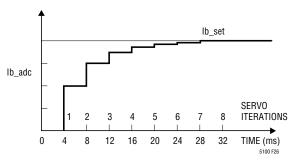

The LTC5100 controls the modulation current with a digital servo control loop using feedback from the on-chip ADC. Figure 3 and Figure 4 are Functional Diagrams of the LTC5100 operating in Automatic Power Control (APC) mode and Constant Current Control (CCC) modes, respectively. These diagrams show the organization and operation of the servo control loops for laser bias and laser modulation. Either diagram can be used to understand the modulation current control loop.

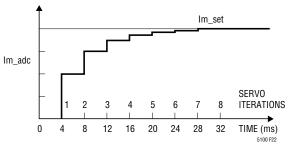

### Servo Control

The average modulation current is controlled by a digital servo loop (shown in the lower half of Figure 3). The nominal modulation current, Im nom, is multiplied by a temperature compensation factor, producing a 10-bit digital set point value. Im set. Im set is the target value for average modulation current. The ADC digitizes the average modulation current, producing a 10-bit value Im adc. The difference between the target value and the actual value produces the servo loop error signal, Im error. Im error is multiplied by a constant, Im gain, to set the loop gain. The result is integrated in a digital accumulator and applied to a 10-bit DAC, increasing or decreasing the modulation amplitude as required to drive the loop error to zero. The servo loop adjusts the modulation amplitude every four milliseconds, producing 250 servo iterations per second.

The modulation servo loop operates on the average modulation current, which is one-half of the peak-to-peak value for a 50% duty cycle signal. The analog electronics in the high speed modulator ensure that controlling the average modulation current is equivalent to controlling the peak-to-peak current.

The ADC input for average modulation current is scaled such that code 512 is the nominal full-scale value, corresponding to 4.5mA per range. Thus, if Im\_rng = 0 and Im = 4.5mA, the ADC digitizes code 512. The control system for the modulation current effectively has 9-bit resolution, because at most one-half of the 10-bit ADC range is utilized. This provision maximizes the compliance voltage range of the modulation output.

The difference equation for the modulation servo loop is:

$$Im\_adc_n = Im\_adc_{n-1} + \frac{Im\_gain}{8} \bullet Im\_error$$

(16)

=

$$Im\_adc_{n-1} + \frac{Im\_gain}{8} \bullet \left(Im\_set - Im\_adc_{n-1}\right)$$

Im\_gain is a 3-bit digital value, so the scaling factor, Im\_gain/8, takes on the discrete values 0, 1/8, 2/8, ..., 7/8. If Im\_gain = 4, then Im\_gain/8 = 0.5 and the error in the control loop is cut in half with each servo iteration. In this case the step response of the loop is given by:

$$Im\_adc_n = Im\_set \bullet \left[ 1 - \left( 1 - \frac{Im\_gain}{8} \right)^n \right]$$

(17)

The step response has the familiar exponential settling characteristic of a first order system. The step response is shown in Figure 22 for  $Im\_gain = 4$ . The remaining error is reduced by one-half with each servo iteration. In seven iterations, or about 28ms, the modulation current settles to under 1% in this example. The measured step response, including the modulation envelope, is shown in the Typical Performance Characteristics.

Figure 22. Step Response of the Average Modulation Current for Im gain = 4

TECHNOLOGY TECHNOLOGY

Reducing Im\_gain slows the settling time and increasing Im\_gain speeds the settling time. For example, with Im\_gain = 1, the residual loop error is cut by 1/8 with each servo iteration. In this case it would take 35 servo iterations (about 140ms) to settle to 1%. With Im\_gain = 7, the residual servo loop error is cut by 7/8 with each servo iteration. In this case it would take only three servo iterations (about 12ms) to settle to 1%, but the servo loop will tend to "hunt" or oscillate at a low level with such a high loop gain.

### **Temperature Compensation**

The set point value for the modulation current, Im\_set in Figure 3 and Figure 4, changes with temperature to compensate the temperature dependence of the laser diode's slope efficiency. Temperature measurements are supplied either by an on-chip temperature sensor or by an external microprocessor, according to the setting of Ext\_temp\_en. The temperature compensated expression for Im\_set is given by:

$$Im\_set = Im\_nom \bullet \begin{pmatrix} Im\_tc2 \bullet 2^{-18} \bullet \Delta T^2 \\ + Im\_tc1 \bullet 2^{-13} \bullet \Delta T + 1 \end{pmatrix} (18)$$

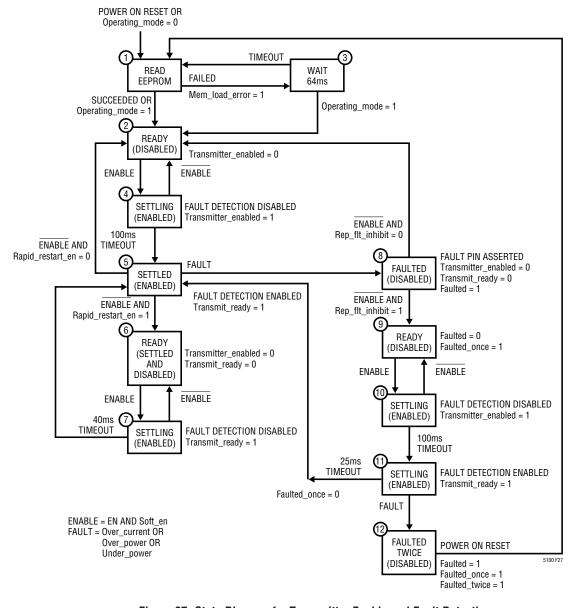

Im\_tc1 and Im\_tc2 are the first and second order temperature coefficients for the modulation current.