## 3.3V 256K × 32/36 pipeline burst synchronous SRAM

#### **Features**

- Organization: 262,144 words × 32 or 36 bits

- Fast clock speeds to 166 MHz in LVTTL/LVCMOS

- Fast clock to data access: 3.5/3.8/4.0/5.0 ns

- Fast  $\overline{OE}$  access time: 3.5/3.8/4.0/5.0 ns

- Fully synchronous register-to-register operation

- Single register "Flow-through" option

- Dual-cycle deselect

- Single-cycle deselect also available (AS7C33256PFS32A/AS7C33256PFS36A)

- Available in both 2 chip enable and 3 chip enable

- 2 CE part number is AS7C33256PFD32A2 or AS7C33256PFD36A2

- Pentium<sup>®1</sup> compatible architecture and timing

- Asynchronous output enable control

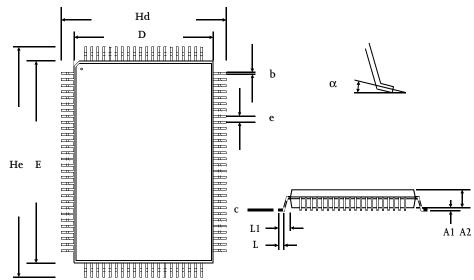

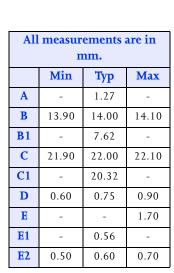

- Available in 100-pin TQFP and 119-pin BGA packages

- Byte write enables

- 3.3V core power supply

- 2.5V or 3.3V I/O operation with separate V<sub>DDO</sub>

- 30 mW typical standby power in power down mode

- NTD<sup>TM1</sup> pipeline architecture available (AS7C33256NTD32A/ AS7C33256NTD36A)

- 1 \*Pentium<sup>®</sup> is a registered trademark of Intel Corporation. NTD™ is a trademark of Alliance Semiconductor Corporation. All trademarks mentioned in this document are the property of their respective owners

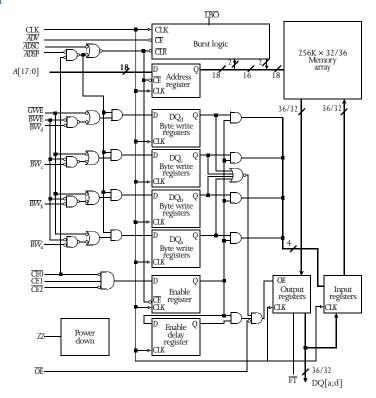

### Logic block diagram

### **Selection guide**

|                                     | -166 | -150 | -133 | -100 | Units |

|-------------------------------------|------|------|------|------|-------|

| Minimum cycle time                  | 6    | 6.6  | 7.5  | 10   | ns    |

| Maximum pipelined clock frequency   | 166  | 150  | 133  | 100  | MHz   |

| Maximum pipelined clock access time | 3.5  | 3.8  | 4    | 5    | ns    |

| Maximum operating current           | 475  | 450  | 425  | 325  | mA    |

| Maximum standby current             | 130  | 110  | 100  | 90   | mA    |

| Maximum CMOS standby current (DC)   | 30   | 30   | 30   | 30   | mA    |

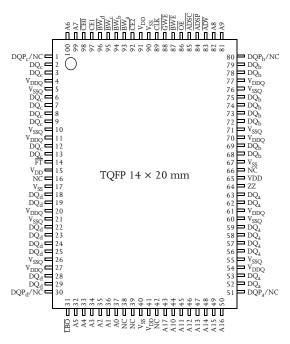

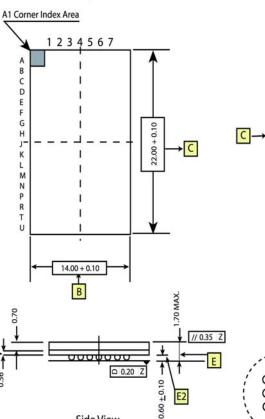

### Pin Arrangment for TQFP 3 Chip Enable

Note: Pins 1, 30, 51, 80 are NC for  $\times$ 32

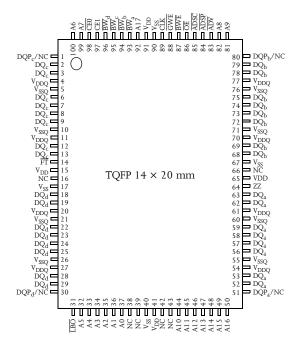

### Pin Arrangment for TQFP 2 Chip Enable

Note: Pins 1, 30, 51, 80 are NC for  $\times$ 32

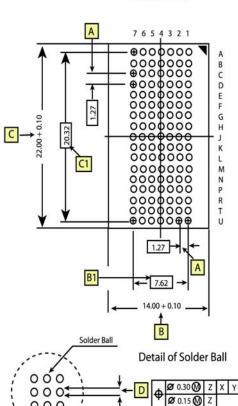

# Ball assignment for 119-ball BGA<sup>1</sup>

|   | 1                  | 2                 | 3               | 4                 | 5               | 6                 | 7                  |

|---|--------------------|-------------------|-----------------|-------------------|-----------------|-------------------|--------------------|

| A | $V_{\mathrm{DDQ}}$ | A                 | A               | ADSP              | A               | A                 | $V_{\mathrm{DDQ}}$ |

| В | NC                 | CE1               | A               | ADSC              | A               | A                 | NC                 |

| C | NC                 | A                 | A               | $V_{\mathrm{DD}}$ | A               | A                 | NC                 |

| D | $DQ_C$             | DQPc              | $V_{SS}$        | NC                | $V_{SS}$        | DQpb              | DQb                |

| E | $DQ_C$             | DQc               | V <sub>SS</sub> | CE0               | V <sub>SS</sub> | DQb               | DQb                |

| F | $V_{\mathrm{DDQ}}$ | DQc               | $V_{SS}$        | ŌĒ                | $V_{SS}$        | DQb               | $V_{\mathrm{DDQ}}$ |

| G | $DQ_C$             | DQc               | BWc             | ADV               | BWb             | DQb               | DQb                |

| H | $DQ_C$             | DQc               | V <sub>SS</sub> | GWE               | V <sub>SS</sub> | DQb               | DQb                |

| J | $V_{\mathrm{DDQ}}$ | $V_{\mathrm{DD}}$ | NC              | $V_{\mathrm{DD}}$ | NC              | $V_{\mathrm{DD}}$ | $V_{\mathrm{DDQ}}$ |

| K | DQd                | DQd               | $V_{SS}$        | CLK               | $V_{SS}$        | DQa               | DQa                |

| L | DQd                | DQd               | BWd             | NC                | BWa             | DQa               | DQa                |

| M | $V_{\mathrm{DDQ}}$ | DQd               | $V_{SS}$        | BWE               | $V_{SS}$        | DQa               | $V_{\mathrm{DDQ}}$ |

| N | DQd                | DQd               | $V_{SS}$        | $A1^2$            | $V_{SS}$        | DQa               | DQa                |

| P | DQd                | DQPd              | V <sub>SS</sub> | $A0^2$            | V <sub>SS</sub> | DQPa              | DQa                |

| R | NC                 | A                 | LBO             | $V_{\mathrm{DD}}$ | FT              | A                 | NC                 |

| T | NC                 | NC                | A               | A                 | A               | NC                | ZZ                 |

| U | $V_{\mathrm{DDQ}}$ | NC                | NC              | NC                | NC              | NC                | $V_{\mathrm{DDQ}}$ |

<sup>1</sup> Note 2D, 2P, 6D and 6P are NC for x32 2 A0 and A1 are the two least significant bits (LSB) of the address field and set the internal burst counter

#### **Functional description**

The AS7C33256PFD32A and 7C33256PFD36A are high-performance CMOS 8-Mbit synchronous Static Random Access Memory (SRAM) devices organized as 262,144 words × 32 or 36 bits, and incorporate a two-stage register-register pipeline for highest frequency on any given technology.

Timing for these devices is compatible with existing Pentium<sup>®</sup> synchronous cache specifications. This architecture is suited for ASIC, DSP (TMS320C6X), and PowerPC<sup>TM1</sup>-based systems in computing, datacomm, instrumentation, and telecommunications systems.

Fast cycle times of 6/6.6/7.5/10 ns with clock access times ( $t_{CD}$ ) of 3.5/3.8/4.0/5.0 ns enable 166, 150, 133 and 100 MHz bus frequencies. Two-chip enable and three-chip enable ( $\overline{\text{CE}}$ ) inputs permit easy memory expansion. Burst operation is initiated in one of two ways: the controller address strobe ( $\overline{\text{ADSC}}$ ), or the processor address strobe ( $\overline{\text{ADSP}}$ ). The burst advance pin ( $\overline{\text{ADV}}$ ) allows subsequent internally generated burst addresses.

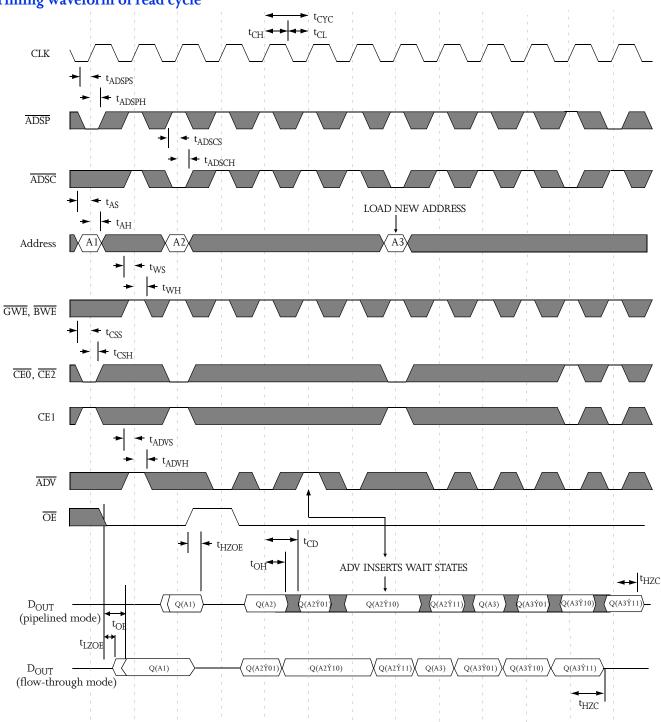

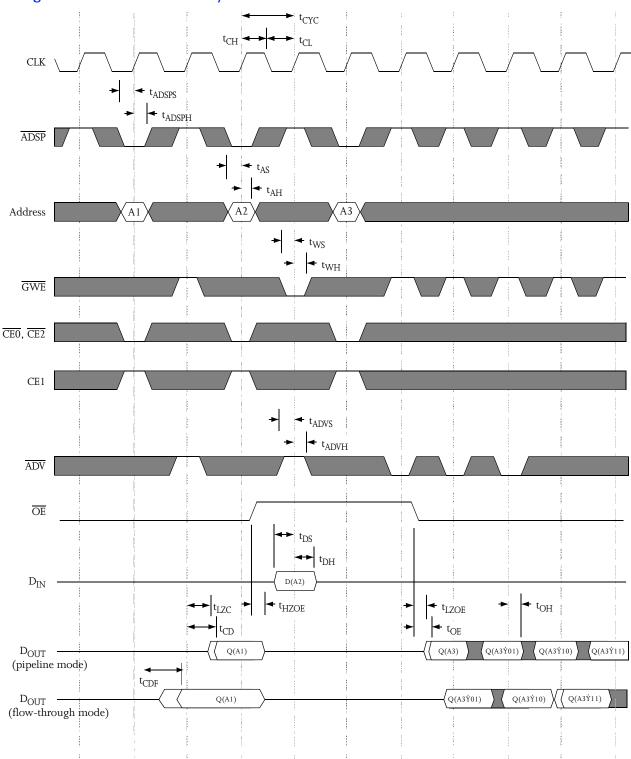

Read cycles are initiated with  $\overline{ADSP}$  (regardless of  $\overline{WE}$  and  $\overline{ADSC}$ ) using the new external address clocked into the on-chip address register when  $\overline{ADSP}$  is sampled Low, the chip enables are sampled active, and the output buffer is enabled with  $\overline{OE}$ . In a read operation the data accessed by the current address, registered in the address registers by the positive edge of CLK, are carried to the data-out registers and driven on the output pins on the next positive edge of CLK.  $\overline{ADV}$  is ignored on the clock edge that samples  $\overline{ADSP}$  asserted, but is sampled on all subsequent clock edges. Address is incremented internally for the next access of the burst when  $\overline{ADV}$  is sampled Low, and both address strobes are High. Burst mode is selectable with the  $\overline{LBO}$  input. With  $\overline{LBO}$  unconnected or driven High, burst operations use a Pentium count sequence. With  $\overline{LBO}$  driven LOW, the device uses a linear count sequence suitable for PowerPC and many other applications.

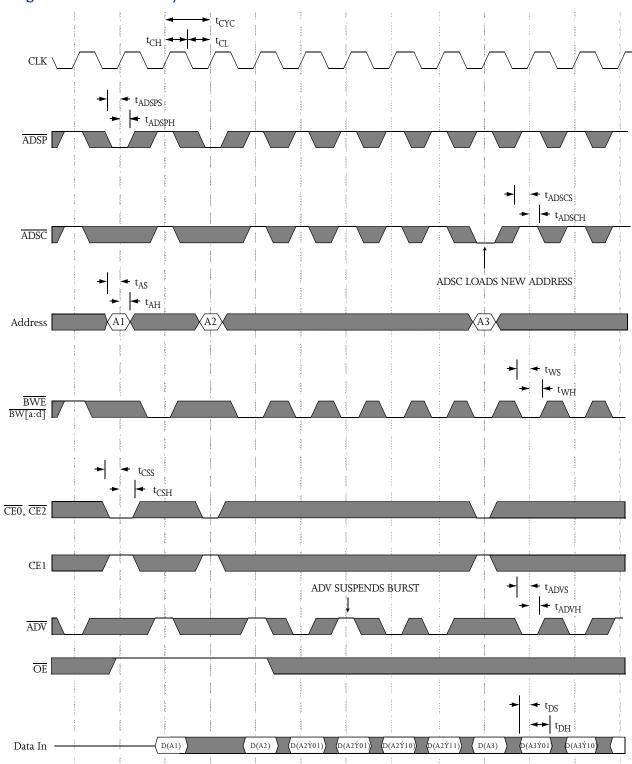

Write cycles are performed by disabling the output buffers with  $\overline{OE}$  and asserting a write command. A global write enable  $\overline{GWE}$  writes all 32/36 bits regardless of the state of individual  $\overline{BW[a:d]}$  inputs. Alternately, when  $\overline{GWE}$  is High, one or more bytes may be written by asserting  $\overline{BWE}$  and the appropriate individual byte  $\overline{BWn}$  signal(s).

$\overline{BWn}$  is ignored on the clock edge that samples  $\overline{ADSP}$  Low, but is sampled on all subsequent clock edges. Output buffers are disabled when  $\overline{BWn}$  is sampled LOW (regardless of  $\overline{OE}$ ). Data is clocked into the data input register when  $\overline{BWn}$  is sampled Low. Address is incremented internally to the next burst address if  $\overline{BWn}$  and  $\overline{ADV}$  are sampled Low.

Read or write cycles may also be initiated with ADSC instead of ADSP. The differences between cycles initiated with ADSC and ADSP follow.

- $\overline{ADSP}$  must be sampled HIGH when  $\overline{ADSC}$  is sampled LOW to initiate a cycle with  $\overline{ADSC}$ .

- WE signals are sampled on the clock edge that samples ADSC LOW (and ADSP High).

- Master chip enable CEO blocks ADSP, but not ADSC.

AS7C33256PFD32A and AS7C33256PFD36A family operates from a core 3.3V power supply. I/Os use a separate power supply that can operate at 2.5V or 3.3V. These devices are available in 100-pin  $14 \times 20$  mm TQFP package and 119-pin  $14 \times 20$  mm BGA package.

#### **Capacitance**

| Parameter         | Symbol           | Signals                  | Test conditions         | Max | Unit |

|-------------------|------------------|--------------------------|-------------------------|-----|------|

| Input capacitance | $C_{IN}$         | Address and control pins | $V_{IN} = 0V$           | 5   | pF   |

| I/O capacitance   | C <sub>I/O</sub> | I/O pins                 | $V_{IN} = V_{OUT} = 0V$ | 7   | pF   |

#### Write enable truth table (per byte)

| GWE | BWE | BWn | WEn            |

|-----|-----|-----|----------------|

| L   | X   | X   | Т              |

| Н   | L   | L   | Т              |

| Н   | Н   | X   | F*             |

| Н   | L   | Н   | F <sup>*</sup> |

$\textbf{Key:} \ X = Don't \ Care, \ L = Low, \ H = High, \ T = True, \ F = False; \ *= Valid \ read; \ n = a, \ b, \ c, \ d; \ \overline{WE}, \ \overline{WEn} = internal \ write \ signal.$

#### **Burst order table**

|                  | Inter | leaved      | Burst (     | Order |                  | Lir           | iear Bu | rst Or | der |

|------------------|-------|-------------|-------------|-------|------------------|---------------|---------|--------|-----|

|                  |       | LBC         | <b>5</b> =1 |       |                  | <u>IBO</u> =0 |         |        |     |

| Starting Address | 00    | 00 01 10 11 |             |       | Starting Address | 00            | 01      | 10     | 11  |

| First increment  | 01    | 00          | 11          | 10    | First increment  | 01            | 10      | 11     | 00  |

| Second increment | 10    | 11          | 00          | 01    | Second increment | 10            | 11      | 00     | 01  |

| Third increment  | 11    | 11 10 01 00 |             |       | Third increment  | 11            | 00      | 01     | 10  |

<sup>1</sup> PowerPC<sup>TM</sup> is a trademark International Business Machines Corporation.

## Signal descriptions

| Signal      | I/O | Properties | Description                                                                                                                                                                                                                                                                                                         |

|-------------|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | I   | CLOCK      | Clock. All inputs except $\overline{OE}$ , $\overline{FT}$ , ZZ, $\overline{LBO}$ are synchronous to this clock.                                                                                                                                                                                                    |

| A0-A17      | I   | SYNC       | Address. Sampled when all chip enables are active and ADSC or ADSP are asserted.                                                                                                                                                                                                                                    |

| DQ[a,b,c,d] | I/O | SYNC       | Data. Driven as output when the chip is enabled and $\overline{\text{OE}}$ is active.                                                                                                                                                                                                                               |

| CEO         | Ι   | SYNC       | Master chip enable. Sampled on clock edges when $\overline{ADSP}$ or $\overline{ADSC}$ is active. When $\overline{CE0}$ is inactive, $\overline{ADSP}$ is blocked. Refer to the Synchronous Truth Table for more information.                                                                                       |

| CE1, CE2    | Ι   | SYNC       | Synchronous chip enables. Active HIGH and active Low, respectively. Sampled on clock edges when $\overline{\text{ADSC}}$ is active or when $\overline{\text{CEO}}$ and $\overline{\text{ADSP}}$ are active.                                                                                                         |

| ADSP        | Ι   | SYNC       | Address strobe processor. Asserted LOW to load a new bus address or to enter standby mode.                                                                                                                                                                                                                          |

| ADSC        | I   | SYNC       | Address strobe controller. Asserted LOW to load a new address or to enter standby mode.                                                                                                                                                                                                                             |

| ADV         | I   | SYNC       | Advance. Asserted LOW to continue burst read/write.                                                                                                                                                                                                                                                                 |

| GWE         | Ι   | SYNC       | Global write enable. Asserted LOW to write all 32/36 bits. When High, $\overline{BWE}$ and $\overline{BW[a:d]}$ control write enable.                                                                                                                                                                               |

| BWE         | I   | SYNC       | Byte write enable. Asserted LOW with $\overline{\text{GWE}} = \text{HIGH}$ to enable effect of $\overline{\text{BW[a:d]}}$ inputs.                                                                                                                                                                                  |

| BW[a,b,c,d] | Ι   | SYNC       | Write enables. Used to control write of individual bytes when $\overline{GWE} = HIGH$ and $\overline{BWE} = Low$ . If any of $\overline{BW[a:d]}$ is active with $\overline{GWE} = HIGH$ and $\overline{BWE} = LOW$ the cycle is a write cycle. If all $\overline{BW[a:d]}$ are inactive the cycle is a read cycle. |

| ŌĒ          | I   | ASYNC      | Asynchronous output enable. I/O pins are driven when $\overline{\text{OE}}$ is active and the chip is in read mode.                                                                                                                                                                                                 |

| <u>I.BO</u> | I   | STATIC     | Count mode. When driven High, count sequence follows Intel XOR convention. When driven Low, count sequence follows linear convention. This signal is internally pulled High.                                                                                                                                        |

| FT          | Ι   | STATIC     | Flow-through mode. When low, enables single register flow-through mode. Connect to $V_{\rm DD}$ if unused or for pipelined operation.                                                                                                                                                                               |

| ZZ          | I   | ASYNC      | Snooze. Places device in low power mode; data is retained. Connect to GND if unused.                                                                                                                                                                                                                                |

## **Absolute maximum ratings**

| Parameter                                  | Symbol                             | Min  | Max                 | Unit |

|--------------------------------------------|------------------------------------|------|---------------------|------|

| Power supply voltage relative to GND       | V <sub>DD</sub> , V <sub>DDQ</sub> | -0.5 | +4.6                | V    |

| Input voltage relative to GND (input pins) | V <sub>IN</sub>                    | -0.5 | $V_{DD} + 0.5$      | V    |

| Input voltage relative to GND (I/O pins)   | V <sub>IN</sub>                    | -0.5 | $V_{\rm DDQ} + 0.5$ | V    |

| Power dissipation                          | $P_{\mathrm{D}}$                   | _    | 1.8                 | W    |

| DC output current                          | I <sub>OUT</sub>                   | _    | 50                  | mA   |

| Storage temperature (plastic)              | T <sub>stg</sub>                   | -65  | +150                | °C   |

| Temperature under bias                     | T <sub>bias</sub>                  | -65  | +135                | °C   |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect reliability.

### Synchronous truth table

| CE0 | CE1 | CE2 | ADSP | ADSC | ADV | WEn <sup>1</sup> | <del>OE</del> | Address accessed | CLK    | Operation     | DQ                |

|-----|-----|-----|------|------|-----|------------------|---------------|------------------|--------|---------------|-------------------|

| Н   | X   | X   | X    | L    | X   | X                | X             | NA               | L to H | Deselect      | Hi–Z              |

| L   | L   | X   | L    | X    | X   | X                | X             | NA               | L to H | Deselect      | Hi–Z              |

| L   | L   | X   | Н    | L    | X   | X                | X             | NA               | L to H | Deselect      | Hi–Z              |

| L   | X   | Н   | L    | X    | X   | X                | X             | NA               | L to H | Deselect      | Hi–Z              |

| L   | X   | Н   | Н    | L    | X   | X                | X             | NA               | L to H | Deselect      | Hi–Z              |

| L   | Н   | L   | L    | X    | X   | X                | L             | External         | L to H | Begin read    | Hi–Z <sup>2</sup> |

| L   | Н   | L   | L    | X    | X   | X                | Н             | External         | L to H | Begin read    | Hi–Z              |

| L   | Н   | L   | Н    | L    | X   | F                | L             | External         | L to H | Begin read    | Hi–Z <sup>2</sup> |

| L   | Н   | L   | Н    | L    | X   | F                | Н             | External         | L to H | Begin read    | Hi–Z              |

| X   | X   | X   | Н    | Н    | L   | F                | L             | Next             | L to H | Cont. read    | Q                 |

| X   | X   | X   | Н    | Н    | L   | F                | Н             | Next             | L to H | Cont. read    | Hi–Z              |

| X   | X   | X   | Н    | Н    | Н   | F                | L             | Current          | L to H | Suspend read  | Q                 |

| X   | X   | X   | Н    | Н    | Н   | F                | Н             | Current          | L to H | Suspend read  | Hi–Z              |

| Н   | X   | X   | X    | Н    | L   | F                | L             | Next             | L to H | Cont. read    | Q                 |

| Н   | X   | X   | X    | Н    | L   | F                | Н             | Next             | L to H | Cont. read    | Hi–Z              |

| Н   | X   | X   | X    | Н    | Н   | F                | L             | Current          | L to H | Suspend read  | Q                 |

| Н   | X   | X   | X    | Н    | Н   | F                | Н             | Current          | L to H | Suspend read  | Hi–Z              |

| L   | Н   | L   | Н    | L    | X   | T                | X             | External         | L to H | Begin write   | $D^3$             |

| X   | X   | X   | Н    | Н    | L   | T                | X             | Next             | L to H | Cont. write   | D                 |

| Н   | X   | X   | X    | Н    | L   | T                | X             | Next             | L to H | Cont. write   | D                 |

| X   | X   | X   | Н    | Н    | Н   | T                | X             | Current          | L to H | Suspend write | D                 |

| Н   | X   | X   | X    | Н    | Н   | T                | X             | Current          | L to H | Suspend write | D                 |

$<sup>{\</sup>bf 1}$  See "Write enable truth table" on page 4 for more information.

Key: X = Don't Care, L = Low, H = High.

## **Recommended operating conditions**

| Parameter                   |              | Symbol             | Min        | Nominal | Max                | Unit |

|-----------------------------|--------------|--------------------|------------|---------|--------------------|------|

| Supply voltage              |              | $V_{\mathrm{DD}}$  | 3.135      | 3.3     | 3.465              | V    |

| Supply voltage              |              | $V_{SS}$           | 0.0        | 0.0     | 0.0                | , ,  |

| 3.3V I/O supply             |              | $V_{\mathrm{DDQ}}$ | 3.135      | 3.3     | 3.465              | V    |

| voltage                     |              | $V_{SSQ}$          | 0.0        | 0.0     | 0.0                | , ,  |

| 2.5V I/O supply             |              | $V_{\mathrm{DDQ}}$ | 2.35       | 2.5     | 2.9                | V    |

| voltage                     |              | $V_{SSQ}$          | 0.0        | 0.0     | 0.0                | ,    |

|                             | Address and  | $V_{\mathrm{IH}}$  | 2.0        | 1       | $V_{\rm DD} + 0.3$ | V    |

| Input voltages <sup>1</sup> | control pins | $V_{\mathrm{IL}}$  | $-0.5^{2}$ | 1       | 0.8                | ,    |

| input voitages              | I/O pins     | $V_{\mathrm{IH}}$  | 2.0        | 1       | $V_{DDQ} + 0.3$    | V    |

|                             | 17 O pinis   | $V_{\mathrm{IL}}$  | $-0.5^{2}$ | 1       | 0.8                | ,    |

| Ambient operating temp      | perature     | $T_{A}$            | 0          | _       | 70                 | °C   |

<sup>1</sup> Input voltage ranges apply to 3.3V I/O operation. For 2.5V I/O operation, contact factory for input specifications. 2  $V_{\rm IL}$  min = -2.0V for pulse width less than 0.2  $\times$   $t_{\rm RC}$ .

<sup>2</sup> Q in "flow through" mode

<sup>3</sup> For WRITE operation following a READ,  $\overline{\text{OE}}$  must be HIGH before the input data set up time and held HIGH throughout the input hold time.

P. 7 of 14

## **TQFP** thermal resistance

| Description                                               | Conditions                                                                                   |         | Symbol             | Typical |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|---------|--------------------|---------|

| Thermal resistance                                        | Tark and distance Callery standard tark mostly along                                         | 1–layer | $	heta_{	ext{JA}}$ | 40      |

| (junction to ambient) <sup>1</sup>                        | Test conditions follow standard test methods and procedures for measuring thermal impedance, | 4–layer | $	heta_{	ext{JA}}$ | 22      |

| Thermal resistance (junction to top of case) <sup>1</sup> | per EIA/JESD51                                                                               |         | $\theta_{JC}$      | 8       |

<sup>1</sup> This parameter is sampled.

#### **DC** electrical characteristics

|                                       |                                             |                                                                                                                                                                                                          | -1  | 66  | -1  | 50  | -1  | 33  | -1  | 00  |      |  |

|---------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|--|

| <b>Parameter</b>                      | Symbol                                      | <b>Test conditions</b>                                                                                                                                                                                   | Min | Max | Min | Max | Min | Max | Min | Max | Unit |  |

| Input leakage<br>current <sup>1</sup> | $ \mathrm{I}_{\mathrm{LI}} $                | $V_{\mathrm{DD}} = \mathrm{Max}$ , $V_{\mathrm{IN}} = \mathrm{GND}$ to $V_{\mathrm{DD}}$                                                                                                                 | -   | 2   | -   | 2   | -   | 2   | -   | 2   | μΑ   |  |

| Output leakage<br>current             | $ I_{LO} $                                  | $\overline{	ext{OE}} \ge 	ext{V}_{	ext{IH}}, 	ext{V}_{	ext{DD}} = 	ext{Max}, \\ 	ext{V}_{	ext{OUT}} = 	ext{GND to V}_{	ext{DD}}$                                                                         | -   | 2   | _   | 2   |     | 2   | -   | 2   | μА   |  |

| Operating power supply current        | I <sub>CC</sub> <sup>2</sup> (Pipelined)    | $\overline{\text{CE0}} = \text{V}_{\text{IL}}, \text{CE1} = \text{V}_{\text{IH}}, \overline{\text{CE2}} = \text{V}_{\text{IL}},$ $\text{f} = \text{f}_{\text{Max}}, \text{I}_{\text{OUT}} = \text{0 mA}$ | -   | 475 | _   | 450 | 1   | 425 | ı   | 325 | mA   |  |

| Operating power supply current        | I <sub>CC</sub> <sup>2</sup> (Flow-through) | $\overline{\text{CE0}} = \text{V}_{\text{IL}}, \text{CE1} = \text{V}_{\text{IH}}, \overline{\text{CE2}} = \text{V}_{\text{IL}},$ $\text{f} = \text{f}_{\text{Max}}, \text{I}_{\text{OUT}} = \text{0 mA}$ | _   | 325 | ı   | 325 | Ι   | 300 | I   | 300 | mA   |  |

|                                       | $I_{SB}$                                    | Deselected, $f = f_{Max}$ , $ZZ \le V_{IL}$                                                                                                                                                              | _   | 130 | _   | 110 | ı   | 100 | ı   | 90  |      |  |

| Standby power supply current          | $I_{SB1}$                                   | Deselected, f = 0, ZZ $\leq$ 0.2V all $V_{IN} \leq$ 0.2V or $\geq$ $V_{DD} - 0.2V$                                                                                                                       | _   | 30  | -   | 30  | -   | 30  | -   | 30  | mA   |  |

| зарріу сштен                          | $I_{SB2}$                                   | Deselected, $f = f_{Max}$ , $ZZ \ge V_{DD} - 0.2V$<br>All $V_{IN} \le V_{IL}$ or $\ge V_{IH}$                                                                                                            | -   | 30  | _   | 30  | 1   | 30  | ı   | 30  |      |  |

| Output voltage                        | $V_{OL}$                                    | $I_{OL} = 8 \text{ mA}, V_{DDQ} = 3.465 \text{V}$                                                                                                                                                        | _   | 0.4 | _   | 0.4 | _   | 0.4 | _   | 0.4 | v    |  |

| Output voitage                        | V <sub>OH</sub>                             | $I_{OH} = -4 \text{ mA}, V_{DDQ} = 3.135 \text{V}$                                                                                                                                                       | 2.4 | _   | 2.4 | _   | 2.4 | _   | 2.4 | _   | •    |  |

<sup>1</sup>  $\overline{LBO}$  pin has an internal pull-up and input leakage =  $\pm 10~\mu A$ .

## DC electrical characteristics for 2.5V I/O operation

|                           |                 |                                                                                                                                             | -166 |     | -150 |     | -133 |     | -100 |     |      |

|---------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-----|------|-----|------|-----|------|

| Parameter                 | Symbol          | <b>Test conditions</b>                                                                                                                      | Min  | Max | Min  | Max | Min  | Max | Min  | Max | Unit |

| Output leakage<br>current | I <sub>LO</sub> | $\overline{\text{OE}} \ge \text{V}_{\text{IH}},  \text{V}_{\text{DD}} = \text{Max}, \\ \text{V}_{\text{OUT}} = \text{GND to V}_{\text{DD}}$ | -1   | 1   | -1   | 1   | -1   | 1   | -1   | 1   | μΑ   |

| Output voltage            | $V_{OL}$        | $I_{OL} = 2 \text{ mA}, V_{DDQ} = 2.65 V$                                                                                                   | -    | 0.7 | _    | 0.7 | -    | 0.7 | _    | 0.7 | V    |

| Output voltage            | V <sub>OH</sub> | $I_{OH} = -2 \text{ mA}, V_{DDQ} = 2.35 \text{V}$                                                                                           | 1.7  | _   | 1.7  | _   | 1.7  | _   | 1.7  | ı   | •    |

<sup>2</sup>  $I_{CC}$  given with no output loading.  $I_{CC}$  increases with faster cycles times and greater output loading.

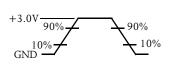

# Timing characteristics over operating range

| S control of the cont | -166                 |     | -150 |     | -133 |     | -100 |     |     |      |                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|-----|------|-----|------|-----|-----|------|--------------------|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Symbol               | Min | Max  | Min | Max  | Min | Max  | Min | Max | Unit | Notes <sup>1</sup> |

| Clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $f_{Max}$            | _   | 166  | _   | 150  | _   | 133  | _   | 100 | MHz  |                    |

| Cycle time (pipelined mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>CYC</sub>     | 6   | _    | 6.6 | _    | 7.5 | _    | 10  | _   | ns   |                    |

| Cycle time (flow-through mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t <sub>CYCF</sub>    | 10  | _    | 10  | _    | 12  | _    | 12  | _   | ns   |                    |

| Clock access time (pipelined mode)- 3.3V VDDQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t <sub>CD</sub> 3.3V | =   | 3.5  | -   | 3.8  | =   | 4.0  | -   | 5.0 | ns   |                    |

| Clock access time (pipelined mode)- 2.5V VDDQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | t <sub>CD</sub> 2.5V | -   | 4.0  | -   | 4.3  | -   | 4.5  | -   | 5.0 | ns   |                    |

| Clock access time (flow-through mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t <sub>CDF</sub>     | _   | 9    | _   | 10   | _   | 10   | _   | 12  | ns   |                    |

| Output enable LOW to data valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>OE</sub>      | _   | 3.5  | _   | 3.8  | _   | 4.0  | _   | 5.0 | ns   |                    |

| Clock HIGH to output Low Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>LZC</sub>     | 0   | _    | 0   | _    | 0   | _    | 0   | _   | ns   | 2,3,4              |

| Data output invalid from clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>OH</sub>      | 1.5 | _    | 1.5 | _    | 1.5 | _    | 1.5 | _   | ns   | 2                  |

| Output enable LOW to output Low Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | t <sub>LZOE</sub>    | 0   | _    | 0   | _    | 0   | _    | 0   | _   | ns   | 2,3,4              |

| Output enable HIGH to output High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>HZOE</sub>    | _   | 3.5  | _   | 3.8  | _   | 4.0  | _   | 4.5 | ns   | 2,3,4              |

| Clock HIGH to output High Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>HZC</sub>     | _   | 3.5  | _   | 3.8  | _   | 4.0  | _   | 5.0 | ns   | 2,3,4              |

| Output enable HIGH to invalid output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t <sub>OHOE</sub>    | 0   | _    | 0   | _    | 0   | _    | 0   | _   | ns   |                    |

| Clock HIGH pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | t <sub>CH</sub>      | 2.4 | _    | 2.5 | _    | 2.5 | _    | 3.5 | _   | ns   | 5                  |

| Clock LOW pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $t_{CL}$             | 2.4 | _    | 2.5 | _    | 2.5 | _    | 3.5 | _   | ns   | 5                  |

| Address setup to clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t <sub>AS</sub>      | 1.5 | _    | 1.5 | _    | 1.5 | _    | 2.0 | _   | ns   | 6                  |

| Data setup to clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $t_{DS}$             | 1.5 | _    | 1.5 | _    | 1.5 | _    | 2.0 | _   | ns   | 6                  |

| Write setup to clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t <sub>WS</sub>      | 1.5 | _    | 1.5 | _    | 1.5 | _    | 2.0 | _   | ns   | 6,7                |

| Chip select setup to clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | t <sub>CSS</sub>     | 1.5 | _    | 1.5 | _    | 1.5 | _    | 2.0 | _   | ns   | 6,8                |

| Address hold from clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>AH</sub>      | 0.5 | -    | 0.5 | _    | 0.5 | _    | 0.5 | _   | ns   | 6                  |