### **FEATURES**

- New proprietary crystal oscillator circuitry provides low REFOUT jitter, excellent duty cycle

- Power-on delay feature ensures full VCC is reached prior to output clocks

- 3.3V and 5V operation supported including the VRE (Voltage Regulated Extended) specification for Pentium™ processor

- Pin and function compatible with w48C54/w48C55 and AV9154/AV9155

- Integral PLL loop filter components ensures stable PLL operation in noisy system environment

- Smooth, glitch free frequency transition of CPU and 2XCPU outputs

- Compatible with Intel x86 and other high performance processors

- Up to eight clock outputs for CPU and peripherals

- Supports Green PC and notebook designs

- Custom options available with metal layer change

- High performance, low power CMOS

### **GENERAL DESCRIPTION**

The w48C54A and w48C55A are low cost, general purpose clock generator ICs. The standard device options described in this document are designed for PC motherboard applications. Backward compatible with the w48C54 and w48C55, these dual-PLL clock devices incorporate an improved crystal oscillator as well as other refinements. On-chip loop filter components ensure stable operation even with the noise typical of a digital system. Device functionality, including input/output options and frequency selection is determined by a single metal mask that allows quick-turn customization capability. Both 3.3 and 5 Volt operation is supported.

The improved crystal oscillator of the **W**48C54A and **W**48C55A most notably provides improved duty cycle at the 14.318 MHz output(s). With this new design, duty cycle is not affected by varying operating conditions such as with the addition of external crystal load capacitors. Clock jitter from the 14.318 MHz output(s) is also improved, as is the crystal oscillation frequency accuracy.

Like the **W**48C54 and **W**48C55, the **W**48C54A and **W**48C55A have a unique power-on delay circuit. This feature allows compatiblility with certain microprocessor devices that cannot withstand clock input toggling until full supply voltage is reached. Upon application of power to the VCC pins, the **W**48C54A/55A output clocks are delayed (held low) for approximately 15 msec, after which they assume normal operation.

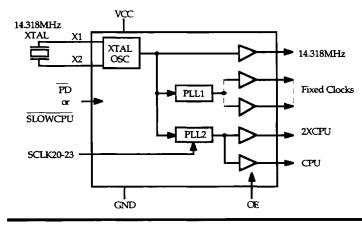

## FUNCTIONAL BLOCK DIAGRAM: w48C54A/55A

### **FUNCTIONAL DESCRIPTION**

The Functional Block Diagram shows the reference clock source can be (1) a 14.318MHz crystal connected across the X1 and X2 input pins, or (2) an input clock connected to the X1 input pin with a frequency of 14.318MHz. In the latter case, the X2 pin is left open. With either source as reference, both the w48C54A and w48C55A generate all necessary clocks at their respective frequencies to drive the CPUCLK (including 2XCPUCLK frequency), keyboard (KBCLK), local bus (BUSCLK), floppy disk (FDCLK) and communications (COMMCLK) clocks. To provide the broadest possible range of frequencies typically required for CPU mother-board designs, the target frequencies can be selected via the SCLK20-SCLK23 inputs. Consult the appropriate tables for the clock selection range. In addition, the w48C54A has one rebuffered reference clock output (14.318MHz) while the w48C55A has two. Quite often, these rebuffered reference clocks (14.318MHz) are used as the sources for the video adapter (as well as video controller designed right on the motherboard) or other function, eliminating the need for extra crystals.

Both the **W**48C54A and **W**48C55A offer smooth, glitch-free transitions when changing CPUCLK/ 2XCPUCLK output frequency. This feature can best be used by power management systems where it is frequently necessary to slow down the clock to conserve power. By controlling the rate of frequency transition, both devices are designed to be compatible with Intel cycle to cycle processor timing specifications. For w48C54A and w48C55A devices which have eight CPUCLK/2XCPUCLK output frequency selections (three select pins), smooth transition occurs with any new frequency selection. However, for w48C54A and w48C55A devices with sixteen CPUCLK/2XCPUCLK selections (four select pins), smooth transition occurs only when changing frequencies among the top eight table selections or among the bottom eight table selections (in other words, SCLK23 must remain low or high during frequency change). Jumping between the top and bottom eight table selections will result in a non-smooth frequency transition (this also is true with the AV9154 and To facilitate automated board level testing, the **W**48C55A and some **W**48C54A have an active high OE (Output Enable) input pin. When pin OE is forced low, all clock outputs are tri-stated. Most logic input pins of the **W**48C54A and **W**48C55A, such as Select, OE and PD, have an internal pull-up resistor. These unused inputs can either be connected to Ground, VCC or left unconnected (an unconnected input pin implementing an internal pull-up resistor will assume a logic high state due to the pull-up resistor).

While featured in all versions of the w48C55A, power down capability is available in selected versions of the w48C54A. When PD is active (low), the device is placed in a standby mode during which power dissipation is at its minimum; all clock outputs are forced low. Similarly, complete device power down is available for w48C54A-04 and w48C54A-63. Partial power down is available for the w48C54A-16. When PDREF and PDCPU of w48C54A-16 are active (high), the reference clock (14.318MHz) and the CPUCLK will be turned off and forced low, respectively.

IC WORKS W48C54A/55A

# PIN DESCRIPTIONS: W48C54A and W48C55A

| Pin Name        | I/O | Description                                                                                           |

|-----------------|-----|-------------------------------------------------------------------------------------------------------|

|                 |     |                                                                                                       |

| 1.843 MHz       | 0   | Fixed 1.843MHz output for serial I/O clock application                                                |

| 8MHz            | 0   | Fixed 8MHz output for keyboard clock application                                                      |

| 12MHz           | 0   | Fixed 12MHz output for keyboard clock application                                                     |

| 14.318MHz       | 0   | Fixed 14.318MHz output for various motherboard functions from 14.318MHz                               |

|                 |     | crystal or external clock output                                                                      |

| 15MHz           | 0   | Fixed 15MHz output for keyboard or bus clock application                                              |

| 16MHz           | 0   | Fixed 16MHz output for APIC or bus clock application                                                  |

| 24MHz           | 0   | Fixed 24MHz output for floppy drive or super I/O applications                                         |

| 32MHz           | 0   | Fixed 32MHz output for ISA or PCI bus clock applications                                              |

| 40MHz           | 0   | Fixed 40MHz output for SCSI clock applications                                                        |

| 2XCPUCLK        | 0   | Clock Output (refer to Frequency Selection Table )                                                    |

| AGND            | -   | Analog ground connection                                                                              |

| CPUCLK          | 0   | Clock Output (refer to Frequency Selection Table )                                                    |

| SCLK20          | I   | Frequency Selection input, LSB                                                                        |

| SCLK21          | I   | Frequency Selection input                                                                             |

| SCLK22          | I   | Frequency Selection input                                                                             |

| SCLK23          | I   | Frequency Selection input, MSB                                                                        |

| GND             | -   | Ground connection                                                                                     |

| OE              | I   | Output Enable, puts all outputs in high impedance state when low                                      |

| SLOWCPU         | I   | Slow CPU input, slows 2XCPUCLK output to 16MHz and CPUCLK output to 8MHz when low                     |

| $\overline{PD}$ | I   | Power Down input, puts <b>W</b> 48C54A/55A in power down mode when low                                |

| PDCPU           | I   | Power Down CPU Clock circuit; when high, puts CPU PLL in power down mode and forces CPUCLK output low |

| PDREF           | I   | Power Down REF; when high, forces 14.318 MHz output low                                               |

| $v_{CC}$        | _   | Power supply connection                                                                               |

| X1/ICLK         | I   | Crystal connection or external clock frequency input                                                  |

| X2              | 0   | Crystal connection, leave unconnected when using external clock                                       |

|                 |     |                                                                                                       |

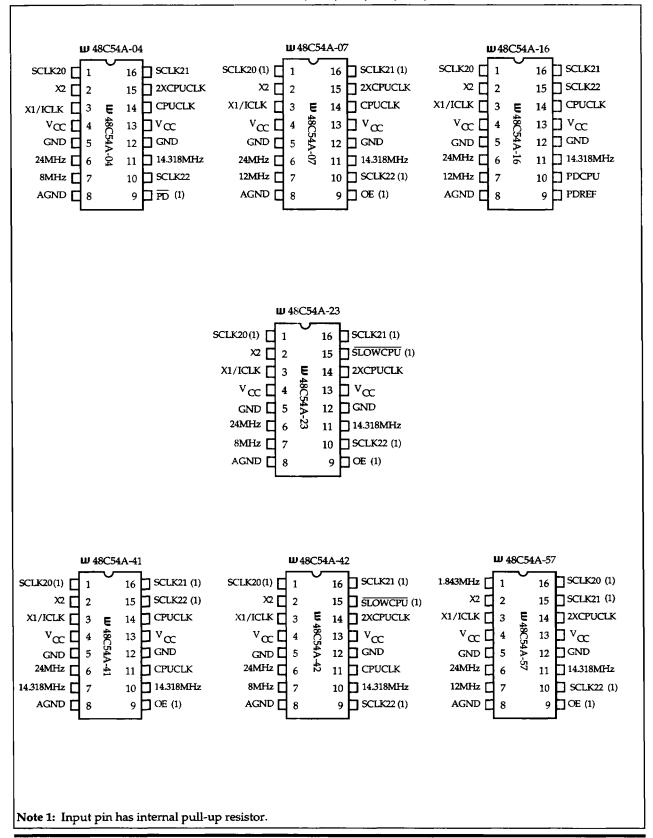

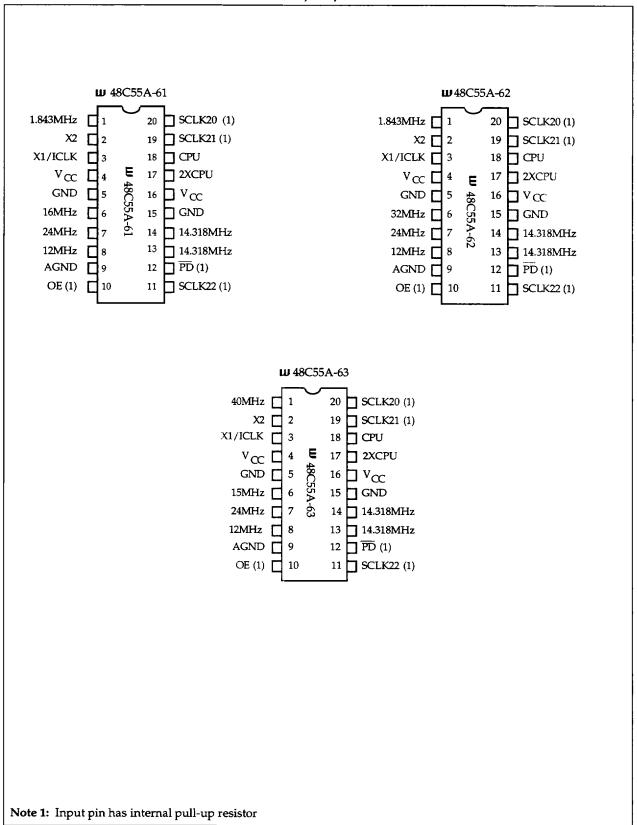

# PIN CONFIGURATIONS: w48C54A-04, -07, -16, -23, -41, -42 and -57

## PIN CONFIGURATIONS: w48C55A -61, -62, and -63

IC WORKS W48C54A/55A

FREQUENCY SELECTION FOR w48C54A (using 14.318MHz input; 3.3V and 5.0V)

| SCLK    | -04       | 4        | -0       | 7        | -16        | -23      | -41    | -42      | <u> </u>   | -57      |

|---------|-----------|----------|----------|----------|------------|----------|--------|----------|------------|----------|

| (23-20) | 2XCPUCLK  | CPUCLK   | 2XCPUCLK | CPUCLK   | CPUCLK     | 2XCPUCLK | CPUOUT | 2XCPUCLK | CPUCLK     | 2XCPUCLK |

| 0       | 100 -(NOT | E 1)- 50 | 100-(NO  | E 1)- 50 | 16         | 16       | 8      | 16       | 8          | 75       |

| 1       | 80        | 40       | 80       | 40       | 20         | 40       | 8      | 40       | 20         | 32       |

| 2       | 66.6      | 33.3     | 66.6     | 33.3     | 25         | 33.3     | 8      | 33.3     | 16.7       | 60       |

| 3       | 50        | 25       | 50       | 25       | 33.3       | 25       | 16     | 25       | 12.5       | 40       |

| 4       | 40        | 20       | 40       | 20       | <b>4</b> 0 | 60       | 25     | 60       | <b>3</b> 0 | 50       |

| 5       | 32        | 16       | 32       | 16       | 50         | 20       | 33.3   | 20       | 10         | 66.6     |

| 6       | 24        | 12       | 24       | 12       | 66.6       | 66.6     | 40     | 66.6     | 33.3       | 80       |

| 7       | 16        | 8        | 16       | 8        | 80         | 50       | 50     | 50       | 25         | 52       |

| 8       | _         | -        | -        | -        | -          | _        | _      | _        |            | _        |

| 9       | -         | -        | _        | _        | -          | _        | _      | -        | -          | -        |

| A       | _         | <i>-</i> | -        | -        | -          | -        | _      | -        |            | _        |

| В       | -         | -        | -        | -        | _          | -        | _      | -        | -          | -        |

| C       | -         | -        | -        | -        | -          | _        | _      | _        | -          | -        |

| D       | _         | -        | -        | -        | _          | -        | _      | -        | -          | _        |

| E       | _         | -        | _        | _        | -          | _        | _      | -        | -          | _        |

| F       | _         | •        | -        | -        | -          | _        | _      | -        | -          | _        |

|         |           |          | L        |          | <u> </u>   |          |        | L        |            |          |

Note 1: Not guaranteed when Vcc < 4.5V.

# PERIPHERAL CLOCKS

|         | -04    | -07    | -16    | -23    | -41    | -42    | -57    |

|---------|--------|--------|--------|--------|--------|--------|--------|

| FDCLK   | 24     | 24     | 24     | 24     | 24     | 24     | 24     |

| BUSCLK  | -      | -      | -      | -      | -      | -      | -      |

| KBCLK   | 8      | 12     | 12     | 8      | -      | 8      | 12     |

| COMMCLK | -      | -      | -      | -      | -      | -      | 1.843  |

| REFCLK  | 14.318 | 14.318 | 14.318 | 14.318 | 14.318 | 14.318 | 14.318 |

6

FREQUENCY SELECTION FOR w48C55A (using 14.318MHz input; 3.3V and 5.0V)

| SCLK (23-20)         -61         -62         -63           2XCPU         CPU         2XCPU         CPU         2XCPU         CPU           0         8         4         8         4         8         4           1         16         8         16         8         16         8           2         32         16         32         16         60         30           3         40         20         40         20         40         20           4         50         25         50         25         50         25           5         66.66         33.33         66.66         33.33         66.66         33.33           6         80         40         80         40         80         40 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2XCPU         CPU         2XCPU         CPU         2XCPU         CPU           0         8         4         8         4         8         4           1         16         8         16         8         16         8           2         32         16         32         16         60         30           3         40         20         40         20         40         20           4         50         25         50         25         50         25           5         66.66         33.33         66.66         33.33         66.66         33.33           6         80         40         80         40         80         40                                                            |    |

| 1     16     8     16     8     16     8       2     32     16     32     16     60     30       3     40     20     40     20     40     20       4     50     25     50     25     50     25       5     66.66     33.33     66.66     33.33     66.66     33.33       6     80     40     80     40     80     40                                                                                                                                                                                                                                                                                                                                                                                        | U  |

| 2     32     16     32     16     60     36       3     40     20     40     20     40     20       4     50     25     50     25     50     25       5     66.66     33.33     66.66     33.33     66.66     33.33       6     80     40     80     40     80     40                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3     40     20     40     20     40     20       4     50     25     50     25     50     25       5     66.66     33.33     66.66     33.33     66.66     33.3       6     80     40     80     40     80     40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4     50     25     50     25     50     25       5     66.66     33.33     66.66     33.33     66.66     33.       6     80     40     80     40     80     40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 5     66.66     33.33     66.66     33.33     66.66     33.       6     80     40     80     40     80     40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +  |

| 6 80 40 80 40 80 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | i  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | l  |

| 7   100 -NOTE1- 50   100 -NOTE1- 50   100 -NOTE1- 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

Note 1: Not guaranteed when Vcc < 4.5V.

# PERIPHERAL CLOCKS

|                                            | -61    | -62    | -63    |

|--------------------------------------------|--------|--------|--------|

| FDCLK BUSCLK KBCLK COMMCLK REFCLK1 REFCLK2 | 24     | 24     | 24     |

|                                            | 16     | 32     | 15     |

|                                            | 12     | 12     | 12     |

|                                            | 1.843  | 1.843  | 40     |

|                                            | 14.318 | 14.318 | 14.318 |

|                                            | 14.318 | 14.318 | 14.318 |

7

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Parameter                                                                         | Sym  | Rating | Parameter                                | Sym     | Rating                                         |

|-----------------------------------------------------------------------------------|------|--------|------------------------------------------|---------|------------------------------------------------|

| V <sub>CC</sub> referenced to GND<br>Storage temperature<br>Operating temperature | TSTG |        | V on I/O ref to GND<br>Power dissipation | -<br>PD | GND-0.5V to V <sub>CC</sub> +0.5V<br>0.5 Watts |

**Note 1:** Stresses above those listed under Absolute Maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure the absolute maximum conditions for extended periods may affect devices reliability.

### **ELECTRICAL CHARACTERISTICS AT 5.0V**

DC CHARACTERISTICS ( $V_{CC} = +5.0V \pm 10\%$ ,  $T_A = 0$ °C to +70°C)

| Parameter                       | Symbol              | Conditions                            | Min                   | Тур   | Max  | Units |

|---------------------------------|---------------------|---------------------------------------|-----------------------|-------|------|-------|

| Input Low Voltage               | $v_{IL}$            | $V_{CC} = 5V$                         | -                     | -     | 0.8  | v     |

| Input High Voltage              | $v_{IH}$            | $V_{CC} = 5V$                         | 2.0                   | -     | -    | v     |

| Input Low Current (Note 2)      | I <sub>IL</sub>     | $V_{IN} = 0V$                         | -                     | -     | -100 | μА    |

| Input High Current              | I <sub>IH</sub>     | $V_{IN} = V_{CC}$                     | -                     | -     | 10   | μА    |

| Output Low Voltage              | v <sub>OL</sub>     | $I_{OL} = 4 \text{ mA}$               | -                     | -     | 0.4  | v     |

| Output High Voltage             | v <sub>OH</sub>     | $I_{OH} = -1 \text{ mA}, V_{CC} = 5V$ | V <sub>CC</sub> -0.4V | _     | -    | v     |

| Output High Voltage             | v <sub>OH</sub>     | $I_{OH}$ = -4 mA, $V_{CC}$ =5 $V$     | v <sub>CC</sub> -0.8V | -     | -    | v     |

| Output High Voltage             | v <sub>OH</sub>     | $I_{OH} = -8 \text{ mA}$              | 2.4                   | -     | -    | v     |

| Supply Current (Note 3)         | I <sub>CC</sub>     | No load                               | -                     | 25    | 40   | mA    |

| Output Freq Change (Note 4)     | F <sub>D</sub>      | Over supply                           | -                     | 0.002 | 0.01 | %     |

|                                 |                     | and temperature                       |                       |       |      |       |

| Short Circuit Current           | I <sub>SC</sub>     | Each output clock                     | 25                    | 40    | -    | mA    |

| Supply Current, Pwr Dwn(Note 5) | I <sub>CCSTBY</sub> |                                       | -                     | 30    | -    | μА    |

| Input Capacitance               | $c_{ m IN}$         | Except X1, X2                         | -                     | -     | 10   | рF    |

| Load Capacitance                | $c_{L}$             | Pins X1, X2                           | -                     | 20    | -    | рF    |

| Pull-Up Resistor Value          | R <sub>P</sub>      | Except X1, X2                         | -                     | 250   |      | kΩ    |

Note 2: Includes pull-up resistor.

Note 3: No output load capacitance, CPUCLK or 2XCPUCLK running at 50MHz. Power supply current can change with different mask configuration.

Note 4: Consideration of reference crystal shift only.

Note 5: With full chip power down pin low.

# **ELECTRICAL CHARACTERISTICS AT 5.0V(cont.)**

AC CHARACTERISTICS  $(V_{CC} = +5.0V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C)$

| Parameter                                | Symbol             | Conditions        | Min      | Тур    | Max   | Units |

|------------------------------------------|--------------------|-------------------|----------|--------|-------|-------|

| Input Clock Rise Time                    | T <sub>ICR</sub>   |                   | -        | -      | 20    | ns    |

| Input Clock Fall Time                    | T <sub>ICF</sub>   |                   | -        | _      | 20    | ns    |

| Output Rise Time, 0.8 to 2.0V            | T <sub>R</sub>     | 25 pf load        | -        | 1      | 2     | ns    |

| Rise Time, 20% to 80% V <sub>CC</sub>    | $T_{\mathbf{R}}$   | 25 pf load        | -        | 2      | 4     | ns    |

| Output Fall Time, 2.0 to 0.8V            | т <sub>F</sub>     | 25 pf load        | -        | 1      | 2     | ns    |

| Fall Time, 80% to 20% V <sub>CC</sub>    | T <sub>F</sub>     | 25 pf load        | -        | 2      | 4     | ns    |

| Duty Cycle, All Outputs                  | $D_{\overline{1}}$ | 25 pf load        | 40/60    | 50/50  | 60/40 | %     |

| Jitter, 1 Sigma                          | T <sub>J1S</sub>   | As compared       | -        | 0.8    | 2.5   | %     |

| Jitter, Absolute                         | Т <sub>ЈАВ</sub>   | With clock period | -        | 2      | 5     | %     |

| Jitter, Absolute                         | T <sub>JAB</sub>   | 16-100 MHz clocks | -        | -      | 700   | ps    |

| Input Frequency                          | F <sub>I</sub>     |                   | -        | 14.318 | -     | MHz   |

| Clock Skew Between CPU and 2XCPU Outputs | T <sub>SK</sub>    |                   | -        |        | 1.0   | ns    |

| Frequency Transition Time                | T <sub>FT</sub>    | From 8-100 MHz    | <u>-</u> | 40     | 50    | ms    |

## **NOTES**

## **ELECTRICAL CHARACTERISTICS AT 3.3V**

DC CHARACTERISTICS ( $V_{CC} = +3.3V \pm 10\%$ ,  $T_A = 0$ °C to +70°C)

| Parameter                        | Symbol              | Conditions                | Min    | Тур   | Max     | Units |

|----------------------------------|---------------------|---------------------------|--------|-------|---------|-------|

| Input Low Voltage                | V <sub>IL</sub>     | $V_{CC} = 3.3V$           | -      | -     | 0.15Vcc | V     |

| Input High Voltage               | $v_{IH}$            | $V_{CC} = 3.3V$           | 0.7Vcc | -     | ~       | V     |

| Input Low Current (Note 2)       | ${ m I}_{ m IL}$    | $V_{IN} = 0V$             | _      | -     | -100    | μА    |

| Input High Current               | I <sub>IH</sub>     | $V_{IN} = V_{CC}$         | -      | -     | 10      | μА    |

| Output Low Voltage               | v <sub>OL</sub>     | $I_{OL} = 4 \text{ mA}$   | -      | -     | 0.4     | v     |

| Output High Voltage              | v <sub>OH</sub>     | $I_{OH} = -4 \text{ mA},$ | 2.4    | -     | -       | V     |

|                                  |                     | V <sub>CC</sub> =3.3V     |        |       |         |       |

| Supply Current (Note 3)          | I <sub>CC</sub>     | No load                   | -      | 20    | 35      | mA    |

| Output Freq Change (Note 4)      | ${	t F}_{ m D}$     | Over supply               | -      | 0.002 | 0.01    | %     |

|                                  |                     | and temperature           |        |       |         |       |

| Short Circuit Current            | I <sub>SC</sub>     | Each output clock         | 25     | 40    | -       | mA    |

| Supply Current, Pwr Dwn (Note 5) | I <sub>CCSTBY</sub> |                           | -      | 25    | _       | μА    |

| Input Capacitance                | $c_{IN}$            | Except X1, X2             | -      | _     | 10      | рF    |

| Load Capacitance                 | $c_{L}$             | Pins X1, X2               | _      | 20    | -       | рF    |

| Pull-Up Resistor Value           | R <sub>P</sub>      | Except X1, X2             | -      | 250   |         | kΩ    |

Note 2: Includes pull-up resistor.

Note 3: No output load capacitance, CPUCLK or 2XCPUCLK running at 50MHz. Power supply current can change with different mask configuration.

Note 4: Consideration of reference crystal shift only

Note 5: With full chip power down pin low.

# **ELECTRICAL CHARACTERISTICS AT 3.3V (cont.)**

AC CHARACTERISTICS ( $V_{CC} = +3.3V \pm 10\%$ ,  $T_A = 0$ °C to +70°C)

| Parameter                                | Symbol           | Conditions        | Min   | Тур    | Max   | Units |

|------------------------------------------|------------------|-------------------|-------|--------|-------|-------|

| Input Clock Rise Time                    | T <sub>ICR</sub> |                   | -     | -      | 20    | ns    |

| Input Clock Fall Time                    | T <sub>ICF</sub> |                   | -     | -      | 20    | ns    |

| Rise Time, 20% to 80% V <sub>CC</sub>    | $T_{\mathbf{R}}$ | 15 pf load        | _     | 2      | 4     | ns    |

| Fall Time, 80% to 20% V <sub>CC</sub>    | T <sub>F</sub>   | 15 pf load        | -     | 2      | 4     | ns    |

| Duty Cycle, All Outputs                  | $D_{T}$          | 15 pf load        | 40/60 | 50/50  | 60/40 | %     |

| Jitter, 1 Sigma                          | T <sub>J1S</sub> | As compared       | -     | 0.8    | 2.5   | %     |

| Jitter, Absolute                         | T <sub>JAB</sub> | with clock period | -     | 2      | 5     | %     |

| Jitter, Absolute                         | T <sub>JAB</sub> | 16-80 MHz clocks  | -     | -      | 700   | ps    |

| Input Frequency                          | FI               |                   | -     | 14.318 | -     | MHz   |

| Clock Skew Between CPU and 2XCPU Outputs | T <sub>SK</sub>  |                   | -     |        | 1.0   | ns    |

| Frequency Transition Time                | T <sub>FT</sub>  | From 8-100 MHz    | -     | 40     | 50    | ms    |

# CROSS REFERENCE LIST: w48C54A/55A

| IC WORKS<br>Device | Compatible<br>Device |

|--------------------|----------------------|

| <b>ш</b> 48С54А-04 | AV9154-04            |

| ш48С54A-07         | AV9154-26            |

| <b>W</b> 48C54A-16 | AV9154-16            |

| <b>W</b> 48C54A-42 | AV9154-42            |

| <b>ш</b> 48C54A-57 | AV9154-27            |

|                    |                      |

| <b>W</b> 48C55A-61 | AV9155-01            |

| <b>W</b> 48C55A-62 | AV9155-02            |

| w48C55A-63         | AV9155-36            |

11

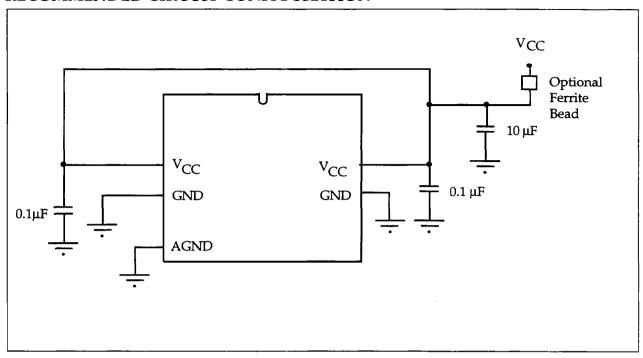

## RECOMMENDED CIRCUIT CONFIGURATION

### RECOMMENDED BOARD LAYOUT: w48C54A/55A

For optimum performance in system applications the above power supply decoupling scheme should be used. All GND pins are connected directly to the ground plane.

VCC decoupling is important to both reduce phase jitter and EMI radiation. The 0.1µf decoupling capacitors should be placed as close to the VCC pins as possible, otherwise the increased trace inductance will negate its decoupling capability. The 10µf decoupling capacitor shown should be a tantalum type. For further EMI protection, the VCC connection can be made via a ferrite bead, as shown above.

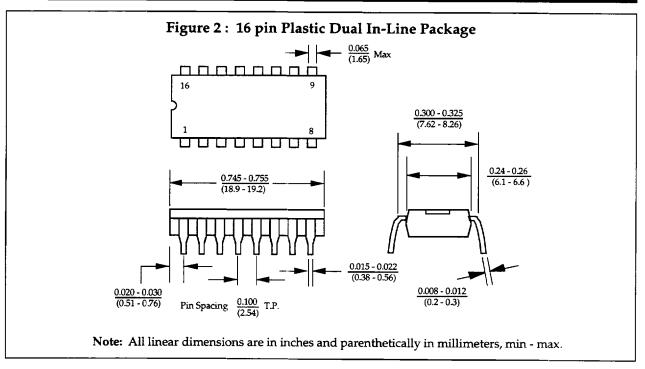

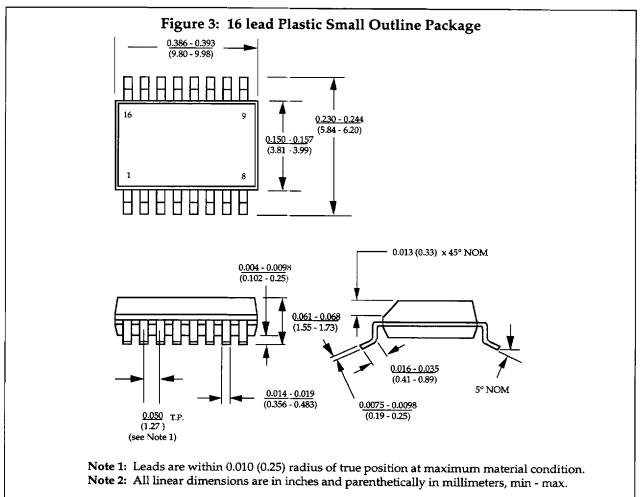

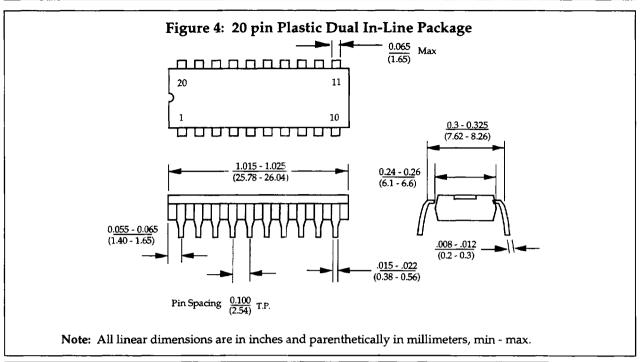

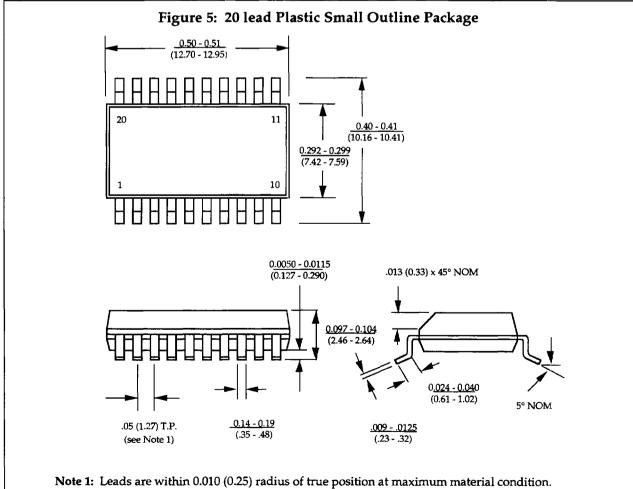

Note 2: All linear dimensions are in inches and parenthetically in millimeters, min - max.

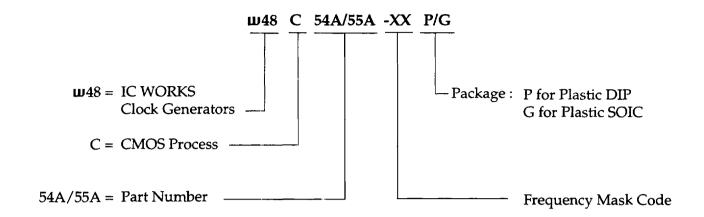

### ORDERING INFORMATION

### VALID PART NUMBERS

ш48С54А-04 ш48С54А-07 ш48С54А-16 ш48С54А-23 ш48С54А-41 ш48С54А-42 ш48С54А-57

**w**48C55A-61 **w**48C55A-62 **w**48C55A-63

IC WORKS, Inc. 3725 North First Street San Jose, CA 95134-1700 Tel: (408) 922-0202

Fax: (408) 922-0833

IC WORKS, Inc. reserves the right to amend or discontinue product development without notice. Circuit and timing diagrams used to describe IC WORKS products operation and applications are included as a means of illustrating a typical product application. Complete information for design purposes is not necessarily given. This information has been carefully checked and is believed to be entirely reliable. IC WORKS, however, will not assume any responsibility for inaccuracies.

### LIFE SUPPORT APPLICATIONS:

IC WORKS products are not designed for use in life support applications, devices, or systems where malfunctions of the IC WORKS product can reasonably be expected to result in personal injury. IC WORKS customers using or selling IC WORKS products for use in such applications do so at their own risk and agree to fully indemnify IC WORKS for any damages resulting in such improper use or sale.

Document No. 48C54A/55A/00/0195