# Am2864B

8192 x 8 Electrically Erasable PROM

## DISTINCTIVE CHARACTERISTICS

- 5-V only operation

- Military temperature range available

- Self-timed Write Cycle with on-chip latches

- Ready/Busy pin and Data Polling for end-of-write indication

- Data protection features to prevent writes from occurring during V<sub>CC</sub> power-up/down

- 32-byte page write mode

- Minimum endurance of 10,000 write cycles per byte with a 10-year retention. For detailed information, see the Am9864 Reliability Report (PID #06891A).

## **GENERAL DESCRIPTION**

The Am2864B is a 65,536-bit Electrically Erasable Programmable Read-Only Memory (EEPROM), organized as 8192 words by 8 bits per word. It operates from a single 5-volt supply and has a fully self timed write cycle with address, data and control lines latched during the write operation. The 32-byte page write mode allows programming in as little as 2.8 seconds. The Am2864B is fabricated on AMD's highly manufacturable N-Channel Silicon gate process, and uses AMD's proprietary EEPROM technology

to achieve the electrically alterable nonvolatile storage. This technology employs the industry-accepted accepted Fowler-Nordheim tunneling across a thin oxide.

The Am2864B provides on-chip the logic necessary to interface with most microprocessors. The latched inputs and self-timed write cycle free the microprocessor to perform other tasks during a write. A transparent automatic erase before write enhances system performance.

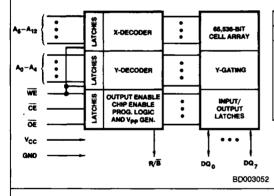

#### **BLOCK DIAGRAM**

# MODE SELECT TABLE

Oudmide

|    | Inputs | i  | Outputs |          |                |               |

|----|--------|----|---------|----------|----------------|---------------|

| CE | ŌĒ     | WE | R/B     | 1/0      | A <sub>9</sub> | Mode          |

| Ļ  | L      | Н  | Hi Z    | Data Out | Х              | Read          |

| L  | Н      | T  | ע       | Data In  | ×              | Write         |

| Н  | X      | x  | Hi Z    | HiZ      | Х              | Standby       |

| L  | н      | н  | Hi Z    | Hi Z     | Х              | Read Inhibit  |

| X  | L      | X  | l –     | _        | X              | Write Inhibit |

| L  | ļ L    | н  | Hi Z    | Code     | V <sub>H</sub> | Auto Select   |

| L  | L      | н  | L       | Din      | X              | Data Polling  |

$V_H = 12.0 V \pm .5 V$ H = HIGH

L = LOW

X = Don't Care

# PRODUCT SELECTOR GUIDE

| Part Number                         | Am2864B-20 Am2864B-20 |      | Am2864B | Am2864B-25 | Am2864B-30 |      | Am2864B355 | Am2864B-35 |  |

|-------------------------------------|-----------------------|------|---------|------------|------------|------|------------|------------|--|

| Maximum<br>Access Time              | 200 ns                |      | 250 ns  |            | 300        | ns   | 350 ns     |            |  |

| V <sub>CC</sub> Supply<br>Tolerance | ±5%                   | ±10% | ±5%     | ± 10%      | ±5%        | ±10% | ±5%        | ±10%       |  |

Publication # Rev. Amendment 05571 D /0 Issue Date: May 1986

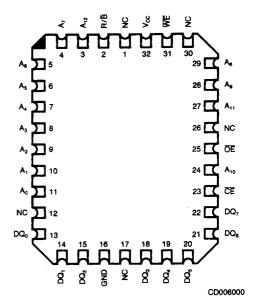

# CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation.

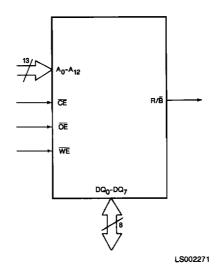

# LOGIC SYMBOL

V<sub>CC</sub> = Power Supply GND = Ground

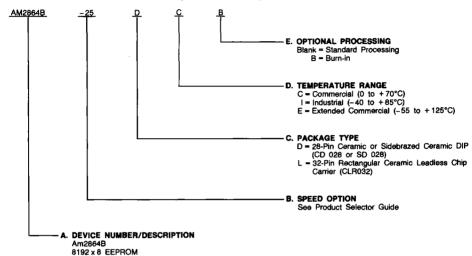

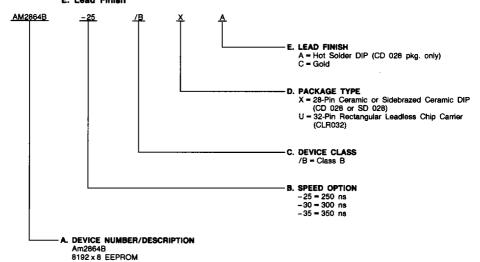

# ORDERING INFORMATION (Cont'd.)

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid

- Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid C     | Valid Combinations      |  |  |  |  |

|-------------|-------------------------|--|--|--|--|

| AM2864B-2   |                         |  |  |  |  |

| AM2864B-20  | ]                       |  |  |  |  |

| AM2864B     | DC, DCB,                |  |  |  |  |

| AM2864B-25  | DI, DIB, DE, DEB,       |  |  |  |  |

| AM2864B-3   | LC, LCB,                |  |  |  |  |

| AM2864B-30  | ] LI, LIB,<br>] LE, LEB |  |  |  |  |

| AM2864B-355 | ],                      |  |  |  |  |

| AM2864B-35  |                         |  |  |  |  |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

# ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |                  |  |  |  |  |  |

|--------------------|------------------|--|--|--|--|--|

| AM2864B-25         |                  |  |  |  |  |  |

| AM2864B-30         | /BXA, /BXC, /BUC |  |  |  |  |  |

| AM2864B-35         |                  |  |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

## **FUNCTIONAL DESCRIPTION**

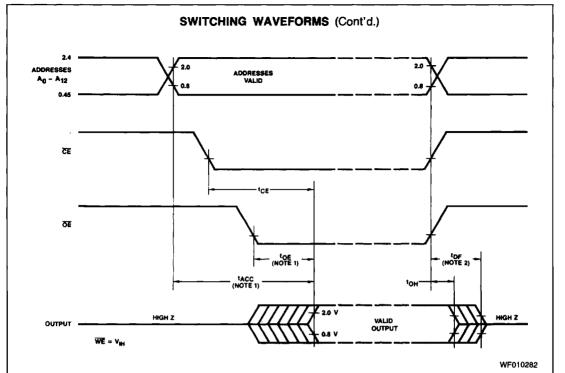

#### Read Mode

The Am2864B has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data to the output pins independent of device selection. Assuming that addresses are stable, address access time ( $t_{\text{ACC}}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{\text{CE}}$ ). Data is available at the outputs  $t_{\text{OE}}$  after the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been LOW and addresses have been stable for at least  $t_{\text{ACC}}$ - $t_{\text{OE}}$ .

## Standby Mode

The Am2864B has a standby mode which reduces the active power dissipation by 60%, from 525 mW to 210 mW ( $V_{CC}$  ±5% values for 0 to 70°C). The Am2864B is placed in the standby mode by applying a TTL HIGH signal to the  $\overline{CE}$  input. When in the standby mode, the outputs are in a high-impedance state, independent of the  $\overline{OE}$  input.

#### **Data Protection**

The Am2864B incorporates several features that prevent unwanted write cycles during V<sub>CC</sub> power-up and power-down. These features protect the integrity of the stored data.

To avoid the initiation of a write cycle during  $V_{CC}$  power-up and power-down, a write cycle is locked out for  $V_{CC}$  less than 3.3 volts (typical 3.8 V). It is the users's responsibility to insure that the control levels are logically correct when  $V_{CC}$  is above 3.3 volts.

There is a WE lockout circuit that prevents WE pulses of less than 20 ns duration from initiating a write cycle.

When the OE control is in logic zero condition, a write cycle cannot be initiated.

## Page Write Mode

The page write allows from 1 to 32 bytes of data to be written into the EEPROM in a single write cycle. The page write mode consists of a load sequence followed by an automatic write sequence.

During the load portion, sequential  $\overline{WE}$  pulses load the byte address and the byte data into a 32-byte register. The bytes can be loaded into this register in any order. On each  $\overline{WE}$  pulse, the "Y" address is latched on the falling edge of the  $\overline{WE}$ , the data input is latched on the rising edge of  $\overline{WE}$ , and the page address ( $A_5$ - $A_{12}$ ) is latched on the falling edge of the last  $\overline{WE}$ . Note that for a write to occur,  $\overline{CE}$  and  $\overline{WE}$  must be LOW and  $\overline{OE}$  must be HIGH. The load portion of the page write is complete when all the data (up to 32 bytes) is loaded into the register.

The automatic write portion starts tww after each transition of WE from LOW-to-HIGH. If WE transitions from HIGH-to-LOW before tww minimum (100 µs), the timer is reset and the automatic write portion does not start. This is how the bytes are loaded into the register. If WE is held LOW, this tww timer never starts and the write cycle is held indefinitely.

If WE transitions from LOW-to-HIGH and stays HIGH for at least tww maximum, then the automatic write sequence is initiated. Note that the load sequence can also be terminated if OE goes LOW. Once OE is LOW, further attempts to load will be ignored and the part will time out (tww) and enter the automatic write sequence.

The automatic write sequence consists of an erase cycle, which erases any data that existed in each addressed cell, and a write cycle, which puts data back into the erased cells. Note

that a page write will only write data to the locations being addressed and will not rewrite the entire page. The Ready/Busy pin (R/B) goes to a logic LOW level during the automatic write sequence. This could signal a microprocessor host that the system bus is free for other activity. When R/B transitions to a HIGH state, the Am2864B has completed writing and is ready to accept another cycle.

# **Byte Mode Write**

When  $\overline{WE}$  is toggled once, the Am2864B operates in the byte mode. A single byte is loaded into the register and after  $\overline{WE}$  goes HIGH and tywy is satisfied, the automatic write cycle starts. It is in this mode that the Am2864B is similar to the Am9864 and the Am2817A.

#### **Auto Select Mode**

The auto select mode allows the reading out of a binary code from an EEPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional at 25°C ±5°C ambient temperature.

To activate this mode, programming equipment must force 11.5 V to 12.5 V on address line  $A_0$  of the Am2864B. Two identifier bytes may then be sequenced from the device outputs by toggling address line  $A_0$  from  $V_{\rm IL}$  to  $V_{\rm IH}$ . All other address lines must be held at  $V_{\rm IL}$  during auto select mode.

Byte 0 ( $A_0 = V_{IL}$ ) represents the manufacturer code and byte 1 ( $A_0 = V_{IL}$ ) the device identifier code. For the Am2864B, these two identifier bytes are given in Table 1. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (07) defined as the parity bit.

## **Output OR-Tieing**

To accommodate multiple memory connections, a 2-line control function is provided to allow for:

- 1. Low memory power dissipation, and

- 2. Assurance that output bus contention will not occur.

It is recommended that  $\overline{CE}$  be decoded and used as the primary device selecting function, while  $\overline{OE}$  be made a common connection to all devices in the array and connected to the read line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

## Ready/Busy Pin

The Ready/Busy (R/B) pin is an open-drain output which allows two or more R/B signals to be OR-tied together. The value of the pullup resistor required is as follows:

$$R_{pu} = \frac{4.6 \text{ volts}}{2.1 \text{ mA} - I_{IL}}$$

IIL = total VIL input current of devices connected to R/B.

A typical pullup resistor value for R/B is 3 k $\Omega$ , assuming I<sub>IL</sub> is less than 0.5 mA.

#### Data Polling

This feature makes the Am2864B highly flexible. It allows the designer the option of a software polling technique as well as the hardware interrupt Ready/Busy technique for end of write indication. Data Polling requires a simple software routine that performs a read operation when the chip is in the automatic write mode. The data that becomes valid during this Data Polling read is the inverse of all 8 bits, last written to the outputs. The true data  $(DQ_0 - DQ_7)$  will become valid when the automatic write has been completed. Note that all 8 bits

invert during Data Polling, thereby giving the user more flexibility during design and layout.

## Chip Clear Mode (Military only)

Another feature included on AMD's Am2864B for military applications is a single-pulse chip erase. This optional mode allows the user to program all bits to a logic ONE with a single 10-ms write pulse. Additional information is available from AMD regarding this test mode -- consult the local AMD sales office.

#### **Endurance**

Since endurance testing is a destructive test it is sampled and not 100% tested. To test for endurance, a sample of devices are written 10,000 times and checked for data retention capability.

There is one main failure mechanism associated with endurance failures in EEPROMs. This failure mechanism is due to charge trapping in the thin tunneling dielectric. At a point, when the amount of trapped charge creates an electric field that exceeds the dielectric breakdown of the oxide, the oxide becomes conductive, and reliable storage of charge on the floating gate is no longer possible. This results in the failure of a single bit to properly write and retain data.

There are three different failure rates associated with this failure mechanism, and the failure rates are a function of the number of write cycles. For less than a few hundred write cycles, the failure rate is relatively high. During AMD testing, each part is written hundreds of times to allow those cells that would be infant-mortality failures to be screened out. For the next 20,000 to 30,000 write cycles the failure rate is low. It is in

this region that AMD EEPROMs are operated. Somewhere above this region, typically well above the guarantee of 104 total write cycles, the failure rate again starts increasing.

The endurance failure rate is a function of the number of write cycles that the part has experienced. All parts that pass the AMD test screens will write a minimum of 10,000 times at every byte location with a maximum failure rate of 5%. In other words, 5% of a sample of devices will fail to write or to retain information after write if they are written 10,000 times. Those devices that fail will typically have a single bit that fails to retain the correct data after being written. This failure rate is measured from a sample of devices, in the same manner that other reliability failure mechanisms are measured.

For more detailed information on how this data was obtained please refer to the Am9864 Reliability Report (PID#06891A).

## **APPLICATIONS**

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. A 0.1-µF ceramic capacitor (high frequency, low inherent inductance) should be used on each device between V<sub>CC</sub> and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on EEPROM arrays, a 4.7-µF bulk electrolytic capacitor should be used between VCC and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

## **PROGRAMMING**

TABLE 1. IDENTIFIER BYTES (Notes 1, 2 & 3)

| Identifier        | A <sub>0</sub>  | DQ <sub>7</sub> | DQ <sub>6</sub> | DQ5 | DQ4 | DQ <sub>3</sub> | DQ <sub>2</sub> | DQ <sub>1</sub> | DQ <sub>0</sub> | Hex |

|-------------------|-----------------|-----------------|-----------------|-----|-----|-----------------|-----------------|-----------------|-----------------|-----|

| Manufacturer Code | V <sub>IL</sub> | 0               | 0               | 0   | 0   | 0               | 0               | 0               | 1               | 01  |

| Device Code       | VIH             | 1               | 0               | 0   | 0   | 1               | 0               | 1               | 0               | 8A  |

Legend: 1 = HIGH 0 = LOW

Notes: 1.  $A_9 = 12.0 \text{ V} \pm 0.5 \text{ V}$

2.  $A_1 - A_8$ ,  $A_{10} - A_{12}$ ,  $\overline{CE}$ ,  $\overline{OE} = V_{IL}$ 3.  $\overline{WE} = V_{IH}$

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65                    | to + 150°C  |

|------------------------------------------|-------------|

| Ambient Temperature with Power Applied65 | to +135°C   |

| Voltage on All Inputs with Respect       |             |

| to GND+ 6.50                             | to _06 V    |

| Voltage on A <sub>9</sub> with Respect   | , 10 -0.0 ¥ |

| to GND+ 13.5                             | 5 to -06 V  |

| 10.0                                     | , 10 -0.0 V |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| O' EIIAIING NANGEO                                    |

|-------------------------------------------------------|

| Commercial (C) Devices                                |

| Temperature (T <sub>C</sub> ) 0 to +70°C              |

| Supply Voltage (V <sub>CC</sub> ±5%)+4.75 to +5.25 V  |

| (V <sub>CC</sub> ±10%)+4.50 to +5.50 V                |

| Industrial (I) Devices                                |

| Temperature (T <sub>C</sub> )40 to +85°C              |

| Supply Voltage (V <sub>CC</sub> ±5%)+4.75 to +5.25 V  |

| (V <sub>CC</sub> ±10%)+4.50 to +5.50 V                |

| Extended Commercial (E) Devices                       |

| Temperature (T <sub>C</sub> )55 to +125°C             |

| Supply Voltage (V <sub>CC</sub> ±10%)+4.50 to +5.50 V |

| Military (M) Devices                                  |

| Temperature (T <sub>C</sub> )55 to +125°C             |

| Supply Voltage (V <sub>CC</sub> ±10%)+4.50 to +5.50 V |

| <b>-</b>                                              |

Operating ranges define those limits between which the functionality of the device is guaranteed,

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameter<br>Symbol | Parameter<br>Description          | Test Conditions               | Min. | Тур.                                             | Max.               | Units |

|---------------------|-----------------------------------|-------------------------------|------|--------------------------------------------------|--------------------|-------|

| l <u>u</u>          | Input Leakage Current             | V <sub>IN</sub> = 0 to 5.5 V  |      |                                                  | 10                 | μΑ    |

| ILO                 | Output Leakage Current            | V <sub>OUT</sub> = 0 to 5.5 V | _    | _                                                | 10                 | μA    |

| loc1                | V <sub>CC</sub> Current (Standby) | CE = VIH, OE = VII            | _    | _                                                | 40                 | mA    |

| lcc2                | V <sub>CC</sub> Current (Active)  | OE = CE - VIL                 | _    |                                                  | 100                | mA.   |

| loc                 | V <sub>CC</sub> Current (Write)   | WE = 1. CE = VIL, OE = VIH    | _    |                                                  | 100                | mA    |

| ViL                 | Input LOW Voltage                 | 10, 22, 177                   | -0.1 |                                                  | .8                 | Volts |

| VIH                 | Input HIGH Voltage                |                               | 2.0  |                                                  | V <sub>CC</sub> +1 | Volts |

| VOL                 | Output LOW Voltage                | I <sub>OL</sub> = 2.1 mA      |      | <del>                                     </del> | 45                 | Volts |

| VOH                 | Output HIGH Voltage               | IOH = -400 μA                 | 2.4  | <del>-</del>                                     |                    | Volts |

| VRB                 | R/B Output LOW                    | IRR = 2.1 mA                  |      | <del></del>                                      | .45                | Volts |

| CiN                 | Input Capacitance (Note 1, 2)     | V <sub>IN</sub> = 0 V         |      | 4                                                | 10                 | pF    |

| COUT                | Output Capacitance (Note 1, 2)    | OE = CE = VIH, VOUT = 0 V     |      | 8                                                | 12                 | ρF    |

| Vwi                 | Write Inhibit Voltage             |                               | 3.3  | 3.8                                              | - ' <sup>2</sup>   | Volts |

Notes: 1. This parameter is sampled on a periodic basis and not 100% tested.

2. Freq. = 1 MHz @ 25°C.

3. Typical values are for nominal supply voltages.

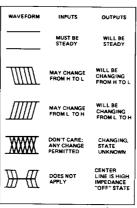

# **KEY TO SWITCHING WAVEFORMS**

KS000010

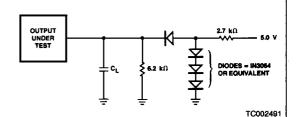

## SWITCHING TEST CIRCUIT

# **Switching Test Conditions**

Output load: 1 TTL gate and CL = 100 pF Input pulse levels: 0.45 V to 2.4 V

# **Timing Measurement Reference Levels**

Input: 0.8 V and 2.0 V Output: 0.8 V and 2.0 V

C<sub>L</sub> = 100 pF, including jig capacitance.

# SWITCHING CHARACTERISTICS over operating ranges

|       |                             |                                                                     | Test                         |      | 64B-2,<br>64B-20 |      |      |      | 64B-3,<br>64B-30 |      | 64 <b>8</b> 355,<br>64 <b>B-3</b> 5 |       |

|-------|-----------------------------|---------------------------------------------------------------------|------------------------------|------|------------------|------|------|------|------------------|------|-------------------------------------|-------|

| No.   | Parameter<br>Symbol         | Parameter<br>Description                                            | Conditions                   | Min. | Max.             | Min. | Max. | Min. | Max.             | Min. | Max.                                | Units |

| READ  |                             | •                                                                   |                              |      |                  |      |      |      |                  |      |                                     |       |

| 1     | †ACC                        | Address to Output Delay                                             | CE = OE<br>= V <sub>IL</sub> |      | 200              |      | 250  |      | 300              |      | 350                                 | ns    |

| 2     | t <sub>CE</sub>             | CE to Output Delay                                                  | ŌĒ ≂ V <sub>IL</sub>         |      | 200              |      | 250  |      | 300              |      | 350                                 | ns    |

| 3     | t <sub>OE</sub>             | Output Enable to Output<br>Delay                                    | CE = VIL                     |      | 75               |      | 100  |      | 110              |      | 120                                 | ns    |

| 4     | t <sub>DF</sub><br>(Note 1) | Output Enable HIGH to<br>Output Float                               | CE = VIL                     | 0    | 60               | 0    | 60   |      | 70               | 0    | 80                                  | ns    |

| 5     | tOH<br>(Note 1)             | Output Hold from<br>Addresses, CE or OE<br>Whichever Occurred First | CE = OE<br>= V <sub>IL</sub> | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

| WRITE | E                           |                                                                     |                              |      |                  |      |      |      |                  |      |                                     |       |

| 6     | tas                         | Address to Write Setup Time                                         |                              | 20   |                  | 20   |      | 20   |                  | 60   |                                     | ns    |

| 7     | tcs                         | CE to Write Setup Time                                              |                              | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

| 8     | twp                         | Write Pulse Width                                                   |                              | 100  |                  | 100  |      | 120  |                  | 150  |                                     | ns    |

| 9     | t <sub>AH</sub>             | Address Hold Time                                                   |                              | 80   |                  | 80   |      | 80   |                  | 100  |                                     | ns    |

| 10    | tos                         | Data Setup Time                                                     |                              | 50   |                  | 50   |      | 50   |                  | 70   |                                     | ns    |

| 11    | t <sub>DH</sub>             | Data Hold Time                                                      |                              | 30   |                  | 30   |      | 30   |                  | 30   |                                     | ns    |

| 12    | tcH                         | CE Hold Time                                                        |                              | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

| 13    | toes                        | OE Setup Time                                                       |                              | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

| 14    | toeh                        | OE Hold Time                                                        |                              | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

| 15    | tos                         | Time to Device Busy                                                 |                              |      | 100              |      | 100  |      | 100              |      | 100                                 | ns    |

| 16    | twc                         | WE Cycle Time                                                       |                              | 1    |                  | 1    |      | 1    |                  | 1    |                                     | μs    |

| 17    | tww                         | Page Write Window<br>(Note 4)                                       |                              | 100  | 500              | 100  | 500  | 100  | 500              | 100  | 1000                                | μs    |

| 18    | twн                         | WE Hold Time                                                        |                              | 250  |                  | 250  |      | 250  |                  | 300  |                                     | ns    |

| 19    | twB                         | Byte Write Cycle                                                    |                              |      | 10               |      | 10   |      | 10               |      | 12                                  | ms    |

| 20    | t <sub>RED</sub>            | Write Recovery from Data<br>Polling Time                            |                              | 20   |                  | 20   |      | 20   |                  | 20   |                                     | μs    |

| 21    | tRE                         | Write Recovery from R/B Time (Note 5)                               |                              | 0    |                  | 0    |      | 0    |                  | 0    |                                     | ns    |

|       | tRBO                        | R/B to Output Time<br>(Notes 2, 5)                                  |                              |      | 50               |      | 50   |      | 50               |      | 50                                  | ns    |

|       | (Notes 1 & 3)               | Number of Writes per Byte                                           |                              | 10   |                  | 10   |      | 10   |                  | 10   |                                     | x1000 |

Notes: 1. This parameter is sampled on a periodic basis to worst-case test conditions and is not 100% tested.

2. If CE and DE - V<sub>IL</sub> when R/B is going to V<sub>OH</sub>, then DQ<sub>0</sub> - DQ<sub>7</sub> becomes valid after t<sub>RBO</sub> + t<sub>ACC</sub>.

3. See Am9864 Reliability Report.

A timer of tww duration starts at every LOW-to-HIGH transition of WE. If it is allowed to time out, a page load will start. A

transition of WE from HIGH-to-LOW will stop the timer.

<sup>5.</sup> This parameter is for information only. It is not tested or characterized.

Read

Notes: 1.  $\overline{\text{OE}}$  may be delayed up to  $t_{ACC}$ - $t_{OE}$  after the falling edge of  $\overline{\text{CE}}$  without impact on  $t_{ACC}$ .

2.  $t_{DE}$  is specified from  $\overline{\text{OE}}$  or  $\overline{\text{CE}}$ , whichever occurs first.

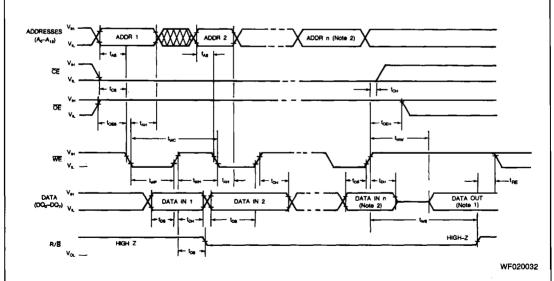

# Page Write

Notes: 1. This is where Data Polling is available. See Data Polling timing for setups. 2. n ≤ 32.

# SWITCHING WAVEFORMS

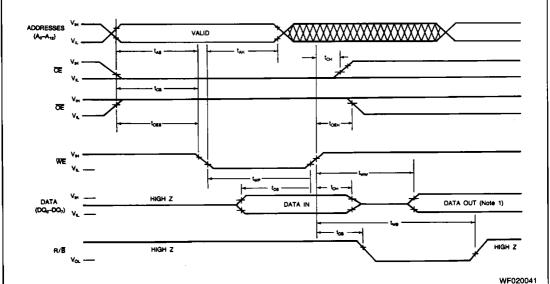

**Byte Write**

Notes: 1. This is where Data Polling is available. See Data Polling timing for setups.

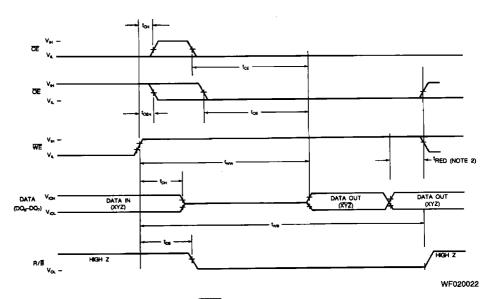

Data Polling

Notes: 1. This is shown for single byte write. In page write, R/B goes LOW on first LOW-to-HIGH transition

After the Write cycle is completed (R/B is HIGH or data out TRUE), the user must meet one of the following conditions to prevent an accidental write: OE LOW, CE HIGH, or WE HIGH.

# GROUP A SUBGROUP TESTING

# DC CHARACTERISTICS

| Parameter<br>Symbol | Subgroups |

|---------------------|-----------|

| ILI                 | 1, 2, 3   |

| lLO                 | 1, 2, 3   |

| I <sub>CC1</sub>    | 1, 2, 3   |

| ICC2                | 1, 2, 3   |

| lcc                 | 1, 2, 3   |

| VIL                 | 1, 2, 3   |

| VIH                 | 1, 2, 3   |

| VOL                 | 1, 2, 3   |

| VoH                 | 1, 2, 3   |

| V <sub>RB</sub>     | 1, 2, 3   |

| C <sub>IN</sub>     | 4         |

| Cout                | 4         |

| Vwi                 | 7, 8      |

# SWITCHING CHARACTERISTICS

| No. | Parameter<br>Symbol | Subgroups | No. | Parameter<br>Symbol | Subgroups |

|-----|---------------------|-----------|-----|---------------------|-----------|

| 1   | tACC                | 9, 10, 11 | 11  | t <sub>DH</sub>     | 9, 10, 11 |

| 2   | t <sub>CE</sub>     | 9, 10, 11 | 12  | tсн                 | 9, 10, 11 |

| 3   | t <sub>OE</sub>     | 9, 10, 11 | 13  | toes                | 9, 10, 11 |

| 4   | t <sub>DF</sub>     | 9, 10, 11 | 14  | t <sub>OEH</sub>    | 9, 10, 11 |

| 5   | tон                 | 9, 10, 11 | 15  | t <sub>DB</sub>     | 9, 10, 11 |

| 6   | tas                 | 9, 10, 11 | 16  | twc                 | 9, 10, 11 |

| 7   | tcs                 | 9, 10, 11 | 17  | tww                 | 9, 10, 11 |

| 8   | twp                 | 9, 10, 11 | 18  | twH                 | 9, 10, 11 |

| 9   | t <sub>AH</sub>     | 9, 10, 11 | 19  | twB                 | 9, 10, 11 |

| 10  | t <sub>DS</sub>     | 9, 10, 11 | 20  | tRED.               | 9, 10, 11 |

# **MILITARY BURN-IN**

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.