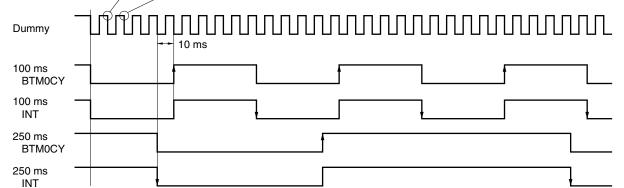

# MOS INTEGRATED CIRCUIT $\mu$ PD17012, 17P012

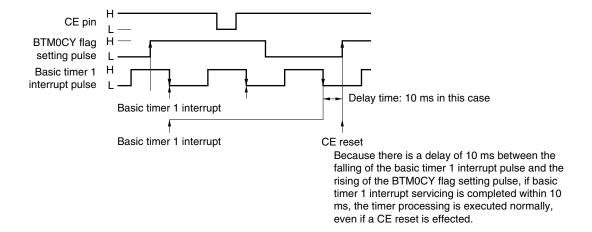

# 4-BIT SINGLE-CHIP MICROCONTROLLERS WITH DIGITAL TUNING SYSTEM HARDWARE

#### **DESCRIPTION**

The  $\mu$ PD17012 is a 4-bit single-chip CMOS microcontroller equipped with hardware for digital tuning systems. The  $\mu$ PD17P012 is a version of the  $\mu$ PD17012 with one-time PROM instead of mask ROM.

The user can write programs to the  $\mu$ PD17P012 once, and it is ideal for experimental production of the  $\mu$ PD17012 during system design or small-scale production.

This series employs a 17K architecture CPU that can directly manipulate the data memory, execute various operations, and control the peripheral hardware with a single instruction. All the instructions are one-word 16-bit instructions. Besides various I/O ports, an LCD controller/driver, A/D converter, D/A converter (PWM output), and BEEP output, this microcontroller has a prescaler that can operate at up to 250 MHz, a PLL frequency synthesizer, and frequency counter for digital tuning systems. This series therefore ideal for configuring a high-performance, multifunctional digital tuning system on a single chip.

#### **FEATURES**

- 17K architecture: General-purpose register method

- Program memory (ROM)

μPD17012: Mask ROM

8 KB (4,096 × 16 bits)

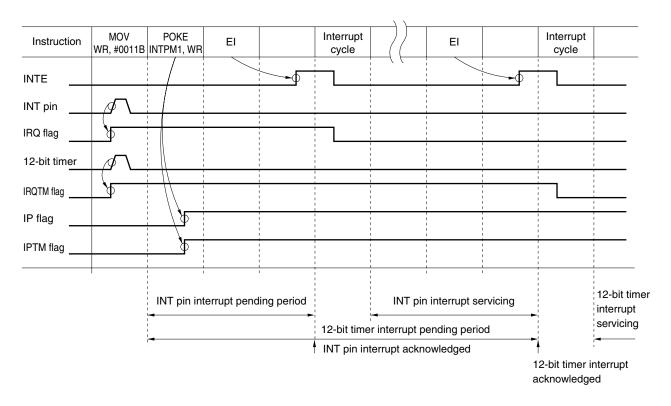

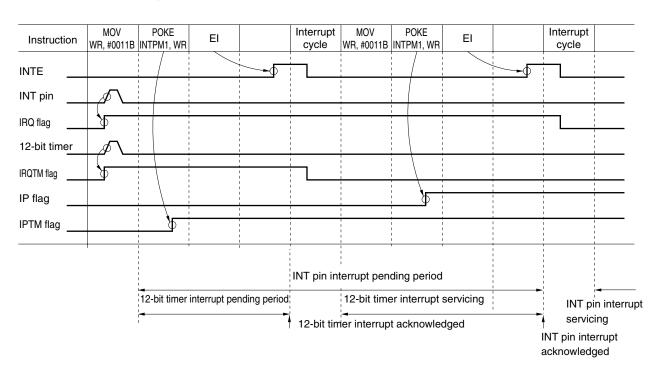

μPD17P012: One-time PROM

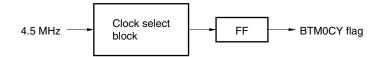

8 KB (4,096 × 16 bits)

- General-purpose data memory (RAM)

- $316 \times 4$  bits

- Instruction execution time

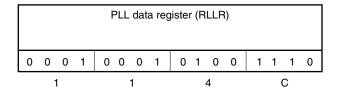

- 4.44  $\mu$ s (with 4.5 MHz crystal resonator)

- · Decimal operation

- · Table reference

- Hardware for PLL frequency synthesizer

Dual modulus prescaler (250 MHz max.), programmable divider, phase comparator, charge pump

- Various peripheral hardware

General-purpose I/O ports, LCD controller/driver, serial

interface, A/D converter, D/A converter (PWM output),

BEEP output, frequency counter

- Interrupts

External: 1 Internal: 3

- Power-on-reset, reset by CE pin, and power failure detector

- Power-saving CMOS

- Supply voltage: VDD = 5 V ±10%

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

The mark ★ shows major revised points.

# **ORDERING INFORMATION**

|   | Part Number             | Package                             |  |  |

|---|-------------------------|-------------------------------------|--|--|

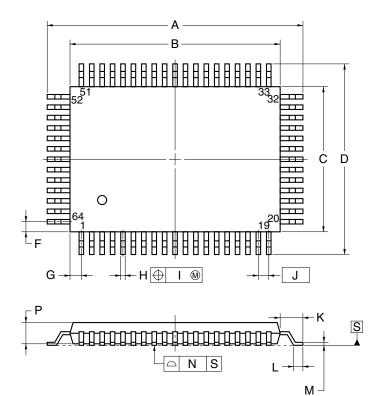

|   | $\mu$ PD17012GF-×××-3BE | 64-pin plastic QFP (14 $\times$ 20) |  |  |

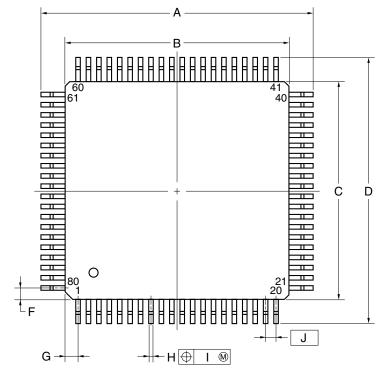

|   | $\mu$ PD17012GC-×××-8BT | 80-pin plastic QFP (14 $	imes$ 14)  |  |  |

| * | $\mu$ PD17P012GF-3BE    | 64-pin plastic QFP (14 $	imes$ 20)  |  |  |

| * | $\mu$ PD17P012GC-8BT    | 80-pin plastic QFP (14 $	imes$ 14)  |  |  |

$\textbf{Remark} \quad \times\!\!\times\!\!\times \text{ indicates the ROM code suffix.}$

# **OVERVIEW OF FUNCTIONS**

| Item                              | μPD17012                                                                                                                                                                                                                                                          | μPD17P012                              |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Program memory (ROM)              | 8 KB (4,096 × 16 bits) (mask ROM)                                                                                                                                                                                                                                 | 8 KB (4,096 × 16 bits) (one-time PROM) |  |

|                                   | Table reference area: 4,096 × 16 bits                                                                                                                                                                                                                             |                                        |  |

| General-purpose data memory (RAM) | 316 × 4 bits                                                                                                                                                                                                                                                      |                                        |  |

| Register file                     | 33 × 4 bits (control register)                                                                                                                                                                                                                                    |                                        |  |

| Port register                     | $12 \times 4$ bits (functions alternately as LCD                                                                                                                                                                                                                  | segment register)                      |  |

| Instruction execution time        | 4.44 $\mu$ s (with 4.5 MHz crystal resonator)                                                                                                                                                                                                                     |                                        |  |

| Stack levels                      | Address stack: 5 levels (stack operati     Interrupt stack: 2 levels (stack operati                                                                                                                                                                               | ,                                      |  |

| General-purpose ports             | <ul><li>I/O ports: 14 pins</li><li>Input ports: 8 pins</li><li>Output ports: 8 pins (+20: LCD segments)</li></ul>                                                                                                                                                 | ent pin)                               |  |

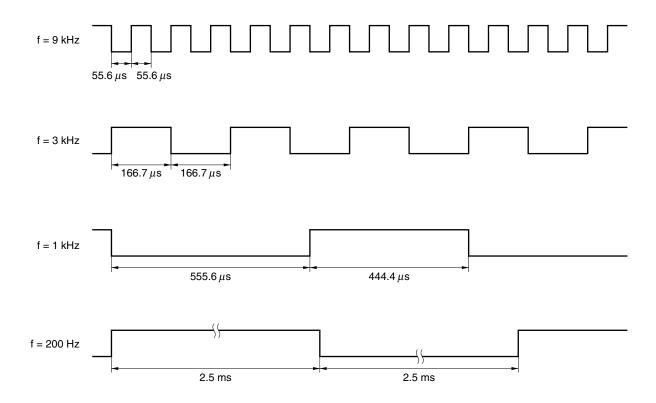

| BEEP output                       | 2 pins (frequency can be set individually) Selectable frequency (200 Hz, 1 kHz, 3 kHz, 9 kHz)                                                                                                                                                                     |                                        |  |

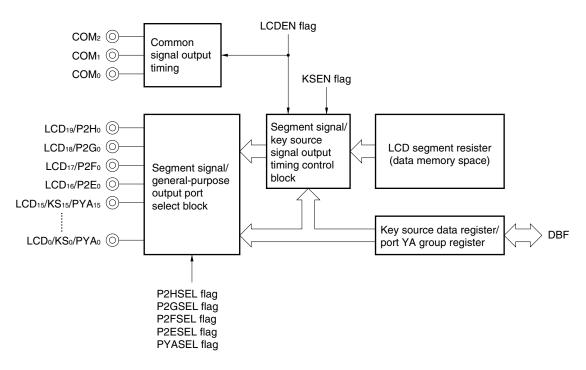

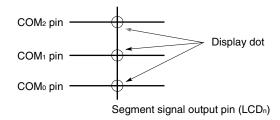

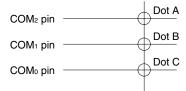

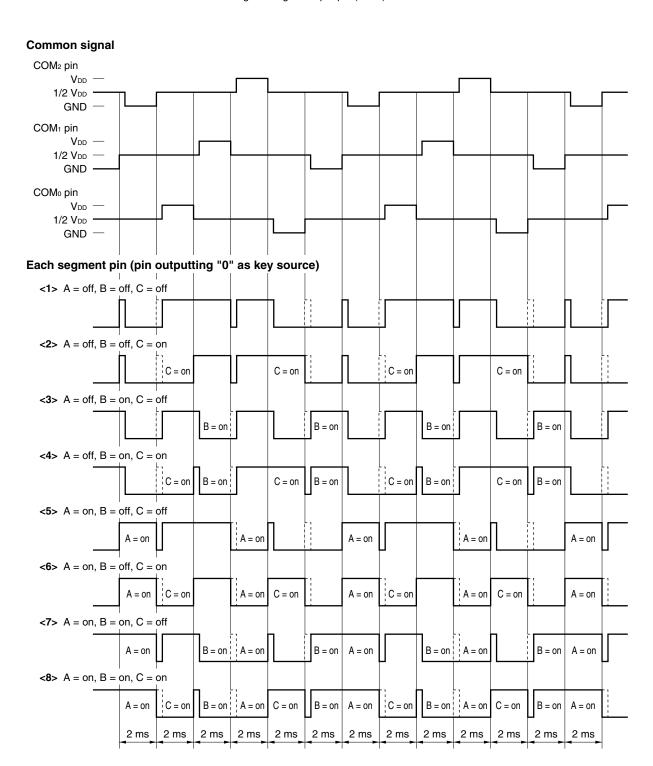

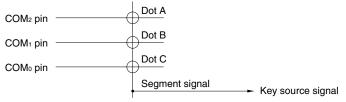

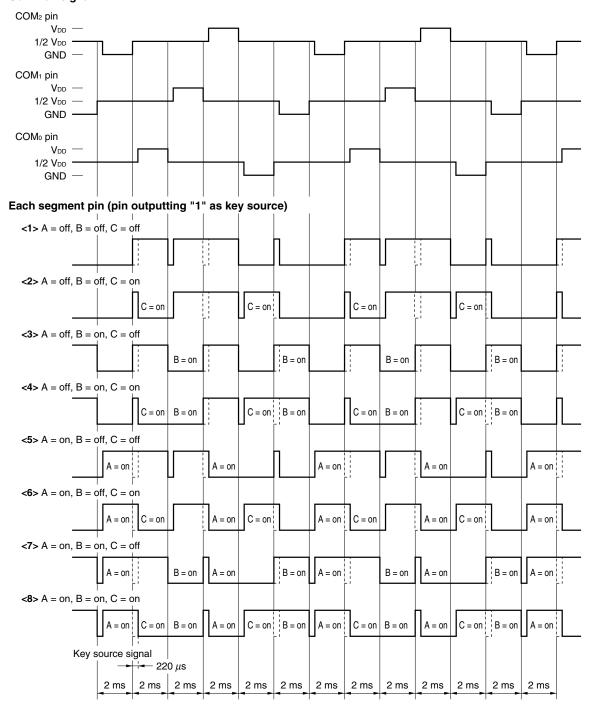

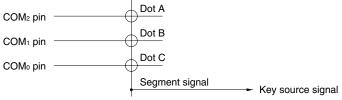

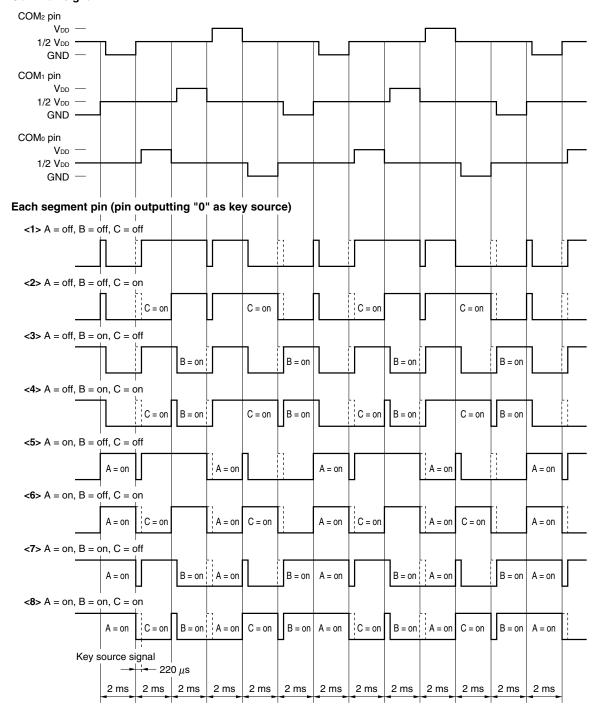

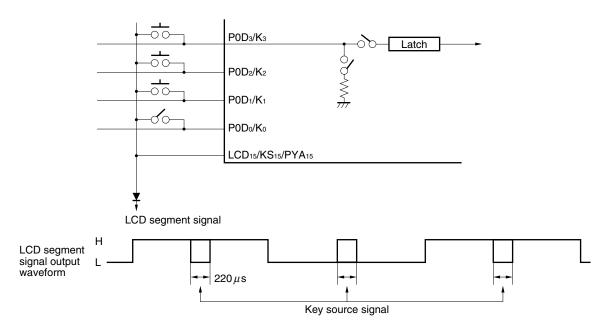

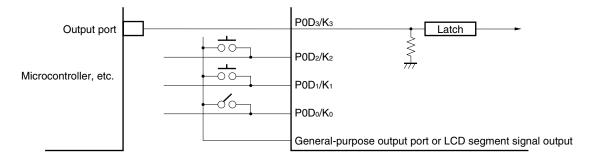

| LCD controller/driver             | 20 segments, 3 commons  1/3 duty, 1/2 bias, frame frequency: 167 Hz, drive voltage: VDD, segment pins also used as key source pins: 16  All 20 pins can be used as output port pins  (4 pins can be set in output mode individually and the rest are set at once) |                                        |  |

| Serial interface                  | 1 channel<br>3-wire (serial I/O)                                                                                                                                                                                                                                  |                                        |  |

| D/A converter                     | 8 bits × 2 channels (PWM output)                                                                                                                                                                                                                                  |                                        |  |

| A/D converter                     | 6 bits × 2 channels (successive approxin                                                                                                                                                                                                                          | nation method by software)             |  |

| Interrupts                        | 4 (maskable) External: 1 (INT pin) Internal: 3 (timer × 2, serial interface)                                                                                                                                                                                      |                                        |  |

| Timer                             | 3 channels<br>12-bit timer (10, 50 μs)<br>Basic timer 0 (1, 5, 100, 250 ms)<br>Basic timer 1 (1, 5, 100, 250 ms)                                                                                                                                                  |                                        |  |

| Reset                             | <ul> <li>Power-on reset (on power application</li> <li>Reset by CE pin (CE pin low level →</li> <li>Power failure detection function</li> </ul>                                                                                                                   |                                        |  |

| Item                      |                     | μPD17012                                                                                                                                                                                                                                                    | μPD17P012                                     |  |

|---------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| PLL frequency synthesizer | Division mode       | Pulse swallow mode (VCOL pin:                                                                                                                                                                                                                               | 20 MHz MAX.)<br>30 MHz MAX.)<br>250 MHz MAX.) |  |

|                           | Reference frequency | 12 programmable frequencies<br>1, 1.25, 2.5, 3, 5, 6.25, 9, 10, 12.5, 2                                                                                                                                                                                     | 25, 50, 100 kHz                               |  |

|                           | Charge pump         | Error-out outputs: 1                                                                                                                                                                                                                                        |                                               |  |

|                           | Phase comparator    | Unlock detection by program                                                                                                                                                                                                                                 |                                               |  |

| Frequency counter         |                     | Frequency measurement     P1B <sub>3</sub> /FMIFC pin: In FMIF mode 5.1     In AMIF mode 0.3     P1B <sub>2</sub> /AMIFC pin: 0.3 to 1 MHz     External gate width measurement P0B <sub>3</sub> /FCG <sub>1</sub> , P0B <sub>2</sub> /FCG <sub>0</sub> pins |                                               |  |

| Supply voltage            |                     | $V_{DD} = 5 \text{ V } \pm 10\%$                                                                                                                                                                                                                            |                                               |  |

| Package                   |                     | 64-pin plastic QFP (14 $\times$ 20)<br>80-pin plastic QFP (14 $\times$ 14)                                                                                                                                                                                  |                                               |  |

3

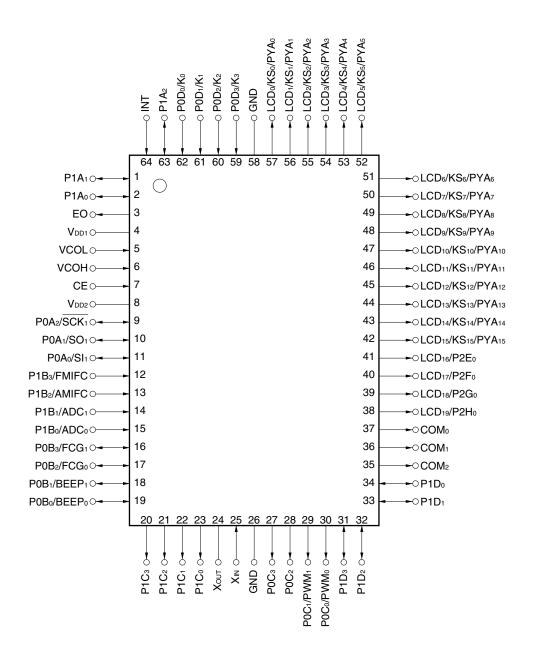

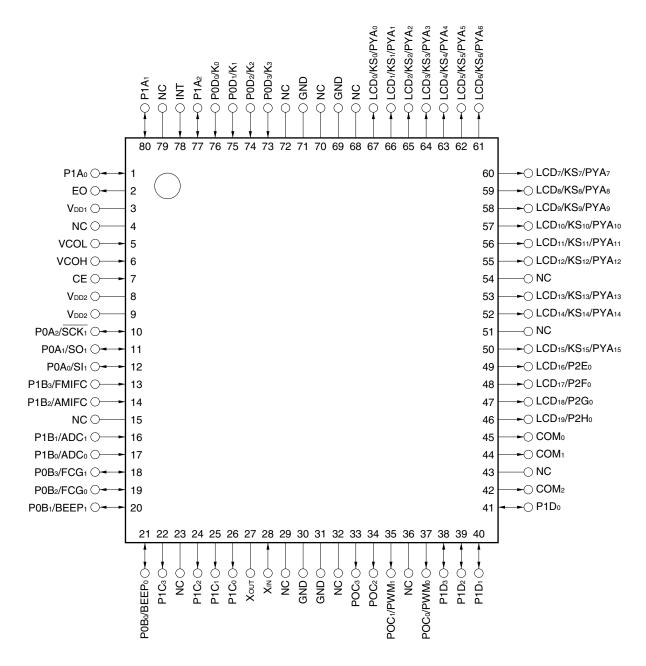

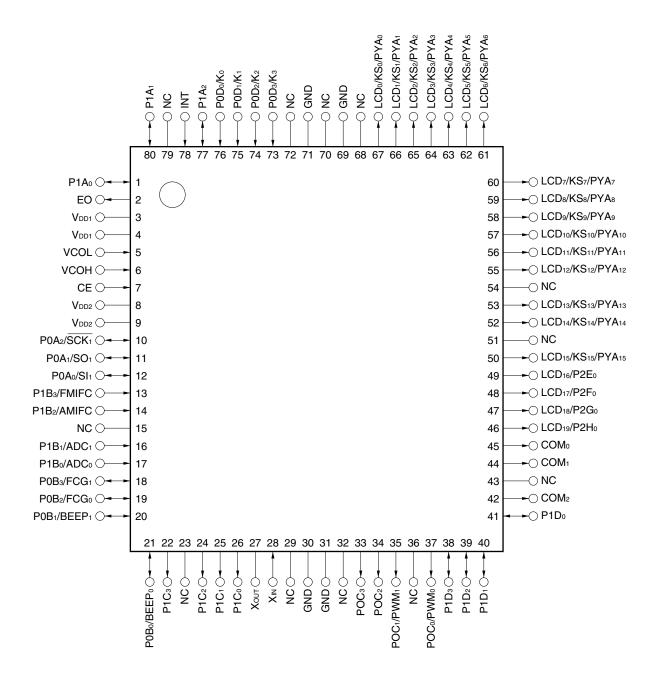

#### **PIN CONFIGURATION (TOP VIEW)**

(1)  $\mu$ PD17012 64-pin plastic QFP (14 × 20)  $\mu$ PD17012GF-×××-3BE

## 80-pin plastic QFP (14 imes 14)

$\mu$ PD17012GC-×××-8BT

Caution Pin 4 can also be used as the V<sub>DD1</sub> pin.

Use pin 4 as the V<sub>DD1</sub> pin when using the  $\mu$ PD17012 and  $\mu$ PD17P012 on the same board.

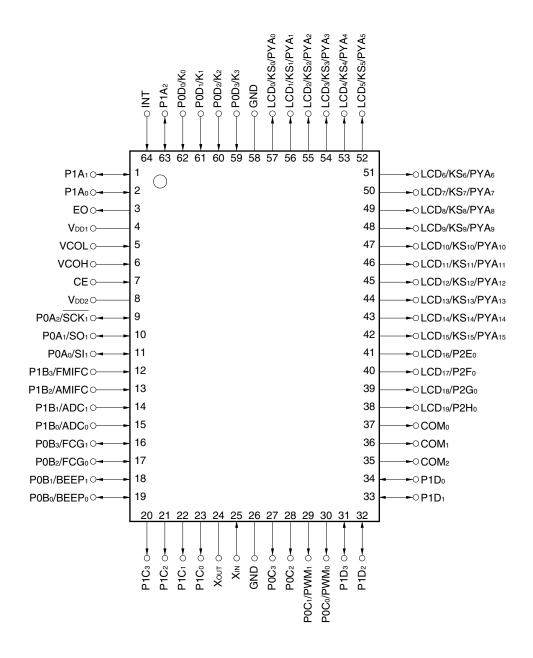

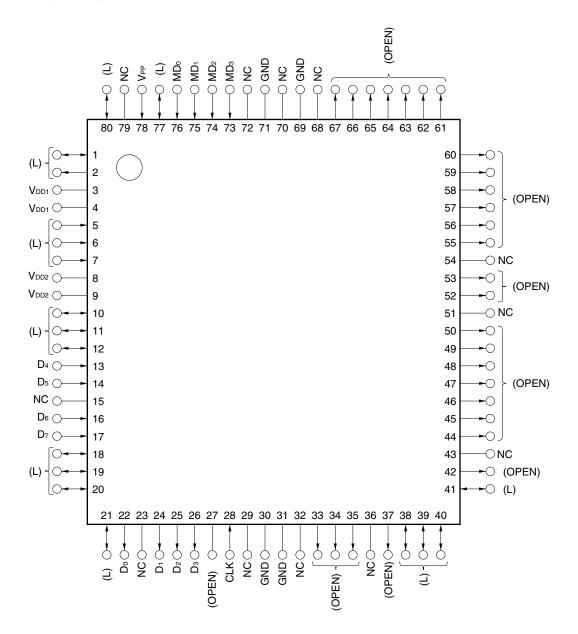

- (2)  $\mu$ PD17P012

- $\star$  64-pin plastic QFP (14 × 20)  $\mu$ PD17P012GF-3BE

- (a) Normal operation mode

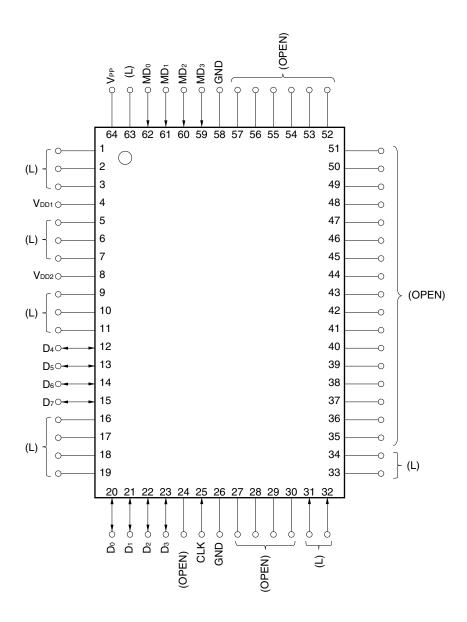

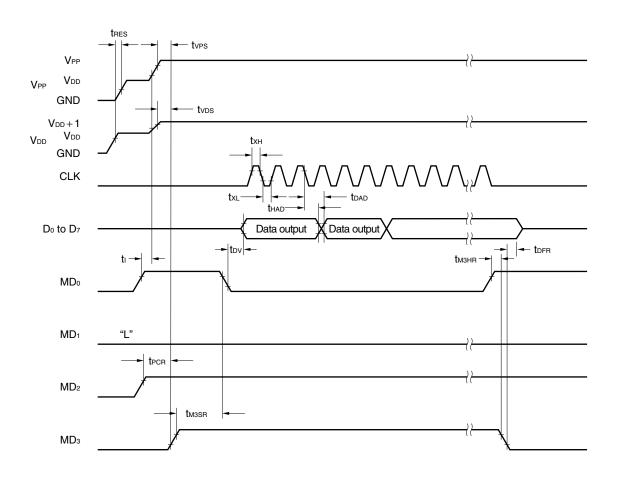

#### (b) PROM programming mode

Caution The items in parentheses indicates the processing of pins not used in the PROM programming mode.

L: Independently connect to GND via a resistor

OPEN: Leave open.

# \* 80-pin plastic QFP (14 x 14)

μPD17P012GC-8BT

#### (a) Normal operation mode

#### (b) PROM programming mode

Caution The items in parentheses indicates the processing of pins not used in the PROM programming mode.

L: Independently connect to GND via a resistor

OPEN: Leave open.

#### PIN IDENTIFICATION

ADC0, ADC1: A/D converter input P0B0 to P0B3: Port 0B

AMIFC: AM intermediate frequency counter input P0D0 to P0D3: Port 0D

BEEPo, BEEP1: BEEP output

CE: Chip enable input

CLK: Address update clock input

COMo to COM2: LCD common signal output

P1Ao to P1A2: Port 1A

P1Bo to P1B3: Port 1B

P1Co to P1C3: Port 1C

P1Co to P1C3: Port 2E

Do to D7: Data I/O P2Fo: Port 2F

EO: Error out output P2Go: Port 2G

FCGo, FCG1: External gate counter input P2Ho: Port 2H

FMIFC: FM intermediate frequency PWMo, PWM1: D/A converter output

counter input PYA<sub>0</sub> to PYA<sub>15</sub>: Port YA

GND: Ground  $\overline{SCK_1}$ : Serial clock I/O INT: External interrupt input SI1: Serial data input Ko to K3: Key source signal input SO1: Serial data output

KS<sub>0</sub> to KS<sub>15</sub>: Key source signal output VCOH: Local oscillation high input LCD<sub>0</sub> to LCD<sub>19</sub>: LCD segment signal output VCOL: Local oscillation low input

NC: No connection VDD1, VDD2: Power supply

MD $_0$  to MD $_3$ : Operation mode selection VPP: Program voltage application P0A $_0$  to P0A $_2$ : Port 0A XIN, XOUT: Crystal resonator connection

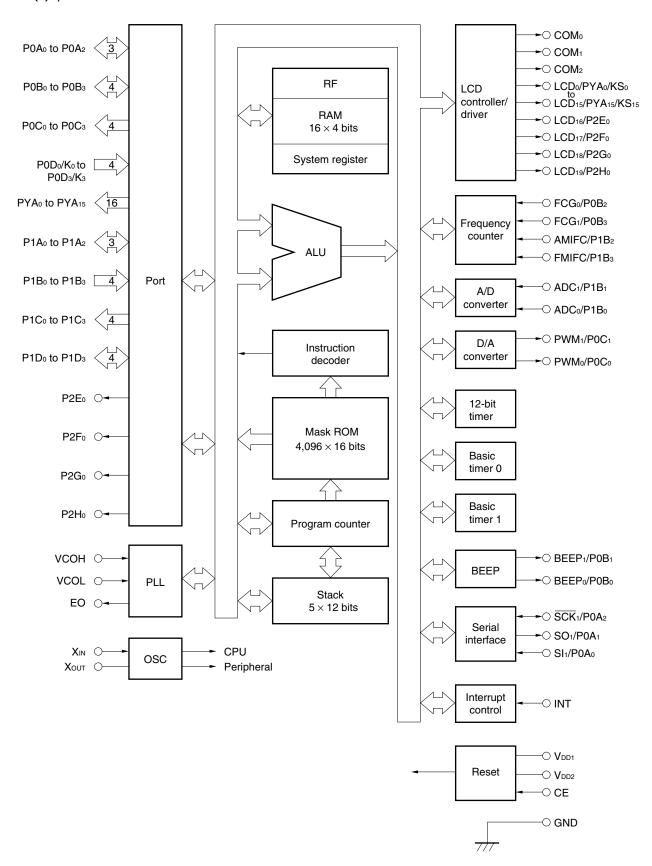

#### **BLOCK DIAGRAM**

#### (1) $\mu$ PD17012

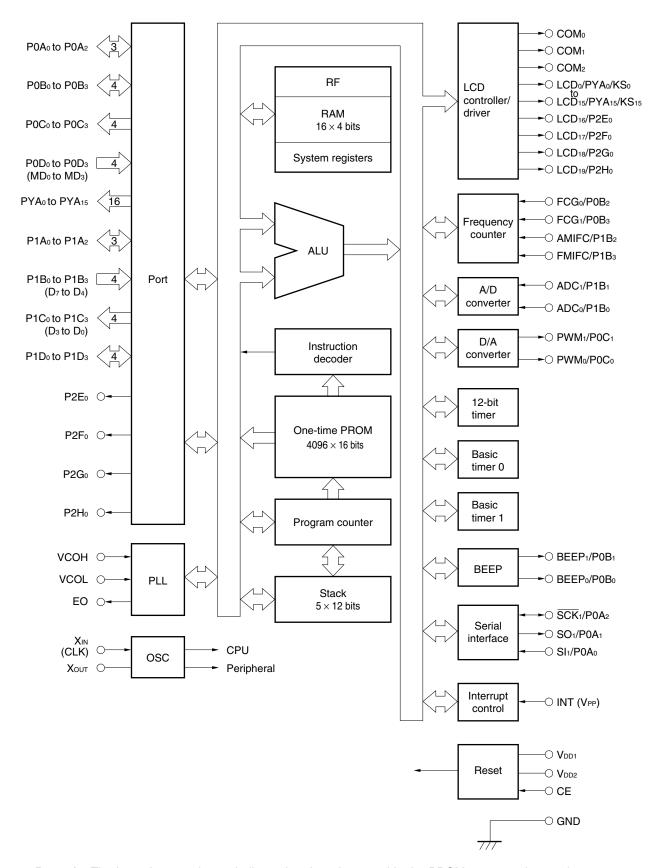

#### \* (2) $\mu$ PD17P012

Remark The items in parentheses indicate the pins when used in the PROM programming mode.

# **CONTENTS**

| PIN F | UNCTIONS                                                                                                                                                                                                                  | 18                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1.1   | Pin Function List                                                                                                                                                                                                         | 18                          |

| 1.2   | Pin Equivalent Circuits                                                                                                                                                                                                   | 21                          |

| 1.3   | Recommended Connection of Unused Pins                                                                                                                                                                                     | 25                          |

| 1.4   | Notes on Using CE and INT Pins                                                                                                                                                                                            | 26                          |

| PRO   | GRAM MEMORY (ROM)                                                                                                                                                                                                         | 27                          |

| 2.1   | Outline of Program Memory                                                                                                                                                                                                 | 27                          |

| 2.2   | Program Memory                                                                                                                                                                                                            | 28                          |

| 2.3   | Program Counter                                                                                                                                                                                                           | 28                          |

| 2.4   | Program Flow                                                                                                                                                                                                              | 29                          |

| ADD   | RESS STACK (ASK)                                                                                                                                                                                                          | 31                          |

| 3.1   | Outline of Address Stack                                                                                                                                                                                                  | 31                          |

| 3.2   | Address Stack Registers (ASR)                                                                                                                                                                                             | 31                          |

| 3.3   | Stack Pointer (SP)                                                                                                                                                                                                        | 32                          |

| 3.4   | Operation of Address Stack                                                                                                                                                                                                | 33                          |

| 3.5   | Notes on Using Address Stack                                                                                                                                                                                              | 33                          |

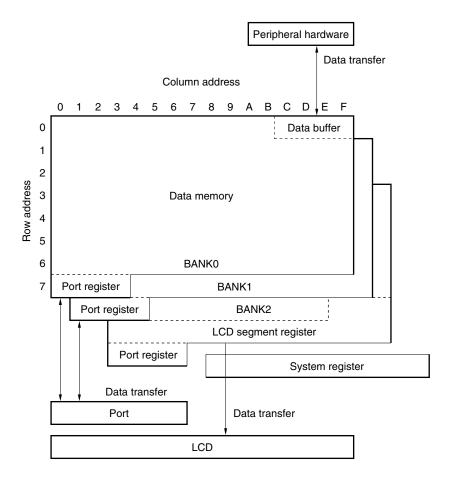

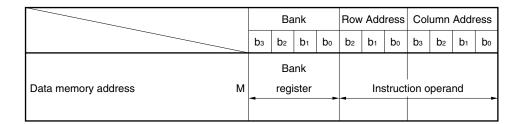

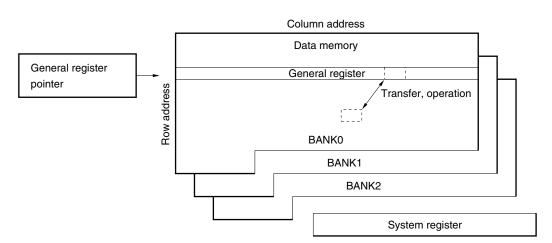

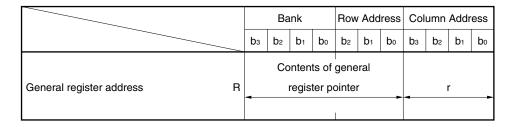

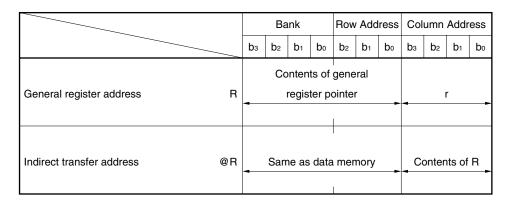

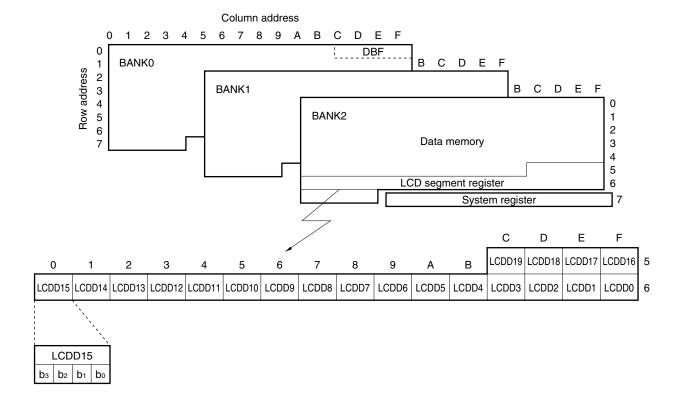

| DATA  | MEMORY (RAM)                                                                                                                                                                                                              | 34                          |

| 4.1   | Outline of Data Memory                                                                                                                                                                                                    | 34                          |

| 4.2   | Configuration and Function of Data Memory                                                                                                                                                                                 | 35                          |

| 4.3   | Addressing of Data Memory                                                                                                                                                                                                 | 37                          |

| 4.4   | Notes on Using Data Memory                                                                                                                                                                                                | 38                          |

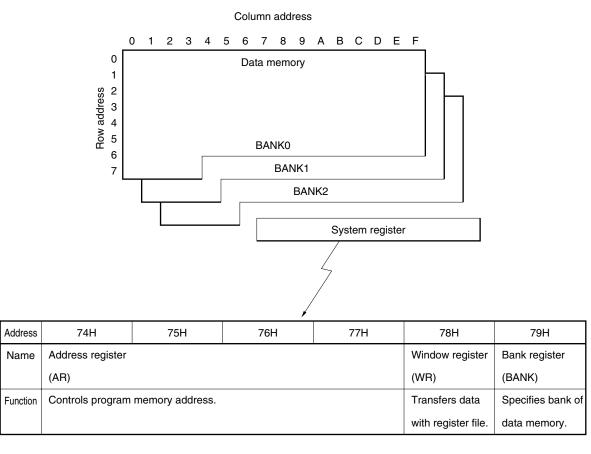

| SYST  | TEM REGISTER (SYSREG)                                                                                                                                                                                                     | 39                          |

| 5.1   | Outline of System Register                                                                                                                                                                                                | 39                          |

| 5.2   | System Register List                                                                                                                                                                                                      | 40                          |

| 5.3   | Address Register (AR)                                                                                                                                                                                                     | 41                          |

| 5.4   |                                                                                                                                                                                                                           |                             |

| 5.5   |                                                                                                                                                                                                                           |                             |

| 5.6   |                                                                                                                                                                                                                           |                             |

| 5.7   | General Register Pointer (RP)                                                                                                                                                                                             |                             |

| 5.8   | • ,                                                                                                                                                                                                                       |                             |

| 5.9   | Notes on Using System Register                                                                                                                                                                                            |                             |

| GENI  | ERAL REGISTER (GR)                                                                                                                                                                                                        | 51                          |

| 6.1   |                                                                                                                                                                                                                           |                             |

| 6.2   | •                                                                                                                                                                                                                         |                             |

| 6.3   |                                                                                                                                                                                                                           |                             |

| 6.4   | Notes on Using General Register                                                                                                                                                                                           | 53                          |

| ALU   | (Arithmetic Logic Unit) BLOCK                                                                                                                                                                                             | 54                          |

| 7.1   | Outline of ALU Block                                                                                                                                                                                                      |                             |

|       | 1.1<br>1.2<br>1.3<br>1.4<br>PROC<br>2.1<br>2.2<br>2.3<br>2.4<br>ADDI<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>DATA<br>4.1<br>4.2<br>4.3<br>4.4<br>SYST<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>6.1<br>6.2<br>6.3<br>6.4<br>ALU | 1.2 Pin Equivalent Circuits |

|     | 7.2   | Configuration and Function of Each Block                                  | 55  |

|-----|-------|---------------------------------------------------------------------------|-----|

|     | 7.3   | ALU Processing Instruction List                                           | 55  |

|     | 7.4   | Notes on Using ALU                                                        | 59  |

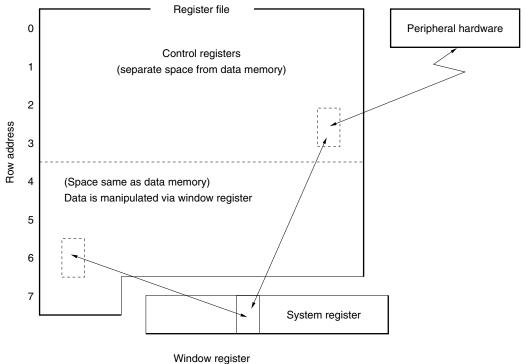

| 8.  | REGIS | STER FILE (RF)                                                            | 60  |

| •   | 8.1   | Outline of Register File                                                  |     |

|     | 8.2   | Configuration and Function of Register File                               |     |

|     | 8.3   | Register File Manipulation Instructions ("PEEK WR, rf" and "POKE rf, WR") |     |

|     | 8.4   | Control Registers                                                         |     |

|     | 8.5   | Notes on Using Register File                                              |     |

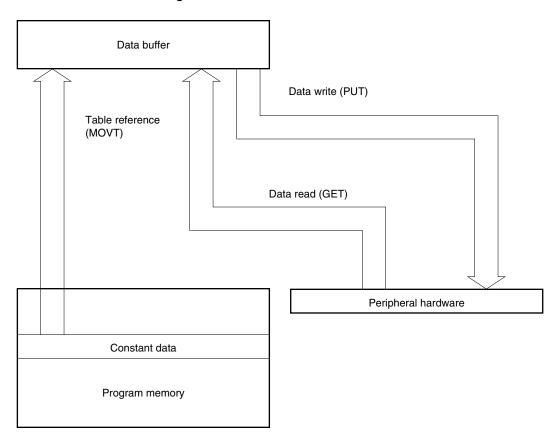

| 9.  | DATA  | BUFFER (DBF)                                                              | 69  |

| ٠.  | 9.1   | Outline of Data Buffer                                                    |     |

|     | 9.2   | Data Buffer                                                               |     |

|     | 9.3   | Peripheral Hardware and Data Buffer List                                  |     |

|     | 9.4   | Notes on Using Data Buffer                                                |     |

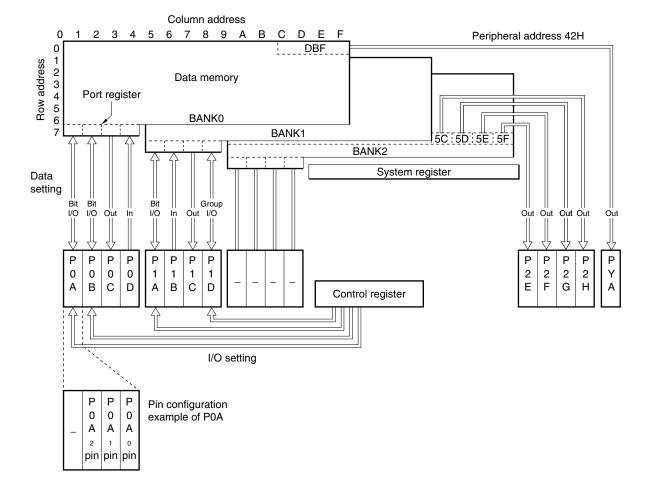

| 10  | CENE  | RAL-PURPOSE PORTS                                                         | 74  |

| 10. |       |                                                                           |     |

|     | 10.1  | Configuration and Classification of General-Purpose Ports                 |     |

|     | 10.2  | Functional Outline of General-Purpose Ports                               |     |

|     | 10.3  | General-Purpose I/O Ports (P0A, P0B, P1A, and P1D)                        |     |

|     | 10.4  | General-Purpose Input Ports (P0D and P1B)                                 |     |

|     | 10.5  | General-Purpose Output Ports (POC and P1C)                                |     |

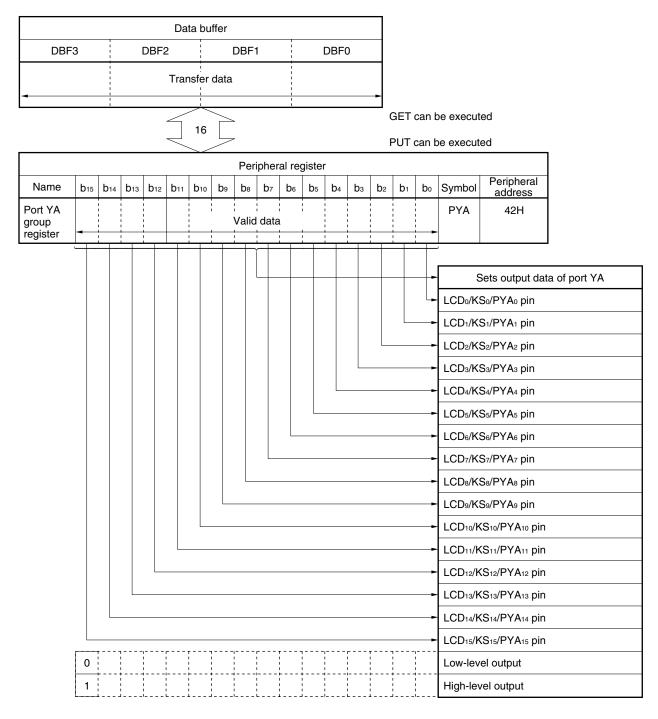

|     | 10.6  | General-Purpose Output Ports (P2E to P2H and PYA)                         | 90  |

| 11. | INTER | RRUPTS                                                                    |     |

|     | 11.1  | Outline of Interrupt Block                                                |     |

|     | 11.2  | Interrupt Control Block                                                   |     |

|     | 11.3  | Interrupt Stack Register                                                  |     |

|     | 11.4  | Stack Pointer, Address Stack Register, Program Counter                    |     |

|     | 11.5  | Interrupt Enable Flip-Flop (INTE)                                         | 104 |

|     | 11.6  | Acknowledging Interrupts                                                  |     |

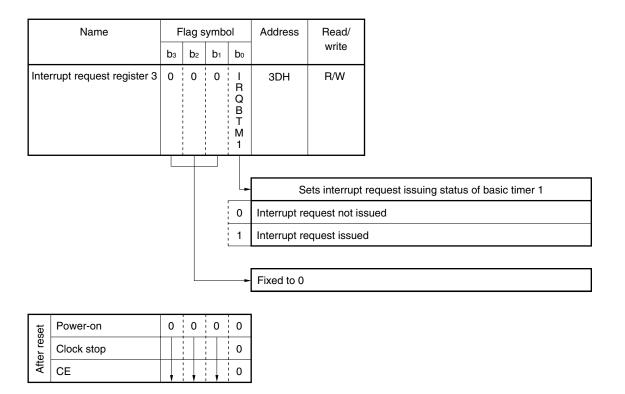

|     | 11.7  | Operations After Acknowledging Interrupt                                  | 110 |

|     | 11.8  | Restoring from Interrupt Servicing Routine                                | 110 |

|     | 11.9  | External (INT Pin) Interrupt                                              | 111 |

|     | 11.10 | Internal Interrupt                                                        | 113 |

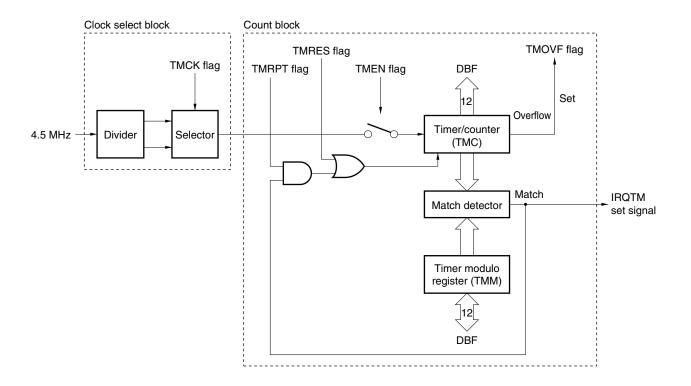

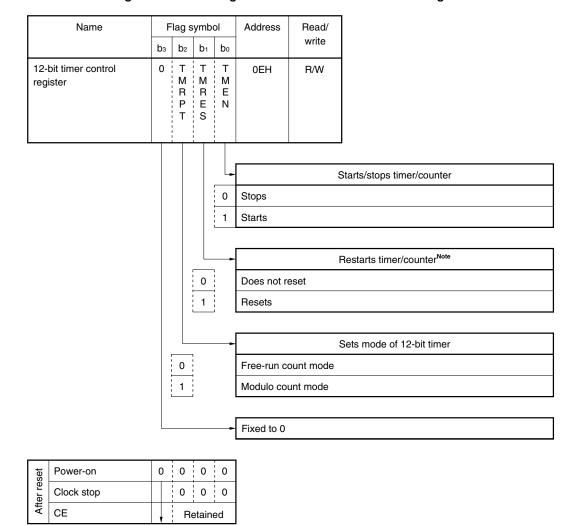

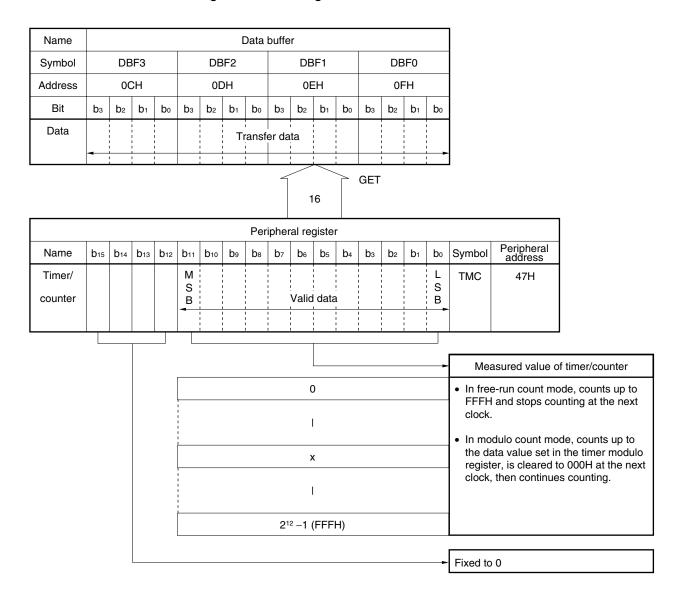

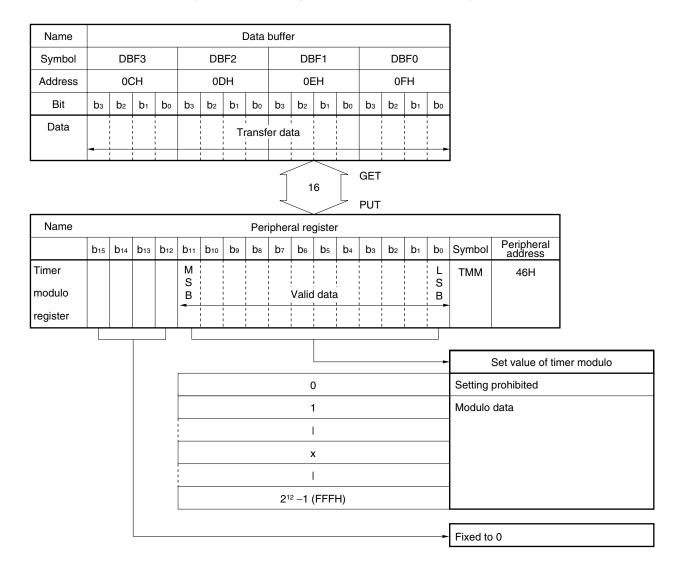

| 12. | TIME  | 3                                                                         | 114 |

|     | 12.1  | General                                                                   | 114 |

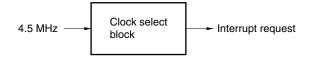

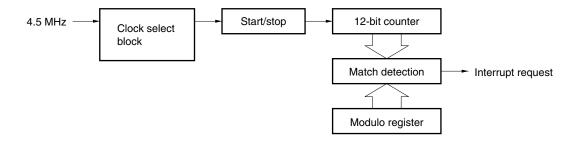

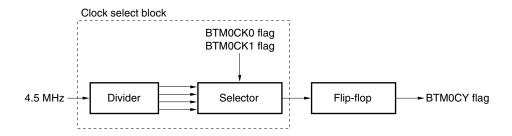

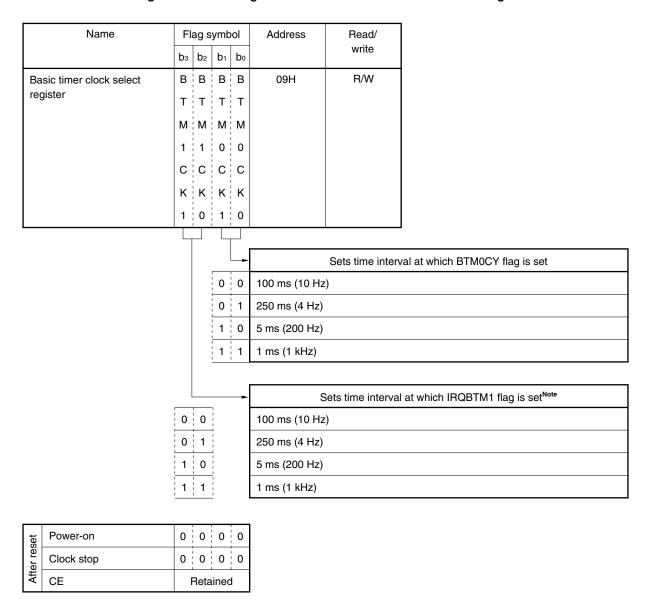

|     | 12.2  | Basic Timer 0                                                             | 115 |

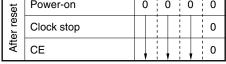

|     | 12.3  | Basic Timer 1                                                             | 128 |

|     | 12.4  | 12-Bit Timer                                                              | 136 |

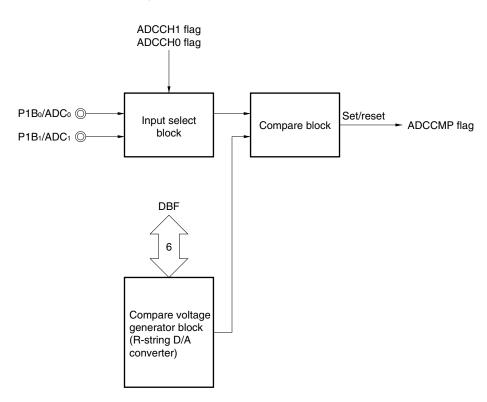

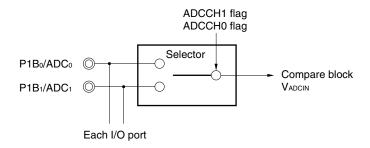

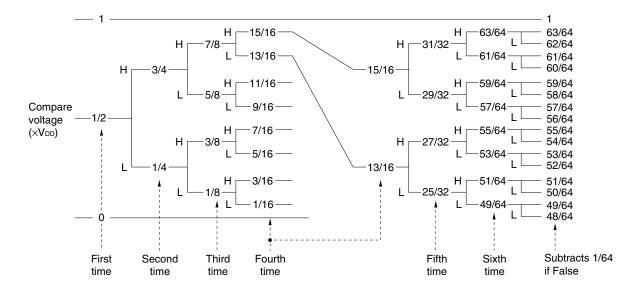

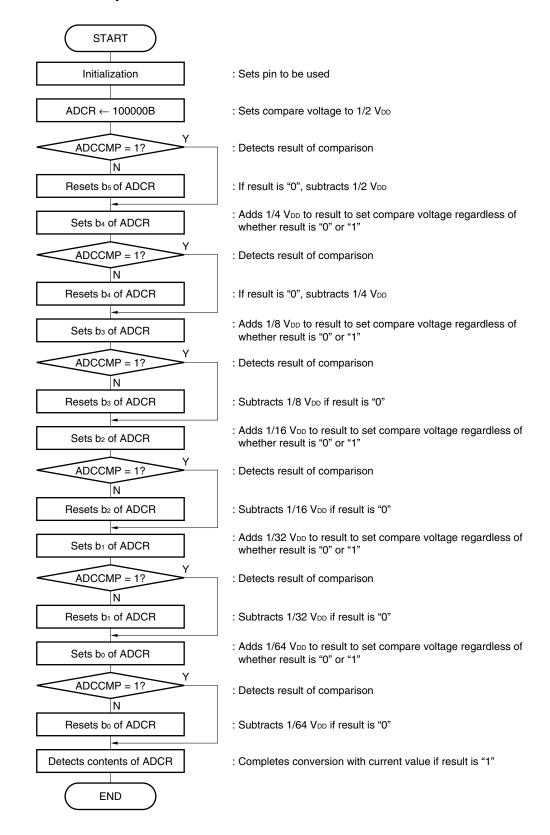

| 13. | A/D C | ONVERTER (ADC)                                                            | 144 |

|     | 13.1  | General                                                                   |     |

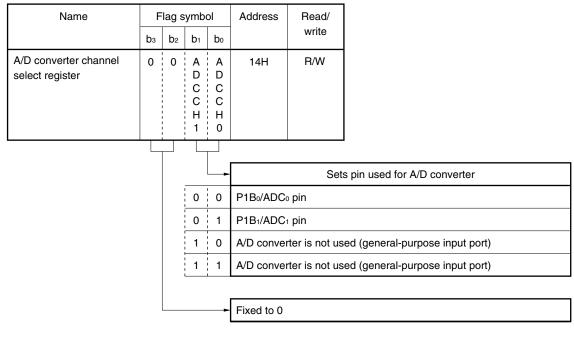

|     | 13.2  | Input Selector Block                                                      | 145 |

|     | 13.3  | Compare Voltage Generator Block and Compare Block                         | 146 |

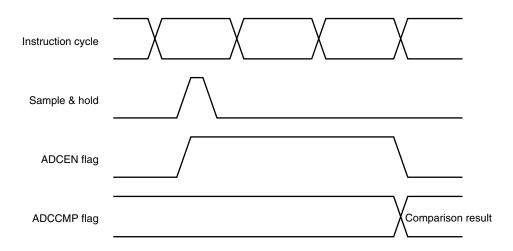

|     | 13.4  | Comparison Timing Chart                                                   | 150 |

|     | 13.5  | Performance of A/D Converter                                              | 150 |

|     | 13.6  | Using A/D Converter                                                      | 151 |

|-----|-------|--------------------------------------------------------------------------|-----|

|     | 13.7  | Status on Reset                                                          | 156 |

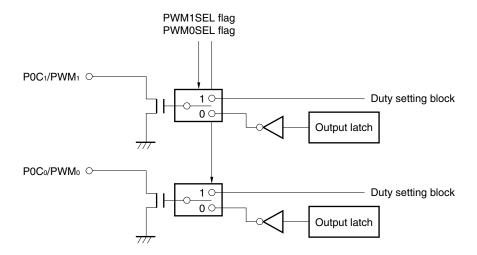

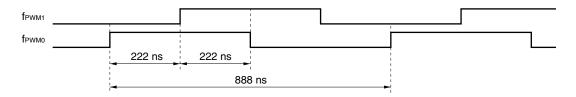

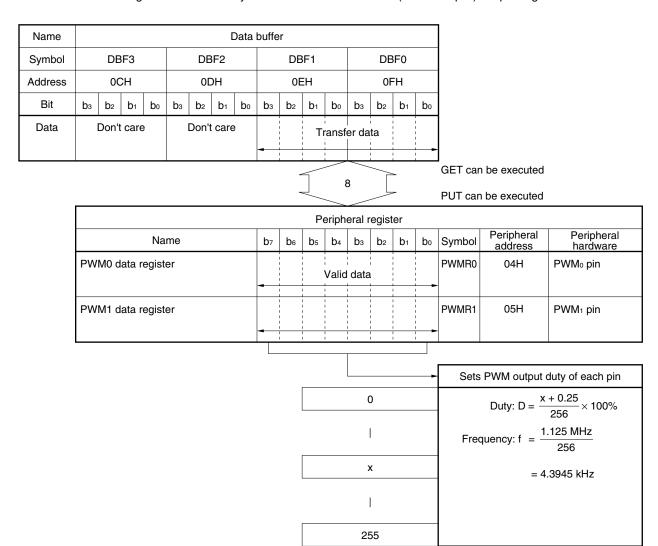

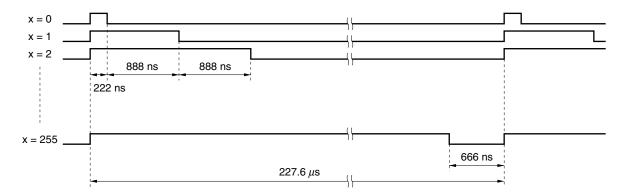

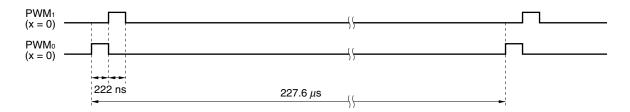

| 14  | D/A C | CONVERTER (DAC)                                                          | 157 |

| 17. | 14.1  | Configuration of D/A Converter                                           |     |

|     | 14.2  | Functional Outline of D/A Converter                                      |     |

|     | 14.3  | Output Select Blocks                                                     |     |

|     | 14.4  | Duty Setting Blocks and Clock Generation Block                           |     |

|     | 14.5  | Cautions on Using D/A Converter                                          |     |

|     | 14.6  | Status on Reset                                                          |     |

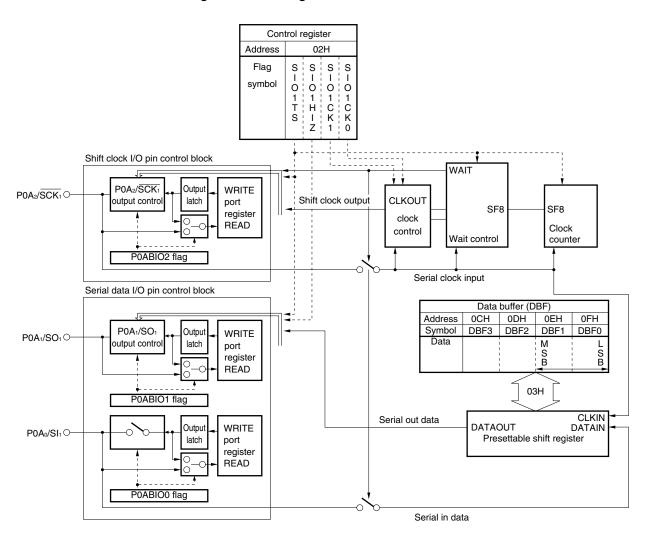

| 15. | SERI  | AL INTERFACE                                                             | 165 |

|     | 15.1  | Configuration of Serial Interface                                        | 166 |

|     | 15.2  | Functional Outline of Serial Interface                                   |     |

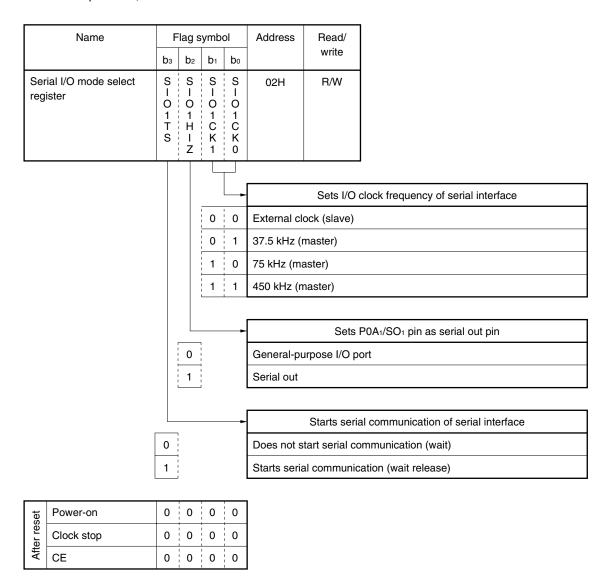

|     | 15.3  | Shift Clock and Serial Data I/O Pin Control Blocks                       | 168 |

|     | 15.4  | Clock Generation Block                                                   | 170 |

|     | 15.5  | Clock Counter                                                            | 172 |

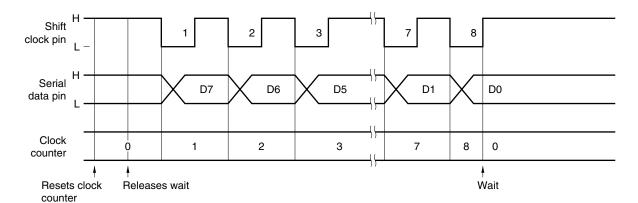

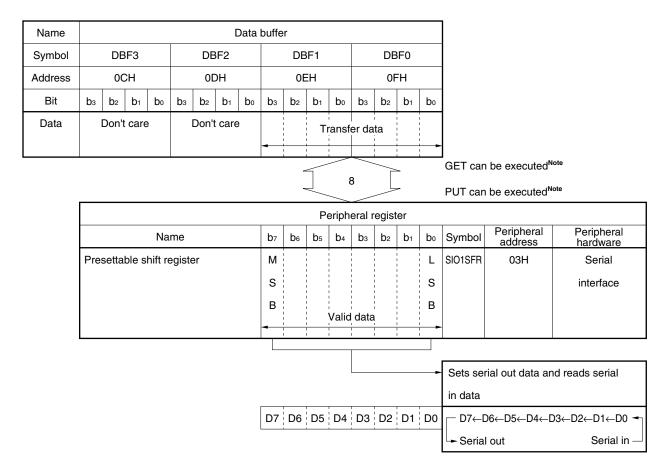

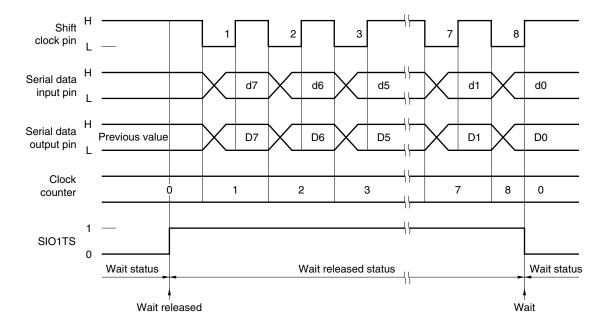

|     | 15.6  | Presettable Shift Register (SIO1SFR)                                     | 173 |

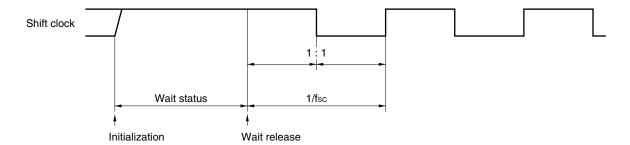

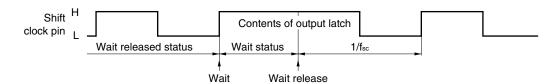

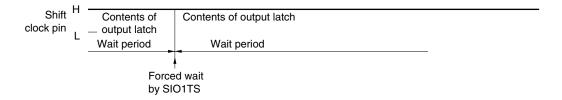

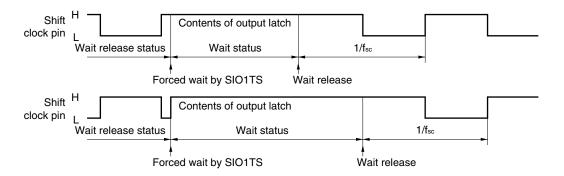

|     | 15.7  | Wait Control Block                                                       | 175 |

|     | 15.8  | Outline of Serial Interface Operation                                    | 177 |

|     | 15.9  | Status of Serial Interface on Reset                                      | 178 |

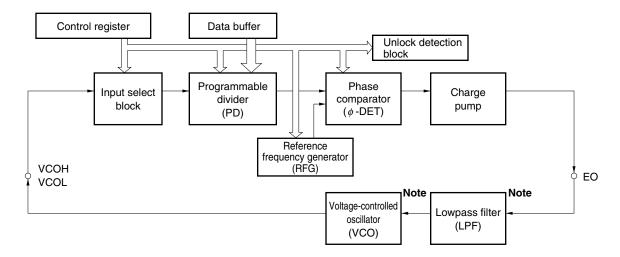

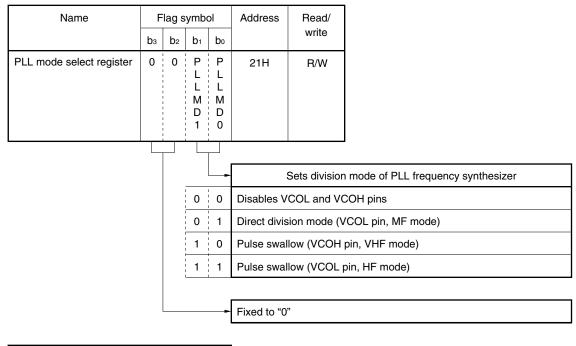

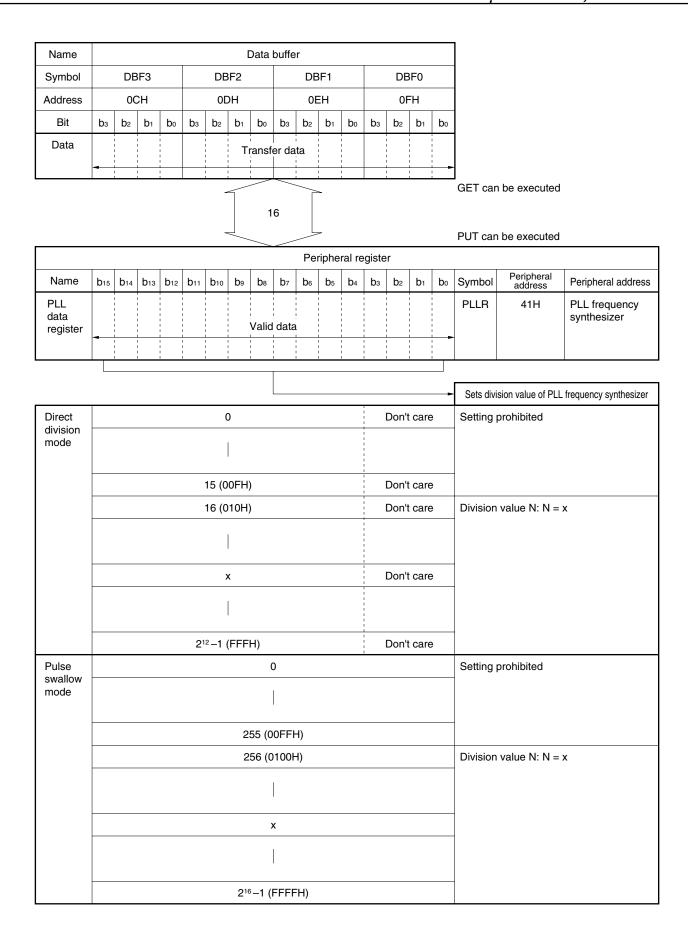

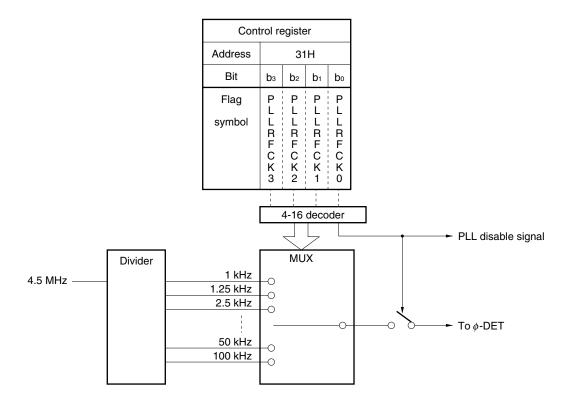

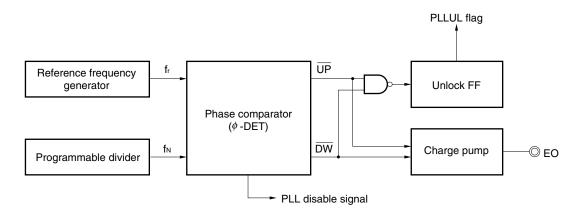

| 16. | PLL F | REQUENCY SYNTHESIZER                                                     | 179 |

|     | 16.1  | Configuration of PLL Frequency Synthesizer                               | 179 |

|     | 16.2  | Functional Outline of PLL Frequency Synthesizer                          | 180 |

|     | 16.3  | Input Select Block and Programmable Divider                              | 181 |

|     | 16.4  | Reference Frequency Generator                                            | 186 |

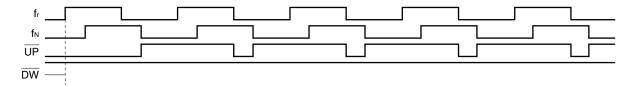

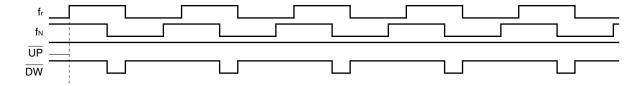

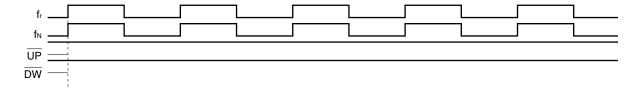

|     | 16.5  | Phase Comparator ( $\phi$ -DET), Charge Pump, and Unlock Detection Block |     |

|     | 16.6  | PLL Disabled Status                                                      |     |

|     | 16.7  | Using PLL Frequency Synthesizer                                          |     |

|     | 16.8  | Status on Reset                                                          | 195 |

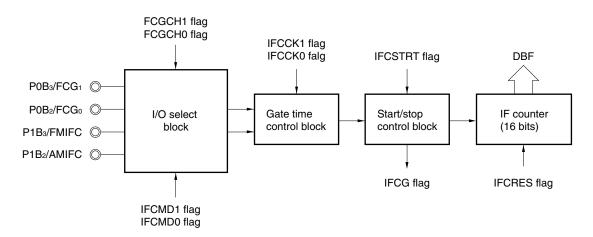

| 17. | FREG  | UENCY COUNTER                                                            | 196 |

|     | 17.1  | Outline of Frequency Counter                                             |     |

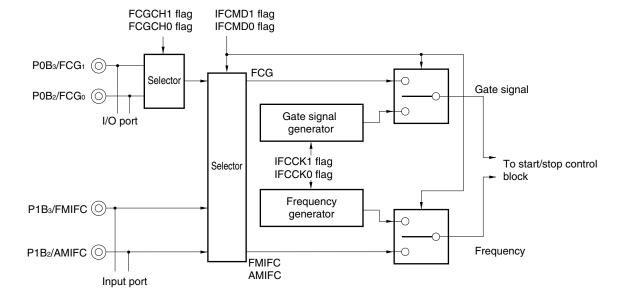

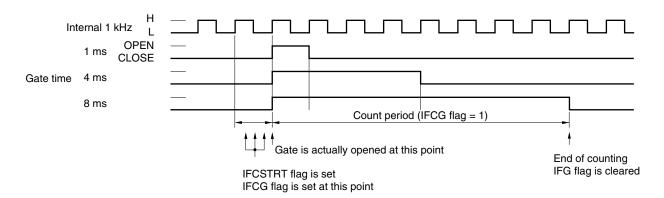

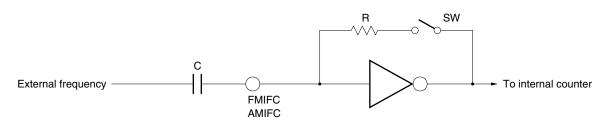

|     | 17.2  | Input/Output Select Block and Gate Time Control Block                    |     |

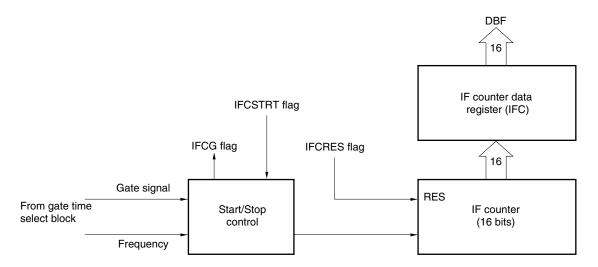

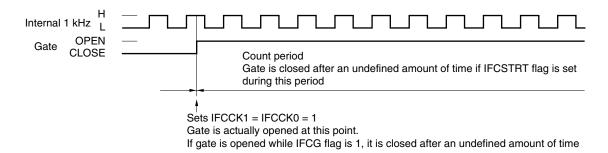

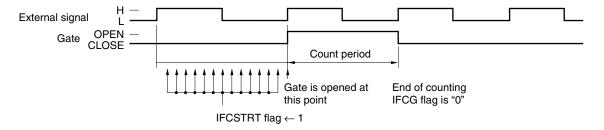

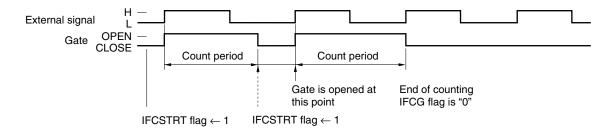

|     | 17.3  | Start/Stop Control Block and IF Counter                                  |     |

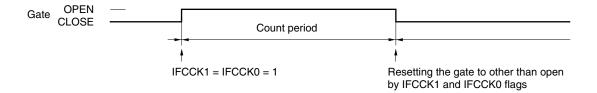

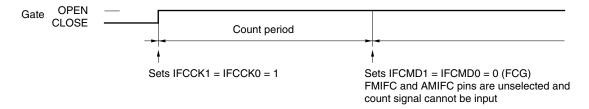

|     | 17.4  | Using IF Counter Function                                                |     |

|     | 17.5  | Error of External Gate Counter                                           |     |

|     | 17.6  | Status on Reset                                                          | 208 |

| 18. | BEEF  | )                                                                        |     |

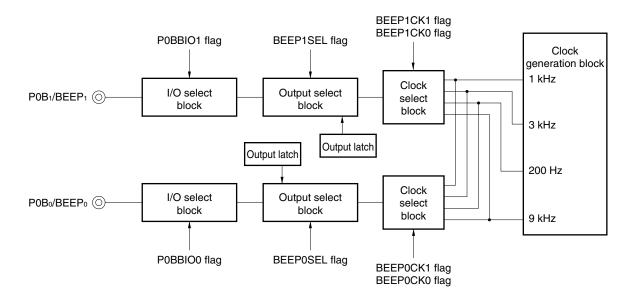

|     | 18.1  | General                                                                  |     |

|     | 18.2  | I/O Select Block and Output Select Block                                 |     |

|     | 18.3  | Clock Select Block and Clock Generator Block                             |     |

|     | 18.4  | Output Waveform of BEEP                                                  | 213 |

|     |       |                                                                          |     |

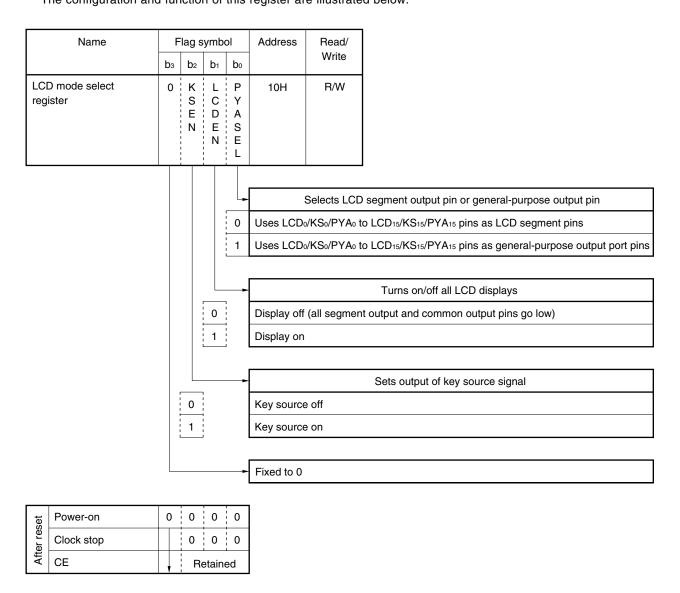

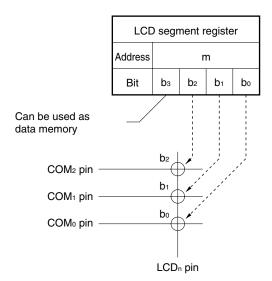

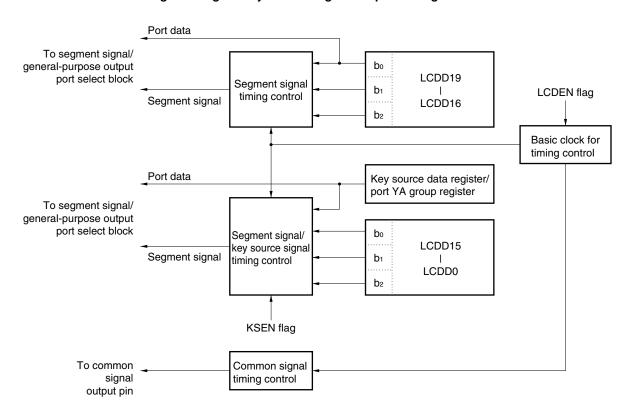

| 19. | LCD          | CONTROLLER/DRIVER                                                         | 214 |

|-----|--------------|---------------------------------------------------------------------------|-----|

|     | 19.1         | Configuration of LCD Controller/Driver                                    | 214 |

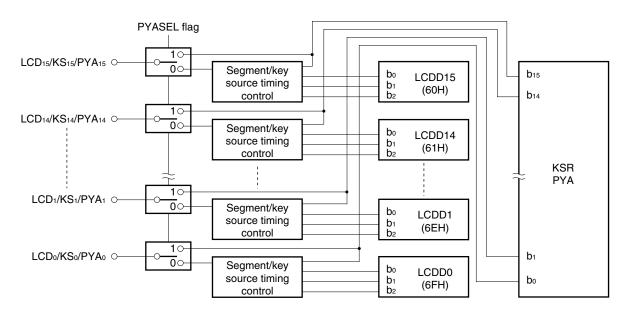

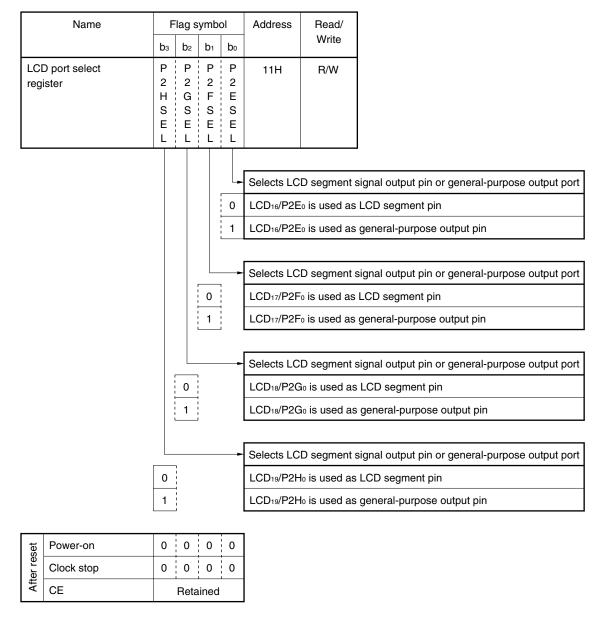

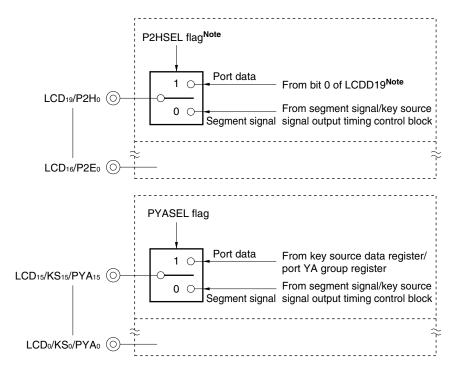

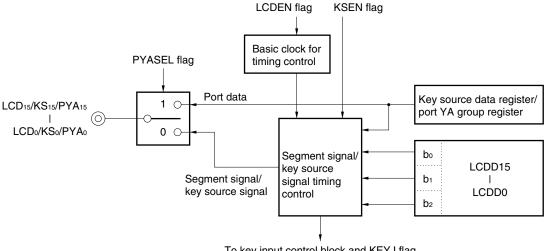

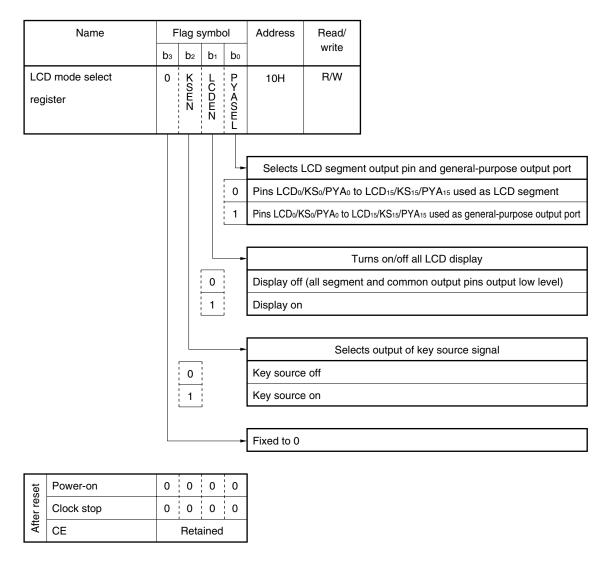

|     | 19.2         | Functional Outline of LCD Controller/Driver                               | 215 |

|     | 19.3         | LCD Segment Register                                                      | 217 |

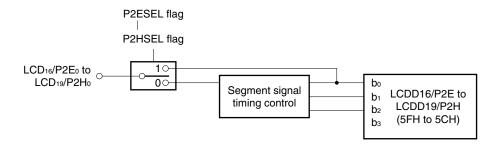

|     | 19.4         | Segment Signal/General-Purpose Output Port Select Block                   | 220 |

|     | 19.5         | Common Signal Output Timing Control Block and                             |     |

|     |              | Segment Signal/Key Source Signal Output Timing Control Block              | 222 |

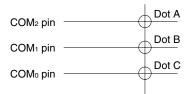

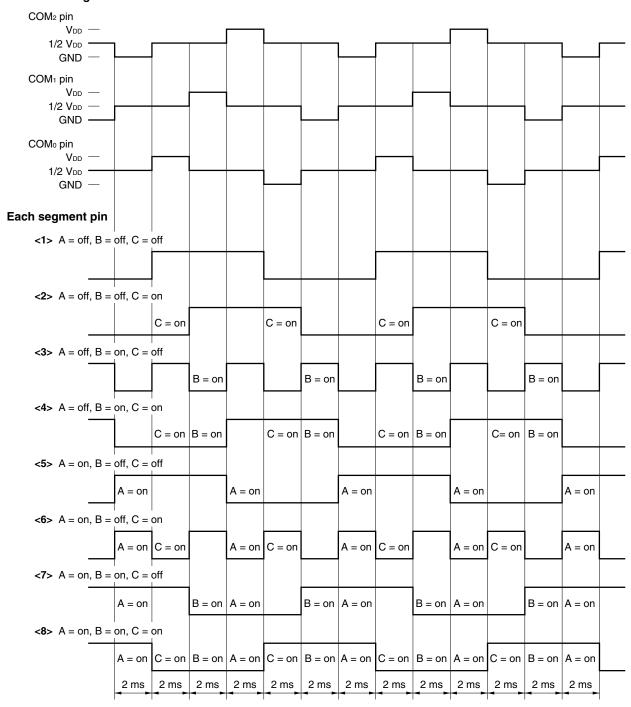

|     | 19.6         | Output Waveforms of Common and Segment Signals                            | 224 |

|     | 19.7         | Using LCD Controller/Driver                                               | 228 |

|     | 19.8         | Status on Reset                                                           | 230 |

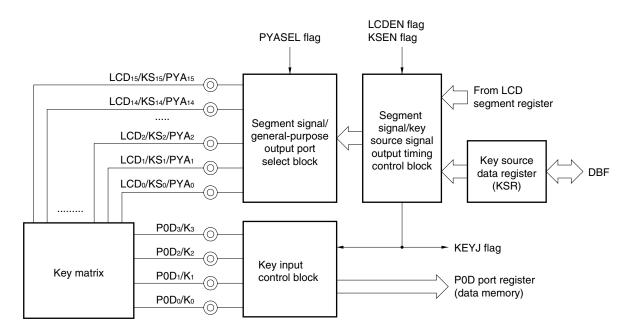

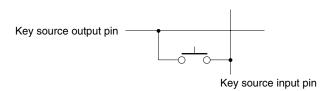

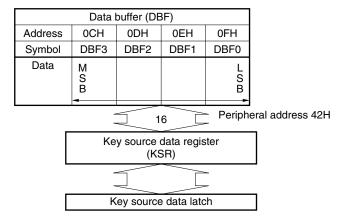

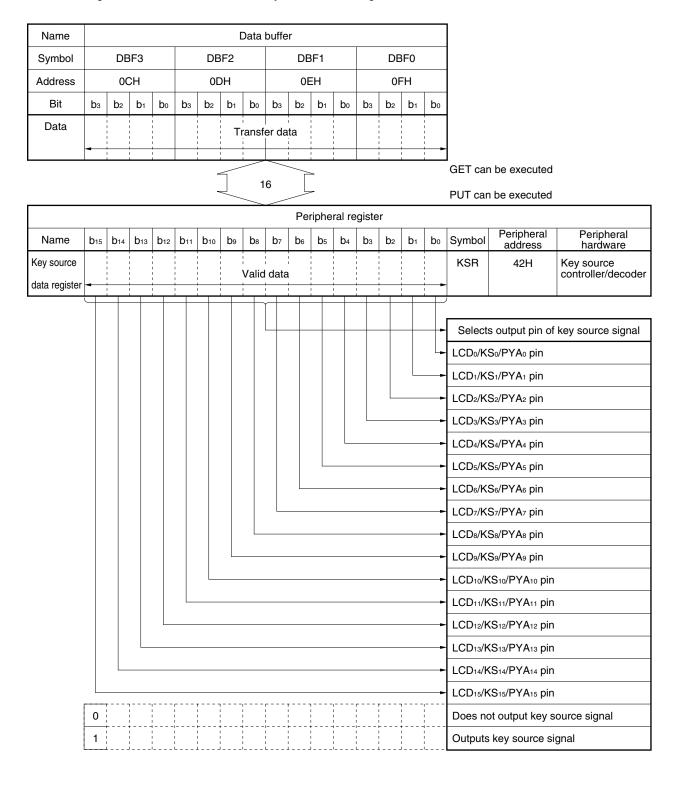

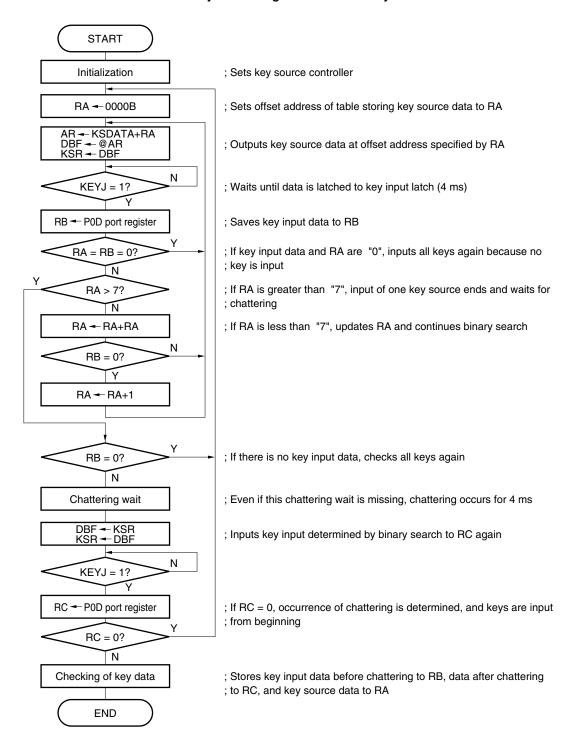

| 20. | KEY          | SOURCE CONTROLLER/DECODER                                                 |     |

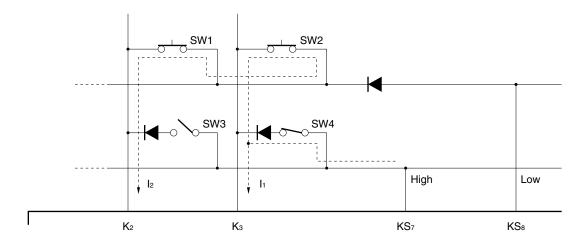

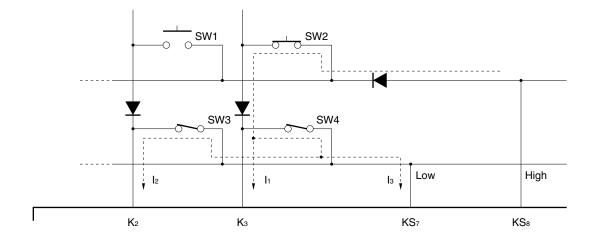

|     | 20.1         | Configuration of Key Source Controller/Decoder                            |     |

|     | 20.2         | Functional Outline of Key Source Controller/Decoder                       | 232 |

|     | 20.3         | Key Source Data Setting Block                                             |     |

|     | 20.4         | Output Timing Control Blocks and Segment/Port Select Block                |     |

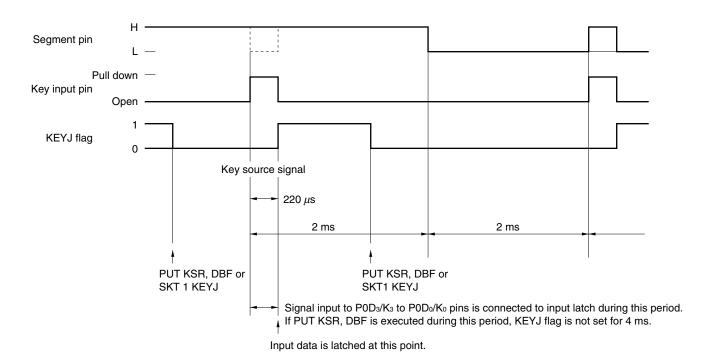

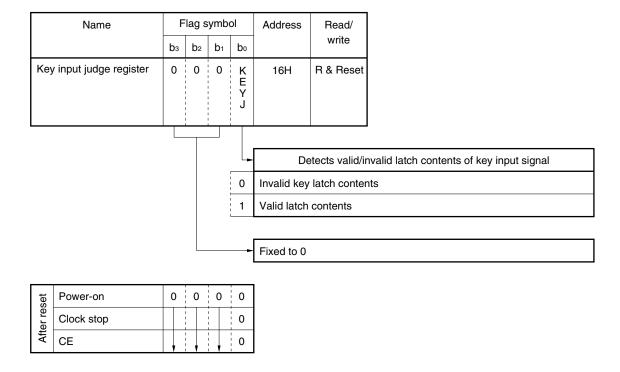

|     | 20.5         | Key Input Control Block                                                   | 239 |

|     | 20.6         | Using Key Source Controller/Decoder                                       |     |

|     | 20.7         | Status on Reset                                                           | 250 |

| 21. | STAN         | NDBY                                                                      |     |

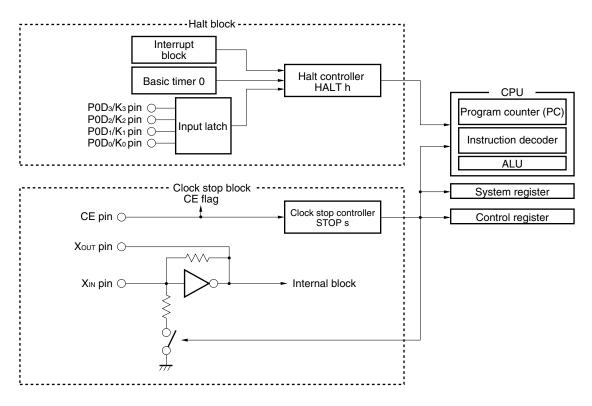

|     | 21.1         | Configuration of Standby Block                                            |     |

|     | 21.2         | Standby Function                                                          |     |

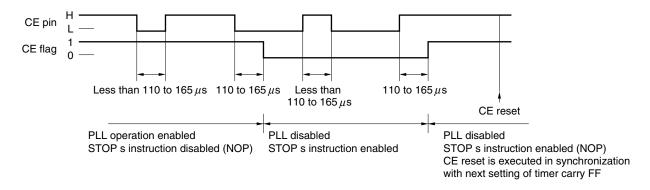

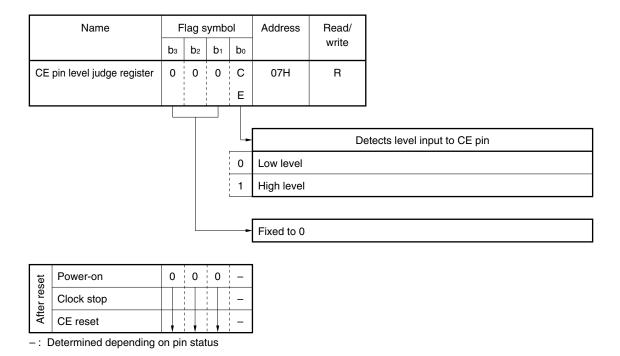

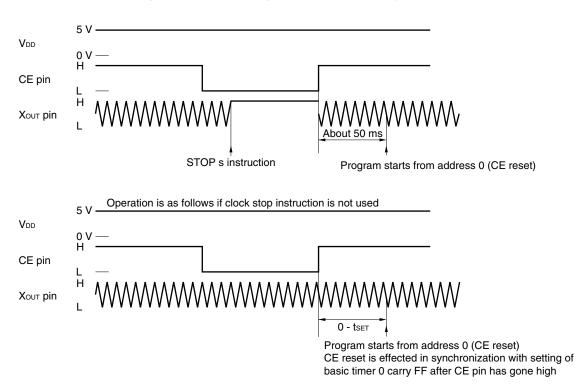

|     | 21.3         | Selecting Device Operation Mode with CE Pin                               |     |

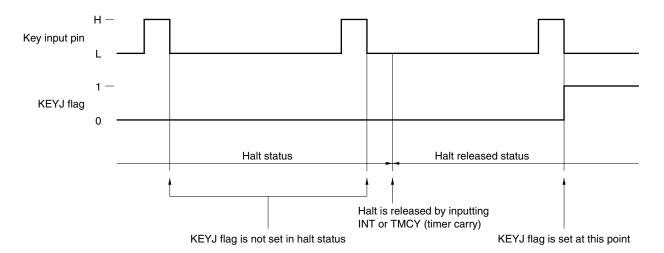

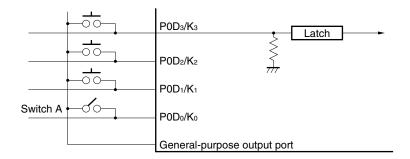

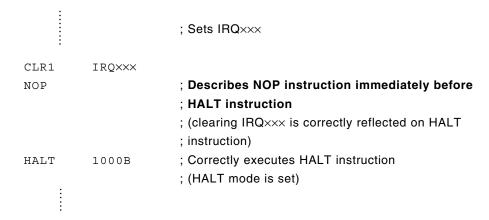

|     | 21.4         | Halt Function                                                             |     |

|     | 21.5         | Clock Stop Function                                                       |     |

|     | 21.6         | Device Operations in Halt and Clock Stop Status                           |     |

|     | 21.7         | Notes on Processing Each Pin in Halt and Clock Stop Status                | 266 |

| 22. | RESE         | ET                                                                        |     |

|     | 22.1         | Configuration of Reset Block                                              |     |

|     | 22.2         | Reset Function                                                            |     |

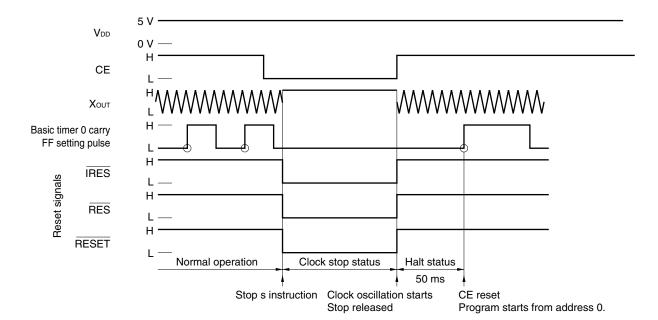

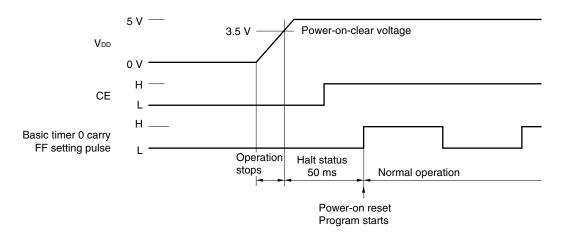

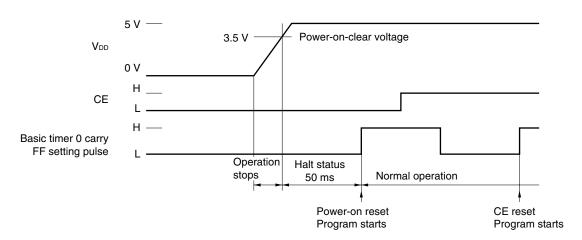

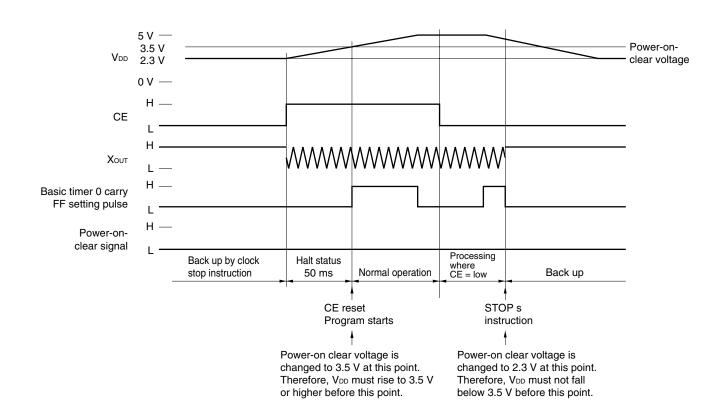

|     | 22.3         | CE Reset                                                                  |     |

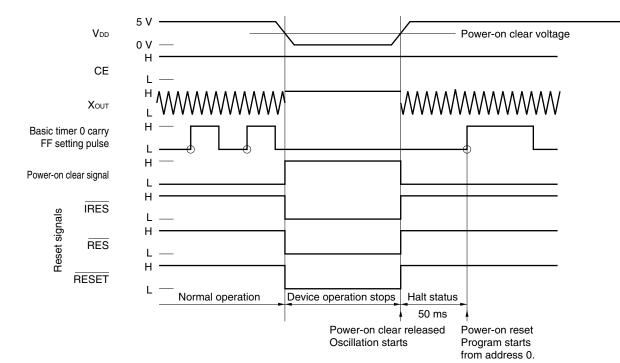

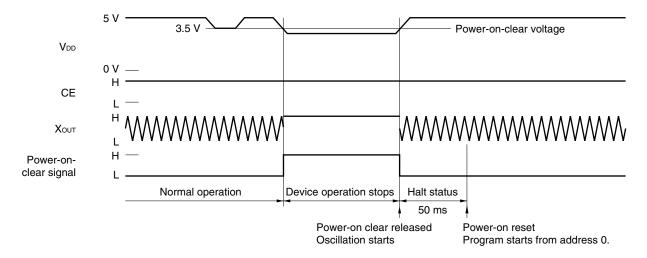

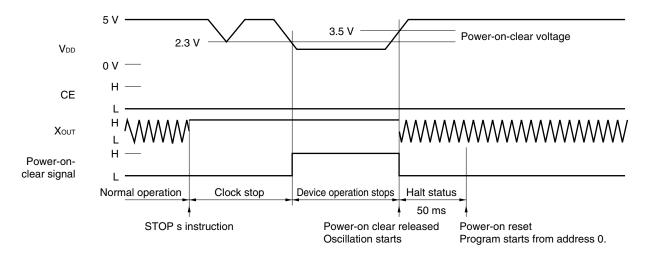

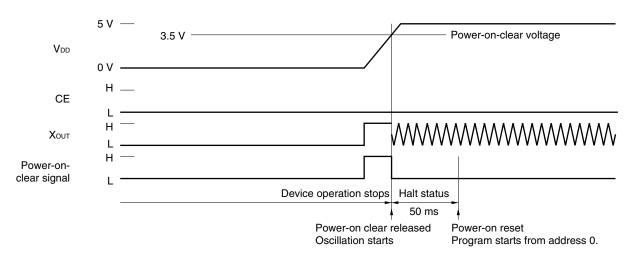

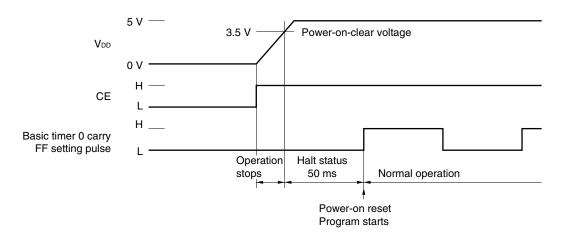

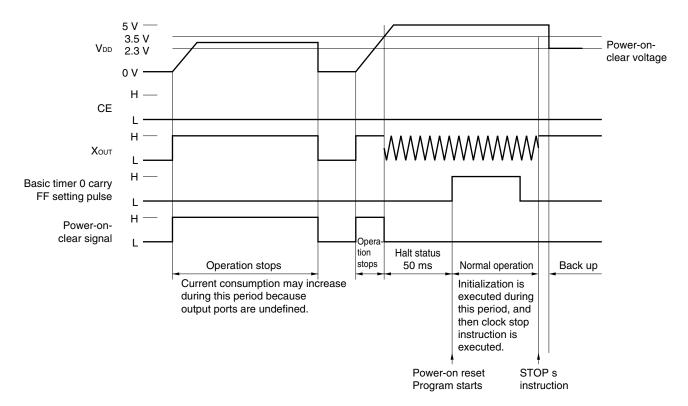

|     | 22.4         | Power-on Reset                                                            | _   |

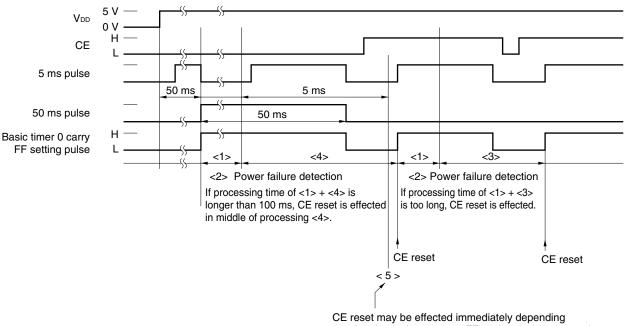

|     | 22.5<br>22.6 | Relationship Between CE Reset and Power-on Reset  Power Failure Detection |     |

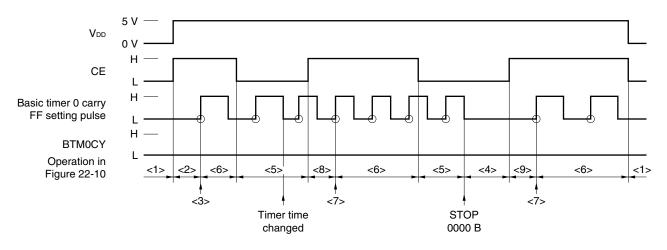

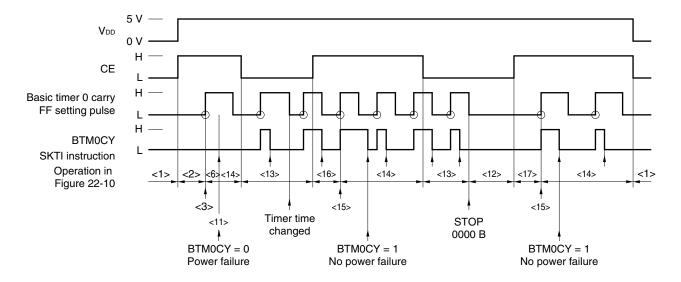

|     | 22.0         | Fower Failure Detection                                                   | 202 |

| 23. | _            | RUCTION SET                                                               |     |

|     | 23.1         | Outline of Instruction Set                                                |     |

|     | 23.2         | Legend                                                                    |     |

|     | 23.3         | Instruction Set List                                                      |     |

|     | 23.4         | Assembler (RA17K) Embedded Macro Instructions                             | 294 |

| 24. | RESE         | ERVED SYMBOLS                                                             |     |

|     | 24.1         | Data Buffer (DBF)                                                         |     |

|     | 24.2         | System Register (SYSREG)                                                  |     |

|     | 24.3         | LCD Segment Register                                                      |     |

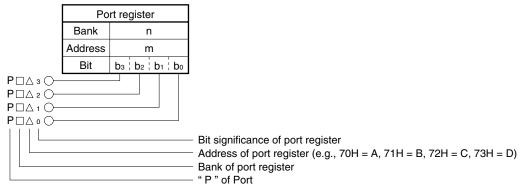

|     | 24.4         | Port Register                                                             | 297 |

|     | 24.5  | Register File (Control Register)                             | 298 |

|-----|-------|--------------------------------------------------------------|-----|

|     |       | Peripheral Hardware Register                                 |     |

|     | 24.7  | Others                                                       | 300 |

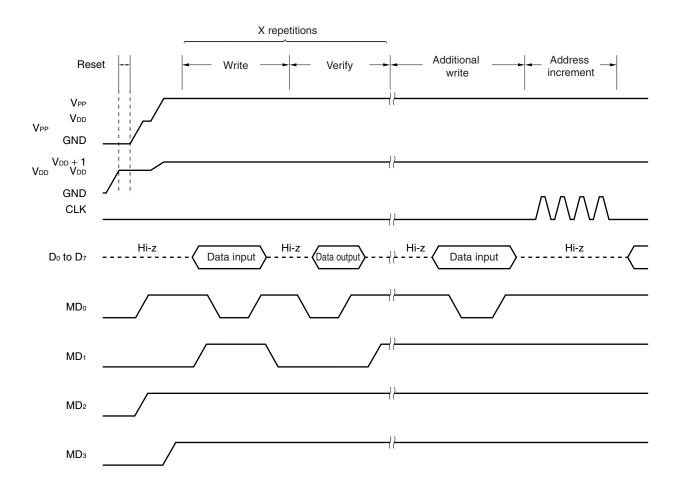

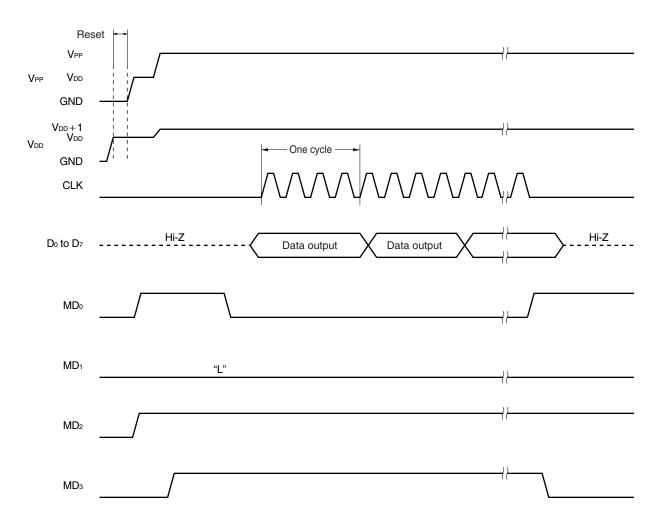

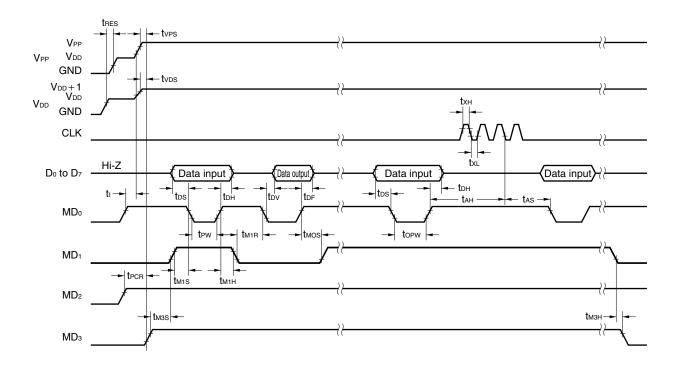

| 25. | ONE-1 | ΓΙΜΕ PROM (PROGRAM MEMORY) WRITE AND VERIFY (μPD17P012 ONLY) | 301 |

|     |       | Operation Modes for Program Memory Write/Verify              |     |

|     | 25.2  | Program Memory Write Procedure                               | 302 |

|     | 25.3  | Program Memory Read Procedure                                | 303 |

| 26. | ELEC  | TRICAL SPECIFICATIONS                                        | 304 |

| 27. | PACK  | AGE DRAWINGS                                                 | 310 |

| 28. | RECO  | MMENDED SOLDERING CONDITIONS                                 | 312 |

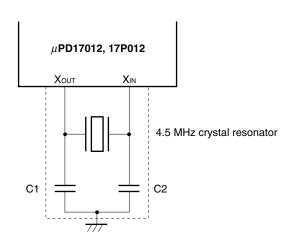

| ΑP  | PENDI | X A. NOTES ON CONNECTING CRYSTAL RESONATOR                   | 313 |

| ۸D  | DENI) | Y R. DEVELOPMENT TOOLS                                       | 21/ |

# 1. PIN FUNCTIONS

# 1.1 Pin Function List

# (1) Normal operation mode

| Pin                  | No.                  | Symbol                                                                                                                         | Function                                                                                                                                                                                                                                                                            | Output Format     | After Power-on |

|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|

| 64-Pin               | 80-Pin               |                                                                                                                                |                                                                                                                                                                                                                                                                                     |                   | Reset          |

| 63<br>1<br>2         | 77<br>80<br>1        | P1A <sub>2</sub><br>P1A <sub>1</sub><br>P1A <sub>0</sub>                                                                       | 3-bit I/O port (port 1A). Input/output can be specified in 1-bit units.                                                                                                                                                                                                             | CMOS<br>push-pull | Input          |

| 3                    | 2                    | EO                                                                                                                             | Output from PLL frequency synthesizer charge pump. The division value of the local oscillation frequency and the phase of the reference frequency are compared at this pin, and the result is output.                                                                               | CMOS<br>3-state   | High impedance |

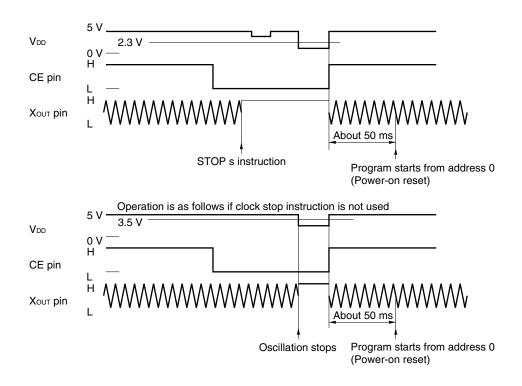

| 4<br>8               | 3 (4)<br>8, 9        | V <sub>DD1</sub><br>V <sub>DD2</sub>                                                                                           | Positive power-supply pins. 5 V $\pm 10\%$ is supplied to these pins. When only the CPU is operating, 3.5 to 5.5 V is supplied to these pins. 2.3 to 5.5 V is supplied when the clock is stopped. The same potential voltage is supplied to V <sub>DD1</sub> and V <sub>DD2</sub> . | -                 | _              |

| 5<br>6               | 5<br>6               | VCOL<br>VCOH                                                                                                                   | PLL local oscillation frequency is input.                                                                                                                                                                                                                                           | -                 | Input          |

| 7                    | 7                    | CE                                                                                                                             | Device selection and reset signal input.                                                                                                                                                                                                                                            | -                 | Input          |

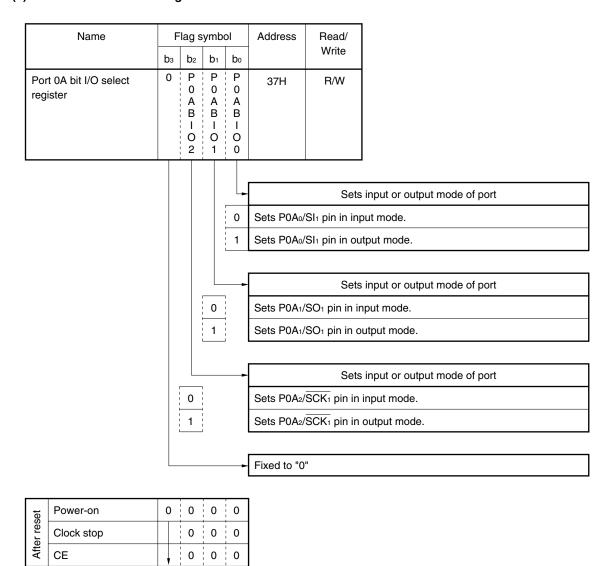

| 9<br>10<br>11        | 10<br>11<br>12       | P0A <sub>2</sub> /SCK <sub>1</sub><br>P0A <sub>1</sub> /SO <sub>1</sub><br>P0A <sub>0</sub> /SI <sub>1</sub>                   | Port 0A and serial interface I/O pins.  PoA <sub>2</sub> to PoA <sub>0</sub> 3-bit I/O port Input/output can be specified in 1-bit units.  SCK <sub>1</sub> Serial clock I/O SO <sub>1</sub> Serial data output SI <sub>1</sub> Serial data input                                   | CMOS<br>push-pull | Input          |

| 12<br>13<br>14<br>15 | 13<br>14<br>16<br>17 | P1B <sub>3</sub> /FMIFC<br>P1B <sub>2</sub> /AMIFC<br>P1B <sub>1</sub> /ADC <sub>1</sub><br>P1B <sub>0</sub> /ADC <sub>0</sub> | Port 1B. Frequency counter input and analog input to A/D converter pins.  • P1B <sub>3</sub> to P1B <sub>0</sub> • 4-bit input port  • FMIFC, AMIFC  • Frequency counter inputs  • ADC <sub>1</sub> , ADC <sub>0</sub> • Analog inputs to A/D converter                             | _                 | Input          |

**Remark** The parenthesized value applies to the  $\mu$ PD17P012.

| Pin                  | n No.                | Symbol                                                                                                                                                   | Function                                                                                                                                                                                                                                                                                          | Output Format                                      | After Power-on   |

|----------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|

| 64-Pin               | 80-Pin               |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                   |                                                    | Reset            |

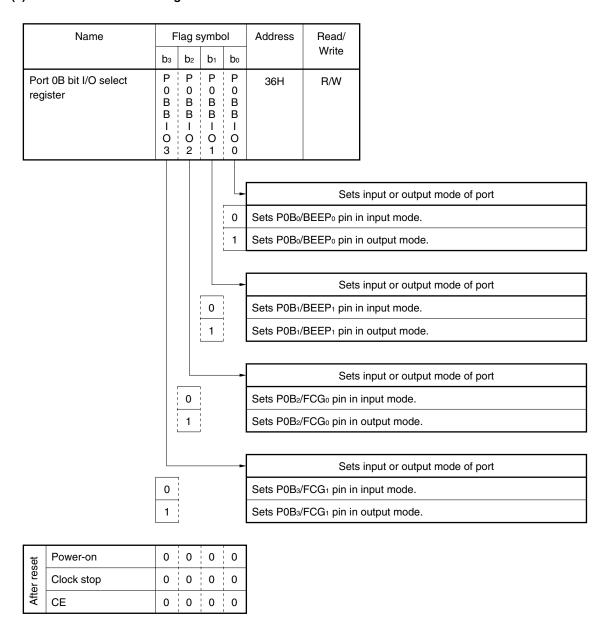

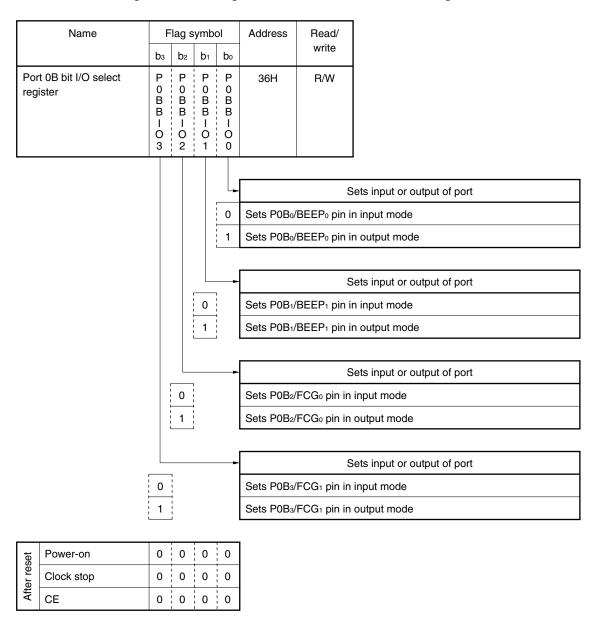

| 16<br>17<br>18<br>19 | 18<br>19<br>20<br>21 | P0B <sub>3</sub> /FCG <sub>1</sub><br>P0B <sub>2</sub> /FCG <sub>0</sub><br>P0B <sub>1</sub> /BEEP <sub>1</sub><br>P0B <sub>0</sub> /BEEP <sub>0</sub>   | Port 0B. External gate counter input and BEEP output pins.  • P0B <sub>3</sub> to P0B <sub>0</sub> • 4-bit I/O port • Input/output can be specified in 1-bit units.  • FCG <sub>1</sub> , FCG <sub>0</sub> • External gate counter inputs  • BEEP <sub>1</sub> , BEEP <sub>0</sub> • BEEP outputs | CMOS<br>push-pull                                  | Input            |

| 20<br>21<br>22<br>23 | 22<br>24<br>25<br>26 | P1C <sub>3</sub><br>P1C <sub>2</sub><br>P1C <sub>1</sub><br>P1C <sub>0</sub>                                                                             | 4-bit output port (port 1C)                                                                                                                                                                                                                                                                       | CMOS<br>push-pull                                  | Low-level output |

| 24                   | 27                   | Хоит                                                                                                                                                     | Pins for connecting crystal resonator for system clock                                                                                                                                                                                                                                            | CMOS push-pull                                     | _                |

| 25                   | 28                   | XIN                                                                                                                                                      | oscillation.                                                                                                                                                                                                                                                                                      | _                                                  |                  |

| 26<br>58             | 30, 69<br>31, 71     | GND                                                                                                                                                      | Ground pins. These pins must be connected to the same potential.                                                                                                                                                                                                                                  | _                                                  | _                |

| 27<br>28<br>29<br>30 | 33<br>34<br>35<br>37 | P0C <sub>3</sub><br>P0C <sub>2</sub><br>P0C <sub>1</sub> /PWM <sub>1</sub><br>P0C <sub>0</sub> /PWM <sub>0</sub>                                         | Port 0C. D/A converter output pins.  PoC <sub>3</sub> to PoC <sub>0</sub> 4-bit output port  PWM <sub>1</sub> , PWM <sub>0</sub> D/A converter outputs                                                                                                                                            | N-ch<br>open-drain<br>(+12 V withstand<br>voltage) | Low-level output |

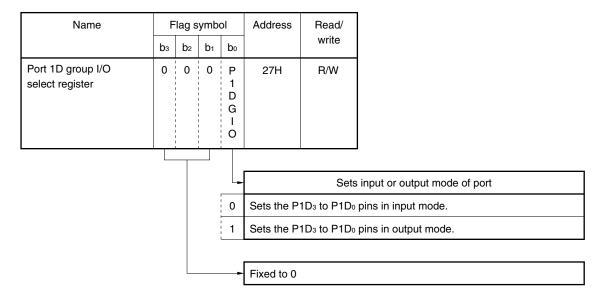

| 31<br>32<br>33<br>34 | 38<br>39<br>40<br>41 | P1D <sub>3</sub><br>P1D <sub>2</sub><br>P1D <sub>1</sub><br>P1D <sub>0</sub>                                                                             | 4-bit I/O port (port 1D). Input/output can be specified in 4-bit units.                                                                                                                                                                                                                           | CMOS<br>push-pull                                  | Input            |

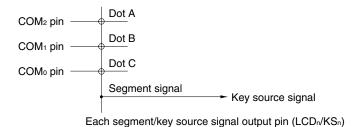

| 35<br>36<br>37       | 42<br>44<br>45       | COM <sub>2</sub><br>COM <sub>1</sub><br>COM <sub>0</sub>                                                                                                 | These pins output the common signals of the LCD controller/driver.                                                                                                                                                                                                                                | CMOS<br>ternary output                             | Low-level output |

| 38<br>39<br>40<br>41 | 46<br>47<br>48<br>49 | LCD <sub>19</sub> /P2H <sub>0</sub><br>LCD <sub>18</sub> /P2G <sub>0</sub><br>LCD <sub>17</sub> /P2F <sub>0</sub><br>LCD <sub>16</sub> /P2E <sub>0</sub> | Port 2H, 2G, 2F, and 2E. LCD controller/driver segment signal output pins.  P2H <sub>0</sub> , P2G <sub>0</sub> , P2F <sub>0</sub> , P2E <sub>0</sub> 1-bit output ports LCD <sub>19</sub> to LCD <sub>16</sub> LCD controller/driver segment signal outputs                                      | CMOS<br>push-pull                                  | Low-level output |

| Pin         | No.                              | Symbol                                                                  | Function                                                                                                                                                                                                                                                                                | Output Format     | After Power-on                    |

|-------------|----------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------|

| 64-Pin      | 80-Pin                           |                                                                         |                                                                                                                                                                                                                                                                                         |                   | Reset                             |

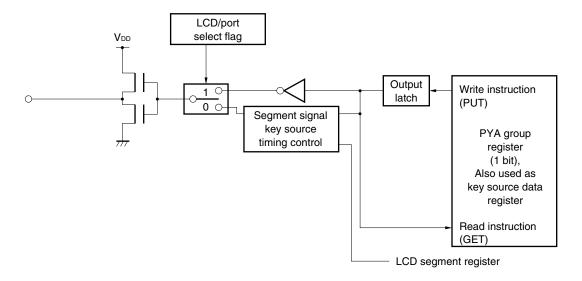

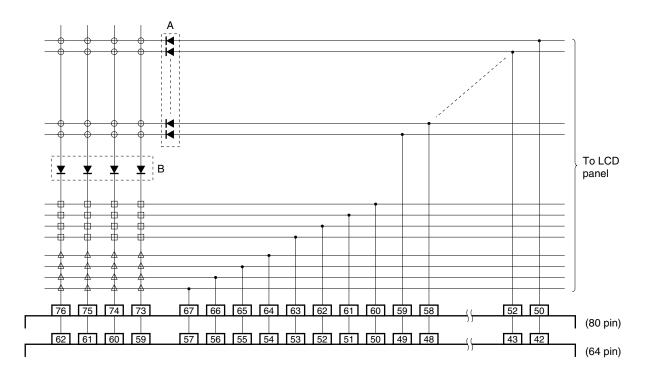

| 42 to 57    | 50<br>52<br>53<br>55<br>to<br>67 | LCD15/KS15/PYA15<br>to<br>LCD0/KS0/PYA0                                 | Port YA. Segment signal output of LCD controller/ driver and key source signal output of key matrix.  PYA <sub>15</sub> to PYA <sub>0</sub> 16-bit output port  LCD <sub>15</sub> to LCD <sub>0</sub> LCD controller/driver segment signal outputs  KS <sub>15</sub> to KS <sub>0</sub> | CMOS<br>push-pull | Low-level output                  |

|             |                                  |                                                                         | Key matrix key source signal outputs                                                                                                                                                                                                                                                    |                   |                                   |

| 59 to<br>62 | 73<br>to<br>76                   | P0D <sub>3</sub> /K <sub>3</sub> to<br>P0D <sub>0</sub> /K <sub>0</sub> | Port 0D. Key source signal return input of LCD segment.  • P0D <sub>3</sub> to P0D <sub>0</sub> • 4-bit input port  • K <sub>3</sub> to K <sub>0</sub> • Key source signal return inputs                                                                                                | -                 | Input with pull-<br>down resistor |

| 64          | 78                               | INT                                                                     | Vector interrupt pin for edge detection. Rising or falling edge can be selected.                                                                                                                                                                                                        | _                 | Input                             |

# (2) PROM programming mode ( $\mu$ PD17P012 only)

| Pin No.     |                   | Symbol                           | Function                                                                                                | Output Format  |

|-------------|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|----------------|

| 64-Pin      | 80-Pin            |                                  |                                                                                                         |                |

| 4           | 3, 4              | V <sub>DD1</sub>                 | Positive power supply. Supply +6 V to these pins when writing, reading,                                 | _              |

| 8           | 8, 9              | V <sub>DD2</sub>                 | or verifying the program memory.                                                                        |                |

| 12 to       | 13, 14,<br>16, 17 | D4 to D7                         | 8-bit data I/O when writing, reading, or verifying the program memory.                                  | CMOS push-pull |

| 20 to<br>23 | 22, 24<br>to 26   | D <sub>0</sub> to D <sub>3</sub> |                                                                                                         |                |

| 25          | 28                | CLK                              | Clock input to update addresses when writing, reading, or verifying the program memory.                 | -              |

| 26, 58      | 30, 69,<br>31, 71 | GND                              | Ground.                                                                                                 | -              |

| 59 to<br>62 | 73 to<br>76       | MD₃ to MD₀                       | Input to select the operation mode when writing, reading, or verifying the program memory.              | -              |

| 64          | 78                | V <sub>PP</sub>                  | Pin to apply the program voltage when writing, reading, or verifying the program memory. Apply +12.5 V. | _              |

**Remark** Pins not listed above are not used in the PROM programming mode. For the processing of unused pins, refer to (2)  $\mu$ PD17P012 (b) PROM programming mode.

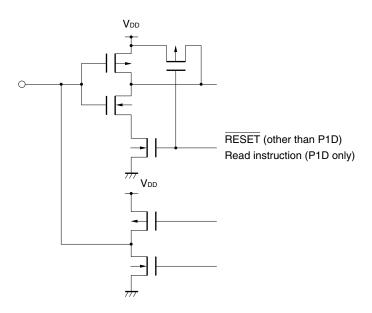

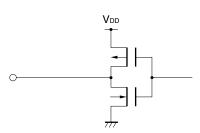

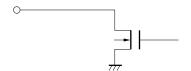

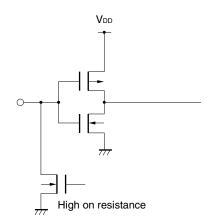

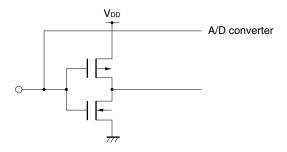

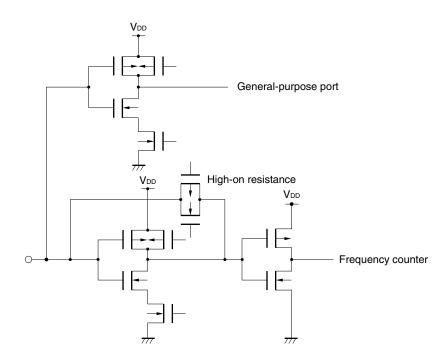

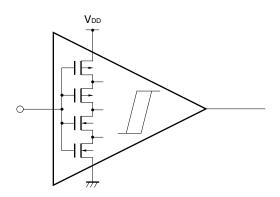

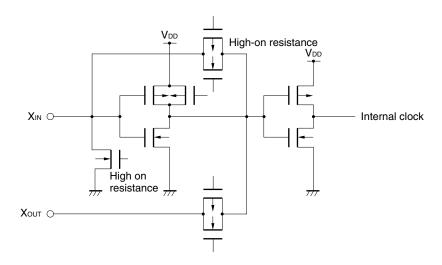

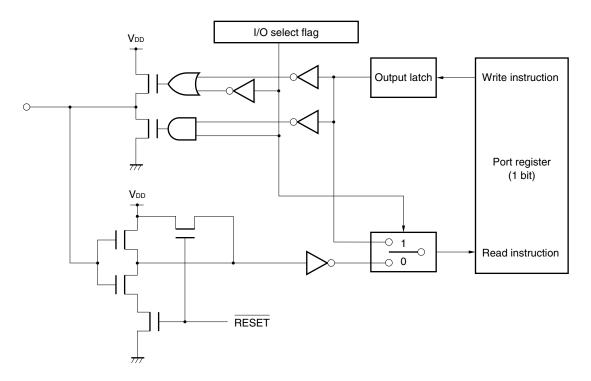

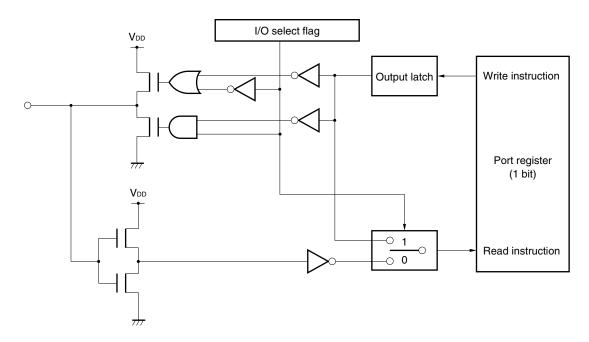

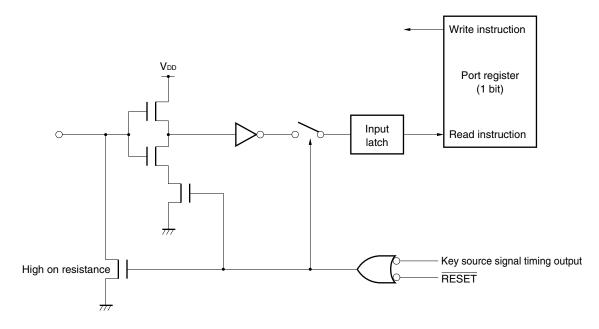

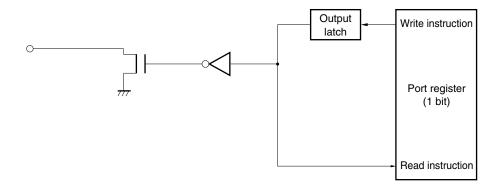

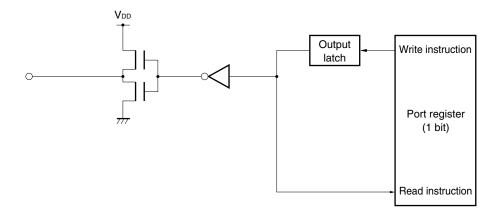

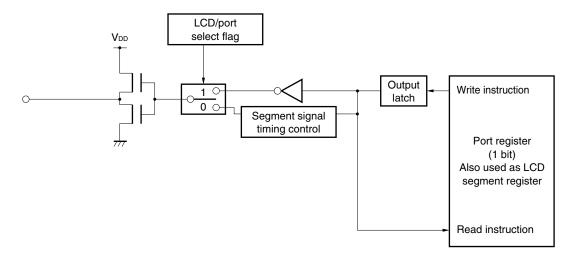

# 1.2 Pin Equivalent Circuits

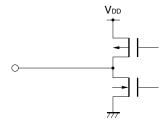

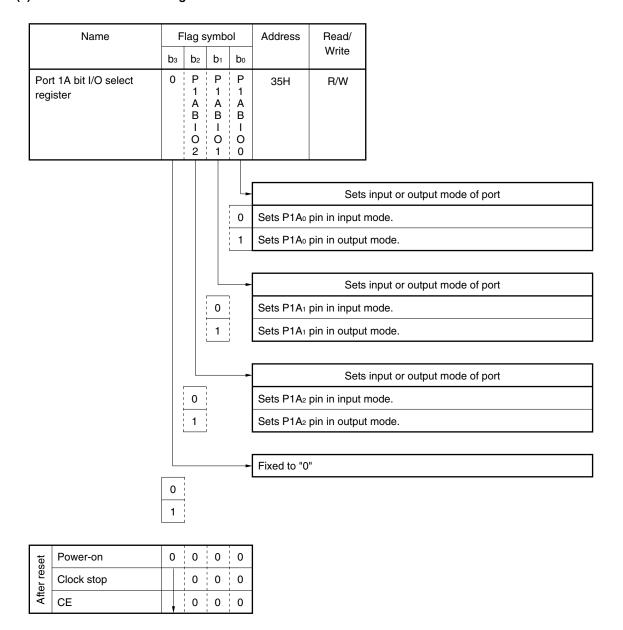

(1) P0A (P0A<sub>2</sub>/SCK<sub>1</sub>, P0A<sub>1</sub>/SO<sub>1</sub>, P0A<sub>0</sub>/SI<sub>1</sub>) P0B (P0B<sub>3</sub>/FCG<sub>1</sub>, P0B<sub>2</sub>/FCG<sub>0</sub>, P0B<sub>1</sub>/BEEP<sub>1</sub>, P0B<sub>0</sub>/BEEP<sub>0</sub>) P1A (P1A<sub>2</sub>, P1A<sub>1</sub>, P1A<sub>0</sub>) P1D (P1D<sub>3</sub>, P1D<sub>2</sub>, P1D<sub>1</sub>, P1D<sub>0</sub>)

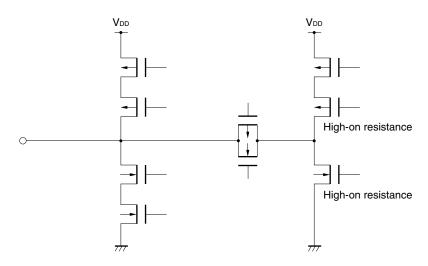

(2) P1C (P1C<sub>3</sub>, P1C<sub>2</sub>, P1C<sub>1</sub>, P1C<sub>0</sub>) LCD<sub>15</sub>/KS<sub>15</sub>/PYA<sub>15</sub> to LCD<sub>0</sub>/KS<sub>0</sub>/PYA<sub>0</sub> LCD<sub>19</sub>/P2H<sub>0</sub>, LCD<sub>18</sub>/P2G<sub>0</sub>, LCD<sub>17</sub>/P2F<sub>0</sub>, LCD<sub>16</sub>/P2E<sub>0</sub>,

(Output)

(3) POC (POC<sub>3</sub>, POC<sub>2</sub>, POC<sub>1</sub>/PWM<sub>1</sub>, POC<sub>0</sub>/PWM<sub>0</sub>) (output)

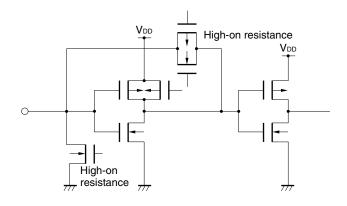

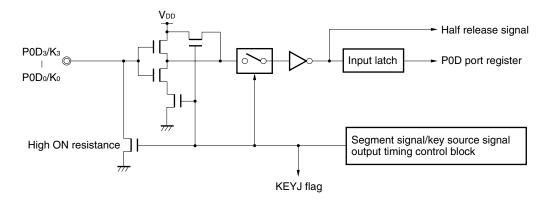

# (4) P0D (P0D $_3/K_3$ , P0D $_2/K_2$ , P0D $_1/K_1$ , P0D $_0/K_0$ ) (input)

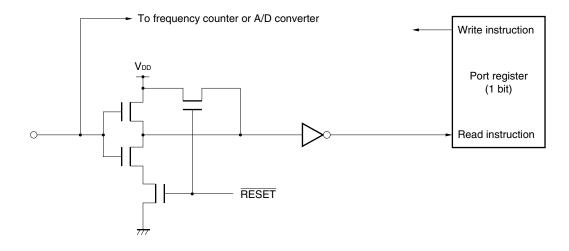

# (5) P1B (P1B<sub>1</sub>/ADC<sub>1</sub>, P1B<sub>0</sub>/ADC<sub>0</sub>) (input)

# (6) P1B (P1B<sub>3</sub>/FMIFC, P1B<sub>2</sub>/AMIFC) (input)

(7) CE | (Schmitt trigger input)

(8) XOUT (output), XIN (input)

(9) EO (output)

(10) COM<sub>2</sub>

COM<sub>1</sub>

COM<sub>0</sub> (Output)

(11) VCOH VCOL (Input)

#### 1.3 Recommended Connection of Unused Pins

The following connections are recommended for unused pins.

Table 1-1. Recommended Connection of Unused Pins

| Pin Name      |                                                                      | I/O Mode               | Recommended Connection of Unused Pins                                                                         |  |  |  |  |  |

|---------------|----------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|               | P0D <sub>0</sub> /K <sub>0</sub> to P0D <sub>3</sub> /K <sub>3</sub> | Input                  | Independently connect to GND via a resistor Note 1.                                                           |  |  |  |  |  |

|               | P1B <sub>0</sub> /ADC <sub>0</sub>                                   |                        | Independently connect to VDD or GND via a resistor Note 1.                                                    |  |  |  |  |  |

|               | P1B <sub>1</sub> /ADC <sub>1</sub>                                   |                        |                                                                                                               |  |  |  |  |  |

|               | P1B <sub>2</sub> /AMIFC <sup>Notes 2, 3</sup>                        |                        | Set to P1B2 and connect to VDD or GND via a resistor Note 1.                                                  |  |  |  |  |  |

|               | P1B <sub>3</sub> /FMIFC <sup>Notes 2, 3</sup>                        |                        | Set to P1B <sub>3</sub> and connect to V <sub>DD</sub> or GND via a resistor Note                             |  |  |  |  |  |

|               | P1C <sub>0</sub> /P1C <sub>3</sub>                                   | CMOS push-pull output  | Leave open.                                                                                                   |  |  |  |  |  |

|               | P2E <sub>0</sub> /LCD <sub>16</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

|               | P2F <sub>0</sub> /LCD <sub>17</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

|               | P2G <sub>0</sub> /LCD <sub>18</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

|               | P2H <sub>0</sub> /LCD <sub>19</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

| pins          | PYA <sub>0</sub> /LCD <sub>0</sub> /KS <sub>0</sub> to               |                        |                                                                                                               |  |  |  |  |  |

| r pi          | PYA <sub>15</sub> /LCD <sub>15</sub> /KS <sub>15</sub>               |                        |                                                                                                               |  |  |  |  |  |

| Port          | P0C <sub>0</sub> /PWM <sub>0</sub>                                   | N-ch open-drain output | Set to low-level output by software, and leave open.                                                          |  |  |  |  |  |

|               | P0C <sub>1</sub> /PWM <sub>1</sub>                                   |                        |                                                                                                               |  |  |  |  |  |

|               | P0C <sub>2</sub> , P0C <sub>3</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

|               | P0A <sub>0</sub> /SI <sub>1</sub>                                    | I/O <sup>Note 4</sup>  | Set to general-purpose input port by software, and independently connect to VDD or GND via a resistor Note 1. |  |  |  |  |  |

|               | P0A <sub>1</sub> /SO <sub>1</sub>                                    |                        |                                                                                                               |  |  |  |  |  |

|               | P0A <sub>2</sub> /SCK <sub>1</sub>                                   |                        |                                                                                                               |  |  |  |  |  |

|               | P0Bo/BEEPo                                                           |                        |                                                                                                               |  |  |  |  |  |

|               | P0B <sub>1</sub> /BEEP <sub>1</sub>                                  |                        |                                                                                                               |  |  |  |  |  |

|               | P0B <sub>2</sub> /FCG <sub>0</sub> Notes 2, 3                        |                        |                                                                                                               |  |  |  |  |  |

|               | P0B <sub>3</sub> /FCG <sub>1</sub> Notes 2, 3                        |                        |                                                                                                               |  |  |  |  |  |

|               | P1A <sub>0</sub> to P1A <sub>2</sub>                                 |                        |                                                                                                               |  |  |  |  |  |

|               | P1D₀ to P1D₃                                                         |                        |                                                                                                               |  |  |  |  |  |

|               | CE                                                                   | Input                  | Connect to V <sub>DD</sub> via a resistor <sup>Note 1</sup> .                                                 |  |  |  |  |  |

| pins          | INT <sup>Note 5</sup>                                                |                        | Connect to GND via a resistor <sup>Note 1</sup> .                                                             |  |  |  |  |  |

| Non-port pins | VCOH, VCOL                                                           |                        | Disable by software, and leave open.                                                                          |  |  |  |  |  |

| on-F          | COM <sub>0</sub> to COM <sub>2</sub>                                 | Output                 | Leave open.                                                                                                   |  |  |  |  |  |

| Z             | EO                                                                   |                        |                                                                                                               |  |  |  |  |  |

- Notes 1. Note that when pulling up (connecting to VDD via a resistor) or pulling down (connecting to GND via a resistor) a pin externally using a high resistance value, the current consumption (through current) of the port increases because the pin approaches the high-impedance state. Generally, a resistance value of several tens of  $k\Omega$  suffices for pull up and pull down, although this value depends on each application circuit.

- 2. This general-purpose input port has a circuit designed so that the current consumption does not increase even in the high-impedance state.

- 3. Do not set this pin to AMIFC, FMIFC, FCGo or FCG1, or the current consumption will increase.

- 4. These input/output ports become general-purpose input ports at power-on, clock stop, and CE reset.

- **5.** In the  $\mu$ PD17P012, the INT pin functions alternately as the V<sub>PP</sub> pin for writing or verifying the program memory. If the INT pin is not used, directly connect to GND.

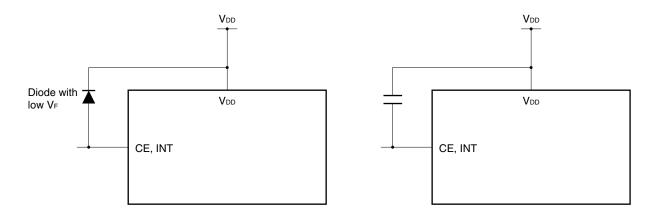

# 1.4 Notes on Using CE and INT Pins

The CE and INT pins have a function to set a test mode (for IC test) in which the internal operations of the  $\mu$ PD17012 and 17P012 are tested, in addition to the functions listed in **1.1 Pin Function List**.

\* In the μPD17P012, the INT pin functions alternately as the V<sub>PP</sub> pin for writing or verifying the program memory. If a voltage higher than V<sub>DD</sub> is applied to either of these pins, the test mode is set. Therefore, if noise exceeding V<sub>DD</sub> is applied to these pins even during normal operation, the test mode may be set by mistake, affecting normal operation.

Noise may be superimposed on these pins if the length of the wiring of these pins is too long.

Therefore, keep the wiring length as short as possible. If noise is inevitable, take noise suppression measures by using an external component as illustrated below.

- Connect a diode with low V<sub>F</sub>

between CE or INT and V<sub>DD</sub>

- Connect a capacitor between CE or INT and VDD

# 2. PROGRAM MEMORY (ROM)

# 2.1 Outline of Program Memory

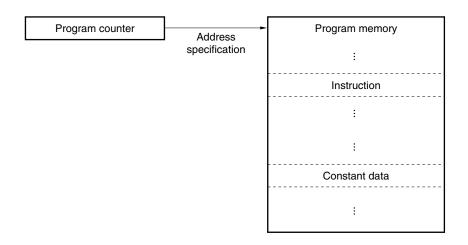

Figure 2-1 illustrates the program memory.

As shown in this figure, the program memory consists of program memory and a program counter.

The addresses of the program memory are specified by the program counter.

The program memory has the following two major functions.

- (1) Storing programs

- (2) Storing constant data

Figure 2-1. Outline of Program Memory

27

#### 2.2 Program Memory

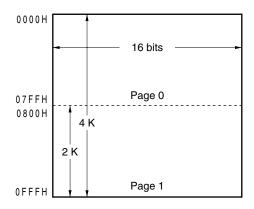

Figure 2-2 shows the configuration of the program memory.

As shown in this figure, the program memory has a configuration of 4,096 steps  $\times$  16 bits.

Therefore, program memory addresses are addresses 0000H to 0FFFH.

All instructions are 1-word instructions, 16 bits long, so that one instruction can be stored in one address of the program memory.

The constant data in the program memory contents is read to the data buffer by using a table reference instruction.

Figure 2-2. Configuration of Program Memory

## 2.3 Program Counter

Figure 2-3 shows the configuration of the program counter.

As shown in this figure, the program counter is configured as a 12-bit binary counter. The most significant bit, b<sub>11</sub>, indicates a page.

The program counter specifies an address of the program memory.

Figure 2-3. Configuration of Program Counter

| PC <sub>11</sub> | PC <sub>10</sub> | PC <sub>9</sub> | PC <sub>8</sub> | PC <sub>7</sub> | PC <sub>6</sub> | PC₅ | PC <sub>4</sub> | РС₃ | PC <sub>2</sub> | PC <sub>1</sub> | PC₀ |  |

|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-----|-----------------|-----------------|-----|--|

| Page             |                  |                 |                 |                 |                 |     |                 |     |                 |                 |     |  |

| PC               |                  |                 |                 |                 |                 |     |                 |     |                 |                 |     |  |

#### 2.4 Program Flow

The execution flow of the program is controlled by the program counter, which specifies an address of the program memory.

Figure 2-4 shows the value set to the program counter when each instruction is executed.

Table 2-1 shows the vector address when an interrupt is acknowledged.

#### 2.4.1 Branch instructions

#### (1) Direct branch ("BR addr")

The branch destination address of the direct branch instruction is in the area of addresses 0000H to 0FFFH, i.e. all the addresses of the program memory.

#### (2) Indirect branch ("BR @AR")

The branch destination address of the indirect branch instruction is in the area of addresses 0000H to 0FFFH, i.e. all the addresses of the program memory.

Also refer to 5.3 Address Register (AR).

#### 2.4.2 Subroutine

#### (1) Direct subroutine call ("CALL addr")

The top address of the subroutine that can be called by the direct subroutine call instruction is within page 0 (addresses 0000H to 07FFH) in the program memory.

#### (2) Indirect subroutine call ("CALL @AR")

The top address of the subroutine that can be called by the indirect subroutine call instruction is in the area of addresses 0000H to 0FFFH, i.e. all the addresses of the program memory.

Also refer to 5.3 Address Register (AR).

#### 2.4.3 Table referencing

Addresses that can be referenced by the table reference instruction ("MOVT DBF, @AR") are in the area of addresses 0000H to 0FFFH, i.e. all the addresses of the program memory.

Also refer to 5.3 Address Register (AR) and 9.2.2 Table reference instruction ("MOVT DBF, @AR").

Figure 2-4. Specification of Program Counter on Instruction Execution

| Program counter                |  | Contents of program counter (PC) |                                                    |                               |                |                |                |            |                |    |                |                |    |

|--------------------------------|--|----------------------------------|----------------------------------------------------|-------------------------------|----------------|----------------|----------------|------------|----------------|----|----------------|----------------|----|

| Instruction                    |  |                                  | b <sub>10</sub>                                    | b <sub>9</sub>                | b <sub>8</sub> | b <sub>7</sub> | b <sub>6</sub> | <b>b</b> 5 | b <sub>4</sub> | bз | b <sub>2</sub> | b <sub>1</sub> | bo |

| BR addr Page 0                 |  |                                  |                                                    | 0 Instruction approach (adds) |                |                |                |            |                |    |                |                |    |

| Page 1                         |  |                                  | Instruction operand (addr)                         |                               |                |                |                |            |                |    |                |                |    |

| CALL addr                      |  |                                  |                                                    | 0 Instruction operand (addr)  |                |                |                |            |                |    |                |                |    |

| BR @AR                         |  |                                  |                                                    |                               |                |                |                |            |                |    |                |                |    |

| CALL @AR                       |  |                                  | Address register contents                          |                               |                |                |                |            |                |    |                |                |    |

| MOVT DBF, @AR                  |  |                                  |                                                    |                               |                |                |                |            |                |    |                |                |    |

| RET                            |  |                                  | Contents of address stack register (ASR) specified |                               |                |                |                |            |                |    |                |                |    |

| RETSK                          |  |                                  | by stack pointer (SP)                              |                               |                |                |                |            |                |    |                |                |    |

| RETI                           |  |                                  | (Return address)                                   |                               |                |                |                |            |                |    |                |                |    |

| When interrupt is acknowledged |  |                                  | Vector address of each interrupt                   |                               |                |                |                |            |                |    | •              |                |    |

| Power-on reset, CE reset       |  |                                  |                                                    | 0                             | 0              | 0              | 0              | 0          | 0              | 0  | 0              | 0              | 0  |

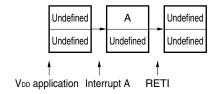

**Table 2-1. Interrupt Vector Address**

| Priority | Internal/External | Interrupt Source | Vector address |  |  |  |

|----------|-------------------|------------------|----------------|--|--|--|

| 1        | External          | INT pin          | 0004H          |  |  |  |

| 2        | Internal          | 12-bit timer     | 0003H          |  |  |  |

| 3        | Internal          | Basic timer 1    | 0002H          |  |  |  |

| 4        | Internal          | Serial interface | 0001H          |  |  |  |

#### 3. ADDRESS STACK (ASK)

#### 3.1 Outline of Address Stack

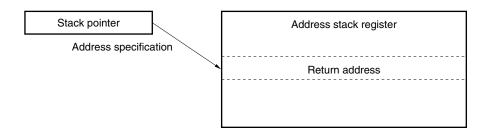

Figure 3-1 illustrates the address stack.

The address stack consists of a stack pointer and address stack registers.

The addresses of the address stack registers are specified by the stack pointer.

The address stack saves a return address when a subroutine call instruction is executed or when an interrupt is acknowledged.

The address stack is also used when a table reference instruction is executed.

Figure 3-1. Outline of Address Stack

#### 3.2 Address Stack Registers (ASR)

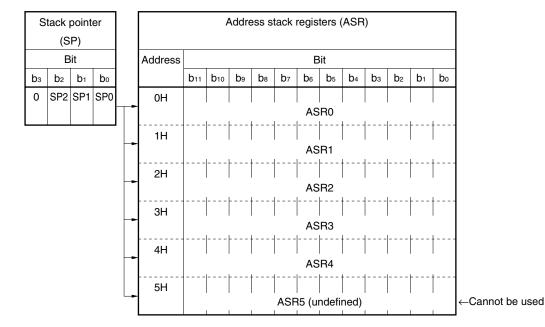

Figure 3-2 shows the configuration of the address stack registers.

Although there are six 12-bit address stack registers: ASR0 to ASR5, no register is assigned to ASR5, and five 12-bit registers, ASR0 to ASR4, are used.

The address stack saves a return address when a subroutine call instruction or table reference instruction is executed, or when an interrupt is acknowledged.

Figure 3-2. Configuration of Address Stack Registers

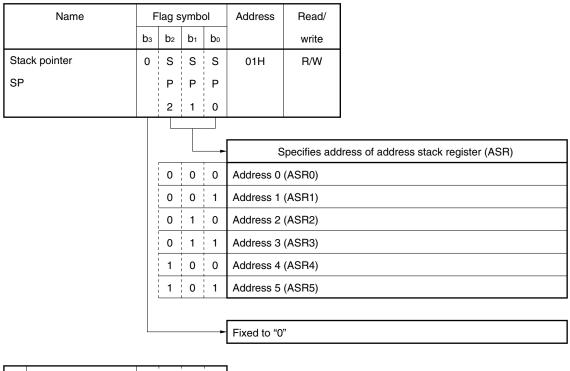

#### 3.3 Stack Pointer (SP)

Figure 3-3 shows the configuration and function of the stack pointer.

The stack pointer is a 4-bit binary counter.

It specifies the address of an address stack register.

The value of the stack pointer can be directly read or written by using a register manipulation instruction.

Figure 3-3. Configuration and Function of Stack Pointer

| set   | Power-on   |  | ) | 1 | 0 | 1 |

|-------|------------|--|---|---|---|---|

| er re | Clock stop |  |   | 1 | 0 | 1 |

| Aff   | CE         |  | , | 1 | 0 | 1 |