# **79C940**

# Media Access Controller for Ethernet (MACE<sup>™</sup>)

## **DISTINCTIVE CHARACTERISTICS**

- Integrated Controller with Manchester encoder/decoder and 10BASE-T transceiver and AUI port

- Supports IEEE 802.3/ANSI 8802-3 and Ethernet standards

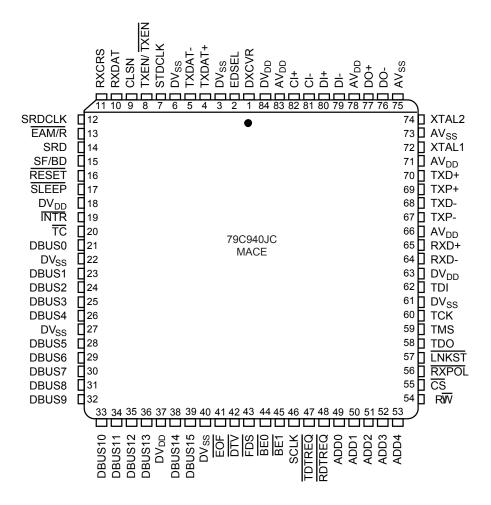

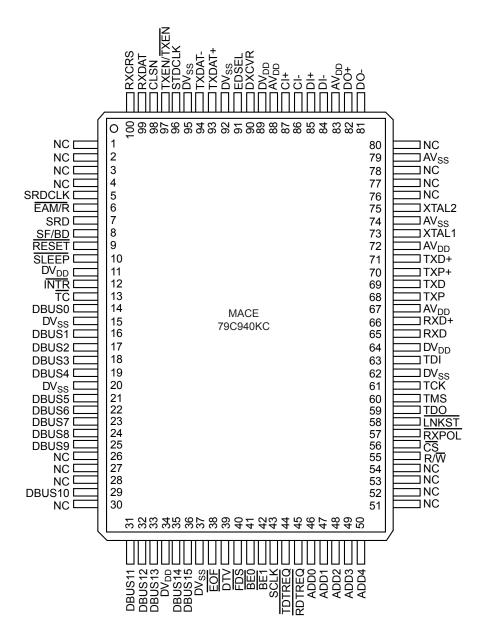

- 84-pin PLCC and 100-pin PQFP Packages

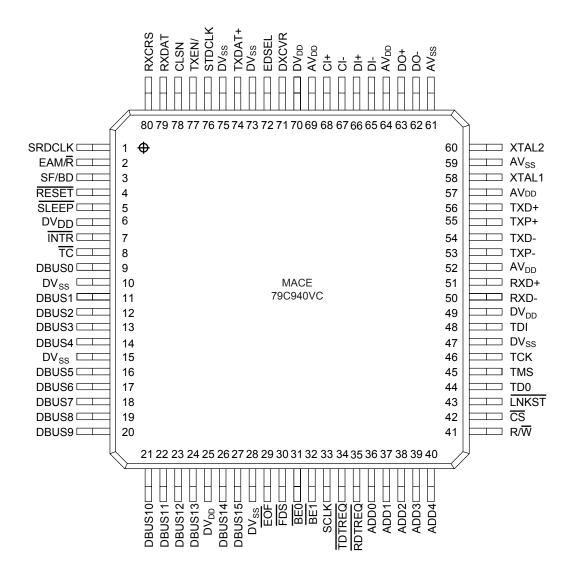

- 80-pin Thin Quad Flat Pack (TQFP) package available for space critical applications such as PCMCIA

- Modular architecture allows easy tuning to specific applications

- High speed, 16-bit synchronous host system interface with 2 or 3 cycles/transfer

- Individual transmit (136 byte) and receive (128 byte) FIFOs provide increase of system latency and support the following features:

- Automatic retransmission with no FIFO reload

- Automatic receive stripping and transmit padding (individually programmable)

- Automatic runt packet rejection

- Automatic deletion of collision frames

- Automatic retransmission with no FIFO reload

- Direct slave access to all on board configuration/status registers and transmit/ receive FIFOs

- Direct FIFO read/write access for simple interface to DMA controllers or I/O processors

- Arbitrary byte alignment and little/big endian memory interface supported

- Internal/external loopback capabilities

- External Address Detection Interface (EADI<sup>™</sup>) for external hardware address filtering in bridge/router applications

- JTAG Boundary Scan (IEEE 1149.1) test access port interface for board level production test

- Integrated Manchester Encoder/Decoder

- Digital Attachment Interface (DAI<sup>™</sup>) allows by-passing of differential Attachment Unit Interface (AUI)

- Supports the following types of network interface:

- AUI to external 10BASE2, 10BASE5 or 10BASE-F MAU

- DAI port to external 10BASE2, 10BASE5, 10BASE-T, 10BASE-F MAU

- General Purpose Serial Interface (GPSI) to external encoding/decoding scheme

- Internal 10BASE-T transceiver with automatic selection of 10BASE-T or AUI port

- Sleep mode allows reduced power consumption for critical battery powered applications

- 5 MHz-25 MHz system clock speed

- Support for operation in industrial temperature range (-40°C to +85°C) available in all three packages

For complete Rochester ordering guide, please refer to page 3 Please consult factory for specific package availability

Rochester Electronics guarantees performance of its semiconductor products to the original OEM specifications. "Typical" values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing. Rochester Electronics reserves the right to make changes without further notice to any specification herein.

### **GENERAL DESCRIPTION**

The Media Access Controller for Ethernet (MACE) chip is a CMOS VLSI device designed to provide flexibility in customized LAN design. The MACE device is specifically designed to address applications where multiple I/O peripherals are present, and a centralized or system specific DMA is required. The high speed, 16-bit synchronous system interface is optimized for an external DMA or I/O processor system, and is similar to many existing peripheral devices, such as SCSI and serial link controllers.

The MACE device is a slave register based peripheral. All transfers to and from the system are performed using simple memory or I/O read and write commands. In conjunction with a user defined DMA engine, the MACE chip provides an IEEE 802.3 interface tailored to a specific application. Its superior modular architecture and versatile system interface allow the MACE device to be configured as a stand-alone device or as a connectivity cell incorporated into a larger, integrated system.

The MACE device provides a complete Ethernet node solution with an integrated 10BASE-T transceiver, and supports up to 25-MHz system clocks. The MACE device embodies the Media Access Control (MAC) and Physical Signaling (PLS) sub-layers of the IEEE 802.3 standard, and provides an IEEE defined Attachment Unit Interface (AUI) for coupling to an external Medium Attachment Unit (MAU). The MACE device is compliant with 10BASE2, 10BASE5, 10BASE-T, and 10BASE-F transceivers.

Additional features also enhance over-all system design. The individual transmit and receive FIFOs optimize system overhead, providing substantial latency during packet transmission and reception, and minimizing intervention during normal network error recovery. The integrated Manchester encoder/decoder eliminates the need for an external Serial Interface Adapter (SIA) in the node system. If support for an external encoding/decoding scheme is desired, the General Purpose Serial Interface (GPSI) allows direct access to/from the MAC. In addition, the Digital Attachment Interface (DAI), which is a simplified electrical attachment specification, allows implementation of MAUs that do not require DC isolation between the MAU and DTE. The DAI port can also be used to indicate transmit, receive, or collision status by connecting LEDs to the port. The MACE device also provides an External Address Detection Interface (EADI) to allow external hardware address filtering in internet working applications.

The 79C940 MACE chip is offered in a Plastic Leadless Chip Carrier (84-pin PLCC), a Plastic Quad Flat Package (100-pin PQFP), and a Thin Quad Flat Package (TQFP 80-pin). There are several small functional and physical differences between the 80-pin TQFP and the 84-pin PLCC and 100-pin PQFP configurations. Because of the smaller number of pins in the TQFP configuration versus the PLCC configuration, four pins are not bonded out. Though the die is identical in all three package configurations, the removal of these four pins does cause some functionality differences between the TQFP and the PLCC and PQFP configurations. Depending on the application, the removal of these pins will or will not have an effect. (See section: "Pins Removed for TQFP Package and Their Effects.)

With the rise of embedded networking applications operating in harsh environments where temperatures may exceed the normal commercial temperature (0°C to +70°C) window, an industrial temperature (-40°C to +85°C) version is available in all three packages; 84-pin PLCC, 100-pin PQFP and 80-pin TQFP. The industrial temperature version of the MACE Ethernet controller is characterized across the industrial temperature range (-40°C to +85°C) within the published power supply specification (4.75 V to 5.25 V; i.e.,  $\pm$ 5% V<sub>CC</sub>). Thus, conformance of MACE performance over this temperature range is guaranteed by the design and characterization monitor.

### **Rochester Ordering Guide**

\*Most products can also be offered as RoHS compliant, designated by a –G suffix. Please contact factory for more information.

| Rochester Part Number | AMD Part Number | Package           | Temperature   |

|-----------------------|-----------------|-------------------|---------------|

| Am79C940B-16JC        | Am79C940B-16JC  | LDCC-84, Plastic  | 0° to +70°C   |

| Am79C940B-25JC        | Am79C940B-25JC  | LDCC-84, Plastic  | 0° to +70°C   |

| Am79C940BJC           | Am79C940BJC     | LDCC-84, Plastic  | 0° to +70°C   |

| Am79C940BJI           | Am79C940BJI     | LDCC-84, Plastic  | -40° to +85°C |

| Am79C940BKC           | Am79C940BKC     | TPAK-100, Plastic | 0° to +70°C   |

| Am79C940BKC/W         | Am79C940BKC/W   | QFP-100, Plastic  | 0° to +70°C   |

| Am79C940BKI           | Am79C940BKI     | TPAK-100, Plastic | -40° to +85°C |

| Am79C940BKI/W         | Am79C940BKI/W   | QFP-100, Plastic  | -40° to +85°C |

| Am79C940BVC           | Am79C940BVC     | TPAK-80, Plastic  | 0° to +70°C   |

| Am79C940BVC/W         | Am79C940BVC/W   | TQFP-80, Plastic  | 0° to +70°C   |

| Am79C940BVI           | Am79C940BVI     | TPAK-80, Plastic  | -40° to +85°C |

| Am79C940BVI/W         | Am79C940BVI/W   | TQFP-80, Plastic  | -40° to +85°C |

CONNECTION DIAGRAMS PL 084 PLCC PACKAGE

CONNECTION DIAGRAMS PQR100 PQFP PACKAGE

## 79C940

CONNECTION DIAGRAMS PQT080 TQFP PACKAGE

**Notes:** Four pin functions available on the PLCC and PQFP packages are not available with the TQFP package. (See full data sheet for description of pins not included with the 80-pin TQFP package. In particular, see section "Pin Functions not available with the 80-pin TQFP package.")

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature   Under Bias   O°C to +70°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Supply Voltage to AVSS or DVss (AVDD, DVDD)0.3 V to +6.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Office and the set of |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

#### **OPERATING RANGES**

| Commercial (C) Devices                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature (T <sub>A</sub> ) $\dots \dots \dots 0^{\circ}$ C to +70°C                                          |

| Industrial (I) Devices                                                                                                  |

| Ambient Temperature (T <sub>A</sub> ) $\dots \dots -40^{\circ}C$ to +85°C                                               |

| V <sub>CC</sub> Supply Voltages                                                                                         |

| (AVDD, DVDD) 5 V $\pm$ 5%                                                                                               |

| All inputs within the range: AVDD – 0.5 V $\leq$ Vin $\leq$ AVSS + 0.5 V, or DV <sub>DD</sub> – 0.5 V $\leq$ Vin $\leq$ |

| Operating ranges define those limits between which the func-                                                            |

tionality of the device is guaranteed.

# DC CHARACTERISTICS (Unless otherwise noted, parametric values are the same between Commercial devices and Industrial devices.)

| Parameter<br>Symbol | Parameter Description                               | Test Conditions                                            | Min             | Max              | Unit |

|---------------------|-----------------------------------------------------|------------------------------------------------------------|-----------------|------------------|------|

| VIL                 | Input LOW Voltage                                   |                                                            |                 | 0.8              | V    |

| V <sub>IH</sub>     | Input HIGH Voltage                                  |                                                            | 2.0             | 1 1              | V    |

|                     | XTAL1 Input LOW Voltage                             | V <sub>SS</sub> = 0.0 V                                    | -0.5            | 0.8              | V    |

| $V_{ILX}$           | (External Clock Signal)                             |                                                            | -0.5            | 0.8              | v    |

| M                   | XTAL1 Input HIGH Voltage                            | V <sub>SS</sub> = 0.0 V                                    | V <sub>DD</sub> | V <sub>DD+</sub> | V    |

| V <sub>IHX</sub>    | (External Clock Signal)                             |                                                            | 0.8             | 0.5              | v    |

| V <sub>OL</sub>     | Output LOW Voltage                                  | I <sub>OL</sub> = 3.2 mA                                   |                 | 0.45             | V    |

| V <sub>OH</sub>     | Output HIGH Voltage                                 | I <sub>OH</sub> = -0.4 mA (Note 1)                         | 2.4             |                  | V    |

| I <sub>IL1</sub>    | Input Leakage Current                               | V <sub>DD</sub> = 5 V, V <sub>IN</sub> = 0 V<br>(Note 2)   | -10             | 10               | μA   |

| I <sub>IL2</sub>    | Input Leakage Current                               | V <sub>DD</sub> = 5 V, V <sub>IN</sub> = 0 V<br>(Note 2)   | -200            | 200              | μA   |

| I <sub>IH</sub>     | Input Leakage Current                               | V <sub>DD</sub> = 5 V, V <sub>IN</sub> = 2.7 V<br>(Note 3) |                 | -100             | μA   |

| I <sub>IAXD</sub>   | Input Current at DI+<br>and DI–                     | -1 V < V <sub>IN</sub> < AV <sub>DD</sub> + 0.5 V          | -500            | +500             | μA   |

| I <sub>IAXC</sub>   | Input Current at CI+<br>and CI–                     | -1 V < V <sub>IN</sub> < AV <sub>DD</sub> + 0.5 V          | -500            | +500             | μA   |

| I <sub>ILXN</sub>   | XTAL1 Input LOW Current<br>during normal operation  | V <sub>IN</sub> = 0 V<br>SLEEP = HIGH                      |                 | -92<br>(Note 9)  | μA   |

| I <sub>IHXN</sub>   | XTAL1 Input HIGH Current<br>during normal operation | V <sub>IN</sub> = 5.5 V<br>SLEEP = HIGH                    |                 | 92<br>(Note 10)  | μA   |

| I <sub>ILXS</sub>   | XTAL1 Input LOW Current<br>during Sleep             | V <sub>IN</sub> = 0 V<br>SLEEP = LOW                       |                 | <10              | μA   |

| I <sub>IHXS</sub>   | XTAL1 Input HIGH Current<br>during Sleep            | $\frac{V_{IN} = 5.5 V}{SLEEP} = LOW$                       |                 | 410              | μA   |

| I <sub>OZ</sub>     | Output Leakage Current                              | 0.4 V < V <sub>OUT</sub> < V <sub>DD</sub><br>(Note 4)     | -10             | 10               | μA   |

| V <sub>AOD</sub>    | Differential Output Voltage<br> (DO+)–(DO–)         | R <sub>L</sub> = 78 Ω                                      | 630             | 1200             | mV   |

| V <sub>AODOFF</sub> | Transmit Differential Output<br>Idle Voltage        | R <sub>L</sub> = 78 Ω (Note 5)                             | -40             | +40              | mV   |

# **DC CHARACTERISTICS (Continued)**

| Parameter<br>Symbol | Parameter Description                         | Test Conditions                                       | Min                   | Max                                          | Unit |

|---------------------|-----------------------------------------------|-------------------------------------------------------|-----------------------|----------------------------------------------|------|

|                     | Transmit Differential                         | R <sub>I</sub> = 78 Ω                                 | _1                    | +1                                           | mA   |

| AODOFF              | Output Idle Current                           |                                                       |                       | · ·                                          |      |

| Vieni               | DO± Common Mode                               | R <sub>I</sub> = 78 Ω                                 | 2.5                   | AVDD                                         | V    |

| V <sub>AOCM</sub>   | Output Voltage                                |                                                       | 2.5                   | AVDD                                         | v    |

| V I                 | DO± Differential Output                       | R <sub>1</sub> = 78 Ω (Note 6)                        | -25                   | 25                                           | mV   |

| V <sub>OD</sub> I   | Voltage Imbalance                             | $R_{L} = 78.22$ (Note 0)                              | -25                   | 25                                           | IIIV |

| V                   | Receive Data Differential                     | $P = 79 \circ (Nata 6)$                               | 25                    | 25                                           | m)/  |

| V <sub>ATH</sub>    | Input Threshold                               | R <sub>L</sub> = 78 Ω (Note 6)                        | -35                   | 35                                           | mV   |

| 14                  | DI± and CI± Differential                      |                                                       | 100                   | 075                                          |      |

| V <sub>ASQ</sub>    | Input Threshold Squelch                       | R <sub>L</sub> = 78 Ω (Note 6)                        | -160                  | -275                                         | mV   |

| 14                  | DI± and CI± Differential                      |                                                       |                       | 4.5                                          |      |

| V <sub>IRDVD</sub>  | Mode Input Voltage Range                      |                                                       |                       | 1.5                                          | V    |

| 14                  | DI± and CI± Input Bias                        | L = 0 m A                                             | AV 0.0                |                                              |      |

| V <sub>ICM</sub>    | Voltage                                       | I <sub>IN</sub> = 0 mA                                | AV <sub>DD</sub> –3.0 | AV <sub>DD</sub> –0.8                        | V    |

| V <sub>OPD</sub>    | DI± Undershoot Voltage at Zero                | (Note 5)                                              |                       | -100                                         | mV   |

|                     | Differential on Transmit Return to Zero (ETD) |                                                       |                       |                                              |      |

|                     | Device Queek, Queek                           | SCLK = 25 MHz                                         |                       | 75                                           | ^    |

| I <sub>DD</sub>     | Power Supply Current                          | XTAL1 = 20 MHz                                        |                       | 75                                           | mA   |

|                     |                                               | SLEEP Asserted, AWAKE = 0                             |                       |                                              |      |

| IDDSLEEP            | Power Supply Current                          | RWAKE = 1 (Note 7)                                    |                       | 100                                          | μA   |

|                     |                                               | SLEEP Asserted, AWAKE = 1                             |                       |                                              |      |

| IDDSLEEP            | Power Supply Current                          | RWAKE = 0 (Note 7)                                    |                       | 10                                           | mA   |

|                     |                                               | SLEEP Asserted, AWAKE = 0                             |                       |                                              |      |

| IDDSLEEP            | Power Supply Current                          | RWAKE = 1 (Note 7)                                    |                       | 20                                           | mA   |

| wisted Pair         | Interface                                     |                                                       |                       |                                              |      |

| I <sub>IRXD</sub>   | Input Current at RXD±                         | AV <sub>SS</sub> < V <sub>IN</sub> < AV <sub>DD</sub> | -500                  | 500                                          | μA   |

| R <sub>RXD</sub>    | RXD± Differential Input<br>Resistance         | (Note 8)                                              | 10                    |                                              | KΩ   |

|                     | RXD±, RXD– Open Circuit                       |                                                       |                       |                                              |      |

| V <sub>TIVB</sub>   | Input Voltage (Bias)                          | I <sub>IN</sub> = 0 mA                                | AV <sub>DD</sub> –3.0 | AV <sub>DD</sub> –1.5                        | V    |

|                     | Differential Mode Input                       |                                                       |                       | <u> </u>                                     |      |

| $V_{TIDV}$          | Voltage Range (RXD±)                          | AV <sub>DD</sub> = +5V                                | -3.1                  | +3.1                                         | V    |

|                     | RXD Positive Squelch                          | Sinusoid                                              |                       | <u> </u>                                     |      |

| $V_{TSQ+}$          | Threshold (Peak)                              | 5 MHz ≤ f ≤10 MHz                                     | 300                   | 520                                          | mV   |

|                     | RXD Negative Squelch                          | Sinusoid                                              |                       |                                              |      |

| $V_{TSQ-}$          | Threshold (Peak)                              | 5 MHz $\leq$ f $\leq$ 10 MHz                          | -520                  | -300                                         | mV   |

|                     | RXD Post-Squelch                              | Sinusoid                                              |                       | <u> </u>                                     |      |

| V <sub>THS+</sub>   | Positive Threshold (Peak)                     | 5 MHz $\leq$ f $\leq$ 10 MHz                          | 150                   | 293                                          | mV   |

|                     | RXD Post-Squelch                              | Sinusoid                                              |                       | <u> </u>                                     |      |

| V <sub>THS-</sub>   | Negative Threshold) (Peak)                    | 5 MHz $\leq$ f $\leq$ 10 MHz                          | -293                  | -150                                         | mV   |

|                     | RXD Positive Squelch                          |                                                       |                       | <u>                                     </u> |      |

| V <sub>LTSQ+</sub>  | Threshold (Peak)                              |                                                       | 180                   | 312                                          | mV   |

|                     | RXD Negative Squelch                          |                                                       |                       | <u> </u>                                     |      |

| V <sub>LTSQ-</sub>  | Threshold (Peak)                              | LRT = LOW                                             | -312                  | -180                                         | mV   |

|                     | RXD Post-Squelch Positive                     |                                                       |                       |                                              |      |

| V <sub>LTHS+</sub>  |                                               | LRT = LOW                                             | 90                    | 156                                          | mV   |

|                     | Threshold (Peak)                              |                                                       |                       |                                              |      |

Specification Number 79C940B-CI (A) Rev C

### **DC CHARACTERISTICS (Continued)**

| Parameter<br>Symbol | Parameter Description                                  | Test Conditions        | Min                   | Мах                    | Unit |

|---------------------|--------------------------------------------------------|------------------------|-----------------------|------------------------|------|

| V <sub>LTHS-</sub>  | RXD Post-Squelch<br>Negative Threshold (Peak)          | LRT = LOW              | -156                  | -90                    | mV   |

| V <sub>RXDTH</sub>  | RXD Switching Threshold                                | (Note 4)               | -35                   | 35                     | mV   |

| V <sub>TXH</sub>    | TXD± and TXD± Output<br>HIGH Voltage                   | DV <sub>SS</sub> = 0V  | DV <sub>DD</sub> –0.6 | DV <sub>DD</sub>       | V    |

| V <sub>TXL</sub>    | TXD± and TXD± Output<br>LOW Voltage                    | DV <sub>DD</sub> = +5V | DV <sub>SS</sub>      | DV <sub>SS</sub> + 0.6 | V    |

| V <sub>TXI</sub>    | TXD± and TXD± Differential<br>Output Voltage Imbalance |                        | -40                   | +40                    | mV   |

| V <sub>TXOFF</sub>  | TXD± and TXD± Idle Output<br>Voltage                   | DV <sub>DD</sub> = +5V |                       | 40                     | mV   |

| R <sub>TX</sub>     | TXD± Differential Driver Output<br>Impedance           | (Note 8)               |                       | 40                     | Ω    |

|                     | TXD± Differential Driver Output<br>Impedance           | (Note 8)               |                       | 80                     | Ω    |

#### Notes:

- 1.  $V_{OH}$  does not apply to open-drain output pins.

- 2.  $I_{IL1}$  and  $I_{IL2}$  applies to all input only pins except DI±, CI±, and XTAL1.

- $I_{IL1} = ADD4-0, \overline{BE}1-0, \overline{CS}, \overline{EAM/R}, \overline{FDS}, \overline{RESET}, RXDAT, R/W, SCLK.$

- $I_{IL2} = \overline{TC}$ , TDI, TCK, TMS.

- 3. Specified for input only pins with internal pull-ups: TC, TDI, TCK, TMS.

- 4. I<sub>OZ</sub> applies to all three-state output pins and bi-directional pins.

- 5. Test not implemented to data sheet specification.

- 6. Tested, but to values in excess of limits. Test accuracy not sufficient to allow screening guard bands.

- 7. During the activation of SLEEP:

- -The following pins are placed in a high impedance state: SRD, SF/BD, TXDAT, DXCVR, DTV, TDTREQ, RDTREQ, NTR and TDO.

- -The following I/O pins are placed in a high impedance mode and have their internal TTL level translators disabled: DBUS15–0, EOF, SRDCLK, RXCRS, RXDAT, CLSN, TXEN, STDCLK and TXDAT+.

- -The following input pin has its internal pull-up and TTL level translator disabled:  $\overline{TC}$ .

- -The following input pins have their internal TTL level translators disabled and do not have internal pull-ups:  $\overline{CS}$ ,  $\overline{FDS}$ , R/W, ADD4-0, SCLK,  $\overline{BE0}$ ,  $\overline{BE1}$  and  $\overline{EAM/R}$ .

- -The following pins are pulled low: XTAL1 (XTAL2 feedback is cut off from XTAL1), TXD+, TXD-, TXP+, TXP-, DO+ and DO.

- -The following pins have their input voltage bias disabled: DI+, DI, CI+ and CI.

- -AWAKE and RWAKE are reset to zero. I<sub>DDSLEEP</sub>, with either AWAKE set or RWAKE set, will be much higher and its value remains to be determined.

- 8. Parameter not tested.

- 9. For industrial temperature version, Max value is  $-150 \ \mu A$ .

- 10. For industrial temperature version, Max value is +150  $\mu\text{A}.$

# AC CHARACTERISTICS (Unless otherwise noted, parametric values are the same between Commercial devices and Industrial devices.)

| No.      | Parameter<br>Symbol | Parameter Description                                        | Test Conditions                  | Min (ns)              | Max (ns)              |

|----------|---------------------|--------------------------------------------------------------|----------------------------------|-----------------------|-----------------------|

| Clock ar | nd Reset Timing     | ]                                                            | •                                | •                     |                       |

| 1        | t <sub>SCLK</sub>   | SCLK period                                                  |                                  | 40                    | 1000                  |

| 2        | t <sub>SCLKL</sub>  | SCLK LOW pulse width                                         |                                  | 0.4*t <sub>SCLK</sub> | 0.6*t <sub>SCLK</sub> |

| 3        | t <sub>SCLKH</sub>  | SCLK HIGH pulse width                                        |                                  | 0.4*t <sub>SCLK</sub> | 0.6*t <sub>SCLK</sub> |

| 4        | t <sub>SCLKR</sub>  | SCLK rise time                                               |                                  |                       | 5                     |

| 5        | t <sub>SCLKF</sub>  | SCLK fall time                                               |                                  |                       | 5                     |

| 6        | t <sub>RST</sub>    | RESET pulse width                                            |                                  | 15*t <sub>SCLK</sub>  |                       |

| 7        | t <sub>BT</sub>     | Network Bit Time (BT)=2*tX1 or tSTDC                         |                                  | 99                    | 101                   |

| Internal | MENDEC Clock        | Timing                                                       |                                  |                       |                       |

| 9        | t <sub>X1</sub>     | XTAL1 period                                                 |                                  | 49.995                | 50.005                |

| 11       | t <sub>X1H</sub>    | XTAL1 HIGH pulse width                                       |                                  | 20                    |                       |

| 12       | t <sub>X1L</sub>    | XTAL1 LOW pulse width                                        |                                  | 20                    |                       |

| 13       | t <sub>X1R</sub>    | XTAL1 rise time                                              |                                  |                       | 5                     |

| 14       | t <sub>X1F</sub>    | XTAL1 fall time                                              |                                  |                       | 5                     |

| BIU TIM  | ING (Note 1)        | ·                                                            |                                  |                       |                       |

| 31       | t <sub>ADDS</sub>   | Address valid setup to SCLK $\downarrow$                     |                                  | 9                     |                       |

| 32       | t <sub>ADDH</sub>   | Address valid hold after SCLK $\downarrow$                   |                                  | 2                     |                       |

| 1. 33    | +                   | CS or FDS and TC, BE1–0,                                     |                                  | 9                     |                       |

|          | t <sub>SLVS</sub>   | R/W setup to SCLK↓                                           |                                  | 9                     |                       |

| 34       | +                   | CS or FDS and TC, BE1–0,                                     |                                  | 2                     |                       |

| 54       | t <sub>SLVH</sub>   | R/₩ hold after SCLK↓                                         |                                  | 2                     |                       |

| 35       | t <sub>DATD</sub>   | Data out valid delay from SCLK $\downarrow$                  | C <sub>L</sub> = 100 pF (Note 2) |                       | 32                    |

| 36       | t <sub>DATH</sub>   | Data out valid hold from SCLK $\downarrow$                   |                                  | 6                     |                       |

| 37       | t <sub>DTVD</sub>   | DTV valid delay from SCLK $\downarrow$                       | C <sub>L</sub> = 100 pF (Note 2) |                       | 32                    |

| 38       | t <sub>DTVH</sub>   | DTV valid hold after SCLK↓                                   |                                  | 6                     |                       |

| 39       | t <sub>EOFD</sub>   | EOF valid delay from SCLK↓                                   | C <sub>L</sub> = 100 pF (Note 2) |                       | 32                    |

| 40       | t <sub>EOFH</sub>   | EOF output valid hold after SCLK $\downarrow$                |                                  | 6                     |                       |

| 41       | t <sub>CSIS</sub>   | CS inactive prior to SCLK $\downarrow$                       |                                  | 9                     |                       |

| 42       | t <sub>EOFS</sub>   | EOF input valid setup to SCLK $\downarrow$                   |                                  | 9                     |                       |

| 43       | t <sub>EOFH</sub>   | EOF input valid hold after SCLK $\downarrow$                 |                                  | 2                     |                       |

| 44       | t <sub>RDTD</sub>   | RDTREQ valid delay from SCLK $\downarrow$                    | C <sub>L</sub> = 100 pF (Note 2) |                       | 32                    |

| 45       | t <sub>RDTH</sub>   | $\overline{RDTREQ}$ input valid hold after SCLK $\downarrow$ |                                  | 6                     |                       |

| 46       | t <sub>TDTD</sub>   | TDTREQ valid delay from SCLK↓                                | C <sub>L</sub> = 100 pF (Note 2) |                       | 32                    |

| 47       | t <sub>тотн</sub>   | TDTREQ input valid hold after SCLK $\downarrow$              |                                  | 6                     |                       |

| 48       | t <sub>DATS</sub>   | Data in valid setup to SCLK $\downarrow$                     |                                  | 9                     |                       |

| 49       | t <sub>DATIH</sub>  | Data in valid setup after SCLK $\downarrow$                  |                                  | 2                     |                       |

| 50       | t <sub>DATE</sub>   | Data output enable delay from SCLK $\downarrow$ (Note 3)     |                                  | 0                     |                       |

| 51       | t <sub>DATD</sub>   | Data output disable delay from SCLK $\downarrow$ (Note 3, 4) |                                  |                       | 25                    |

#### Notes:

The following BIU timing assumes that EDSEL = 1. Therefore, these parameters are specified with respect to the falling edge of SCLK (SCLK↓). If EDSEL = 0, the same parameters apply but should be referenced to the rising edge of SCLK ↑).

2. Tested with C<sub>L</sub> set at 100 pF and derated to support the Indicated distributed capacitive Load. See the BIU output valid delay vs. Load Chart.

3. Guaranteed by design-not tested.

4. t<sub>DATD</sub> is defined as the time required for outputs to turn high impedence and is not referred to as output voltage lead.

# AC CHARACTERISTICS (continued)

| No.      | Parameter<br>Symbol  | Parameter Description                                                                                                                          | Test Conditions            | Min (ns)               | Max (ns)             |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|----------------------|

| AUI Timi | ing                  |                                                                                                                                                |                            |                        |                      |

| 53       | t <sub>DOTD</sub>    | XTAL1 (externally driven) to DO± ουτπυτ                                                                                                        |                            |                        | 100                  |

| 54       | t <sub>DOTR</sub>    | DO± rise time (10% to 90%)                                                                                                                     |                            | 2.5                    | 5.0                  |

| 55       | t <sub>DOTF</sub>    | DO± fall time (10% to 90%)                                                                                                                     |                            | 2.5                    | 5.0                  |

| 56       | t <sub>DOETM</sub>   | DO± rise and fall mismatch                                                                                                                     |                            |                        | 1                    |

| 57       | t <sub>DOETD</sub>   | DO± End of Transmit Delimiter                                                                                                                  |                            | 200                    | 375                  |

| 58       | t <sub>PWRDI</sub>   | DI± pulse width to reject                                                                                                                      | input  >   <sub>VASQ</sub> |                        | 15                   |

| 59       | t <sub>PWODI</sub>   | DI± pulse width to turn on internal DI carrier sense                                                                                           | input  >   <sub>VASQ</sub> | 45                     |                      |

| 60       | t <sub>PWMDI</sub>   | DI± pulse width to maintain internal DI carrier sense on                                                                                       | input  >   <sub>VASQ</sub> | 45                     | 136                  |

| 61       | t <sub>PWKDI</sub>   | DI± pulse width to turn internal DI carrier sense off                                                                                          | input  >   <sub>VASQ</sub> | 200                    |                      |

| 62       | t <sub>PWRCI</sub>   | CI± pulse width to reject                                                                                                                      | input  >   <sub>VASQ</sub> |                        | 10                   |

| 63       | t <sub>PWOCI</sub>   | $Cl\pm$ pulse width to turn on internal SQE sense                                                                                              | input  >   <sub>VASQ</sub> | 26                     |                      |

| 64       | t <sub>PWMCI</sub>   | Cl± pulse width to maintain internal SQE sense on                                                                                              | input  >   <sub>VASQ</sub> | 26                     | 90                   |

| 65       | t <sub>PWKCI</sub>   | Cl± pulse width to turn internal SQE sense off                                                                                                 | input  >   <sub>VASQ</sub> | 160                    |                      |

| 66       | t <sub>SQED</sub>    | CI± SQE Test delay from O± inactive                                                                                                            | input  >   <sub>VASQ</sub> |                        |                      |

| 67       | t <sub>SQEL</sub>    | CI± SQE Test length                                                                                                                            | input  >   <sub>VASQ</sub> |                        |                      |

| 79       | t <sub>CLSHI</sub>   | CLSN high time                                                                                                                                 |                            | t <sub>STDC</sub> + 30 |                      |

| 80       | t <sub>TXH</sub>     | TXEN or DO± hold time from CLSN↑                                                                                                               | input  >   <sub>VASQ</sub> | 32*t <sub>STDC</sub>   | 96*t <sub>STDC</sub> |

| DAI Port | Timing               |                                                                                                                                                |                            |                        |                      |

| 70       | t <sub>TXEND</sub>   | STDCLK <sup>↑</sup> delay to $\overline{TXEN}\downarrow$                                                                                       | C <sub>L</sub> = 50 pF     |                        | 70                   |

| 72       | t <sub>TXDD</sub>    | STDCLK <sup>↑</sup> delay to TXDAT± change                                                                                                     | C <sub>L</sub> = 50 pF     |                        | 70                   |

| 80       | t <sub>TXH</sub>     | $\overline{TXEN}$ or $TXDAT\pm$ hold time from $CLSN\uparrow$                                                                                  |                            | 32*t <sub>STDC</sub>   | 96*t <sub>STDC</sub> |

| 95       | t <sub>DOTF</sub>    | $\frac{\text{Mismatch in STDCLK} \neq \text{to } \overline{\text{TXEN}} \downarrow \text{ and } }{\overline{\text{TXDAT}} \pm \text{ change}}$ |                            |                        | 15                   |

| 96       | t <sub>TXDTR</sub>   | TXDAT± rise time                                                                                                                               | See Note 1                 |                        | 5                    |

| 97       | t <sub>TXDTF</sub>   | TXDAT± fall time                                                                                                                               | See Note 1                 |                        | 5                    |

| 98       | t <sub>TXDTM</sub>   | TXDAT± rise and fall mismatch                                                                                                                  | See Note 1                 |                        | 1                    |

| 99       | t <sub>TXENETD</sub> | TXEN End of Transmit Delimiter                                                                                                                 |                            | 250                    | 350                  |

| 100      | t <sub>FRXDD</sub>   | First RXDAT↓ delay to RXCRS↑                                                                                                                   |                            |                        | 100                  |

| 101      | t <sub>LRXDD</sub>   | Last RXDAT $\neq$ delay to RXCRS $\downarrow$                                                                                                  |                            |                        | 120                  |

| 102      | t <sub>CRSCLSD</sub> | RXCRS <sup><math>\uparrow</math></sup> delay to CLSN <sup><math>\uparrow</math></sup> (TXEN = 0)                                               |                            |                        | 100                  |

# AC CHARACTERISTICS (continued)

| No.        | Parameter<br>Symbol  | Parameter Description                                                       | Test Conditions          | Min (ns)               | Max (ns)             |

|------------|----------------------|-----------------------------------------------------------------------------|--------------------------|------------------------|----------------------|

| GPSI Cloci | k Timing             |                                                                             | L                        | 1                      |                      |

| 17         | t <sub>STDC</sub>    | STDCLK period                                                               |                          | 99                     | 101                  |

| 18         | t <sub>STDCL</sub>   | STDCLK low pulse width                                                      | See Note 1               | 45                     |                      |

| 19         | t <sub>STDCH</sub>   | STDCLK high pulse width                                                     |                          | 45                     |                      |

| 20         | t <sub>STDCR</sub>   | STDCLK rise time                                                            | See Note 1               |                        | 5                    |

| 21         | t <sub>STDCF</sub>   | STDCLK fall time                                                            | See Note 1               |                        | 5                    |

| 22         | t <sub>SRDC</sub>    | SRDCLK period                                                               |                          | 85                     | 115                  |

| 23         | t <sub>SRDCH</sub>   | SRDCLK HIGH pulse width                                                     |                          | 38                     |                      |

| 24         | t <sub>SRDCL</sub>   | SRDCLK LOW pulse width                                                      |                          | 38                     |                      |

| 25         | t <sub>SRDCR</sub>   | SRDCLK rise time                                                            | See Note 1               |                        | 5                    |

| 26         | t <sub>SRDCF</sub>   | SRDCLK fall time                                                            | See Note 1               |                        | 5                    |

| GPSI Timir | ng                   |                                                                             |                          |                        |                      |

| 70         | t <sub>TXEND</sub>   | STDCLK <sup>↑</sup> delay to TXEN <sup>↑</sup>                              | (C <sub>L</sub> = 50 pF) |                        | 70                   |

| 71         | t <sub>TXENH</sub>   | TXEN hold time from STDCLK <sup>↑</sup>                                     | (C <sub>L</sub> = 50 pF) | 5                      |                      |

| 72         | t <sub>TXDD</sub>    | STDCLK <sup>↑</sup> delay to TXDAT+ change                                  | (C <sub>L</sub> = 50 pF) |                        | 70                   |

| 73         | t <sub>TXDH</sub>    | TXDAT+ hold time from STDCLK↑                                               | (C <sub>L</sub> = 50 pF) | 5                      |                      |

| 74         | t <sub>RXDR</sub>    | RXDAT rise time                                                             | See Note 1               |                        | 8                    |

| 75         | t <sub>RXDF</sub>    | RXDAT fall time                                                             | See Note 1               |                        | 8                    |

| 76         | t <sub>RXDH</sub>    | RXDAT hold time (SRDCLK <sup>↑</sup> to RXDAT change)                       |                          | 25                     |                      |

| 77         | t <sub>RXDS</sub>    | RXDAT setup time (RXDAT stable to SRDCLK <sup>↑</sup> )                     |                          | 0                      |                      |

| 78         | t <sub>CRSL</sub>    | RXCRS low time                                                              |                          | t <sub>STDC</sub> + 20 |                      |

| 79         | t <sub>CLSHI</sub>   | CLSN high time                                                              |                          | t <sub>STDC</sub> + 30 |                      |

| 80         | t <sub>TXH</sub>     | TXEN or TXDAT± hold time from<br>CLSN↑                                      |                          | 32*t <sub>STDC</sub>   | 96*t <sub>STDC</sub> |

| 81         | t <sub>CRSH</sub>    | RXCRS hold time from SRDCLK1                                                |                          | 0                      |                      |

| ADI Featu  | ure Timing           |                                                                             |                          |                        |                      |

| 85         | t <sub>DSFBDR</sub>  | SRDCLK↓ delay to SF/BD↑                                                     |                          |                        | 20                   |

| 86         | t <sub>DSFBDF</sub>  | SRDCLK↓ delay to SF/BD↑                                                     |                          |                        | 20                   |

| 87         | t <sub>EAMRIS</sub>  | EAM/R invalid setup prior to<br>SRDCLK↓ after SFD                           |                          | -150                   |                      |

| 88         | t <sub>EAMS</sub>    | EAM setup to SRDCLK↓ at bit 6 of<br>Source Address byte 1 (match<br>packet) |                          | 0                      |                      |

| 89         | t <sub>EAMR</sub> L  | EAM/R low time                                                              |                          | 200                    |                      |

| 90         | t <sub>SFBDHIH</sub> | SF/BD high hold from last<br>SRDCLK↓                                        |                          | 100                    |                      |

| 91         | t <sub>EARS</sub>    | EAR setup SRDCLK↓ at bit 6 of<br>message byte 64<br>(reject normal packet)  |                          | 0                      |                      |

Note:

1. Not tested but data available upon request.

## AC CHARACTERISTICS (continued)

| No.      | Parameter<br>Symbol | Parameter Description                                                                                           | Test Conditions     | Min                   | Мах                    |

|----------|---------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------|

| IEEE 114 | 9.1 Timing          |                                                                                                                 | <u>I</u> I          |                       |                        |

| 109      | t <sub>TCLK</sub>   | TCK Period, 50% duty cycle (+5%)                                                                                |                     | 100                   |                        |

| 110      | t <sub>su1</sub>    | TMS setup to TCK↑                                                                                               |                     | 8                     |                        |

| 111      | t <sub>su2</sub>    | TDI setup to TCK↑                                                                                               |                     | 5                     |                        |

| 112      | t <sub>hd1</sub>    | TMS hold time from TCK↑                                                                                         |                     | 5                     |                        |

| 113      | t <sub>hd2</sub>    | TDI hold time from TCK↑                                                                                         |                     | 10                    |                        |

| 114      | t <sub>d1</sub>     | TCK↓ delay to TDO                                                                                               |                     |                       | 30                     |

| 115      | t <sub>d2</sub>     | TCK↓ delay to SYSTEM OUTPUT                                                                                     |                     |                       | 35                     |

| 10BASE-  | -T Transmit Ti      | ming                                                                                                            |                     | Min                   | Max                    |

| 125      | t <sub>TETD</sub>   | Transmit Start of Idle                                                                                          |                     | 250                   | 350                    |

| 126      | t <sub>TR</sub>     | Transmitter Rise Time                                                                                           | (10% to 90%)        |                       | 5.5                    |

| 127      | t <sub>TF</sub>     | Transmitter Fall Time                                                                                           | (90% to 10%)        |                       | 5.5                    |

| 128      | t <sub>TM</sub>     | Transmitter Rise and Fall Time Mismatch                                                                         |                     |                       | 1                      |

| 129      | t <sub>XMTON</sub>  | XMT# Asserted Delay                                                                                             |                     |                       | 100                    |

| 130      | t <sub>XMTOFF</sub> | XMT# De-asserted Delay                                                                                          |                     | TBD                   | TBD                    |

| 131      | t <sub>PERLP</sub>  | Idle Signal Period                                                                                              |                     | 8                     | 24                     |

| 132      | t <sub>PWLP</sub>   | Idle Link Pulse Width                                                                                           | (Note 1)            | 75                    | 120                    |

| 133      | t <sub>PWPLP</sub>  | Predistortion Idle Link Pulse Width                                                                             | (Note 1)            | 45                    | 55                     |

| 134      | t <sub>JA</sub>     | Transmit Jabber Activation Time                                                                                 |                     | 20                    | 150                    |

| 135      | t <sub>JR</sub>     | Transmit Jabber Reset Time                                                                                      |                     | 250                   | 750                    |

| 136      | t <sub>JREC</sub>   | Transmit Jabber Recovery Time (Minimum<br>Time Gap Between Transmitted Packets to<br>Prevent Jabber Activation) |                     | 1.0                   |                        |

| 10BASE-  | -T Receive Tin      | ning                                                                                                            |                     |                       |                        |

| 140      | t <sub>PWNRD</sub>  | RXD Pulse Width Not to Turn Off Internal Carrier Sense                                                          | VIN > VTHS<br>(min) | 136                   | -                      |

| 141      | t <sub>PWROFF</sub> | RXD Pulse Width to Turn Off VIN> VTHS (min)                                                                     |                     | 200                   |                        |

| 142      | t <sub>RETD</sub>   | Receive Start of Idle                                                                                           |                     | 200                   |                        |

| 143      | t <sub>RCVON</sub>  | RCV# Asserted Delay                                                                                             |                     | t <sub>RON</sub> – 50 | t <sub>RON</sub> – 100 |

| 144      | t <sub>RCVOFF</sub> | RCV# De-asserted Delay                                                                                          |                     | TBD                   | TBD                    |

#### Note:

1. Not tested but data available upon request.

Rochester Electronics guarantees performance of its semiconductor products to the original OEM specifications. "Typical" values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing. Rochester Electronics reserves the right to make changes without further notice to any specification herein.