19-0602; Rev 2; 1/07

AVAILABLE

#### **Features**

**General Description**

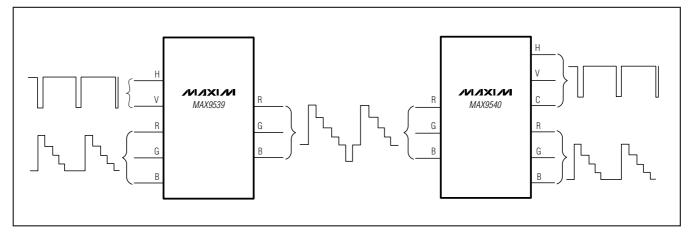

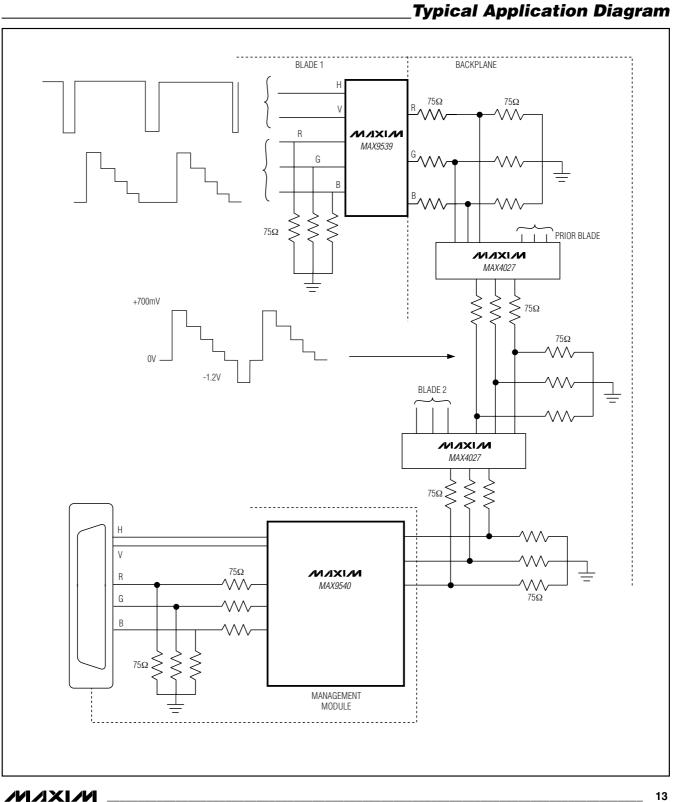

The MAX9539/MAX9540 chipset provides a 3-wire (RGB) interface for 5-wire (RGBHV) video by adding and extracting the H, V, and composite sync from the graphics video signals. This chipset eliminates the problem of sync-to-video timing (skew errors) in a 5wire interface, while reducing the number of channels required to transport video signals.

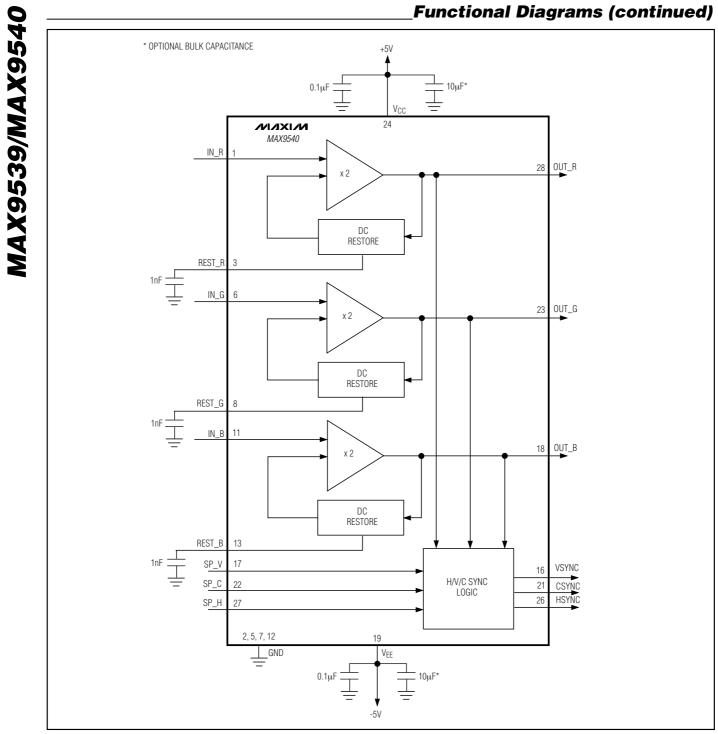

The MAX9539 mixes the H and V sync signals and adds them to create a 3-wire interface from a 5-wire (RGBHV) input. The MAX9540 recovers the H and V sync signals to create a 5-wire (RGBHV) interface from the 3-wire input. The MAX9540 also provides a composite sync output.

The chipset includes the MAX9539 sync adder and the MAX9540 sync extractor with 180MHz large-signal bandwidths to address display resolutions up to 1600 x 1200 at 85Hz for VGA-to-UXGA applications. Both devices feature a DC restore function, which virtually eliminates any changes in black level. The chipset uses a proprietary H and V sync addition/extraction scheme (true sync) to minimize skew errors.

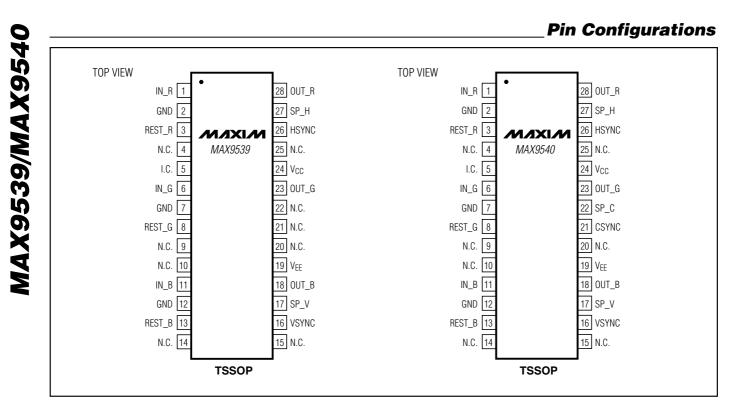

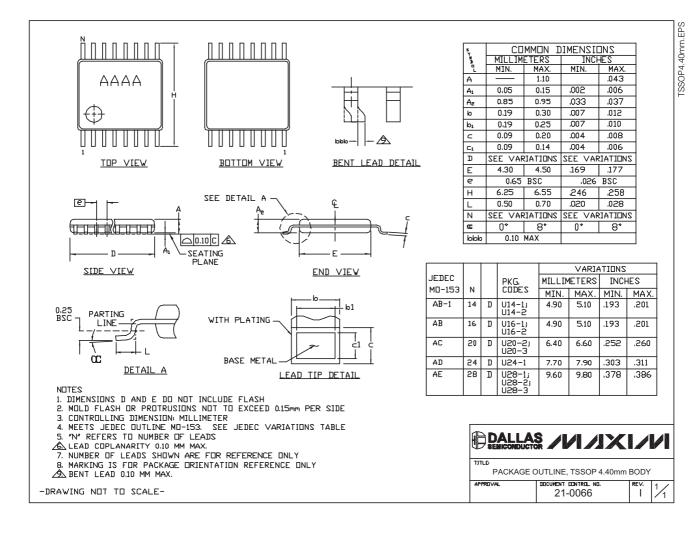

The MAX9539/MAX9540 are available in 28-pin TSSOP packages and are specified over the extended -40°C to +85°C temperature range.

#### **Applications**

Enterprise Class (Blade) Servers Laptop PCs Web Appliances Keyboard-Video-Mouse (KVM)

- 3-Wire RBG to 5-Wire RBGHV Interface

- Supports VGA-to-UXGA Resolution

- Low Offset Voltage (±1mV)

- 180MHz Large-Signal Bandwidth

### **Ordering Information**

| PIN-<br>PACKAGE | PKG<br>CODE                     | DESCRIPTION                                                     |

|-----------------|---------------------------------|-----------------------------------------------------------------|

| 28 TSSOP        | U28-3                           | Sync Adder                                                      |

| 28 TSSOP        | U28-3                           | Sync Adder                                                      |

| 28 TSSOP        | U28-3                           | Sync Extractor                                                  |

| 28 TSSOP        | U28-3                           | Sync Extractor                                                  |

|                 | PACKAGE28 TSSOP28 TSSOP28 TSSOP | PACKAGE CODE   28 TSSOP U28-3   28 TSSOP U28-3   28 TSSOP U28-3 |

Note: All devices are specified over the -40°C to +85°C operating temperature range.

+Denotes lead-free package.

\*Future product—contact factory for availability.

Pin Configurations appear at end of data sheet.

### **Chipset Diagram**

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

| 0                 |

|-------------------|

| 1                 |

| Y                 |

| S)                |

| 0                 |

| Ľ.                |

|                   |

|                   |

|                   |

| 2                 |

| $\mathbf{\Sigma}$ |

| 5                 |

| <b>m</b>          |

| Ŋ                 |

| 0                 |

| Ň.                |

|                   |

| 4                 |

| Ę                 |

| $\leq$            |

|                   |

### **ABSOLUTE MAXIMUM RATINGS**

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |               |

|-------------------------------------------------------|---------------|

| 28-Pin TSSOP (U28-3) Single-Layer Board               |               |

| (derate 13mW/°C above +70°C)                          | 1039mW        |

| 28-Pin TSSOP (U28-3) Multilayer Board                 |               |

| (derate 14.3mW/°C above +70°C)                        | 1143mW        |

| Operating Temperature                                 | 40°C to +85°C |

| Junction Temperature                                  | +150°C        |

| Storage Temperature Range                             |               |

| Lead Temperature (soldering, 10s)                     | +300°C        |

**Note 1:** Continuous power dissipation rating must also be observed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### MAX9539 DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V, V_{EE} = -5V, GND = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 2 and 3)

| PARAMETER                                           | SYMBOL                                                                          | CONDITIONS                                                      | MIN   | ТҮР   | MAX   | UNITS |

|-----------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------|-------|-------|-------|-------|

|                                                     | Vcc                                                                             | Guaranteed by PSRR test                                         | 4.5   |       | 5.5   | V     |

| Supply Voltage Range                                | VEE                                                                             | Guaranteed by PSRR test                                         | -5.5  |       | -4.5  | v     |

| Quiescent Supply Current                            | Icc                                                                             | R <sub>L</sub> = ∞                                              |       | 61    | 90    | mA    |

|                                                     | IEE                                                                             | R <sub>L</sub> = ∞                                              | 55    |       | 75    | ШA    |

| Input Voltage Range                                 | VIN                                                                             | Inferred from voltage gain test                                 | 0     |       | 1     | V     |

| DC-Restore Input Voltage Range                      | $\Delta V_{IN}_{RESTORE}$                                                       | Inferred from output DC-Restore<br>Rejection Ratio test         | -0.30 |       | +0.30 | V     |

| DC-Restore Rejection Ratio                          | DCRR<br>( $\Delta V_{OS}$ /<br>$\Delta V_{IN_RESTORE}$ )                        | $V_{IN\_RESTORE} = -0.3V$ to +0.3V                              | 28    | 50    |       | dB    |

| Input Bias Current                                  | IB                                                                              |                                                                 |       | ±2    | ±30   | μA    |

| Input Resistance                                    | R <sub>IN</sub>                                                                 |                                                                 |       | 400   |       | kΩ    |

| Output Sync Amplitude                               | VSYNC                                                                           | H or V sync is active                                           | -2.65 | -2.35 | -2.05 | V     |

| Output Offset Voltage                               | V <sub>OS</sub>                                                                 | $\Delta V_{IN\_RESTORE\_} = 0V, T_A = +25^{\circ}C$<br>(Note 4) |       | ±1    | ±8    | mV    |

| Temperature Coefficient of<br>Output Offset Voltage | $\frac{\text{TCV}_{\text{OS}}}{(\Delta V_{\text{OS}}  /  \Delta T_{\text{A}})}$ | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                   |       | -24   |       | µV/°C |

| Voltage Gain                                        | G                                                                               | $V_{IN} = 0 \text{ to } + 1 \text{V}$                           | +1.95 | +2    | +2.05 | V/V   |

| Gain Matching                                       | ΔG                                                                              | R to G to B                                                     |       | ±1    | ±2    | %     |

| Gain Linearity                                      |                                                                                 |                                                                 |       | 0.02  |       | %     |

| Power-Supply Rejection Ratio                        | PSRR<br>ΔV <sub>OS</sub> /<br>Δ(V <sub>CC</sub> - V <sub>EE</sub> )             | V <sub>CC</sub> , V <sub>EE</sub> = $\pm 4.5$ V to $\pm 5.5$ V  | 50    | 70    |       | dB    |

## MAX9539 DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +5V, V_{EE} = -5V, GND = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 2 and 3)

| PARAMETER                  | SYMBOL | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|----------------------------|--------|------------|-----|-----|-----|-------|

| HSYNC, VSYNC INPUTS        | ·      | <u>.</u>   |     |     |     |       |

| High Input Voltage         | VIH    |            | 2   |     |     | V     |

| Low Input Voltage          | VIL    |            |     |     | 0.8 | V     |

| High Input Current         | Ιн     | $V_I = 5V$ |     | 10  | 60  | μΑ    |

| Low Input Current          | ЦĽ     | $V_I = OV$ |     | 2.5 |     | μA    |

| SP_H, SP_V INPUTS          |        |            |     |     |     |       |

| High Input Voltage         | VIH    |            | 2   |     |     | V     |

| Low Input Voltage          | VIL    |            |     |     | 0.8 | V     |

| High Input Current         | Ιн     | $V_I = 5V$ |     | 0.1 | 20  | μA    |

| Low Input Current          | ЦĽ     | $V_I = OV$ |     | 1   | 20  | μA    |

| REST_R, REST_B, REST_G INF | PUTS   |            |     |     |     | •     |

| Hold-Mode Droop Current    | IDROOP |            |     | ±2  |     | nA    |

### **MAX9539 AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5V, V_{EE} = -5V, GND = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                              | SYMBOL            | CONDITIONS                    | MIN TYP MAX | UNITS  |

|----------------------------------------|-------------------|-------------------------------|-------------|--------|

| Large-Signal Bandwidth                 | LSBW              | $V_{OUT} = 2V_{P-P}$          | 180         | MHz    |

| Slew Rate                              | SR                | $V_{OUT} = 2V_{P-P}$          | 900         | V/µs   |

| Channel-to-Channel Crosstalk           | X <sub>TALK</sub> | $V_{OUT} = 2V_{P-P}$ at 10MHz | -60         | dB     |

| Settling Time                          | ts                | $V_{OUT} = 2V_{P-P}$ to 0.1%  | 15          | ns     |

| Input Voltage-Noise Density            | en                | f = 100kHz                    | 30          | nV/√Hz |

| Input Current-Noise Density            | in                | f = 100kHz                    | 12          | pA/√Hz |

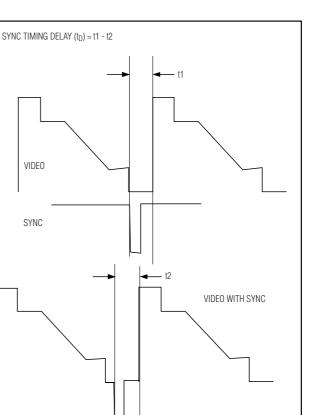

| Sync Timing Delay                      | tD                | H sync only (Note 5)          | -20         | ns     |

| Channel-to-Channel Sync Timing<br>Skew | $\Delta(t_D)$     | H sync only (Note 5)          | 1           | ns     |

| Sync Edge Jitter                       | <b>t</b> JITTER   |                               | 200         | psp-p  |

| Line Droop                             |                   | f = 50kHz                     | 0.01        | %      |

| Field Tilt                             |                   | f = 60Hz                      | 0.04        | %      |

|                                        | fH                | H sync                        | 15 to 150   | kHz    |

| Sync Frequency Range                   | fv                | V sync                        | 40 to 100   | Hz     |

### MAX9540 DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V, V_{EE} = -5V, GND = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .) (Notes 2 and 3)

| PARAMETER                                           | SYMBOL                                                              | CONDITIONS                                                      | MIN   | ТҮР  | MAX   | UNITS |

|-----------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|-------|------|-------|-------|

| Owen ha Malta and Damana                            | Vcc                                                                 | Guaranteed by PSRR test                                         | 4.5   |      | 5.5   | N     |

| Supply Voltage Range                                | VEE                                                                 | Guaranteed by PSRR test                                         | -5.5  |      | -4.5  | V     |

|                                                     | Icc                                                                 | $R_L = \infty$                                                  |       | 61   | 90    |       |

| Quiescent Supply Current                            | IEE                                                                 | R <sub>L</sub> = ∞                                              |       | 54   | 75    | mA    |

| Input Voltage Range                                 | VIN                                                                 | Inferred from voltage gain test                                 | 0     |      | 1     | V     |

| DC-Restore Input Voltage Range                      | $\Delta V_{IN}_{RESTORE}$                                           | Inferred from DC-Restore Rejection<br>Ratio test                | -0.30 |      | +0.30 | V     |

| DC-Restore Rejection Ratio                          | DCRR<br>(ΔV <sub>OS</sub> /<br>ΔVIN_RESTORE)                        | VIN_RESTORE = -0.3V to +0.3V                                    | 28    | 50   |       | dB    |

| Input Bias Current                                  | IB                                                                  |                                                                 |       | ±2   | ±30   | μA    |

| Input Resistance                                    | RIN                                                                 |                                                                 |       | 400  |       | kΩ    |

| Output Black Level                                  | VBLACK                                                              | H or V sync is active: V <sub>IN</sub> < -1V                    |       | ±1   | ±16   | mV    |

| Output Offset Voltage                               | VOS                                                                 | $\Delta V_{IN\_RESTORE\_} = 0V, T_A = +25^{\circ}C$<br>(Note 4) |       | ±1   | ±8    | mV    |

| Temperature Coefficient of<br>Output Offset Voltage | TCV <sub>OS</sub><br>(ΔV <sub>OS</sub> /ΔΤ <sub>Α</sub> )           | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                 |       | -24  |       | µV/°C |

| Voltage Gain                                        | G                                                                   | $V_{IN} = 0$ to $+1V$                                           | +1.95 | +2   | +2.05 | V/V   |

| Gain Matching                                       | ΔG                                                                  | R to G to B                                                     |       | ±1   | ±2    | %     |

| Gain Linearity                                      |                                                                     |                                                                 |       | 0.02 |       | %     |

| Power-Supply Rejection Ratio                        | PSRR<br>ΔV <sub>OS</sub> /<br>Δ(V <sub>CC</sub> - V <sub>EE</sub> ) | $V_{CC}$ , $V_{EE} = \pm 4.5V$ to $\pm 5.5V$                    | 50    | 70   |       | dB    |

| SP_H, SP_V, SP_C INPUTS                             | ·                                                                   |                                                                 |       |      |       |       |

| High Input Voltage                                  | VIH                                                                 |                                                                 | 2     |      |       | V     |

| Low Input Voltage                                   | VIL                                                                 |                                                                 |       |      | 0.8   | V     |

| High Input Current                                  | ЧН                                                                  | $V_{I} = 5V$                                                    |       | 0.01 | 20    | μA    |

| Low Input Current                                   | ΙĮĽ                                                                 | $V_{I} = 0V$                                                    |       | 1    | 20    | μA    |

| REST_R, REST_G, REST_B INPL                         | JTS                                                                 |                                                                 |       |      |       |       |

| Hold-Mode Droop Current                             | IDROOP                                                              |                                                                 |       | ±2   |       | nA    |

| HSYNC, VSYNC, CSYNC OUTPU                           | TS                                                                  |                                                                 |       |      |       |       |

| High Voltage Level                                  | VOH                                                                 | I <sub>OH</sub> (source) = +8mA                                 | 2.4   |      |       | V     |

| Low Voltage Level                                   | Vol                                                                 | I <sub>OL</sub> (sink) = -8mA                                   |       |      | 0.5   | V     |

### MAX9540 AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V, V_{EE} = -5V, GND = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                    | SYMBOL            | CONDITIONS                                    | MIN TYP MAX | UNITS  |

|------------------------------|-------------------|-----------------------------------------------|-------------|--------|

| Large-Signal Bandwidth       | LSBW              | V <sub>OUT</sub> = 2V <sub>P-P</sub>          | 180         | MHz    |

| Slew Rate                    | SR                | V <sub>OUT</sub> = 2V <sub>P-P</sub>          | 900         | V/µs   |

| Channel-to-Channel Crosstalk | X <sub>TALK</sub> | V <sub>OUT</sub> = 2V <sub>P-P</sub> at 10MHz | -60         | dB     |

| Settling Time                | ts                | $V_{OUT} = 2V_{P-P}$ to 0.1%                  | 15          | ns     |

| Input Voltage-Noise Density  | en                | f = 100kHz                                    | 30          | nV/√Hz |

| Input Current-Noise Density  | in                | f = 100kHz                                    | 12          | pA/√Hz |

| Sync Timing Delay            | t <sub>D</sub>    | H sync only (Note 5)                          | -10         | ns     |

| Sync Timing Skew             | $\Delta(t_D)$     | H sync only (Note 5)                          | 1           | ns     |

| Sync Edge Jitter             | <b>UITTER</b>     |                                               | 200         | psp-p  |

| Line Droop                   |                   | f = 50kHz                                     | 0.01        | %      |

| Field Tilt                   |                   | f = 60Hz                                      | 0.04        | %      |

|                              | fH                | H sync                                        | 15 to 150   | kHz    |

| Sync Frequency Range         | fv                | V sync                                        | 40 to 100   | Hz     |

**Note 2:** All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature limits are guaranteed by design. **Note 3:** DC restore is not active. HSYNC and VSYNC are not applied. REST\_R, REST\_G, and REST\_B are grounded.

Note 4: DC restore is active. REST\_R, REST\_G, and REST\_B are bypassed with 1nF to ground.

Note 5: The sync timing error is measured as follows: The input signals are measured from the falling edge of H sync/V sync to the start of active video, called t1. The output signal is then measured from the falling edge of H sync/V sync to the start of active video, called t2. All measurements are at the 50% points as shown in Figure 1.

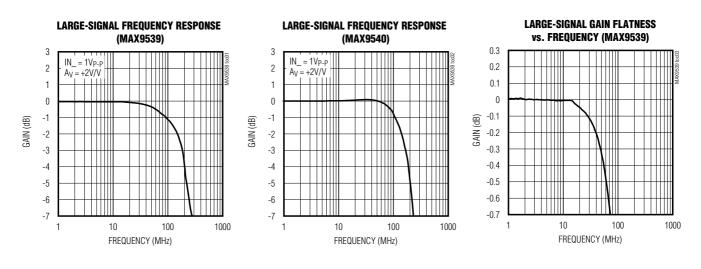

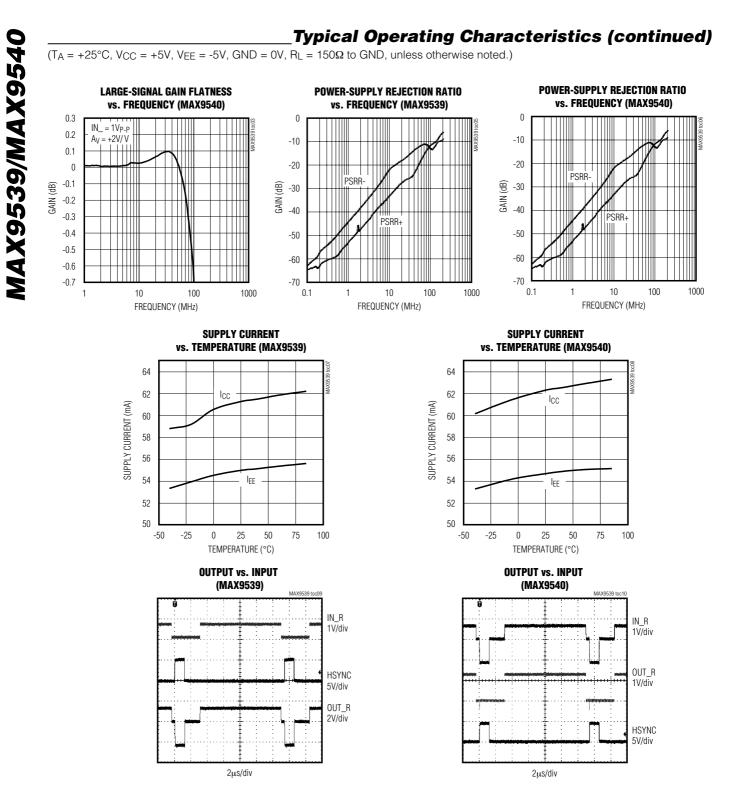

### **Typical Operating Characteristics**

(T\_A = +25°C, V\_{CC} = +5V, V\_{EE} = -5V, GND = 0V, R<sub>L</sub> = 150 $\Omega$  to GND, unless otherwise noted.)

| PIN                                    | NAME   | FUNCTION                                                             |

|----------------------------------------|--------|----------------------------------------------------------------------|

| 1                                      | IN_R   | Red Video Input                                                      |

| 2, 7, 12                               | GND    | Ground                                                               |

| 3                                      | REST_R | Red DC Restore. Connect a 1nF capacitor from REST_R to GND.          |

| 4, 9, 10, 14,<br>15, 20, 21,<br>22, 25 | N.C.   | No Connection. Not internally connected.                             |

| 5                                      | I.C.   | Internally Connected. For best performance, connect this pin to GND. |

| 6                                      | IN_G   | Green Video Input                                                    |

| 8                                      | REST_G | Green DC Restore. Connect a 1nF capacitor from REST_G to GND.        |

| 11                                     | IN_B   | Blue Video Input                                                     |

| 13                                     | REST_B | Blue DC Restore. Connect a 1nF capacitor from REST_B to GND.         |

| 16                                     | VSYNC  | Vertical Sync Input                                                  |

| 17                                     | SP_V   | Vertical Sync Polarity Input                                         |

| 18                                     | OUT_B  | Blue Output with Vertical Sync                                       |

| 19                                     | VEE    | Negative Power-Supply Input. Bypass with a 0.1µF capacitor to GND.   |

| 23                                     | OUT_G  | Green Output with Composite Sync.                                    |

| 24                                     | Vcc    | Positive Power-Supply Input. Bypass with a 0.1µF capacitor to GND.   |

| 26                                     | HSYNC  | Horizontal Sync Input                                                |

| 27                                     | SP_H   | Horizontal Sync Polarity Input                                       |

| 28                                     | OUT_R  | Red Output with Horizontal Sync                                      |

\_MAX9539 Pin Description

| PIN                         | NAME            | FUNCTION                                                             |

|-----------------------------|-----------------|----------------------------------------------------------------------|

| 1                           | IN_R            | Red Video Input with Horizontal Sync                                 |

| 2, 7, 12                    | GND             | Ground                                                               |

| 3                           | REST_R          | Red DC Restore. Connect a 1nF capacitor from REST_R to GND.          |

| 4, 9, 10, 14,<br>15, 20, 25 | N.C.            | No Connection. Not internally connected.                             |

| 5                           | I.C.            | Internally Connected. For best performance, connect this pin to GND. |

| 6                           | IN_G            | Green Video Input with Composite Sync                                |

| 8                           | REST_G          | Green DC Restore. Connect a 1nF capacitor from REST_G to GND.        |

| 11                          | IN_B            | Blue Video Input with Vertical Sync                                  |

| 13                          | REST_B          | Blue DC Restore. Connect a 1nF capacitor from REST_B to GND.         |

| 16                          | VSYNC           | Vertical Sync Output                                                 |

| 17                          | SP_V            | Vertical Sync Polarity Input                                         |

| 18                          | OUT_B           | Blue Video Output                                                    |

| 19                          | VEE             | Negative Power-Supply Input. Bypass with a 0.1µF capacitor to GND.   |

| 21                          | CSYNC           | Composite Sync Output                                                |

| 22                          | SP_C            | Composite Sync Polarity Input                                        |

| 23                          | OUT_G           | Green Video Output                                                   |

| 24                          | V <sub>CC</sub> | Positive Power-Supply Input. Bypass with a 0.1µF capacitor to GND.   |

| 26                          | HSYNC           | Horizontal Sync Output                                               |

| 27                          | SP_H            | Horizontal Sync Polarity Input                                       |

| 28                          | OUT_R           | Red Video Output                                                     |

### \_Detailed Description

The MAX9539/MAX9540 chipset provides a 3-wire (RGB) interface for 5-wire (RGBHV) video by adding and extracting the H, V, and composite sync from the graphics video signals. This chipset eliminates the problem of sync-to-video timing (skew errors) in a 5-wire interface, while reducing the number of channels required when transporting video signals.

The MAX9539 mixes the H and V sync signals and adds them to create a 3-wire interface from a 5-wire (RGBHV) input. The MAX9540 recovers the H and V sync signals to create a 5-wire (RGBHV) interface from the 3-wire input. The MAX9540 also provides a composite sync output.

The chipset includes the MAX9539 sync adder and the MAX9540 sync extractor with 180MHz large-signal bandwidths to address display resolutions up to 1600 x 1200 at 85Hz for VGA-to-UXGA applications. Both devices feature a DC-restore function, which virtually eliminates any changes in black level. The chipset uses a proprietary H and V sync addition/extraction scheme (true sync) to minimize skew errors.

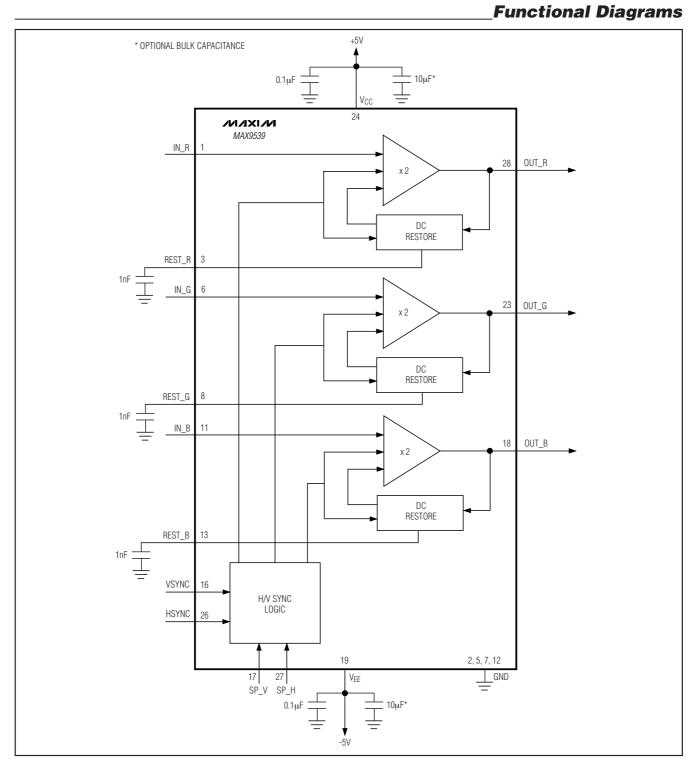

#### MAX9539 Sync Adder

MAX9540 Pin Description

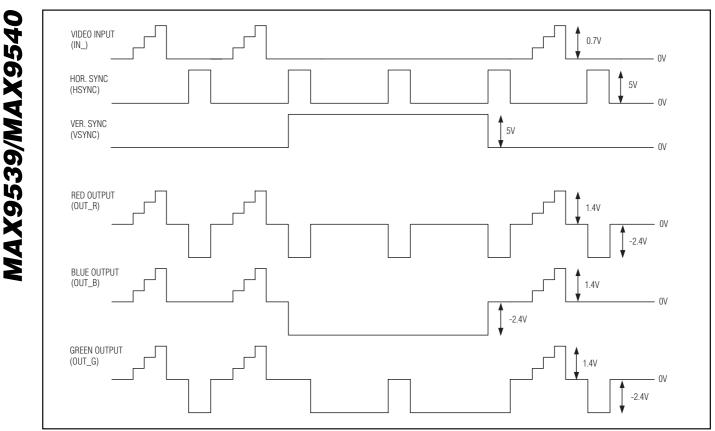

The MAX9539 mixes the H and V sync signals and adds them to create a 3-wire interface from a 5-wire (RGBHV) input. Sync signals are added to the input video signals. Horizontal sync is added to red video, vertical sync is added to blue video, and composite sync is added to green video. Composite sync is the XOR function between H sync and V sync and is internally generated by the MAX9539. The sync level of the video outputs is -2.4V. The DC-restore function removes any DC offset ( $\Delta V_{IN\_RESTORE}$ ) in the RGB video inputs and sets the output black level to 0V at the back porch of the H sync. Therefore, the output black level is set to 0V at the beginning of every line.

Figure 2 illustrates the functionality of the MAX9539. In this example, the sync signals are of positive polarity.

#### MAX9540 Sync Extractor

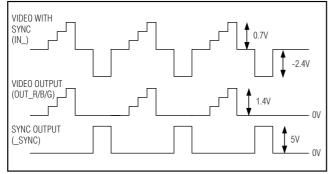

The MAX9540 recovers the H and V sync signals to create a 5-wire (RGBHV) interface from the 3-wire input. The output video signals are obtained by removing the sync pulses of the input video. The sync outputs correspond to the sync pulses of the input video: horizontal sync is

VIDEO

SYNC

obtained from the red input, vertical sync is obtained from the blue input, and composite sync is obtained from the green input. Like the MAX9539, the DC-restore function removes any DC offset in the RGB video inputs and sets the output black levels to OV. This happens at the back porch (trailing edge) of the sync pulse.

Figure 3 illustrates the functionality of the MAX9540. In this example, the sync signals are of positive polarity.

#### **DC** Restore

The MAX9539/MAX9540 DC-restore function removes the input signal DC level and restores 0V for the black level of the output video signal. 1nF restore capacitors are needed for the sample-and-hold circuitry at REST\_R, REST\_G, and REST\_B. A value less than 0.5nF can cause AC instability in the sample-and-hold circuitry. A value higher than 2nF increases the settling time of the sample-and-hold circuitry, shifting the output black level from 0V.

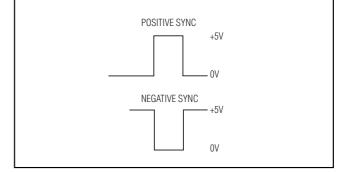

Sync Polarity Sync polarity refers to the idle state and pulse amplitude of the sync pulse. A sync pulse that idles low and pulses high is referred to as a positive sync pulse. A sync pulse that idles high and pulses low is referred to as a negative sync pulse as seen in Figure 4. To accommodate positive and negative sync input signals, the MAX9539/MAX9540 have vertical and horizontal sync polarity inputs (SP\_V and SP\_H). Drive SP\_V or SP\_H high for positive sync polarity. Drive SP\_V or SP\_H low for negative sync polarity. The MAX9540 also has a composite polarity input (SP\_C). Drive SP\_C high for positive sync polarity or drive SP\_C low for negative sync polarity (Table 1).

#### Layout and Power-Supply Bypassing

The MAX9539/MAX9540 have an extremely high bandwidth and require careful board layout. For best performance use constant-impedance microstrip or stripline techniques.

To realize the full AC performance of these high-speed amplifiers, pay careful attention to power-supply bypassing and board layout. The PC board should have at least two layers: a signal and power layer on one side, and a large, low-impedance ground plane on the other side. The ground plane should be as free of voids as possible. With multilayer boards, locate the ground plane on a layer that incorporates no signal or power traces.

Observe the following guidelines when designing the board regardless of whether or not a constant-impedance board is used.

1) Do not use wire-wrap boards or breadboards.

IAX9539/MAX9540

Figure 1. Sync Timing Delay  $(t_D) = t1 - t2$

### Table 1. Sync Polarity Table

| INPUT LOGIC<br>VALUE | SP_V     | SP_H     | SP_C<br>(MAX9540) |

|----------------------|----------|----------|-------------------|

| 1                    | Positive | Positive | Positive          |

|                      | sync     | sync     | sync              |

| 0                    | Negative | Negative | Negative          |

|                      | sync     | sync     | sync              |

- 2) Do not use IC sockets; they increase parasitic capacitance and inductance.

- Keep lines as short and as straight as possible. Do 3) not make 90° turns; round all corners.

- Observe high-frequency bypassing techniques to 4) maintain the amplifier's accuracy and stability.

- Use surface-mount components. They generally 5) have shorter bodies and lower parasitic reactance, yielding better high-frequency performance than through-hole components.

Figure 2. MAX9539 Input and Output Functionality

Figure 3. MAX9540 Input and Output Functionality

The bypass capacitors should include a  $0.1\mu$ F ceramic surface-mount capacitor between each supply pin and the ground plane, located as close to the package as possible. Optionally, place a  $10\mu$ F tantalum capacitor at the power-supply pins' points of entry to the PC board to ensure the integrity of incoming supplies. The power-supply trace should lead directly from the tanta-

Figure 4. Sync Pulse Polarity

lum capacitor to the  $V_{CC}$  and  $V_{EE}$  pins. To minimize parasitic inductance, keep PC traces short and use surface-mount components.

Use surface-mount resistors for input termination and output back termination. Place the termination resistors as close to the IC as possible.

MAX9539/MAX9540

### Chip Information

PROCESS: Bipolar

\_\_\_\_\_

M/IXI/M

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

### **Revision History**

Pages changed at Rev 2: 1, 2, 4, 15

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.