# HTG13J0/HTG13B0 4-bit Microcontroller

#### **Hardware Features**

- Operating voltage: 2.4V~3.3V

- 8 input lines

- 3 output lines

- RC oscillator for system clock

- 8K×8 program ROM

- 160×4 data RAM

- 40×8 segment LCD driver, 1/5 bias, 1/8 duty

- 5 working registers

- 8-bit programmable timer with built-in frequency source

- Internal timer overflow interrupt

- 16 kinds of programmable sound effect

- Halt function and wake up reduces power consumption

- 96 powerful instructions

- Up to  $4.0\mu$  sec instruction cycle (1.0MHz system clock), at  $V_{DD}$ =3V

- · One-level subroutine nesting

- 8-bit table read instruction

- Halt instruction

1

## **General Description**

The HTG13J0/HTG13B0 are two processors from HOLTEK's 4-bit stand alone single chip microcontroller specially designed for the application of LCD display products. These two devices are similar in most ways apart from chip size and some electronic characteristics.

They are especially suited for applications requiring low power consumption system with many LCD segments, such as calculator, scale, subsystem controller, hand-held LCD products and electronic appliances.

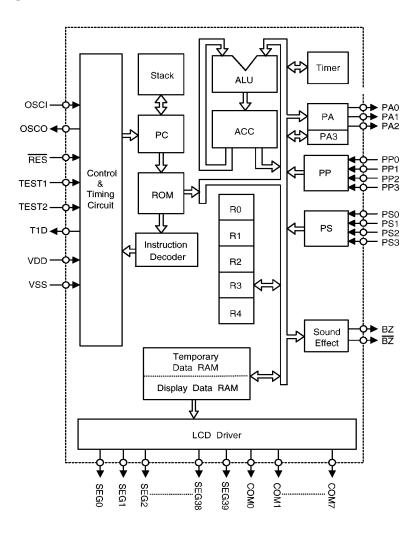

# **Block Diagram**

2

Note:

ACC: Accumulator

PC: Program Counter

R0~R4: Working Register

PA0~PA2: Output Port

PP, PS: Input Ports

PA3: ROM bank switch

# **Pad Description**

| Pad No.             | Pad name                      | I/O         | Mask Option                   | Function                                                                                                                        |

|---------------------|-------------------------------|-------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1 2                 | $\frac{BZ}{BZ}$               | 0           | *                             | Sound effect output                                                                                                             |

| 3                   | VDD                           | Ι           | _                             | Positive power supply                                                                                                           |

| 4<br>5              | OSCI<br>OSCO                  | I<br>O      | _                             | OSCI, OSCO are connected to resistor for internal system clock.                                                                 |

| 6<br>15<br>16<br>21 | T512<br>TEST1<br>TEST2<br>T1D | O<br>I<br>O | _                             | For test mode only TEST1 and TEST2 must let it open when the chip is in normal operation (with an internal pull high resistor). |

| 7~14                | COM7~COM0                     | О           | _                             | Output for LCD panel common plate                                                                                               |

| 17~19<br>22         | PS2~PS0<br>PS3                | I           | Pull-High or<br>None<br>**    | 4-bit port for input only                                                                                                       |

| 20                  | VSS                           | I           | _                             | Negative power supply, GND.                                                                                                     |

| 23~25               | PA2~PA0                       | О           | CMOS or<br>NMOS<br>Open Drain | 3-bit latch port for output only                                                                                                |

| 26~29               | PP0~PP3                       | I           | Pull-High or<br>None<br>**    | 4-bit port for input only                                                                                                       |

| 30                  | RES                           | I           | _                             | Input for reset LSI inside.<br>Reset is active at logical low level.                                                            |

| 31~70               | SEG39~SEG0                    | 0           | _                             | LCD driver outputs for LCD panel segment                                                                                        |

<sup>\*: 6</sup> internal sources deriving from system clock can be selected as sound effect clock by mask option. If HOLTEK's sound library is invoked, only 128K and 64K is accepted.

<sup>\*\*:</sup> Each bit of input ports PS, PP can be a trigger source of HALT interrupt. That can be specified by mask option.

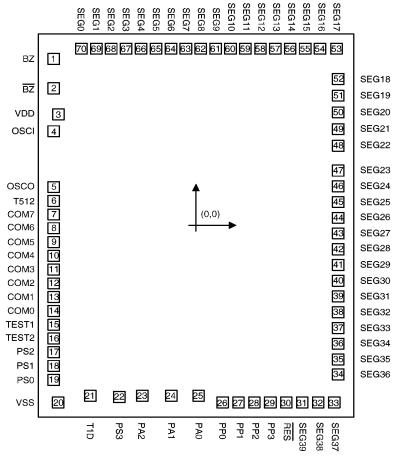

### **Pad Position**

#### HTG13J0

Chip size:  $2746 \times 3552 \, (\mu m)^2$

Note: The IC substrate should be connected to VSS in PCB layout artwork.

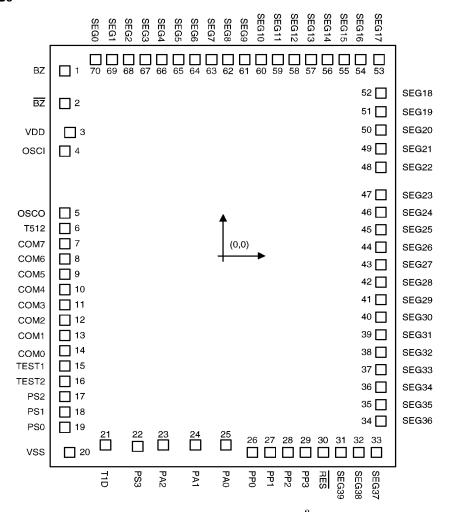

**HTG13B0**

Chip size:  $3020\times3970~(\mu m)^2$

Note: The IC substrate should be connected to VSS in PCB layout artwork.

# **Pad Coordinates**

HTG13J0 Unit: μm

| Pad No.  | X        | Y        | Pad No. | X        | $\mathbf{Y}$ |

|----------|----------|----------|---------|----------|--------------|

| 1        | -1244.25 | 1523.47  | 36      | 1244.25  | -1080.67     |

| 2        | -1244.25 | 1256.62  | 37      | 1244.25  | -936.67      |

| 3        | -1203.75 | 1017.25  | 38      | 1244.25  | -792.67      |

| 4        | -1244.25 | 861.97   | 39      | 1244.25  | -648.67      |

| 5        | -1244.25 | 353.02   | 40      | 1244.25  | -504.67      |

| 6        | -1244.25 | 227.02   | 41      | 1244.25  | -360.67      |

| 7        | -1244.25 | 101.03   | 42      | 1244.25  | -216.68      |

| 8        | -1244.25 | -24.98   | 43      | 1244.25  | -72.68       |

| 9        | -1244.25 | -150.98  | 44      | 1244.25  | 71.32        |

| 10       | -1244.25 | -276.98  | 45      | 1244.25  | 215.32       |

| 11       | -1244.25 | -402.98  | 46      | 1244.25  | 359.33       |

| 12       | -1244.25 | -528.97  | 47      | 1244.25  | 503.33       |

| 13       | -1244.25 | -654.97  | 48      | 1244.25  | 729.22       |

| 14       | -1244.25 | -780.97  | 49      | 1244.25  | 882.22       |

| 15       | -1244.25 | -906.97  | 50      | 1244.25  | 1035.22      |

| 16       | -1244.25 | -1032.97 | 51      | 1244.25  | 1188.22      |

| 17       | -1244.25 | -1158.97 | 52      | 1244.25  | 1341.22      |

| 18       | -1244.25 | -1284.97 | 53      | 1228.95  | 1617.53      |

| 19       | -1244.25 | -1410.97 | 54      | 1084.95  | 1617.53      |

| 20       | -1206.45 | -1617.53 | 55      | 954.45   | 1617.53      |

| 21       | -923.85  | -1556.78 | 56      | 823.95   | 1617.53      |

| 22       | -671.40  | -1568.47 | 57      | 693.45   | 1617.53      |

| 23       | -469.35  | -1556.78 | 58      | 562.95   | 1617.53      |

| $\bf 24$ | -217.35  | -1556.78 | 59      | 432.45   | 1617.53      |

| 25       | 22.95    | -1556.78 | 60      | 301.95   | 1617.53      |

| 26       | 232.20   | -1617.53 | 61      | 171.45   | 1617.53      |

| 27       | 371.70   | -1617.53 | 62      | 40.95    | 1617.53      |

| 28       | 511.20   | -1617.53 | 63      | -89.55   | 1617.53      |

| 29       | 650.70   | -1617.53 | 64      | -220.05  | 1617.53      |

| 30       | 790.20   | -1617.53 | 65      | -350.55  | 1617.53      |

| 31       | 929.70   | -1617.53 | 66      | -481.05  | 1617.53      |

| 32       | 1069.20  | -1617.53 | 67      | -611.55  | 1617.53      |

| 33       | 1208.70  | -1617.53 | 68      | -742.05  | 1617.53      |

| 34       | 1244.25  | -1361.03 | 69      | -872.55  | 1617.53      |

| 35       | 1244.25  | -1224.67 | 70      | -1003.05 | 1617.53      |

HTG13B0 Unit:  $\mu m$

|         |          |          |         |          | Unit: μn |

|---------|----------|----------|---------|----------|----------|

| Pad No. | X        | Y        | Pad No. | X        | Y        |

| 1       | -1382.50 | 1692.75  | 36      | 1382.50  | -1200.75 |

| 2       | -1382.50 | 1396.25  | 37      | 1382.50  | -1040.75 |

| 3       | -1337.50 | 1130.25  | 38      | 1382.50  | -880.75  |

| 4       | -1382.50 | 957.75   | 39      | 1382.50  | -720.75  |

| 5       | -1382.50 | 392.25   | 40      | 1382.50  | -560.75  |

| 6       | -1382.50 | 252.25   | 41      | 1382.50  | -400.75  |

| 7       | -1382.50 | 112.25   | 42      | 1382.50  | -240.75  |

| 8       | -1382.50 | -27.75   | 43      | 1382.50  | -80.75   |

| 9       | -1382.50 | -167.75  | 44      | 1382.50  | 79.25    |

| 10      | -1382.50 | -307.75  | 45      | 1382.50  | 239.25   |

| 11      | -1382.50 | -447.75  | 46      | 1382.50  | 399.25   |

| 12      | -1382.50 | -587.75  | 47      | 1382.50  | 559.25   |

| 13      | -1382.50 | -727.75  | 48      | 1382.50  | 810.25   |

| 14      | -1382.50 | -867.75  | 49      | 1382.50  | 980.25   |

| 15      | -1382.50 | -1007.75 | 50      | 1382.50  | 1150.25  |

| 16      | -1382.50 | -1147.75 | 51      | 1382.50  | 1320.25  |

| 17      | -1382.50 | -1287.75 | 52      | 1382.50  | 1490.25  |

| 18      | -1382.50 | -1427.75 | 53      | 1365.50  | 1797.25  |

| 19      | -1382.50 | -1567.75 | 54      | 1205.50  | 1797.25  |

| 20      | -1340.50 | -1797.25 | 55      | 1060.50  | 1797.25  |

| 21      | -1026.50 | -1729.75 | 56      | 915.50   | 1797.25  |

| 22      | -746.00  | -1742.75 | 57      | 770.50   | 1797.25  |

| 23      | -521.50  | -1729.75 | 58      | 625.50   | 1797.25  |

| 24      | -241.50  | -1729.75 | 59      | 480.50   | 1797.25  |

| 25      | 25.50    | -1729.75 | 60      | 335.50   | 1797.25  |

| 26      | 258.00   | -1797.25 | 61      | 190.50   | 1797.25  |

| 27      | 413.00   | -1797.25 | 62      | 45.50    | 1797.25  |

| 28      | 568.00   | -1797.25 | 63      | -99.50   | 1797.25  |

| 29      | 723.00   | -1797.25 | 64      | -244.50  | 1797.25  |

| 30      | 878.00   | -1797.25 | 65      | -389.50  | 1797.25  |

| 31      | 1033.00  | -1797.25 | 66      | -534.50  | 1797.25  |

| 32      | 1188.00  | -1797.25 | 67      | -679.50  | 1797.25  |

| 33      | 1343.00  | -1797.25 | 68      | -824.50  | 1797.25  |

| 34      | 1382.50  | -1512.25 | 69      | -969.50  | 1797.25  |

| 35      | 1382.50  | -1360.75 | 70      | -1114.50 | 1797.25  |

# **Absolute Maximum Ratings\***

| Supply Voltage0.3V to 5.5V        | Storage Temperature $-50^{\circ}\mathrm{C}$ to $125^{\circ}\mathrm{C}$ |

|-----------------------------------|------------------------------------------------------------------------|

| Input VoltageVss-0.3V to Vpp+0.3V | Operating Temperature                                                  |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **D.C. Characteristics**

HTG13J0 (Ta=25°C)

| g 1.1              | D (                                                           |                 | Test Conditions                                | 3.51 | /m   | 24   | T    |  |

|--------------------|---------------------------------------------------------------|-----------------|------------------------------------------------|------|------|------|------|--|

| Symbol             | Parameter                                                     | V <sub>DD</sub> | Conditions                                     | Min. | Тур. | Max. | Uint |  |

| $V_{ m DD}$        | Operating Voltage                                             | _               | _                                              | 2.4  | _    | 3.3  | V    |  |

| ${ m I}_{ m DD}$   | Operating Current                                             | 3V              | No load, f <sub>SYS</sub> =500kHz              | _    | 200  | 500  | μА   |  |

| $I_{STB}$          | Standby Current                                               | 3V              | System halt                                    | _    | _    | 1    | μА   |  |

| $v_{\mathrm{IL1}}$ | Input Low Voltage PS, PP                                      | 3V              | _                                              | 0    | _    | 0.6  | v    |  |

| $V_{\mathrm{IH1}}$ | Input High Voltage PS, PP                                     | 3V              | _                                              | 2.1  | _    | 3.0  | v    |  |

| $V_{\rm IL2}$      | Input Low Voltage RES                                         | 3V              | _                                              | 0    | _    | 0.6  | V    |  |

| $V_{\mathrm{IH2}}$ | Input High Voltage RES                                        | 3V              | _                                              | 2.6  | _    | 3.0  | v    |  |

| $I_{\mathrm{OL1}}$ | Port A & BZ & BZ Output Sink Current                          | 3V              | V <sub>DD</sub> =3V, V <sub>OL</sub> =0.3V     | 1.5  | 3.0  | _    | mA   |  |

| $I_{ m OH1}$       | Port A & BZ & $\overline{\text{BZ}}$<br>Output Source Current | 3V              | $V_{\mathrm{DD}}$ =3V, $V_{\mathrm{OH}}$ =2.7V | -0.8 | -1.5 | _    | mA   |  |

| $I_{ m OL2}$       | Segment 0~7 Output<br>Sink Current                            | 3V              | $V_{ m LCD}$ =3V, $V_{ m OL}$ =0.3V            | 80   | 130  | _    | μА   |  |

| $ m I_{OH2}$       | Segment 0~7 Output<br>Source Current                          | 3V              | $V_{ m LCD}$ =3V, $V_{ m OH}$ =2.7V            | -50  | -90  | _    | μА   |  |

| $I_{OL3}$          | Segment 8~39 Output<br>Sink Current                           | 3V              | $V_{ m LCD}$ =3V, $V_{ m OL}$ =0.3V            | 40   | 80   | _    | μА   |  |

| $I_{ m OH3}$       | Segment 8~39 Output<br>Source Current                         | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V    | -30  | -60  | _    | μА   |  |

| I <sub>OL4</sub>   | Common Sink Current                                           | 3V              | $V_{\rm LCD}$ =3V, $V_{\rm OL}$ =0.3V          | 60   | 120  | _    | μА   |  |

| $I_{\mathrm{OH4}}$ | Common Source Current                                         | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V    | -60  | -120 | _    | μА   |  |

| $R_{\mathrm{PH}}$  | Pull-high resistance                                          | 3V              | $PS, PP, \overline{RES}$                       | 50   | _    | 300  | kΩ   |  |

8

29th Apr '98

HTG13B0 (Ta=25°C)

| Symbol             | nbol Parameter                         |                 | <b>Test Conditions</b>                      | Min.   | T    | Max. | Uint |  |

|--------------------|----------------------------------------|-----------------|---------------------------------------------|--------|------|------|------|--|

| Symbol             | Parameter                              | V <sub>DD</sub> | Conditions                                  | WIIII. | Тур. | wax. |      |  |

| $V_{\mathrm{DD}}$  | Operating Voltage                      | _               | _                                           | 2.4    | _    | 3.3  | V    |  |

| $I_{\mathrm{DD}}$  | Operating Current                      | 3V              | No load, fsys=500kHz                        | _      | 300  | 500  | μА   |  |

| $I_{STB}$          | Standby Current                        | 3V              | System halt                                 | _      |      | 1    | μΑ   |  |

| $V_{\rm IL1}$      | Input Low Voltage PS, PP               | 3V              | _                                           | 0      | _    | 0.6  | v    |  |

| $v_{\rm IH1}$      | Input High Voltage PS, PP              | 3V              | _                                           | 2.1    |      | 3.0  | v    |  |

| $V_{\rm IL2}$      | Input Low Voltage RES                  | 3V              | _                                           | 0      | _    | 0.6  | v    |  |

| $V_{\rm IH2}$      | Input High Voltage RES                 | 3V              | _                                           | 2.6    | _    | 3.0  | v    |  |

| $I_{OL1}$          | Port A & BZ & BZ Output Sink Current   | 3V              | V <sub>DD</sub> =3V, V <sub>OL</sub> =0.3V  | 1.5    | 3.0  | _    | mA   |  |

| $I_{OH1}$          | Port A & BZ & BZ Output Source Current | 3V              | V <sub>DD</sub> =3V, V <sub>OH</sub> =2.7V  | -0.8   | -1.5 | _    | mA   |  |

| $I_{OL2}$          | Segment 0~7 Output<br>Sink Current     | 3V              | V <sub>LCD</sub> =3V, V <sub>OL</sub> =0.3V | 80     | 130  | _    | μА   |  |

| $ m I_{OH2}$       | Segment 0~7 Output<br>Source Current   | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V | -50    | -90  | _    | μА   |  |

| $I_{OL3}$          | Segment 8~39 Output<br>Sink Current    | 3V              | V <sub>LCD</sub> =3V, V <sub>OL</sub> =0.3V | 40     | 80   | _    | μА   |  |

| Іонз               | Segment 8~39 Output<br>Source Current  | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V | -30    | -60  | _    | μА   |  |

| $I_{\rm OL4}$      | Common Sink Current                    | 3V              | V <sub>LCD</sub> =3V, V <sub>OL</sub> =0.3V | 60     | 120  | _    | μA   |  |

| $I_{\mathrm{OH4}}$ | Common Source Current                  | 3V              | V <sub>LCD</sub> =3V, V <sub>OH</sub> =2.7V | -60    | -120 | _    | μA   |  |

| $R_{\mathrm{PH}}$  | Pull-high resistance                   | 3V              | $PS, PP, \overline{RES}$                    | 50     | _    | 300  | kΩ   |  |

9

### A.C. Characteristics

HTG13J0 (Ta=25°C)

| Symbol                      | Parameter          | Tes             | t Conditions             | Min.    | Т                       | Max. | Unit       |

|-----------------------------|--------------------|-----------------|--------------------------|---------|-------------------------|------|------------|

| Symbol                      | Farameter          | V <sub>DD</sub> | Conditions               | 141111. | Тур.                    | Max. | Ont        |

| $f_{ m SYS}$                | System Clock       | 3V              | R:680k~5kΩ               | 32      |                         | 1000 | kHz        |

| $\mathbf{f}_{\mathrm{LCD}}$ | LCD Clock          | 3V              | _                        | _       | 512*                    |      | $_{ m Hz}$ |

| $t_{\rm COM}$               | LCD Common Period  | _               | 1/8 duty                 | _       | (1/f <sub>LCD</sub> )×8 | _    | Sec        |

| $\mathbf{t}_{\mathrm{CY}}$  | Cycle Time         | _               | f <sub>SYS</sub> =1.0MHz | _       | 4.0                     | _    | μs         |

| $\mathbf{t}_{\mathrm{RES}}$ | Reset Pulse Width  | _               | _                        | 5       | _                       | _    | ms         |

| f <sub>SOUND</sub>          | Sound Effect Clock | _               | _                        | _       | 64 or 128<br>**         | _    | kHz        |

<sup>\*:</sup> In general,,  $f_{\rm LCD}$  is selected and optimized by HOLTEK according to  $f_{\rm SYS}$  and operating voltage.

HTG13B0 (Ta=25°C)

| Symbol                      | Parameter          | Tes             | st Condition             | Min.   | Tem                     | Max. | Unit |

|-----------------------------|--------------------|-----------------|--------------------------|--------|-------------------------|------|------|

| Symbol                      | Farameter          | V <sub>DD</sub> | Condition                | WIIII. | Тур.                    | wax. | Onit |

| $f_{\mathrm{SYS}}$          | System Clock       | 3V              | R:680k~12kΩ              | 32     |                         | 1000 | kHz  |

| $\mathbf{f}_{\mathrm{LCD}}$ | LCD Clock          | 3V              | _                        | _      | 512*                    | _    | Hz   |

| tcom                        | LCD Common Period  | _               | 1/8 duty                 | _      | (1/f <sub>LCD</sub> )×8 | _    | Sec  |

| $\mathbf{t}_{\mathrm{CY}}$  | Cycle Time         | _               | f <sub>SYS</sub> =1.0MHz | _      | 4.0                     | _    | μs   |

| $t_{ m RES}$                | Reset Pulse Width  |                 | _                        | 5      | _                       | _    | ms   |

| fsound                      | Sound Effect Clock |                 | _                        | _      | 64 or 128<br>**         | _    | kHz  |

<sup>\*:</sup> In general,,  $f_{\rm LCD}$  is selected and optimized by HOLTEK according to  $f_{\rm SYS}$  and operating voltage.

10

$29 {

m th} \ {

m Apr} \ {

m '}98$

<sup>\*\*:</sup> Only these two frequency of clock signal is supported by HOLTEK sound library.

<sup>\*\*</sup>: Only these two frequency of clock signal is supported by HOLTEK sound library.

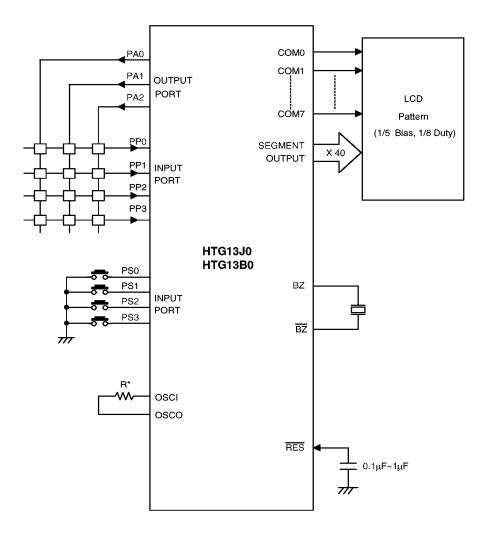

# **Application Circuit**

$R^*$ : depends on the required frequency of system clock. (R=680k~5k $\Omega$ , at  $V_{DD}$ =3V)

### System Architecture

#### Program counter - PC

The bit 13 of program memory is controlled by PA3 which can change the address of the program. There are two banks of program memory, which are selected by PA3, every bank is 4KB ROM. The instruction "OUT PA,A" is used to change the value of PA3. Then, low or high 4K ROM is selected accordingly. All instructions are not effective on crossing bank, unless the value of PA3 is changed in advance.

The 12-bit program counter (PC) controls the sequence in which the instructions stored in program ROM are executed and its contents specify maximum 4096 address.

After accessing a memory word to fetch an instruction code, the contents of the program counter are incremented by one or two, then the program counter will point to the memory word containing the next instruction code.

When executing the jump instruction (JMP, JNZ, JC, JTMR...), subroutine call, internal interrupt, external interrupt or return from subroutine, the PC manipulates the program transfer by loading the address corresponding to each instruction.

| Mode                   |     | Program Counter |      |     |     |     |     |     |     |     |     |     |     |  |  |

|------------------------|-----|-----------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|--|

| Mode                   | PA3 | PC11            | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |  |  |

| Initial<br>reset       | 1   | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| Internal<br>interrupt  | PA3 | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |  |  |

| External interrupt     | PA3 | 0               | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   |  |  |

| Jump, call instruction | PA3 | PC11            | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |  |  |

| Conditional<br>branch  | PA3 | @               | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |  |  |

| Return from subroutine | PA3 | S11             | S10  | S9  | S8  | S7  | S6  | S5  | S4  | S3  | S2  | S1  | S0  |  |  |

12

#### Notes:

PC11~PC0 : Bits of Instruction Code.

© PC11 Keeps Current Value.

S11~S0 : Bits of Stack Register.

PA3 : Bits of Bank Value.

#### **Program memory - ROM**

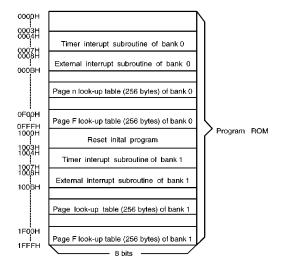

The program memory is used to store program instruction which is to be executed. It is organized with  $8192 \times 8$  bits and addressed by the program counter and PA3.

Certain locations in bank 0 of program memory are reserved for specific usage:

#### • Location 0004H

This area are reserved for TIMER interrupt service program. A timer interrupt resulting from TIMER overflow, if interrupt is enabled, the CPU begins execution at location 0004H.

# • Location 0008H

Activating the PS or PP input pins of the processor with the interrupts enabled during HALT mode causes the program to jump to this location.

Location 0n00H~0nFFH (n=current number) and 0F00H~0FFFH.

The last 256 bytes of each page in program memory, addressed from 0n00H to 0nFFH and 0F00H to 0FFFH can be used as a look—up table. The instructions READ R4A, READ MR0A, READF R4A, READF MR0A can read the table and transfer the contents of the table to ACC and R4 or transfer to ACC and data memory addressed by register pair "R1,R0". These area may function as normal program memory depending on user's requirement. Note that the page number n must be greater than zero, some locations in page 0 are reserved for specific usage as mentioned.

Certain locations in bank 1 of program memory are reserved for specific usage:

#### • Location 1000H

This area are reserved for the initialization program. After reset, the CPU always begins execution at location 1000H.

#### Location 1004H

This area are reserved for TIMER interrupt service program. A timer interrupt resulting from TIMER overflow, if interrupt is enabled, the CPU begins execution at location 1004H.

#### • Location 1008H

Activating the PS or PP input pins of the processor with the interrupts enabled during HALT mode causes the program to jump to this location

• Location 1n00H~1nFFH (n=current number) and 1F00H~1FFFH.

The last 256 bytes of each page in program memory, addressed from 1n00H to 1nFFH and 1F00H to 1FFFH can be used as a loop-up table. The instructions READ R4A, READ MR0A, READF R4A, READF MR0A can read the table and transfer the contents of the table to ACC and R4 or transfer to ACC and data memory addressed by register pair "R1,R0". These area may function as normal program memory depending on user's requirement. Note that the page number n must be greater than zero, some locations in page 1 are reserved for specific use as mentioned.

The program memory (ROM) mapping is shown below:

Program memory

In the execution of an instruction, the program counter is added before the executing phase. So a careful manipulation of READ MR0A and READ R4A is needed in the page margin.

#### Stack register

The stack register is a group of registers used to save the contents of the program counter (PC) and is arranged in 13 bits×1 level. One bit is used to store the carry flag. An interrupt will force the contents of the PC and the carry flag onto the stack register. A subroutine call will also cause the PC contents to be pushed onto the stack; however the carry flag will not be stored. At the end of a subroutine or an interrupt (indicated by a return instruction RET or RETI), the contents of the stack register are returned to the PC.

Executing "RETI" instruction will restore the carry flag from stack register, but "RET" does't.

#### Working registers – R0,R1,R2,R3,R4

These five registers are usually used to store the frequently accessed data. The working register can be incremented (+1) or decremented (-1). The JNZ Rn,address (n=0,1,4) instruction makes very efficient use of the working register as program loop counter. Also the register pairs of R1, R0 and R3, R2 can be used as the data memory pointer, when the data memory transfer instruction is executed.

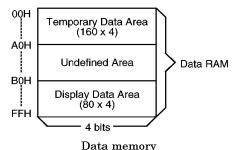

#### Data memory - RAM

The data memory is a static RAM organized with  $256 \times 4$  bit format and is used to store temporary data & display data. All of the data memory locations are indirectly addressable through the register pair "R1,R0" or "R3,R2".

There are two areas in the data memory, temporary data area and display data area. Access to temporary data memory is done 00H–9FH address, and access to display data memory is done in B0H–FFH address.

The locations between the temporary and display data areas are undefined and cannot be used.

When data is written in the display area, the LCD driver automatically reads it and generates an LCD driving signal.

#### Accumulator - ACC

The register ACC plays the most important role in data manipulation and data transfer. It is not only one of the sources of input to the ALU but also the destination of the result due to ALU. Data transfer can be performed between ACC and other registers, data memory or I/O ports.

#### Arithmetic and logic unit - ALU

This circuit performs arithmetic and logic operation. The ALU provides the following functions:

Arithmetic operation (ADD, ADC, SUB, SBC, DAA)

- Logic operation (AND, OR, XOR)

- Rotation (RL, RR, RLC, RRC)

- Increment & Decrement (INC, DEC)

- Branch decision (JZ, JNZ, JC, JNC...)

- The ALU not only outputs the results of data operation but also sets the status of carry flag (C) in some instructions.

#### Timer

This is a programmable 8—bit count-up counter internal frequency sources to aid the user in counting and generate accurate time base.

The Timer is presettable and readable with software instructions. "TIMER XXH", "MOV TMRL,A" and "MOV TMRH,A" preload TIMER value. "MOV A,TMRL" and "MOV A,TMRH" read the contents of TIMER to ACC.

The Timer is stopped by a hardware reset or "TIMER OFF" instruction and started by a TIMER ON instruction.

Once the Timer is started, it will increment to its maximum count (FFH) and overflow to zero (00H) and will not stop until a "TIMER OFF" instruction or reset. When the overflow occurs, it will set the Timer Flag (TF) simultaneously. If interrupt is enabled, the Timer circuit supports TF for internal interrupt. The state of the TF is also testable with conditional instruction JTMR.

The Timer flag is cleared after the interrupt or JTMR instruction is executed.

The frequency of internal frequency source can be selected by mask option.

Frequency of TIMER clock =

$$\frac{system\ clock}{2^n}$$

Where n=0,1,2.....13 except 6, by mask option (the sixth stage is reserved for internal use).

#### Interrupt

The HTG13J0/HTG13B0 provide both internal and external interrupt modes. The DI and EI instructions are used to disable and enable the interrupts. During halt mode, if the PP or PS input pin is triggered on a high to low transition in the enable interrupt mode and the program is not within a CALL subroutine, the external interrupt is activated. This causes a subroutine call to location 8 and resets the interrupt latch.

Likewise when the timer flag is set in the enable interrupt mode and the program is not within a CALL subroutine, the internal interrupt is activated. This causes a subroutine call to location 4 and resets the timer flag.

When running under a CALL subroutine or DI the inerrupt acknowledge is on hold until the RET or EI instruction is invoked. The CALL instruction should not be used within an interrupt routine as unpredictable behaviours may

occur. If within a CALL subroutine interrupt occurs, the interrupt will be serviced after leaving the CALL subroutine.

The interrupts are disabled by a hardware reset or a DI instruction. They remain disabled until the EI instruction is executed.

Each input port pin can be programmed by mask option to have an external interrupt function in the HALT mode.

#### Initial reset

The HTG13J0/HTG13B0 provide a  $\overline{RES}$  pin for system initialization. Since the  $\overline{RES}$  pin has internal pull high resistor, only an external  $0.1\mu{\sim}1\mu$  capacitor is needed. If the reset pulse is generated externally, it must be held low for at least 5 ms.

When  $\overline{RES}$  is active, the internal block will be initialized as below:

| PA3 & PC            | 1000H                       |

|---------------------|-----------------------------|

| TIMER               | Stop                        |

| Timer flag          | Reset (low)                 |

| SOUND               | Sound off and One sing mode |

| Output Port A       | high (or floating state)    |

| Interrupt           | Disabled                    |

| BZ and BZ<br>output | High level                  |

#### Halt

This is a special feature of HTG13J0/HTG13B0. It will stop the chip's normal operation and reduce power consumption. When the instruction "HALT" is executed, then

- The system clock will be stopped

- The contents of the on-chip RAM and registers remain unchanged

- LCD segments and commons keep VDD voltage (i.e. LCD becomes blank)

The system can escape HALT mode by ways of initial reset or external interrupt and wake-up from the following entry of program counter value.

Initial reset: 1000H.

Interrupt (enabled): 1008H or 0008H.

Interrupt (disabled): next address of HALT instruction.

In HALT mode, each bit of port PP, PS, can be used as external interrupt by mask option to wake-up system. This signal is active in low-going transition.

#### Sound effect

HTG13J0/HTG13B0 provide sound effect circuit which offers up to 16 sounds with 3 effects of tone, boom and noise. HOLTEK supports a sound library which have melody, alarm, shooting of machine gun etc. That can meet user's requirement.

Whenever instruction "SOUND n" or "SOUND A" is executed, the specified sound begin playing. Whenever "SOUND OFF" is executed, it terminates the singing sound immediately.

There are two singing mode, SONE mode and SLOOP mode, this is activated by "SOUND ONE" and "SOUND LOOP". In SONE mode, the sound that has been specified plays just once. In SLOOP mode, the sound being specified keeps playing repeatedly.

Since sound  $0\sim11$  contain 32 notes, sound  $12\sim15$  contain 64 notes, the later possess better sound than the former.

The frequency of sound effect circuit can be selected by mask option.

Frequency of sound effect circuit =  $\frac{system\ clock}{2^m}$

Where m=0,1,2,3,4,5.

The HOLTEK'S sound library only supports sound clock frequency 128K or 64K. If user wants to utilize HOLTEK'S sound library, please select the proper system clock and mask option.

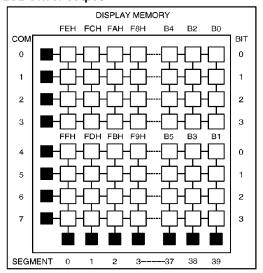

#### LCD display memory

As mentioned in the data memory section, the LCD display memory is embedded in data memory. It can be read and written as normal data memory.

The following figure shows the mapping between display memory and LCD pattern.

To turn on/off the display, the programmer just writes 1/0 to the corresponding bit of display memory.

The LCD display module may have any form as long as the number of the common is no more than 8 and the segment is no more than 40.

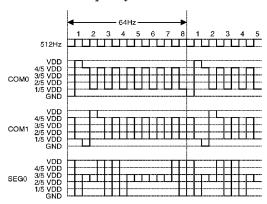

#### **LCD** driver output

LCD display memory

The output number of the LCD driver is  $40 \times 8$ . That can directly drive a LCD being 1/8 duty cycle and 1/5 bias. All LCD segments are random at the initial clear mode.

The bias voltage circuit of LCD display is builtin. No external resistor is needed.

The frequency of LCD driving clock shall be fixed in about 512Hz. That can not be selected by the user, and HOLTEK will set it according to the application.

An example of a LCD driving waveform (1/8 duty & 1/5 bias) is shown below.

#### Oscillator circuit

16

Only one external resistor is needed for HTG13J0/HTG13B0 oscillator circuit.

29th Apr '98

The system clock is also used as the reference signal of LCD driving clock, sound effect clock, and internal frequency source of TIMER.

One HTG13J0/HTG13B0 machine cycle consists of a sequence of 4 states numbered T1 to T4. Each state lasts for one oscillator period. The machine cycle is  $4\mu s$ , if the system frequency is up to 1.0MHz.

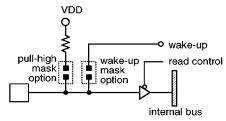

#### Input ports - PS, PP

All ports can have internal pull high resistors determined by mask option. Every bit of the input ports PP and PS can be specified to be a trigger source to wake up the HALT interrupt by mask option. A high to low transition on one of these pins will wake up the device from a HALT status.

Input ports – PS, PP

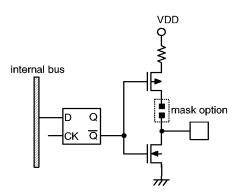

#### Output port - PA0~PA2

A mask option is available to select whether the output is a CMOS or open drain NMOS type. After an initial clear the output port PA defaults to be high for CMOS or floating for NMOS.

Output port - PA0~PA2

#### Note:

PA3 controls the bit 13 of program memory. It must be careful about PA3. When instruction "OUT PA,A" is operated, port A is changed as well.

#### Mask option

The following options are available by mask option which the user must select prior to manufacture.

- Each bit of input ports PS, PP with or without pull-high resistor

- Each bit of input ports PS, PP function as HALT interrupt trigger

- Each bit of output port PA0~PA2 with CMOS or open drain NMOS

- 8 bit programmable TIMER with internal frequency sources. There are 13 (The sixth stage is reserved for internal use) internal frequency sources which can be selected as clocking signal.

- Six kinds of sound clock frequency:  $f_{SYS}/2^m$ , m=0, 1, 2, 3, 4, 5

29th Apr '98

# **Instruction Set Summary**

| ADC A, R1R0   Subtract data memory with carry to ACC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | monic                                 | Byte Cycle                           | CF  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|-----|

| ADC A,[R1R0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | metic                                 |                                      |     |

| SUB A,[R1R0]         Subtract data memory from ACC         1         1         1           SBC A,[R1R0]         Subtract data memory from ACC with borrow         1         1         1           ADD A,XH         Add immediate data to ACC         2         2         2           DAA         Decimal adjust ACC for addition         1         1           Logic Operation         AND A,[R1R0]         AND data memory to ACC         1         1           AND A,[R1R0]         OR data memory to ACC         1         1         1           AND [R1R0],A         AND ACC to data memory to ACC         1         1         1           AND [R1R0],A         AND ACC to data memory         1         1         1           AND A,KH         AND immediate data to ACC         2         2         2           AND A,XH         AND immediate data to ACC         2         2         2           AND A,XH         OR immediate data to ACC         2         2         2           AND A,XH         OR immediate data to ACC         2         2         2           AND immediate data to ACC         2         2         2           AND immediate data to ACC         1         1         1           INC Ra, Incre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1R0] Ado                              | 1 1                                  | √   |

| SBC A,[R1R0]   Subtract data memory from ACC with borrow   ADD A,XH   Add immediate data to ACC   2   2   2   2   2   2   2   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .1R0]   Ado                           | 1 1                                  | √   |

| SBC A,[R1R0]   Subtract data memory from ACC with borrow   1   ADD A,XH   Add immediate data to ACC   2   2   2   2   2   2   2   2   2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1R0] Sub                              | 1 1                                  | √   |

| ADD A,XH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       | 1 1                                  | √   |

| SUB A,XH         Subtract immediate data from ACC         2         2         2           DAA         Decimal adjust ACC for addition         1         1           Logic Operation         AND data memory to ACC         1         1           AND A,[R1R0]         OR data memory to ACC         1         1           OR A,[R1R0]         Exclusive-OR data memory to ACC         1         1           AND [R1R0],A         AND ACC to data memory         1         1           OR [R1R0],A         OR ACC to data memory         1         1           AND A,XH         OR CC to data memory         1         1           AND A,XH         AND immediate data to ACC         2         2           OR A,XH         Exclusive-OR immediate data to ACC         2         2           XOR A,XH         Exclusive-OR immediate data to ACC         2         2           Increment & Decrement         Increment ACC         1         1           INC R         Increment data memory         1         1           INC R         Increment ACC         1         1           INC R         Decrement data memory         1         1           INC R         Decrement data memory         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       | $2 \mid 2 \mid$                      |     |

| DAA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | $2 \mid 2 \mid$                      | √   |

| AND data memory to ACC  OR A,[R1R0]  OR data memory to ACC  1 1  XOR A,[R1R0]  Exclusive-OR data memory to ACC  AND [R1R0],A  OR ACC to data memory  OR [R1R0],A  OR ACC to data memory  I 1  XOR [R1R0],A  OR ACC to data memory  I 2  XOR [R1R0],A  AND immediate data to ACC  OR A,XH  OR immediate data to ACC  OR A,XH  OR immediate data to ACC  Increment & Decrement  INC A  Increment data memory  Increment data me |                                       | 1 1                                  | √   |

| OR A,[R1R0]       OR data memory to ACC       1       1         XOR A,[R1R0]       Exclusive-OR data memory to ACC       1       1         AND [R1R0],A       AND ACC to data memory       1       1         OR [R1R0],A       OR ACC to data memory       1       1         XOR [R1R0],A       Exclusive-OR ACC to data memory       1       1         AND a,XH       AND immediate data to ACC       2       2       2         OR A,XH       OR immediate data to ACC       2       2       2         XOR A,XH       Exclusive-OR immediate data to ACC       2       2       2         Increment & Decrement       Decrement       1       1       1         INC Rn       Increment ACC       1       1       1       1         INC [R1R0]       Increment data memory       1       1       1         INC [R3R2]       Increment data memory       1       1       1         DEC A       Decrement register       1       1       1         DEC [R1R0]       Decrement data memory       1       1       1         DEC [R3R2]       Decrement data memory       1       1       1         Data Move       Move data memory to ACC       1 </td <td>peration</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | peration                              |                                      |     |

| XOR A, R1R0   Exclusive-OR data memory to ACC   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21R0] AN                              | 1 1                                  | _   |

| AND [R1R0],A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R0] OR                                | 1   1                                | _   |

| OR [R1R0],A         OR ACC to data memory         1         1           XOR [R1R0],A         Exclusive—OR ACC to data memory         1         1           AND A,XH         AND immediate data to ACC         2         2           OR A,XH         OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           Increment &         Decrement         1         1         1           INC RA,XH         Increment ACC         2         2         2           Increment &         Decrement acc         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td>.1R0] Exc</td> <td>1 1</td> <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .1R0] Exc                             | 1 1                                  | _   |

| XOR [R1RO],A         Exclusive—OR ACC to data memory         1         1           AND A,XH         AND immediate data to ACC         2         2           OR A,XH         OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         1         1           INC R         Increment ACC         1         1         1           INC R         Increment data memory         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30],A AN                              | 1 1                                  | _   |

| AND A,XH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | )],A OR                               | 1 1                                  | _   |

| OR A,XH         OR immediate data to ACC         2         2           XOR A,XH         Exclusive—OR immediate data to ACC         2         2           Increment & Decrement         Increment ACC         1         1         1           INC A         Increment ACC         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RO],A Exc                             | 1 1                                  | _   |

| Increment & Decrement   Decr   |                                       | $2 \mid 2$                           | _   |

| Increment & Decrement   Decr   | OR                                    | $2 \mid 2 \mid$                      | _   |

| Decrement   INC A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | H Exc                                 |                                      | _   |

| INC A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                      |     |

| INC Rn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ement                                 |                                      |     |