# HIGH SPEED MASTER/SLAVE D FLIP-FLOP

UPG706B-1 UPG706B-2

### **FEATURES**

- ECL COMPATIBLE

- ULTRA HIGH SPEED AND HIGH INPUT SENSITIVITY fmax = 4 GHz MIN at ECL Input Level (UPG706B-1, -2)

- HERMETICALLY SEALED CERAMIC PACKAGE ASSURES HIGH RELIABILITY

- UPG706B-1 MAX INPUT SENSITIVITY: (Vin = 200 mVp-p at 2 GHz MIN.)

- UPG706B-2 MAX INPUT SENSITIVITY: (VIN = 600 mVP-P at 2 GHz MIN.)

# **DESCRIPTION AND APPLICATIONS**

UPG706B is a GaAs ultra high speed and high sensitivity master/slave D-type Flip-Flop. It is recommended as the data regeneration circuit in a high speed fiber optics communications receiver. It incorporates a high sensitivity amplifier and a high speed D-FF on a single GaAs substrate. This product is also available in chip form, (UPG706P).

### ABSOLUTE MAXIMUM RATINGS (TA= 25°C)

| SYMBOLS | PARAMETERS                 | UNITS | RATINGS     |  |

|---------|----------------------------|-------|-------------|--|

| Voo     | Supply Voltage             | ٧     | +4          |  |

| Vssı    | Supply Voltage             | ٧     | Voo-4       |  |

| Vss2    | Supply Voltage             | ٧     | -8          |  |

| Vin     | Input Voltage              | ٧     | VDD - VSS2  |  |

| Tstg    | Storage Temperature        | °C    | -65 to +175 |  |

| TC(OP)  | Operating Case Temperature | °C    | -65 to +125 |  |

| Рт      | Total Power Dissipation    | mW    | 800         |  |

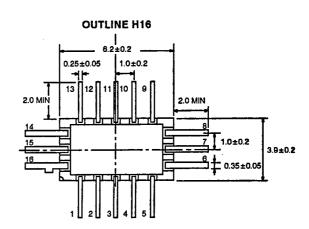

# OUTLINE DIMENSIONS (Units in mm)

#### Notes:

- Vos and Vose, which are normally open, can also be used as blas

adjusting terminals to optimize operating frequency or output

waveform. Vos and Vose are terminals to adjust the F/F circuit

current and output waveform respectively. When Vose, which is

an input logic threshold value adjusting terminal, is kept open,

the optimum voltage is generated internally.

- The metallized section on the back surface of the package, which is used as a heat sink, is shared with the Vss2 terminal (Vss = -5.2V normally). Do not ground the metallized section to GND (0 V) to prevent short circuit with VDD (VDD = 0 V normally) or some other terminals.

- 3. Take great care to prevent static electricity because the IC circuitry is composed of GaAs MES FETs.

# ELECTRICAL CHARACTERISTICS (TA = 25°C)

| PART NUMBER PACKAGE OUTLINE |                                        |                 | UPG706B-1, 706B-2<br>H16 |      |      |      |

|-----------------------------|----------------------------------------|-----------------|--------------------------|------|------|------|

| SYMBOLS                     | PARAMETERS                             | TEST CONDITIONS | UNITS                    | MIN  | TYP  | MAX  |

| Iss2                        | Supply Current                         |                 | mA                       |      | 110  |      |

| Vон                         | High Level Output Voltage <sup>1</sup> |                 | ٧                        | -1.0 | -0.8 | -0.6 |

| Vol                         | Low Level Output Voltage <sup>1</sup>  | VDD = 0 V       | V                        | -2.0 | -1.8 | -1.6 |

| Vтн                         | Threshold Voltage                      | 125 – 01        | ٧                        |      | -1.3 |      |

| Іон                         | High Level Output Current              | Vss1 = -2 V     | mA                       | 0 .  | 4    |      |

| loL                         | Low Level Output Current               | Vss2 = -5.2 V   | mA                       |      | 26   |      |

| fфмах                       | Maximum Clock Frequency <sup>2</sup>   | VSS2 = -5.2 V   | GHz                      | 4    |      |      |

| fфмах                       | Maximum Clock Frequency <sup>3</sup>   |                 | GHz                      | 2    | ·    |      |

| ф                           | Phase Margin                           |                 | deg.                     |      | 250  |      |

| TPD                         | Propagation Delay                      |                 | ps                       |      | 400  | 600  |

| TR                          | Output Rise Time <sup>5</sup>          |                 | ps                       |      | 100  |      |

| TF                          | Output Fall Time <sup>6</sup>          |                 | ps                       |      | 100  |      |

| ts                          | Set Up Time                            |                 | ps                       |      | 290  |      |

| tн                          | Hold Time                              |                 | ps                       |      | -110 |      |

### Notes:

The value in case 50  $\Omega$  load resistance is connected between output and VTT terminal. VTT is the terminating voltage of the external 50  $\Omega$  load resistance and it becomes the high level voltage of the output waveform. The normal output waveform can be obtained even if VTT is controlled from -1.5 V to 0 V. If VTT is adjusted to -0.8 V, the ECL level output can be obtained.

ECL input level.

200 mVP-P input level (UPG706B-1)

600 mVP-P input level (UPG706B-2)

The time from 20% to 80% of output voltage amplitude.

## **TRUTH TABLE**

|       | INF  | ОИТРИТ |       |        |        |  |

|-------|------|--------|-------|--------|--------|--|

| СГОСК | DATA | SET    | RESET | Qn + 1 | Qn + 1 |  |

|       | L    | L      | L     | Ĺ      | Н      |  |

|       | Н    | L      | L     | н      | L      |  |

|       | X    | L      | L     | Qn     | Ōn     |  |

| Х     | Х    | L      | Н     | L      | Н      |  |

| Х     | X    | Н      | L     | Н      | L      |  |

| Х     | Х    | Н      | Н     |        |        |  |

H:

High Level

L: X: Low Level High or Low

Qn:

The output before the clock pulse Qn + 1: The output after the clock pulse

A. When it is open, each terminal has following voltage internally.

D: ECL Reference Voltage

CK: ECL Reference Voltage

CK: ECL Reference Voltage

RESET: Low SET:

Low

Vcs, Vcsc and Vcsa: Appropriate voltage as needed.

B. Symmetric termination is required for Q and  $\overline{Q}$  even when they are not used.