# Precision, Very Low Noise, Low Input Bias Current, Wide Bandwidth JFET Operational Amplifiers

# AD8510/AD8512/AD8513

#### FEATURES

Fast settling time: 500 ns to 0.1% Low offset voltage: 400  $\mu$ V maximum Low T<sub>c</sub>V<sub>os</sub>: 1  $\mu$ V/°C typical Low input bias current: 25 pA typical at V<sub>5</sub> = ±15 V Dual-supply operation: ±5 V to ±15 V Low noise: 8 nV/ $\sqrt{Hz}$  typical at f = 1 kHz Low distortion: 0.0005% No phase reversal Unity gain stable

#### **APPLICATIONS**

Instrumentation Multipole filters Precision current measurement Photodiode amplifiers Sensors Audio

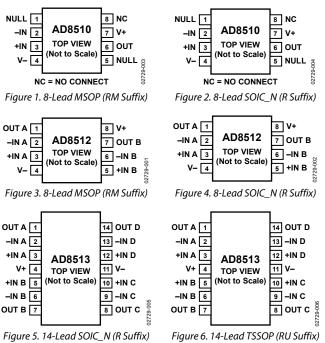

### **PIN CONFIGURATIONS**

**GENERAL DESCRIPTION**

The AD8510/AD8512/AD8513 are single-, dual-, and quadprecision JFET amplifiers that feature low offset voltage, input bias current, input voltage noise, and input current noise.

The combination of low offsets, low noise, and very low input bias currents makes these amplifiers especially suitable for high impedance sensor amplification and precise current measurements using shunts. The combination of dc precision, low noise, and fast settling time results in superior accuracy in medical instruments, electronic measurement, and automated test equipment. Unlike many competitive amplifiers, the AD8510/ AD8512/AD8513 maintain their fast settling performance even with substantial capacitive loads. Unlike many older JFET amplifiers, the AD8510/AD8512/AD8513 do not suffer from output phase reversal when input voltages exceed the maximum common-mode voltage range. Fast slew rate and great stability with capacitive loads make the AD8510/AD8512/AD8513 a perfect fit for high performance filters. Low input bias currents, low offset, and low noise result in a wide dynamic range of photodiode amplifier circuits. Low noise and distortion, high output current, and excellent speed make the AD8510/AD8512/AD8513 great choices for audio applications.

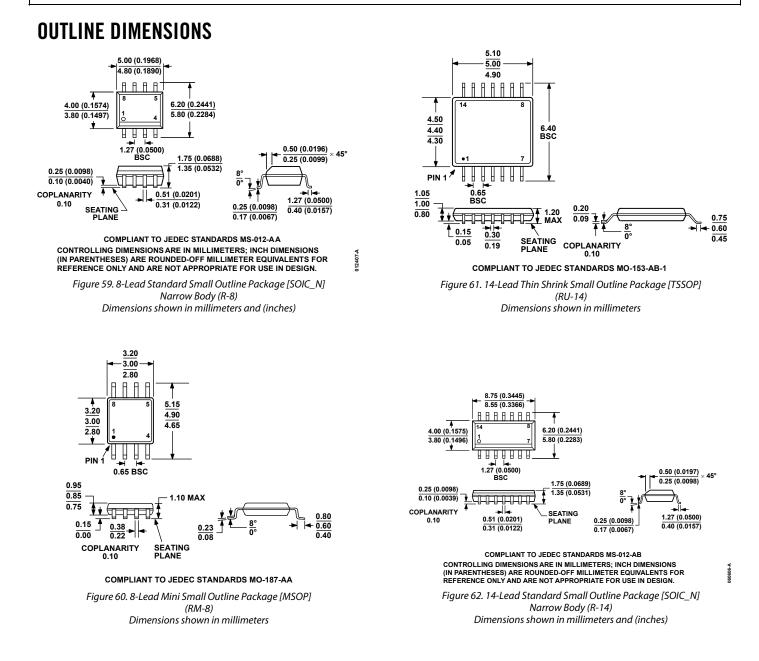

The AD8510/AD8512 are both available in 8-lead narrow SOIC\_N and 8-lead MSOP packages. MSOP-packaged parts are only available in tape and reel. The AD8513 is available in 14-lead SOIC\_N and TSSOP packages.

The AD8510/AD8512/AD8513 are specified over the  $-40^{\circ}$ C to  $+125^{\circ}$ C extended industrial temperature range.

Rev. I Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2002-2009 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features                             |

|--------------------------------------|

| Applications1                        |

| Pin Configurations                   |

| General Description                  |

| Revision History                     |

| Specifications                       |

| Electrical Characteristics           |

| Absolute Maximum Ratings             |

| ESD Caution                          |

| Typical Performance Characteristics7 |

| General Application Information13    |

| Input Overvoltage Protection         |

### **REVISION HISTORY**

### 2/09-Rev. H to Rev. I

| Changes to Figure 25<br>Changes to Ordering Guide |           |

|---------------------------------------------------|-----------|

| 10/07—Rev. G to Rev. H                            |           |

| Changes to Crosstalk Section<br>Added Figure 58   |           |

| 6/07—Rev. F to Rev. G                             |           |

| Changes to Figure 1 and Figure 2                  |           |

| Changes to Table 1 and Table 2                    |           |

| Updated Outline Dimensions                        |           |

| Changes to Ordering Guide                         |           |

| 6/06—Rev. E to Rev. F                             |           |

| Changes to Figure 23                              | 9         |

| Updated Outline Dimensions                        |           |

| Changes to Ordering Guide                         |           |

| 6/04—Rev. D to Rev. E                             |           |

| Changes to Format                                 | Universal |

| Changes to Specifications                         |           |

| Updated Outline Dimensions                        |           |

| 10/03—Rev. C to Rev. D                            |           |

| Added AD8513 Model                                | Universal |

| Changes to Specifications                         |           |

| Added Figure 36 through Figure 40                 |           |

| Added Figure 55 and Figure 57                     | 17        |

| Changes to Ordering Guide                         |           |

|   | Output Phase Reversal                   | . 13 |

|---|-----------------------------------------|------|

|   | Total Harmonic Distortion (THD) + Noise | . 13 |

|   | Total Noise Including Source Resistors  | . 13 |

|   | Settling Time                           | . 14 |

|   | Overload Recovery Time                  | . 14 |

|   | Capacitive Load Drive                   | . 14 |

|   | Open-Loop Gain and Phase Response       | . 15 |

|   | Precision Rectifiers                    | . 16 |

|   | I-V Conversion Applications             | . 17 |

| C | Dutline Dimensions                      | . 19 |

|   | Ordering Guide                          | . 20 |

#### 9/03—Rev. B to Rev. C

| Changes to Ordering Guide                                                                                                                                                                                                                                      |                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Updated Figure 2                                                                                                                                                                                                                                               |                                                              |

| Changes to Input Overvoltage Protection Section                                                                                                                                                                                                                |                                                              |

| Changes to Figure 10 and Figure 11                                                                                                                                                                                                                             |                                                              |

| Changes to Photodiode Circuits Section                                                                                                                                                                                                                         |                                                              |

| Changes to Figure 13 and Figure 14                                                                                                                                                                                                                             |                                                              |

| Deleted Precision Current Monitoring Section                                                                                                                                                                                                                   |                                                              |

| Updated Outline Dimensions                                                                                                                                                                                                                                     |                                                              |

| 3/03—Rev. A to Rev. B                                                                                                                                                                                                                                          |                                                              |

| Updated Figure 5                                                                                                                                                                                                                                               |                                                              |

| Updated Outline Dimensions                                                                                                                                                                                                                                     |                                                              |

| 8/02—Rev. 0 to Rev. A                                                                                                                                                                                                                                          |                                                              |

|                                                                                                                                                                                                                                                                |                                                              |

| Added AD8510 Model                                                                                                                                                                                                                                             | Universal                                                    |

|                                                                                                                                                                                                                                                                |                                                              |

| Added Pin Configurations                                                                                                                                                                                                                                       | 1                                                            |

| Added Pin Configurations<br>Changes to Specifications                                                                                                                                                                                                          | 1<br>2                                                       |

| Added Pin Configurations                                                                                                                                                                                                                                       | 1<br>2<br>4                                                  |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide                                                                                                                                                                             | 1<br>2<br>4<br>5                                             |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3                                                                                                                                               | 1<br>                                                        |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3<br>Added TPC 10 and TPC 12                                                                                                                    | 1<br>                                                        |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3<br>Added TPC 10 and TPC 12<br>Replaced TPC 20                                                                                                 |                                                              |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3<br>Added TPC 10 and TPC 12<br>Replaced TPC 20<br>Replaced TPC 27                                                                              |                                                              |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3<br>Added TPC 10 and TPC 12<br>Replaced TPC 20<br>Replaced TPC 27<br>Changes to General Application Information Section                        |                                                              |

| Added Pin Configurations<br>Changes to Specifications<br>Changes to Ordering Guide<br>Changes to TPC 2 and TPC 3<br>Added TPC 10 and TPC 12<br>Replaced TPC 20<br>Replaced TPC 27<br>Changes to General Application Information Section<br>Changes to Figure 5 | 1<br>2<br>4<br>5<br>6<br>8<br>9<br>9<br>10<br>11<br>11<br>13 |

## **SPECIFICATIONS**

@  $V_{\text{S}}$  = ±5 V,  $V_{\text{CM}}$  = 0 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

#### Table 1.

| Parameter                                   | Symbol                   | Conditions                                                                   | Min  | Тур    | Мах  | Unit    |

|---------------------------------------------|--------------------------|------------------------------------------------------------------------------|------|--------|------|---------|

| INPUT CHARACTERISTICS                       |                          |                                                                              |      |        |      |         |

| Offset Voltage (B Grade) <sup>1</sup>       | Vos                      |                                                                              |      | 0.08   | 0.4  | mV      |

|                                             |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 0.8  | mV      |

| Offset Voltage (A Grade)                    | Vos                      |                                                                              |      | 0.1    | 0.9  | mV      |

|                                             |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 1.8  | mV      |

| Input Bias Current                          | l <sub>B</sub>           |                                                                              |      | 21     | 75   | рА      |

|                                             |                          | $-40^{\circ}C < T_A < +85^{\circ}C$                                          |      |        | 0.7  | nA      |

|                                             |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 7.5  | nA      |

| Input Offset Current                        | los                      |                                                                              |      | 5      | 50   | рА      |

|                                             |                          | $-40^{\circ}C < T_A < +85^{\circ}C$                                          |      |        | 0.3  | nA      |

|                                             |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 0.5  | nA      |

| Input Capacitance                           |                          |                                                                              |      |        |      |         |

| Differential                                |                          |                                                                              |      | 12.5   |      | рF      |

| Common Mode                                 |                          |                                                                              |      | 11.5   |      | pF      |

| Input Voltage Range                         |                          |                                                                              | -2.0 |        | +2.5 | V       |

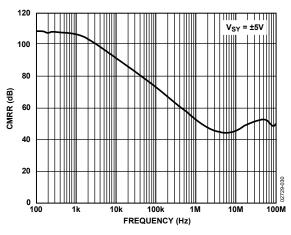

| Common-Mode Rejection Ratio                 | CMRR                     | $V_{CM} = -2.0 \text{ V to } +2.5 \text{ V}$                                 | 86   | 100    |      | dB      |

| Large-Signal Voltage Gain                   | Avo                      | $R_L = 2 \text{ k}\Omega$ , $V_O = -3 \text{ V}$ to $+3 \text{ V}$           | 65   | 107    |      | V/mV    |

| Offset Voltage Drift (B Grade) <sup>1</sup> | $\Delta V_{os}/\Delta T$ |                                                                              |      | 0.9    | 5    | μV/°C   |

| Offset Voltage Drift (A Grade)              | $\Delta V_{OS}/\Delta T$ |                                                                              |      | 1.7    | 12   | μV/°C   |

| OUTPUT CHARACTERISTICS                      |                          |                                                                              |      |        |      |         |

| Output Voltage High                         | Vон                      | $R_L = 10 \ k\Omega$                                                         | 4.1  | 4.3    |      | v       |

| Output Voltage Low                          | Vol                      | $R_L = 10 \text{ k}\Omega, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$ |      | -4.9   | -4.7 | v       |

| Output Voltage High                         | V <sub>OH</sub>          | $R_L = 2 \ k\Omega$                                                          | 3.9  | 4.2    |      | v       |

| Output Voltage Low                          | Vol                      | $R_L = 2 \text{ k}\Omega, -40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$  |      | -4.9   | -4.5 | v       |

| Output Voltage High                         | V <sub>OH</sub>          | $R_L = 600 \Omega$                                                           | 3.7  | 4.1    |      | v       |

| Output Voltage Low                          | Vol                      | $R_L = 600 \Omega$ , $-40^{\circ}C < T_A < +125^{\circ}C$                    |      | -4.8   | -4.2 | v       |

| Output Current                              | I <sub>OUT</sub>         |                                                                              | ±40  | ±54    |      | mA      |

| POWER SUPPLY                                |                          |                                                                              |      |        |      |         |

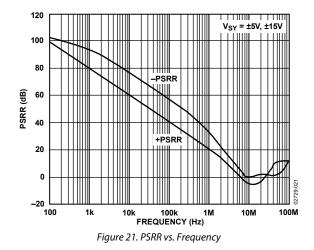

| Power Supply Rejection Ratio                | PSRR                     | $V_{s} = \pm 4.5 V \text{ to } \pm 18 V$                                     | 86   | 130    |      | dB      |

| Supply Current/Amplifier                    | lsy                      |                                                                              |      |        |      |         |

| AD8510/AD8512/AD8513                        |                          | $V_{O} = 0 V$                                                                |      | 2.0    | 2.3  | mA      |

| AD8510/AD8512                               |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 2.5  | mA      |

| AD8513                                      |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                         |      |        | 2.75 | mA      |

| DYNAMIC PERFORMANCE                         |                          |                                                                              |      |        |      |         |

| Slew Rate                                   | SR                       | $R_L = 2 \ k\Omega$                                                          |      | 20     |      | V/µs    |

| Gain Bandwidth Product                      | GBP                      |                                                                              |      | 8      |      | MHz     |

| Settling Time                               | ts                       | To 0.1%, 0 V to 4 V step, G = +1                                             |      | 0.4    |      | μs      |

| Total Harmonic Distortion (THD) + Noise     | THD + N                  | 1 kHz, G = +1, R <sub>L</sub> = 2 kΩ                                         |      | 0.0005 |      | %       |

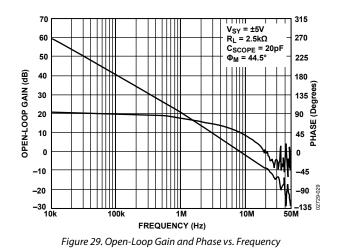

| Phase Margin                                | фм                       |                                                                              |      | 44.5   |      | Degrees |

| NOISE PERFORMANCE                           |                          |                                                                              |      |        |      |         |

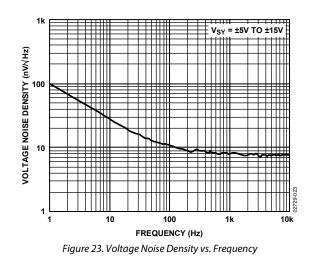

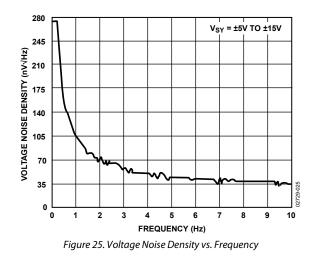

| Voltage Noise Density                       | en                       | f = 10 Hz                                                                    |      | 34     |      | nV/√Hz  |

|                                             |                          | f = 100 Hz                                                                   |      | 12     |      | nV/√Hz  |

|                                             |                          | f = 1 kHz                                                                    |      | 8.0    | 10   | nV/√Hz  |

|                                             |                          | f = 10 kHz                                                                   |      | 7.6    |      | nV/√Hz  |

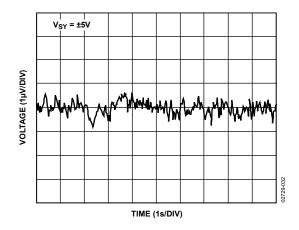

| Peak-to-Peak Voltage Noise                  | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz bandwidth                                                    |      | 2.4    | 5.2  | μV p-p  |

<sup>1</sup> AD8510/AD8512 only.

### **ELECTRICAL CHARACTERISTICS**

@  $V_{\text{S}}$  = ±15 V,  $V_{\text{CM}}$  = 0 V,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

#### Table 2.

| Parameter                                   | Symbol                   | Conditions                                                                                                     | Min       | Тур        | Max       | Unit      |

|---------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------|-----------|------------|-----------|-----------|

| INPUT CHARACTERISTICS                       |                          |                                                                                                                |           |            |           |           |

| Offset Voltage (B Grade) <sup>1</sup>       | Vos                      |                                                                                                                |           | 0.08       | 0.4       | mV        |

|                                             |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                         |           |            | 0.8       | mV        |

| Offset Voltage (A Grade)                    | Vos                      |                                                                                                                |           | 0.1        | 1.0       | mV        |

| Oliset Voltage (A Glade)                    | VOS                      | -40°C < T <sub>A</sub> < +125°C                                                                                |           | 0.1        | 1.8       | mV        |

| Input Pipe Current                          |                          | $-40 C < T_A < +125 C$                                                                                         |           | 25         | 80        |           |

| Input Bias Current                          | IB                       | -40°C < T <sub>A</sub> < +85°C                                                                                 |           | 25         |           | рА        |

|                                             |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                         |           |            | 0.7<br>10 | nA        |

| Input Officet Current                       | 1                        | $-40 C < T_A < +123 C$                                                                                         |           | 6          | 75        | nA        |

| Input Offset Current                        | los                      | 40°C (T ( ) 85°C                                                                                               |           | 0          |           | pА        |

|                                             |                          | $-40^{\circ}C < T_{A} < +85^{\circ}C$                                                                          |           |            | 0.3       | nA        |

|                                             |                          | -40°C < T <sub>A</sub> < +125°C                                                                                |           |            | 0.5       | nA        |

| Input Capacitance<br>Differential           |                          |                                                                                                                |           | 12.5       |           | <b>DF</b> |

| Common Mode                                 |                          |                                                                                                                |           |            |           | pF        |

|                                             |                          |                                                                                                                | -13.5     | 11.5       | +13.0     | pF<br>V   |

| Input Voltage Range                         | CMRR                     |                                                                                                                |           | 109        | +13.0     | v<br>dB   |

| Common-Mode Rejection Ratio                 | -                        | $V_{CM} = -12.5 \text{ V to } +12.5 \text{ V}$                                                                 | 86<br>115 | 108<br>106 |           |           |

| Large-Signal Voltage Gain                   | Avo                      | $ \begin{array}{l} R_L = 2 \; k\Omega,  V_{CM} = 0 \; V, \\ V_O = -13.5 \; V \; to \; +13.5 \; V \end{array} $ | 115       | 196        |           | V/mV      |

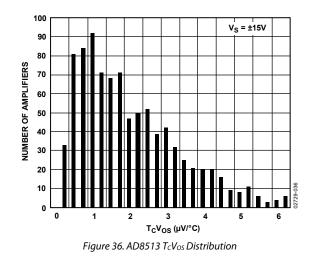

| Offset Voltage Drift (B Grade) <sup>1</sup> | $\Delta V_{OS}/\Delta T$ |                                                                                                                |           | 1.0        | 5         | μV/°C     |

| Offset Voltage Drift (A Grade)              | $\Delta V_{os}/\Delta T$ |                                                                                                                |           | 1.7        | 12        | μV/°C     |

| OUTPUT CHARACTERISTICS                      |                          |                                                                                                                |           |            |           |           |

| Output Voltage High                         | V <sub>OH</sub>          | $R_L = 10 \ k\Omega$                                                                                           | +14.0     | +14.2      |           | V         |

| Output Voltage Low                          | Vol                      | $R_L = 10 \text{ k}\Omega$ , $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                |           | -14.9      | -14.6     | V         |

| Output Voltage High                         | V <sub>OH</sub>          | $R_L = 2 \ k\Omega$                                                                                            | +13.8     | +14.1      |           | V         |

| Output Voltage Low                          | Vol                      | $R_L = 2 \text{ k}\Omega$ , $-40^{\circ}\text{C} < T_A < +125^{\circ}\text{C}$                                 |           | -14.8      | -14.5     | V         |

| Output Voltage High                         | V <sub>OH</sub>          | $R_L = 600 \ \Omega$                                                                                           | +13.5     | +13.9      |           | V         |

|                                             |                          | $R_L = 600 \ \Omega, -40^{\circ}C < T_A < +125^{\circ}C$                                                       | +11.4     |            |           | V         |

| Output Voltage Low                          | Vol                      | $R_L = 600 \ \Omega$                                                                                           |           | -14.3      | -13.8     | V         |

|                                             |                          | $R_L = 600 \ \Omega, -40^{\circ}C < T_A < +125^{\circ}C$                                                       |           |            | -12.1     | V         |

| Output Current                              | IOUT                     |                                                                                                                |           | ±70        |           | mA        |

| POWER SUPPLY                                |                          |                                                                                                                |           |            |           |           |

| Power Supply Rejection Ratio                | PSRR                     | $V_{S} = \pm 4.5 \text{ V to } \pm 18 \text{ V}$                                                               | 86        |            |           | dB        |

| Supply Current/Amplifier                    | Isy                      |                                                                                                                |           |            |           |           |

| AD8510/AD8512/AD8513                        |                          | $V_{\rm O} = 0 V$                                                                                              |           | 2.2        | 2.5       | mA        |

| AD8510/AD8512                               |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                           |           |            | 2.6       | mA        |

| AD8513                                      |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                           |           |            | 3.0       | mA        |

| DYNAMIC PERFORMANCE                         |                          |                                                                                                                |           |            |           |           |

| Slew Rate                                   | SR                       | $R_L = 2 \ k\Omega$                                                                                            |           | 20         |           | V/µs      |

| Gain Bandwidth Product                      | GBP                      |                                                                                                                |           | 8          |           | MHz       |

| Settling Time                               | ts                       | To 0.1%, 0 V to 10 V step, G = +1                                                                              |           | 0.5        |           | μs        |

|                                             |                          | To 0.01%, 0 V to 10 V step, G = +1                                                                             |           | 0.9        |           | μs        |

| Total Harmonic Distortion (THD) + Noise     | THD + N                  | 1 kHz, G = +1, $R_L = 2 k\Omega$                                                                               |           | 0.0005     |           | %         |

| Phase Margin                                | фм                       |                                                                                                                |           | 52         |           | Degre     |

| Parameter                  | Symbol | Conditions                | Min | Тур | Мах | Unit   |

|----------------------------|--------|---------------------------|-----|-----|-----|--------|

| NOISE PERFORMANCE          |        |                           |     |     |     |        |

| Voltage Noise Density      | en     | f = 10 Hz                 |     | 34  |     | nV/√Hz |

|                            |        | f = 100 Hz                |     | 12  |     | nV/√Hz |

|                            |        | f = 1 kHz                 |     | 8.0 | 10  | nV/√Hz |

|                            |        | f = 10 kHz                |     | 7.6 |     | nV/√Hz |

| Peak-to-Peak Voltage Noise | en p-p | 0.1 Hz to 10 Hz bandwidth |     | 2.4 | 5.2 | μV p-p |

<sup>1</sup> AD8510/AD8512 only.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                     | Rating                  |

|-----------------------------------------------|-------------------------|

| Supply Voltage                                | ±18 V                   |

| Input Voltage                                 | ±Vs                     |

| Output Short-Circuit Duration to GND          | Observe derating curves |

| Storage Temperature Range                     | –65°C to +150°C         |

| Operating Temperature Range                   | -40°C to +125°C         |

| Junction Temperature Range                    | –65°C to +150°C         |

| Lead Temperature (Soldering, 10 sec)          | 300°C                   |

| Electrostatic Discharge<br>(Human Body Model) | 2000 V                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 4. Thermal Resistance

| Package Type       | θ <sub>JA</sub> <sup>1</sup> | θις | Unit |

|--------------------|------------------------------|-----|------|

| 8-Lead MSOP (RM)   | 210                          | 45  | °C/W |

| 8-Lead SOIC_N (R)  | 158                          | 43  | °C/W |

| 14-Lead SOIC_N (R) | 120                          | 36  | °C/W |

| 14-Lead TSSOP (RU) | 180                          | 35  | °C/W |

$^1$   $\theta_{JA}$  is specified for worst-case conditions, that is,  $\theta_{JA}$  is specified for device soldered in circuit board for surface-mount packages.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

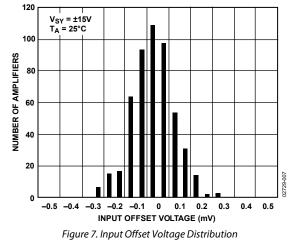

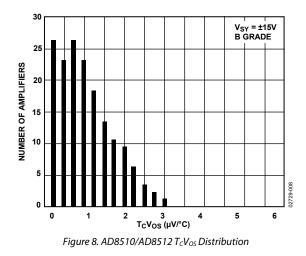

## **TYPICAL PERFORMANCE CHARACTERISTICS**

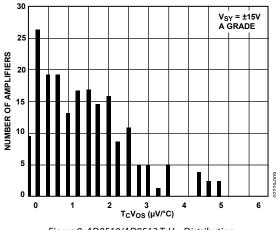

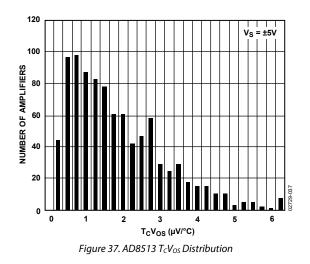

Figure 9. AD8510/AD8512 T<sub>c</sub>V<sub>os</sub> Distribution

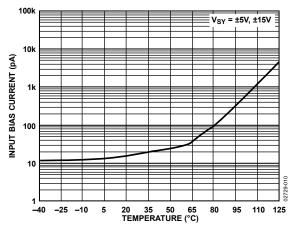

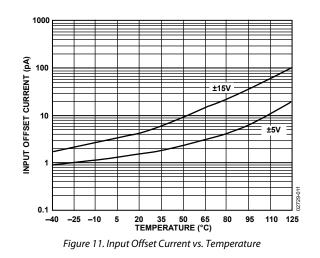

Figure 10. Input Bias Current vs. Temperature

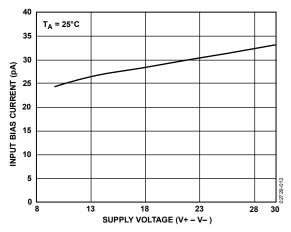

Figure 12. Input Bias Current vs. Supply Voltage

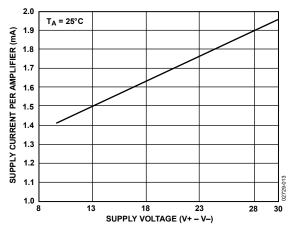

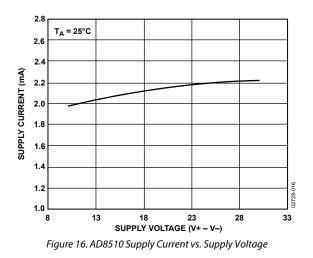

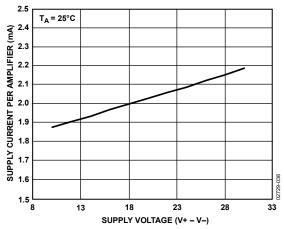

Figure 13. AD8512 Supply Current per Amplifier vs. Supply Voltage

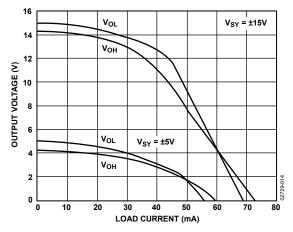

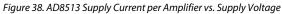

Figure 14. AD8510/AD8512 Output Voltage vs. Load Current

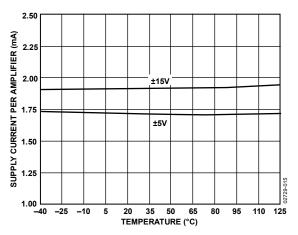

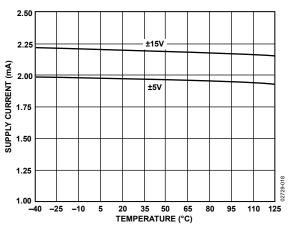

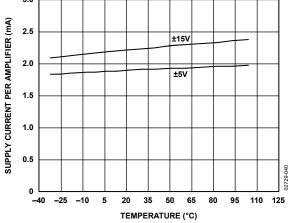

Figure 15. AD8512 Supply Current per Amplifier vs. Temperature

Figure 18. AD8510 Supply Current vs. Temperature

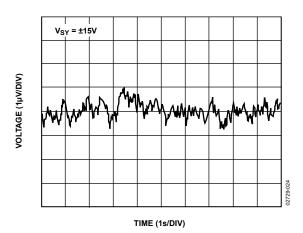

Figure 24. 0.1 Hz to 10 Hz Input Voltage Noise

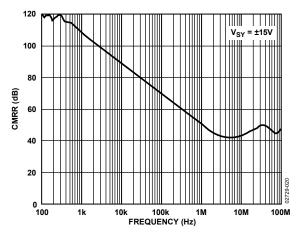

Figure 20. CMRR vs. Frequency

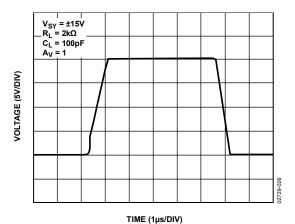

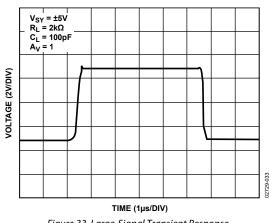

Figure 26. Large-Signal Transient Response

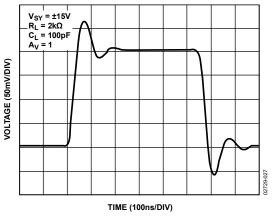

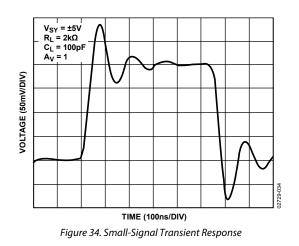

Figure 27. Small-Signal Transient Response

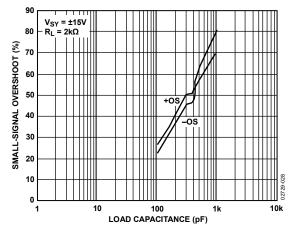

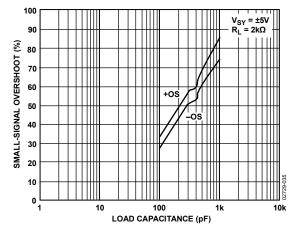

Figure 28. Small-Signal Overshoot vs. Load Capacitance

Figure 30. CMRR vs. Frequency

Figure 32. 0.1 Hz to 10 Hz Input Voltage Noise

Figure 33. Large-Signal Transient Response

Figure 35. Small-Signal Overshoot vs. Load Capacitance

## GENERAL APPLICATION INFORMATION INPUT OVERVOLTAGE PROTECTION

The AD8510/AD8512/AD8513 have internal protective circuitry that allows voltages as high as 0.7 V beyond the supplies to be applied at the input of either terminal without causing damage. For higher input voltages, a series resistor is necessary to limit the input current. The resistor value can be determined from the formula

$$\frac{V_{IN} - V_S}{R_S} \le 5 \text{ mA}$$

With a very low offset current of <0.5 nA up to 125°C, higher resistor values can be used in series with the inputs. A 5 k $\Omega$  resistor protects the inputs from voltages as high as 25 V beyond the supplies and adds less than 10  $\mu$ V to the offset.

### **OUTPUT PHASE REVERSAL**

Phase reversal is a change of polarity in the transfer function of the amplifier. This can occur when the voltage applied at the input of an amplifier exceeds the maximum common-mode voltage.

Phase reversal can cause permanent damage to the device and can result in system lockups. The AD8510/AD8512/AD8513 do not exhibit phase reversal when input voltages are beyond the supplies.

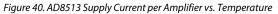

Figure 41. No Phase Reversal

### TOTAL HARMONIC DISTORTION (THD) + NOISE

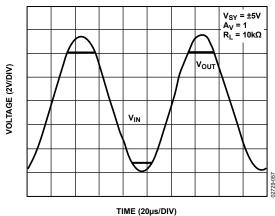

The AD8510/AD8512/AD8513 have low THD and excellent gain linearity, making these amplifiers great choices for precision circuits with high closed-loop gain and for audio application circuits. Figure 42 shows that the AD8510/AD8512/AD8513 have approximately 0.0005% of total distortion when configured in positive unity gain (the worst case) and driving a 100 k $\Omega$  load.

### TOTAL NOISE INCLUDING SOURCE RESISTORS

The low input current noise and input bias current of the AD8510/AD8512/AD8513 make them the ideal amplifiers for circuits with substantial input source resistance. Input offset voltage increases by less than 15 nV per 500  $\Omega$  of source resistance at room temperature. The total noise density of the circuit is

$$_{nTOTAL} = \sqrt{e_n^2 + (i_n R_s)^2 + 4kTR_s}$$

where:

е

$e_n$  is the input voltage noise density of the parts.

$i_n$  is the input current noise density of the parts.  $R_s$  is the source resistance at the noninverting terminal.

*k* is Boltzmann's constant ( $1.38 \times 10^{-23}$  J/K).

*T* is the ambient temperature in Kelvin (T =  $273 + ^{\circ}$ C).

For  $R_S < 3.9 \text{ k}\Omega$ ,  $e_n$  dominates and  $e_{nTOTAL} \approx e_n$ . The current noise of the AD8510/AD8512/AD8513 is so low that its total density does not become a significant term unless  $R_S$  is greater than 165 M $\Omega$ , an impractical value for most applications.

The total equivalent rms noise over a specific bandwidth is expressed as

$$e_{nTOTAL} = e_{nTOTAL} \sqrt{BW}$$

where BW is the bandwidth in hertz.

Note that the previous analysis is valid for frequencies larger than 150 Hz and assumes flat noise above 10 kHz. For lower frequencies, flicker noise (1/f) must be considered.

### SETTLING TIME

Settling time is the time it takes the output of the amplifier to reach and remain within a percentage of its final value after a pulse is applied at the input. The AD8510/AD8512/AD8513 settle to within 0.01% in less than 900 ns with a step of 0 V to 10 V in unity gain. This makes each of these parts an excellent choice as a buffer at the output of DACs whose settling time is typically less than 1  $\mu$ s.

In addition to the fast settling time and fast slew rate, low offset voltage drift and input offset current maintain the full accuracy of 12-bit converters over the entire operating temperature range.

### **OVERLOAD RECOVERY TIME**

Overload recovery, also known as overdrive recovery, is the time it takes the output of an amplifier to recover to its linear region from a saturated condition. This recovery time is particularly important in applications where the amplifier must amplify small signals in the presence of large transient voltages.

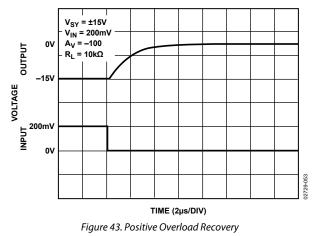

Figure 43 shows the positive overload recovery of the AD8510/ AD8512/AD8513. The output recovers in approximately 200 ns from a saturated condition.

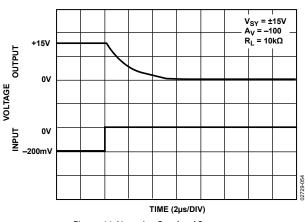

The negative overdrive recovery time shown in Figure 44 is less than 200 ns.

In addition to the fast recovery time, the AD8510/AD8512/ AD8513 show excellent symmetry of the positive and negative recovery times. This is an important feature for transient signal rectification because the output signal is kept equally undistorted throughout any given period.

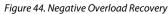

### **CAPACITIVE LOAD DRIVE**

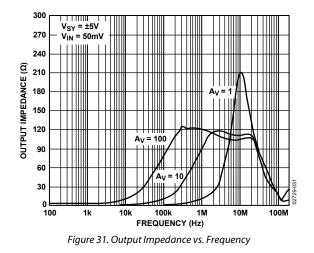

The AD8510/AD8512/AD8513 are unconditionally stable at all gains in inverting and noninverting configurations. Each device is capable of driving a capacitive load of up to 1000 pF without oscillation in unity gain using the worst-case configuration.

However, as with most amplifiers, driving larger capacitive loads in a unity gain configuration may cause excessive overshoot and ringing, or even oscillation. A simple snubber network significantly reduces the amount of overshoot and ringing. The advantage of this configuration is that the output swing of the amplifier is not reduced, because R<sub>S</sub> is outside the feedback loop.

Figure 45. Snubber Network Configuration

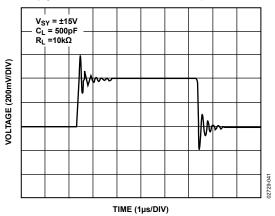

Figure 46 shows a scope plot of the output of the AD8510/AD8512/ AD8513 in response to a 400 mV pulse. The circuit is configured in positive unity gain (worst case) with a load experience of 500 pF.

Figure 46. Capacitive Load Drive Without Snubber

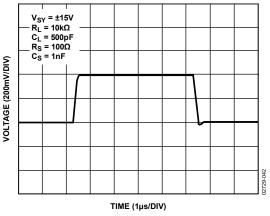

When the snubber circuit is used, the overshoot is reduced from 55% to less than 3% with the same load capacitance. Ringing is virtually eliminated, as shown in Figure 47.

Figure 47. Capacitive Load with Snubber Network

Optimum values for  $R_s$  and  $C_s$  depend on the load capacitance and input stray capacitance and are determined empirically. Table 5 shows a few values that can be used as starting points.

| Table 5. Optimum | Values for Capacitive Loads |

|------------------|-----------------------------|

|------------------|-----------------------------|

| CLOAD  | R <sub>s</sub> (Ω) | Cs     |

|--------|--------------------|--------|

| 500 pF | 100                | 1 nF   |

| 2 nF   | 70                 | 100 pF |

| 5 nF   | 60                 | 300 pF |

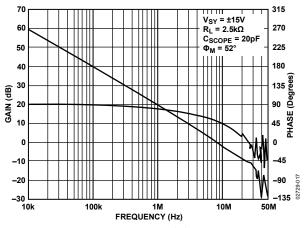

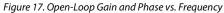

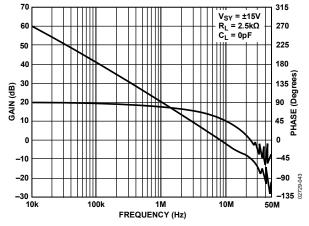

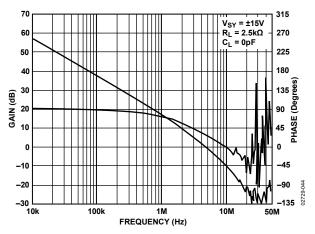

#### **OPEN-LOOP GAIN AND PHASE RESPONSE**

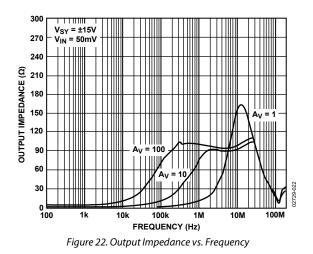

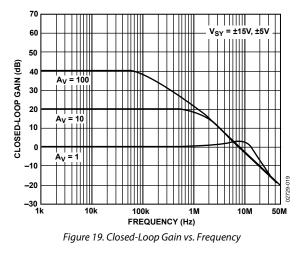

In addition to their impressive low noise, low offset voltage, and offset current, the AD8510/AD8512/AD8513 have excellent loop gain and phase response even when driving large resistive and capacitive loads.

Compared with Competitor A (see Figure 49) under the same conditions, with a 2.5 k $\Omega$  load at the output, the AD8510/AD8512/AD8513 have more than 8 MHz of bandwidth and a phase margin of more than 52°.

Competitor A, on the other hand, has only 4.5 MHz of bandwidth and 28° of phase margin under the same test conditions. Even with a 1 nF capacitive load in parallel with the 2 k $\Omega$  load at the output, the AD8510/AD8512/AD8513 show much better response than Competitor A, whose phase margin is degraded to less than 0, indicating oscillation.

Figure 49. Frequency Response of Competitor A

### **PRECISION RECTIFIERS**

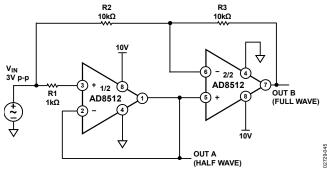

Rectifying circuits are used in a multitude of applications. One of the most popular uses is in the design of regulated power supplies, where a rectifier circuit is used to convert an input sinusoid to a unipolar output voltage.

However, there are some potential problems with amplifiers used in this manner. When the input voltage ( $V_{\rm IN}$ ) is negative, the output is zero, and the magnitude of  $V_{\rm IN}$  is doubled at the inputs of the op amp. If this voltage exceeds the power supply voltage, it may permanently damage some amplifiers. In addition, the op amp must come out of saturation when  $V_{\rm IN}$  is negative. This delays the output signal because the amplifier requires time to enter its linear region.

Although the AD8510/AD8512/AD8513 have a very fast overdrive recovery time, which makes them great choices for the rectification of transient signals, the symmetry of the positive and negative recovery times is also important to keep the output signal undistorted.

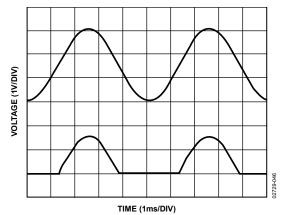

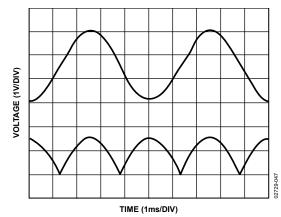

Figure 50 shows the test circuit of the rectifier. The first stage of the circuit is a half-wave rectifier. When the sine wave applied at the input is positive, the output follows the input response. During the negative cycle of the input, the output tries to swing negative to follow the input, but the power supply restrains it to zero. In a similar fashion, the second stage is a follower during the positive cycle of the sine wave and an inverter during the negative cycle.

Figure 50. Half-Wave and Full-Wave Rectifiers

Figure 51. Half-Wave Rectifier Signal (OUT A in Figure 50)

Figure 52. Full-Wave Rectifier Signal (OUT B in Figure 50)

### **I-V CONVERSION APPLICATIONS**

#### **Photodiode Circuits**

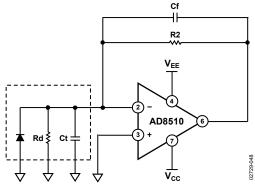

Common applications for I-V conversion include photodiode circuits where the amplifier is used to convert a current emitted by a diode placed at the positive input terminal into an output voltage.

The AD8510/AD8512/AD8513's low input bias current, wide bandwidth, and low noise make them each an excellent choice for various photodiode applications, including fax machines, fiber optic controls, motion sensors, and bar code readers.

The circuit shown in Figure 53 uses a silicon diode with zero bias voltage. This is known as a photovoltaic mode; this configuration limits the overall noise and is suitable for instrumentation applications.

Figure 53. Equivalent Preamplifier Photodiode Circuit

A larger signal bandwidth can be attained at the expense of additional output noise. The total input capacitance (Ct) consists of the sum of the diode capacitance (typically 3 pF to 4 pF) and the amplifier's input capacitance (12 pF), which includes external parasitic capacitance. Ct creates a pole in the frequency response that can lead to an unstable system. To ensure stability and optimize the bandwidth of the signal, a capacitor is placed in the freedback loop of the circuit shown in Figure 53. It creates a zero and yields a bandwidth whose corner frequency is  $1/(2\pi(R2Cf))$ .

The value of R2 can be determined by the ratio

$V/I_D$

where:

V is the desired output voltage of the op amp.  $I_D$  is the diode current.

For example, if  $I_{\rm D}$  is 100  $\mu A$  and a 10 V output voltage is desired, R2 should be 100 k $\Omega$ . Rd (see Figure 53) is a junction resistance that drops typically by a factor of 2 for every 10°C increase in temperature.

A typical value for Rd is 1000 M $\Omega$ . Because Rd >> R2, the circuit behavior is not impacted by the effect of the junction resistance. The maximum signal bandwidth is

$$f_{MAX} = \sqrt{\frac{ft}{2\pi R^2 Ct}}$$

where *ft* is the unity gain frequency of the amplifier.

Cf can be calculated by

$$Cf = \sqrt{\frac{Ct}{2\pi R^2 ft}}$$

where *ft* is the unity gain frequency of the op amp, and it achieves a phase margin,  $\varphi_M$ , of approximately 45°.

A higher phase margin can be obtained by increasing the value of Cf. Setting Cf to twice the previous value yields approximately  $\phi_M = 65^\circ$  and a maximal flat frequency response, but it reduces the maximum signal bandwidth by 50%.

Using the previous parameters with a  $Cf \approx 1$  pF, the signal bandwidth is approximately 2.6 MHz.

#### Signal Transmission Applications

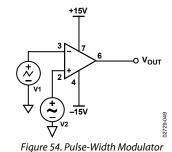

One popular signal transmission method uses pulse-width modulation. High data rates may require a fast comparator rather than an op amp. However, the need for sharp, undistorted signals may favor using a linear amplifier.

The AD8510/AD8512/AD8513 make excellent voltage comparators. In addition to a high slew rate, the AD8510/ AD8512/AD8513 have a very fast saturation recovery time. In the absence of feedback, the amplifiers are in open-loop mode (very high gain). In this mode of operation, they spend much of their time in saturation.

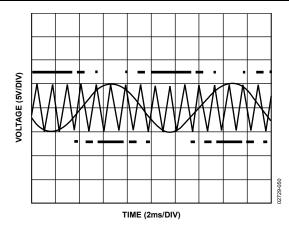

The circuit shown in Figure 54 was used to compare two signals of different frequencies, namely a 100 Hz sine wave and a 1 kHz triangular wave. Figure 55 shows a scope plot of the resulting output waveforms. A pull-up resistor (typically 5 k $\Omega$ ) can be connected from the output to  $V_{CC}$  if the output voltage needs to reach the positive rail. The trade-off is that power consumption is higher.

#### Crosstalk

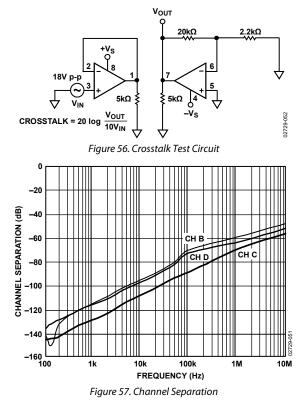

Crosstalk, also known as channel separation, is a measure of signal feedthrough from one channel to another on the same IC. The AD8512/AD8513 have a channel separation of better than –90 dB for frequencies up to 10 kHz and of better than –50 dB for frequencies up to 10 MHz. Figure 57 shows the typical channel separation behavior between Amplifier A (driving amplifier) and each of the following: Amplifier B, Amplifier C, and Amplifier D.

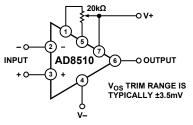

The AD8510 single has two additional active terminals that are not present on the AD8512 dual or AD8513 quad parts. These pins are labeled "null" and are used for fine adjustment of the input offset voltage. Although the guaranteed maximum offset voltage at room temperature is 400  $\mu$ V and over the  $-40^{\circ}$ C to  $+125^{\circ}$ C range is 800 mV maximum, this offset voltage can be reduced by adding a potentiometer to the null pins as shown in Figure 58. With the 20 k $\Omega$  potentiometer shown, the adjustment range is approximately  $\pm 3.5$  mV. The potentiometer parallels low value resistors in the drain circuit of the JFET differential input pair and allows unbalancing of the drain currents to change the offset voltage. If offset adjustment is not required, these pins should be left unconnected.

Caution should be used when adding adjusting potentiometers to any op amp with this capability for several reasons. First, there is gain from these nodes to the output; therefore, capacitive coupling from noisy traces to these nodes will inject noise into the signal path. Second, the temperature coefficient of the potentiometer will not match the temperature coefficient of the internal resistors, so the offset voltage drift with temperature will be slightly affected. Third, this provision is for adjusting the offset voltage of the op amp, not for adjusting the offset of the overall system. Although it is tempting to decrease the value of the potentiometer to attain more range, this will adversely affect the dc and ac parameters. Instead, increase the potentiometer to 50 k $\Omega$  to decrease the range if needed.

Figure 58. Optional Offset Nulling Circuit

### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description | Package Option | Branding |

|------------------------------|-------------------|---------------------|----------------|----------|

| AD8510ARMZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B7A#     |

| AD8510ARMZ <sup>1</sup>      | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B7A#     |

| AD8510AR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510ARZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510ARZ-REEL71             | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510BR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510BR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510BRZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510BRZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8510BRZ-REEL71             | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512ARMZ-REEL <sup>1</sup> | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B8A#     |

| AD8512ARMZ <sup>1</sup>      | -40°C to +125°C   | 8-Lead MSOP         | RM-8           | B8A#     |

| AD8512AR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512AR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512AR-REEL7               | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512ARZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512ARZ-REEL71             | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BR                     | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BR-REEL                | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BR-REEL7               | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BRZ <sup>1</sup>       | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BRZ-REEL <sup>1</sup>  | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8512BRZ-REEL71             | -40°C to +125°C   | 8-Lead SOIC_N       | R-8            |          |

| AD8513AR                     | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513AR-REEL                | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513AR-REEL7               | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513ARZ <sup>1</sup>       | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513ARZ-REEL <sup>1</sup>  | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513ARZ-REEL71             | -40°C to +125°C   | 14-Lead SOIC_N      | R-14           |          |

| AD8513ARU                    | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8513ARU-REEL               | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8513ARUZ <sup>1</sup>      | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

| AD8513ARUZ-REEL <sup>1</sup> | -40°C to +125°C   | 14-Lead TSSOP       | RU-14          |          |

<sup>1</sup> Z = RoHS Compliant Part, # denotes RoHS compliant product may be top or bottom marked.

©2002–2009 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D02729-0-2/09(I)

www.analog.com

Rev. I | Page 20 of 20