# Quad 2-Input NAND Schmitt Trigger

The MC74VHCT132A is an advanced high speed CMOS Schmitt NAND trigger fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation.

Pin configuration and function are the same as the MC74VHC00, but the inputs have hysteresis and, with its Schmitt trigger function, the VHCT132A can be used as a line receiver which will receive slow input signals.

The VHCT inputs are compatible with TTL levels. This device can be used as a level converter for interfacing 3.3V to 5.0V, because it has full 5V CMOS level output swings.

The VHCT132A input structures provide protection when voltages between 0V and 5.5V are applied, regardless of the supply voltage. The output structures also provide protection when  $V_{CC}=0V$ . These input and output structures help prevent device destruction caused by supply voltage – input/output voltage mismatch, battery backup, hot insertion, etc.

The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output. The inputs tolerate voltages up to 7V, allowing the interface of 5V systems to 3V systems.

- High Speed:  $t_{PD} = 4.9$ ns (Typ) at  $V_{CC} = 5V$

- Low Power Dissipation:  $I_{CC} = 2\mu A$  (Max) at  $T_A = 25$ °C

- TTL-Compatible Inputs:  $V_{IL} = 0.8V$ ;  $V_{IH} = 2.0V$

- Power Down Protection Provided on Inputs

- Balanced Propagation Delays

- Designed for 2V to 5.5V Operating Range

- Low Noise:  $V_{OLP} = 0.8V$  (Max)

- Pin and Function Compatible with Other Standard Logic Families

- Latchup Performance Exceeds 300mA

- ESD Performance: HBM > 2000V; Machine Model > 200V

- Chip Complexity: 72 FETs or 18 Equivalent Gates

# MC74VHCT132A

**D SUFFIX** 14-LEAD SOIC PACKAGE CASE 751A-03

**DT SUFFIX** 14-LEAD TSSOP PACKAGE CASE 948G-01

M SUFFIX 14-LEAD SOIC EIAJ PACKAGE CASE 965-01

#### ORDERING INFORMATION

MC74VHCTXXAD SOIC

MC74VHCTXXADT TSSOP

MC74VHCTXXAM SOIC EIAJ

#### **FUNCTION TABLE**

| Inp | Output |   |

|-----|--------|---|

| Α   | Y      |   |

| L   | L      | Н |

| L   | Н      | Н |

| Н   | L      | Н |

| Н   | Н      | L |

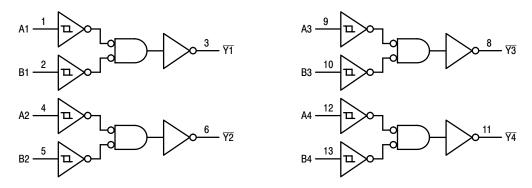

Figure 1. Logic Diagram

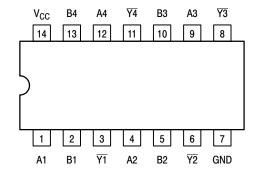

Figure 2. Pinout: 14-Lead Packages (Top View)

#### **MAXIMUM RATINGS\***

| Symbol           | Parameter                                 | Parameter                        |               |    |  |

|------------------|-------------------------------------------|----------------------------------|---------------|----|--|

| V <sub>CC</sub>  | DC Supply Voltage                         | - 0.5 to + 7.0                   | V             |    |  |

| V <sub>in</sub>  | DC Input Voltage                          | - 0.5 to + 7.0                   | V             |    |  |

| V <sub>out</sub> | DC Output Voltage                         | $-0.5$ to $V_{CC} + 0.5$         | V             |    |  |

| I <sub>IK</sub>  | Input Diode Current                       | - 20                             | mA            |    |  |

| I <sub>OK</sub>  | Output Diode Current                      |                                  | ± 20          | mA |  |

| l <sub>out</sub> | DC Output Current, per Pin                |                                  | ± 25          | mA |  |

| Icc              | DC Supply Current, V <sub>CC</sub> and GN | D Pins                           | ± 50          | mA |  |

| P <sub>D</sub>   | Power Dissipation in Still Air,           | SOIC Packages†<br>TSSOP Package† | 500<br>450    | mW |  |

| T <sub>stg</sub> | Storage Temperature                       |                                  | - 65 to + 150 | °C |  |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq$  ( $V_{in}$  or  $V_{out}$ )  $\leq$   $V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

†Derating — SOIC Packages: – 7 mW/°C from 65° to 125°C TSSOP Package: – 6.1 mW/°C from 65° to 125°C

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                                | Min  | Max             | Unit |

|------------------|------------------------------------------|------|-----------------|------|

| V <sub>CC</sub>  | DC Supply Voltage                        | 4.5  | 5.5             | V    |

| V <sub>in</sub>  | DC Input Voltage                         | 0    | 5.5             | V    |

| V <sub>out</sub> | DC Output Voltage                        | 0    | V <sub>CC</sub> | V    |

| T <sub>A</sub>   | Operating Temperature, All Package Types | - 40 | + 85            | °C   |

#### DC ELECTRICAL CHARACTERISTICS

|                  |                                                                 |                                                              | Vcc               | ٦                    | Γ <sub>A</sub> = 25°0 | A = 25°C T <sub>A</sub> ≤ |                      | $T_A \le 85^{\circ}C$ $T_A$ |                      | ≤ 125°C              |      |

|------------------|-----------------------------------------------------------------|--------------------------------------------------------------|-------------------|----------------------|-----------------------|---------------------------|----------------------|-----------------------------|----------------------|----------------------|------|

| Symbol           | Parameter                                                       | Test Conditions                                              | V                 | Min                  | Тур                   | Max                       | Min                  | Max                         | Min                  | Max                  | Unit |

| V <sub>T+</sub>  | Positive Threshold Voltage                                      |                                                              | 3.0<br>4.5<br>5.5 |                      |                       | 1.7<br>2.0<br>2.0         |                      | 1.6<br>2.0<br>2.0           |                      | 1.6<br>2.0<br>2.0    | V    |

| V <sub>T</sub> – | Negative Threshold Voltage                                      |                                                              | 3.0<br>4.5<br>6.0 | 0.35<br>0.5<br>0.6   |                       |                           | 0.35<br>0.5<br>0.6   |                             | 0.35<br>0.5<br>0.6   |                      | V    |

| V <sub>H</sub>   | Hysteresis Voltage                                              |                                                              | 3.0<br>4.5<br>5.5 | 0.30<br>0.40<br>0.50 |                       | 1.20<br>1.40<br>1.60      | 0.30<br>0.40<br>0.50 | 1.20<br>1.40<br>1.60        | 0.30<br>0.40<br>0.50 | 1.20<br>1.40<br>1.60 | V    |

| V <sub>OH</sub>  | Minimum High–Level<br>Output Voltage<br>I <sub>OH</sub> = –50μA | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$I_{OH} = -50 \mu A$ | 2.0<br>3.0<br>4.5 | 1.9<br>2.9<br>4.4    | 2.0<br>3.0<br>4.5     |                           | 1.9<br>2.9<br>4.4    |                             | 1.9<br>2.9<br>4.4    |                      | V    |

|                  |                                                                 | I <sub>OH</sub> = - 4mA<br>I <sub>OH</sub> = - 8mA           | 4.5<br>5.5        | 2.58<br>3.94         |                       |                           | 2.48<br>3.80         |                             | 2.34<br>3.66         |                      |      |

| V <sub>OL</sub>  | Maximum Low–Level<br>Output Voltage                             | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$I_{OL} = 50 \mu A$  | 2.0<br>3.0<br>4.5 |                      | 0.0<br>0.0<br>0.0     | 0.1<br>0.1<br>0.1         |                      | 0.1<br>0.1<br>0.1           |                      | 0.1<br>0.1<br>0.1    | V    |

|                  |                                                                 | $I_{OL} = 4mA$<br>$I_{OL} = 8mA$                             | 4.5<br>5.5        |                      |                       | 0.36<br>0.36              |                      | 0.44<br>0.44                |                      | 0.52<br>0.52         |      |

| I <sub>IN</sub>  | Maximum Input Leakage<br>Current                                | V <sub>IN</sub> = 5.5V or<br>GND                             | 0 to 5.5          |                      |                       | ± 0.1                     |                      | ± 1.0                       |                      | ± 1.0                | μА   |

| I <sub>CC</sub>  | Maximum Quiescent<br>Supply Current                             | $V_{IN} = V_{CC}$ or GND                                     | 5.5               |                      |                       | 2.0                       |                      | 20                          |                      | 40                   | μА   |

| Ісст             | Quiescent Supply Current                                        | Input: V <sub>IN</sub> = 3.4V                                | 5.5               |                      |                       | 1.35                      |                      | 1.50                        |                      | 1.65                 | mA   |

| I <sub>OPD</sub> | Output Leakage Current                                          | V <sub>OUT</sub> = 5.5V                                      | 0.0               |                      |                       | 0.5                       |                      | 5.0                         |                      | 10                   | μΑ   |

<sup>\*</sup> Absolute maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute—maximum—rated conditions is not implied.

## AC ELECTRICAL CHARACTERISTICS (Input $t_r = t_f = 3.0$ ns)

|                                        |                                                     |                                                                                 | 7   | T <sub>A</sub> = 25°C |              | T <sub>A</sub> = - |              | <b>T</b> <sub>A</sub> ≤ 1 | 125°C        |      |

|----------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|-----|-----------------------|--------------|--------------------|--------------|---------------------------|--------------|------|

| Symbol                                 | Parameter                                           | Test Conditions                                                                 | Min | Тур                   | Max          | Min                | Max          | Min                       | Max          | Unit |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Maximum Propagation Delay, A or B to $\overline{Y}$ | $V_{CC} = 3.3 \pm 0.3 \text{ V C}_{L} = 15 \text{pF}$<br>$C_{L} = 50 \text{pF}$ |     | 7.6<br>10.1           | 11.9<br>15.4 | 1.0<br>1.0         | 14.0<br>17.5 |                           | 16.5<br>20.0 | ns   |

|                                        |                                                     | $V_{CC} = 5.0 \pm 0.5 \text{ V C}_{L} = 15 \text{pF}$ $C_{L} = 50 \text{pF}$    |     | 4.9<br>6.4            | 7.7<br>9.7   | 1.0<br>1.0         | 9.0<br>11.0  |                           | 11.0<br>13.0 |      |

| C <sub>in</sub>                        | Maximum Input<br>Capacitance                        |                                                                                 |     | 4                     | 10           |                    | 10           |                           | 10           | pF   |

|          |                                         | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |    |

|----------|-----------------------------------------|-----------------------------------------|----|

| $C_{PD}$ | Power Dissipation Capacitance (Note 1.) | 16                                      | pF |

C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation: I<sub>CC(OPR)</sub> = C<sub>PD</sub> • V<sub>CC</sub> • f<sub>in</sub> + I<sub>CC</sub>/4 (per gate). C<sub>PD</sub> is used to determine the no–load dynamic power consumption; P<sub>D</sub> = C<sub>PD</sub> • V<sub>CC</sub><sup>2</sup> • f<sub>in</sub> + I<sub>CC</sub> • V<sub>CC</sub>.

## NOISE CHARACTERISTICS (Input $t_{r} = t_{f} = 3.0 \text{ns}, C_{L} = 50 \text{pF}, V_{CC} = 5.0 \text{ V})$

|                  |                                              | T <sub>A</sub> = 25°C |       |      |

|------------------|----------------------------------------------|-----------------------|-------|------|

| Symbol           | Characteristic                               | Тур                   | Max   | Unit |

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> | 0.3                   | 0.8   | V    |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub> | - 0.3                 | - 0.8 | V    |

| V <sub>IHD</sub> | Minimum High Level Dynamic Input Voltage     |                       | 3.5   | V    |

| $V_{ILD}$        | Maximum Low Level Dynamic Input Voltage      |                       | 1.5   | V    |

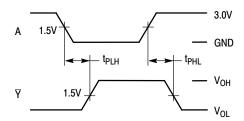

Figure 3. Switching Waveforms

\*Includes all probe and jig capacitance

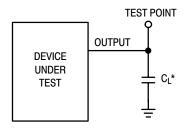

Figure 4. Test Circuit

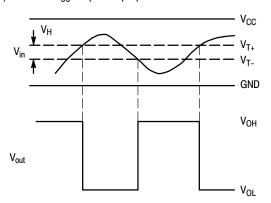

## (a) A Schmitt-Trigger Squares Up Inputs With Slow Rise and Fall Times

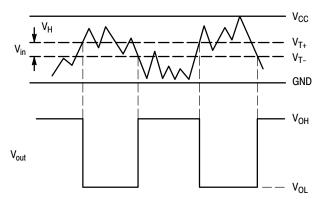

#### (b) A Schmitt-Trigger Offers Maximum Noise Immunity

Figure 5. Typical Schmitt-Trigger Applications

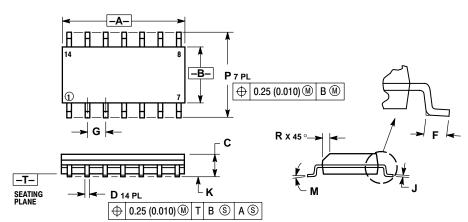

#### **OUTLINE DIMENSIONS**

**D SUFFIX** SOIC-14 CASE 751A-03 **ISSUE F**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIM | MIN    | MAX    | MIN   | MAX   |

| Α   | 8.55   | 8.75   | 0.337 | 0.344 |

| В   | 3.80   | 4.00   | 0.150 | 0.157 |

| С   | 1.35   | 1.75   | 0.054 | 0.068 |

| D   | 0.35   | 0.49   | 0.014 | 0.019 |

| F   | 0.40   | 1.25   | 0.016 | 0.049 |

| G   | 1.27   | BSC    | 0.050 | BSC   |

| J   | 0.19   | 0.25   | 0.008 | 0.009 |

| K   | 0.10   | 0.25   | 0.004 | 0.009 |

| M   | 0 °    | 7°     | 0 °   | 7°    |

| P   | 5.80   | 6.20   | 0.228 | 0.244 |

| R   | 0.25   | 0.50   | 0.010 | 0.019 |

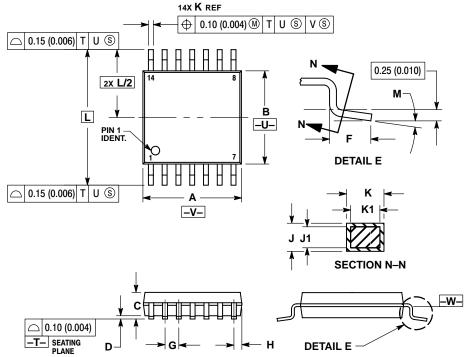

#### **OUTLINE DIMENSIONS**

#### **DT SUFFIX TSSOP** CASE 948G-01 **ISSUE 0**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

- DIMENSIONING AND TOLERANDING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15

- OR GATE BURRS SHALL NOT EXCEED 0.15

(0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD

FLASH OR PROTRUSION. INTERLEAD FLASH OR

PROTRUSION SHALL NOT EXCEED

0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.08 (0.03) TOTAL IN

EXCESS OF THE K DIMENSION AT MAXIMUM

MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR

REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE DETERMINED

AT DATUM PLANE-W-

|     | MILLIN   | IETERS | INCHES    |       |  |  |

|-----|----------|--------|-----------|-------|--|--|

| DIM | MIN      | MAX    | MIN       | MAX   |  |  |

| Α   | 4.90     | 5.10   | 0.193     | 0.200 |  |  |

| В   | 4.30     | 4.50   | 0.169     | 0.177 |  |  |

| С   |          | 1.20   |           | 0.047 |  |  |

| D   | 0.05     | 0.15   | 0.002     | 0.006 |  |  |

| F   | 0.50     | 0.75   | 0.020     | 0.030 |  |  |

| G   | 0.65 BSC |        | 0.026     | BSC   |  |  |

| Н   | 0.50     | 0.60   | 0.020     | 0.024 |  |  |

| J   | 0.09     | 0.20   | 0.004     | 0.008 |  |  |

| J1  | 0.09     | 0.16   | 0.004     | 0.006 |  |  |

| K   | 0.19     | 0.30   | 0.007     | 0.012 |  |  |

| K1  | 0.19     | 0.25   | 0.007     | 0.010 |  |  |

| L   | 6.40     |        | 0.252 BSC |       |  |  |

| M   | 0°       | 8°     | 0°        | 8°    |  |  |

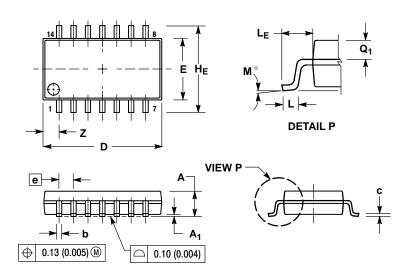

#### **OUTLINE DIMENSIONS**

**M SUFFIX** SO-14 **CASE 965-01 ISSUE 0**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTR

- PROTRUSIONS SHALL NOT EXCEED 0.15 (0.006)

PER SIDE.

1 TERMINAL NUMBERS ARE SHOWN FOR

REFERENCE ONLY.

5. THE LEAD WIDTH DIMENSION (b) DOES NOT

INCLUDE DAMBAR PROTRUSION. ALLOWABLE

DAMBAR PROTRUSION SHALL BE 0.08 (0.003)

TOTAL IN EXCESS OF THE LEAD WIDTH

DIMENSION AT MAXIMUM MATERIAL CONDITION.

DAMBAR CANNOT BE LOCATED ON THE LOWER

RADIUS OR THE FOOT. MINIMUM SPACE

BETWEEN PROTRUSIONS AND ADJACENT LEAD

TO BE 0.46 (0.018). TO BE 0.46 ( 0.018).

|                | MILLIN | IETERS | INC   | HES   |

|----------------|--------|--------|-------|-------|

| DIM            | MIN    | MAX    | MIN   | MAX   |

| Α              |        | 2.05   |       | 0.081 |

| A <sub>1</sub> | 0.05   | 0.20   | 0.002 | 0.008 |

| b              | 0.35   | 0.50   | 0.014 | 0.020 |

| C              | 0.18   | 0.27   | 0.007 | 0.011 |

| D              | 9.90   | 10.50  | 0.390 | 0.413 |

| E              | 5.10   | 5.45   | 0.201 | 0.215 |

| е              | 1.27   | BSC    | 0.050 | BSC   |

| HE             | 7.40   | 8.20   | 0.291 | 0.323 |

| 0.50           | 0.50   | 0.85   | 0.020 | 0.033 |

| LE             | 1.10   | 1.50   | 0.043 | 0.059 |

| M              | 0 °    | 10 °   | 0 °   | 10 °  |

| $Q_1$          | 0.70   | 0.90   | 0.028 | 0.035 |

| Z              |        | 1.42   |       | 0.056 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**EUROPE:** LDC for ON Semiconductor – European Support

German Phone: (+1) 303–308–7140 (Mon–Fri 2:30pm to 7:00pm CET)

Email: ONlit-german@hibbertco.com

French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (Mon–Fri 12:00pm to 5:00pm GMT)

Email: ONlit@hibbertco.com

EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

Toll-Free from Mexico: Dial 01-800-288-2872 for Access -

then Dial 866-297-9322

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

Phone: 1-303-675-2121 (Tue-Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center

4-32-1 Nishi-Gotanda, Shinagawa-ku, Tokyo, Japan 141-0031

Phone: 81–3–5740–2700

Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.