Application Note August 2002 AN1032

## Introduction

Analog input signals which originate externally to a system can be destructive to a multiplexer for several reasons:

- Analog signals may be present while the MUX power supplies are off.

- 2. The signal lines may receive induced voltage spikes from nearby sources.

- Static electricity may be introduced on the signal lines by personnel or equipment.

- Grounding problems are frequent; AC power line voltages at high impedance can appear on the signal lines. Signal lines can be accidentally shorted to other voltage sources.

Each of these situations are common in data acquisition, telemetry, and process control systems. In each case, a voltage at the multiplexer input exceeds the rail voltage. Without current limiting, this voltage will degrade or destroy the device.

## **Protection Methods**

Any conventional CMOS multiplexer can be protected against overvoltage destruction by external resistor- diode networks which limit input current to a safe level. Such networks are expensive, however, both in cost and in circuit board space. Another drawback is the output signal corruption that accompanies an overvoltage - regardless of which input is selected. This occurs due to parasitic bipolar transistors within the multiplexer which turn on during overvoltage.

A few multiplexers feature built-in overvoltage protection, designed to eliminate the external networks. The protection capability varies widely among these devices, however. Some offer very slight advantages over ordinary multiplexers while others withstand wide voltage extremes. Unfortunately, nearly all suffer from the same output signal corruption problem described above.

Intersil overvoltage protected multiplexers, HI-506A/507A/ 508A/509A/546/547/548/549, are exceptions to this rule. During overvoltage, active protection circuitry automatically shuts off the parasitic transistor, thereby preventing output signal corruption. These devices will withstand a continuous voltage on any one input of  $\pm 20$  Volts greater than either supply (this limitation is due only to temperature rise considerations at maximum ambient) and have withstood simulated static discharge conditions of greater than 4,500 Volts.

It should be emphasized that only the HI-506A through 509A, and HI-0546 through HI-0549, (and exact equivalents from authorized alternate suppliers) will have this kind of protection necessary for inputs from the outside world. Certain CMOS process improvements, such as "floating body" and "buried layer" do help minimize one failure mode (latchup) but will still fail under excess voltage or current conditions prevalent in this type application.

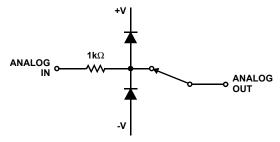

A simplified equivalent circuit of the internal protection network is shown in Figure 1.

FIGURE 1. SIMPLE EQUIVALENT CIRCUIT OF THE INTERNAL PROTECTION NETWORK

This will help answer the question of what happens when the supplies are turned off, but input signals are present. If the supplies are shorted to ground, then the inputs will have about  ${\rm lk}\Omega$  impedance to ground. If the supplies are open circuit, then the most positive and most negative inputs will act as supplies to the multiplexer.

Under normal operating conditions, internally protected multiplexers have one difference from the unprotected versions - ON resistance is necessarily higher because of the added series current limiting resistor. However, to achieve the same degree of protection with conventional devices, the same resistance must be added externally, plus external diodes which would add to the effective leakage currents.

Conventional unprotected multiplexers are suitable for systems where the MUX inputs come from sources within the equipment, such as from op amps powered by the same ±15 volt supplies. The HI-506/507/1818A/1828Aare intended for this type system. They are entirely free of any latch-up tendency, which have plagued some other types, even in these more benign applications. They are also free of the performance compromises which have accompanied some attempts to cure the latch-up problem.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com