S3C72K8/P72K8 PRODUCT OVERVIEW

1

# **PRODUCT OVERVIEW**

#### **OVERVIEW**

The S3C72K8 singl-chip CMOS microcontroller has been designed for high performance using Samsung's newest 4-bit CPU core, SAM48 (Samsung Arrageable Microcontrollers). With a two-channel comparator, up-to-320-dot LCD direct drive capability, 8-bit timer/counter, watchdog timer and serial I/O, the S3C72K8 offers an excellent design solution for a wide variety of applications which require LCD functions.

Up to 27 pins of the 80-pin QFP package can be dedicated to I/O. Seven vectored interrupts provide fast response to internal and external events. In addition, the S3C72K8's advanced CMOS technology provides for low power consumption and a wide operating voltage range.

#### **OTP**

The S3C72K8 microcontroller is also available is OTP (one time programmable) version, S3P72K8. S3P72K8 microcontroller has an one-chop 8 Kbyte one time programmable EPROM instead of masked ROM. The S3P72K8 is comparable to S3C72K8, both in function and in pin configuration.

PRODUCT OVERVIEW S3C72K8/P72K8

#### **FEATURES**

#### **Memory**

- 8 K × 8-bit RAM

- 1.024 × 4-bit ROM

#### 27 I/O Pins

- Input only: 4 pins

- I/O: 15 pins

- Output: maximum 8 pins for 1-bit level output (sharing with segment driver outputs)

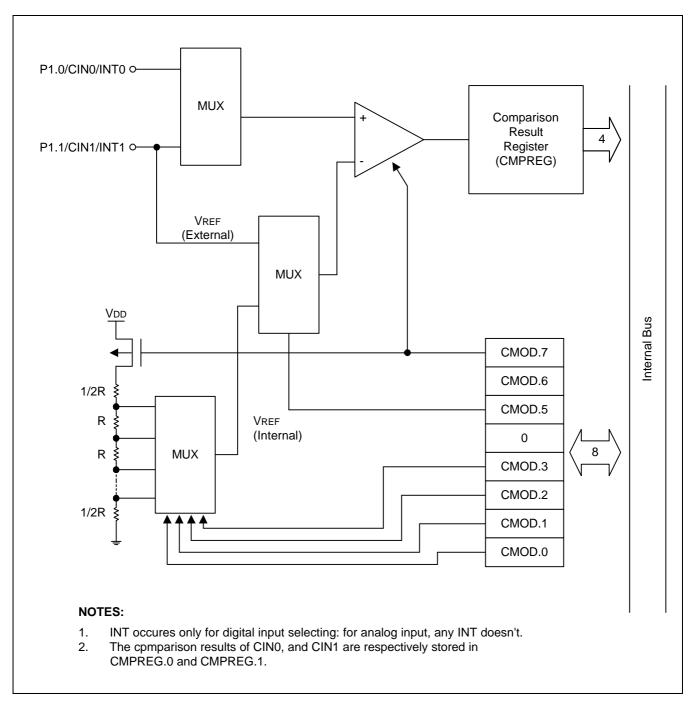

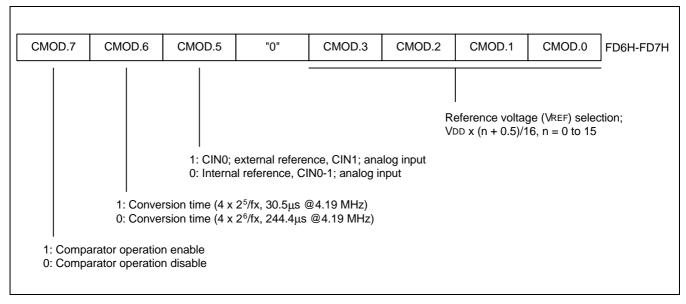

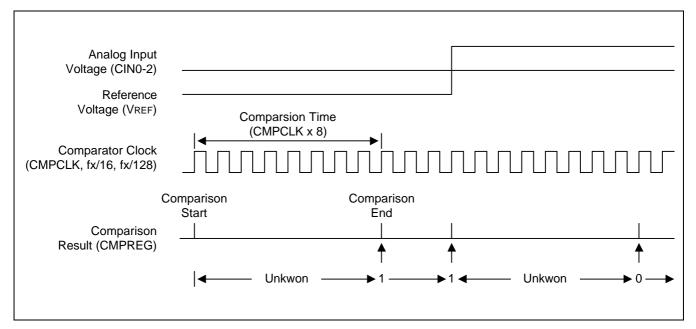

## Comparator

- Two channel mode: internal reference (4-bit resolution)

- One channel mode: external reference

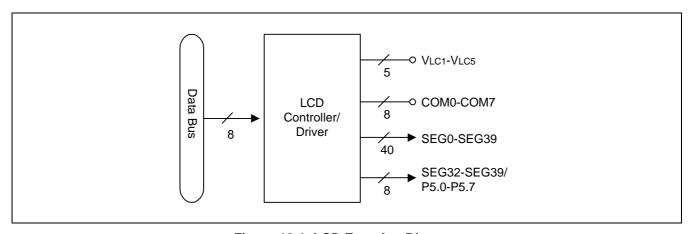

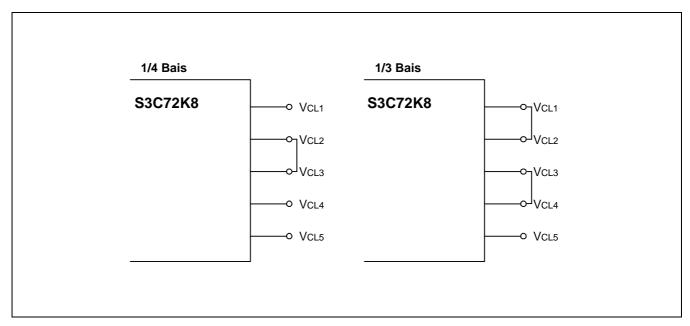

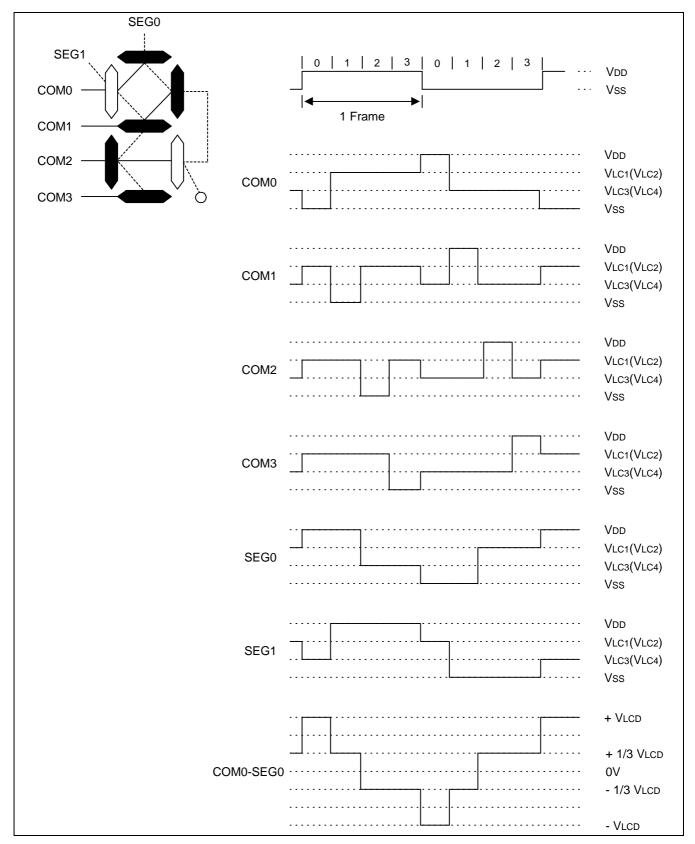

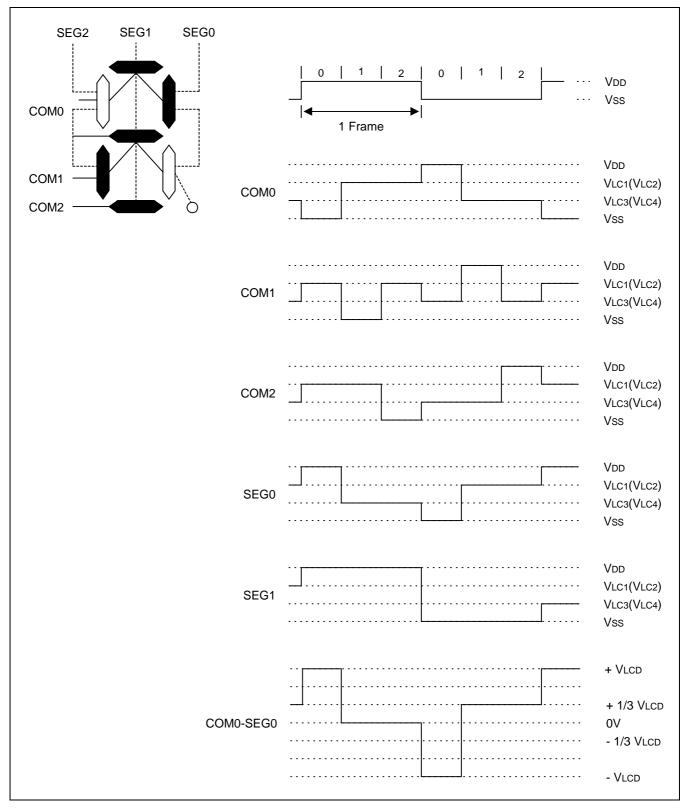

#### LCD Controller/Driver

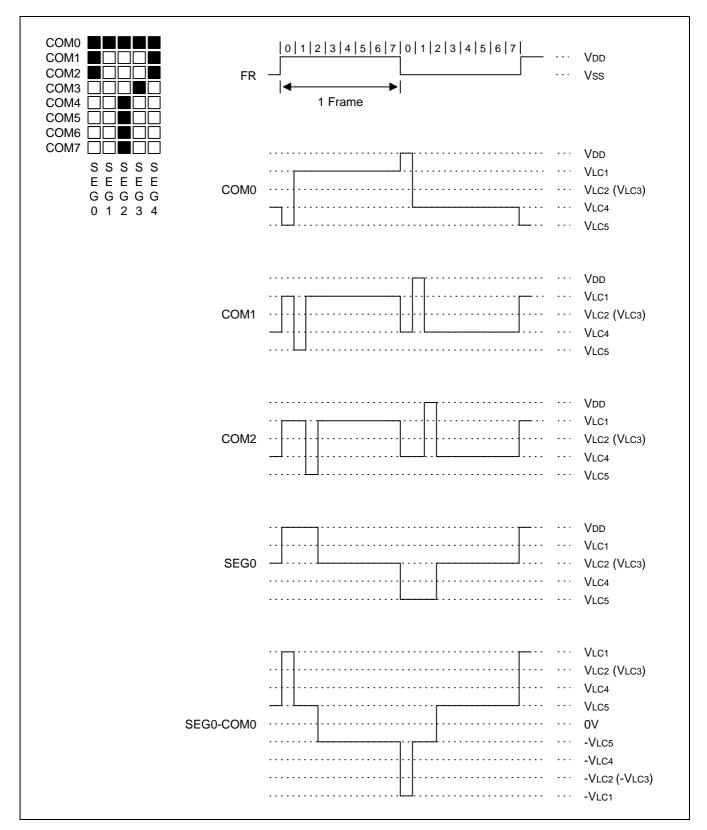

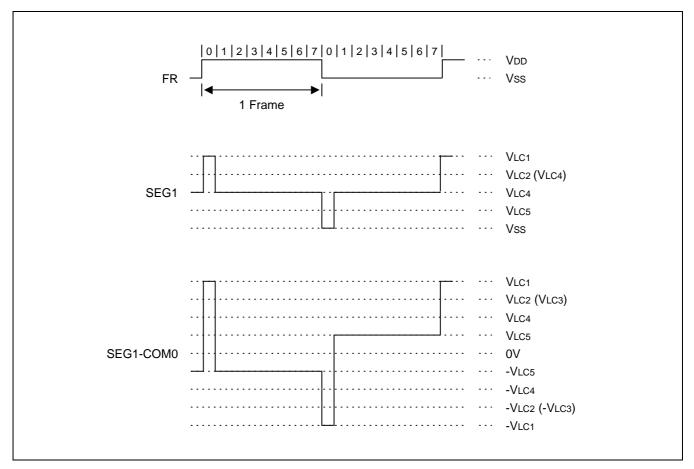

- 40 segments and 8 common terminals

- 3, 4 and 8 common selectable

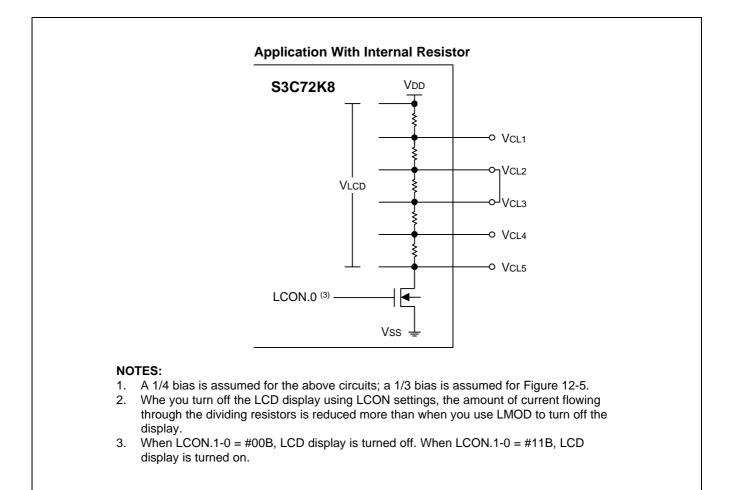

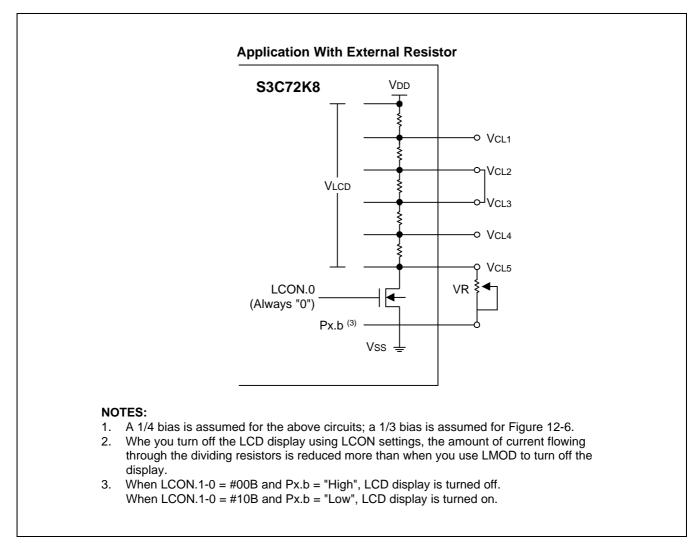

- Internal resistor circuit for LCD bias

- All dot can be switched on/off

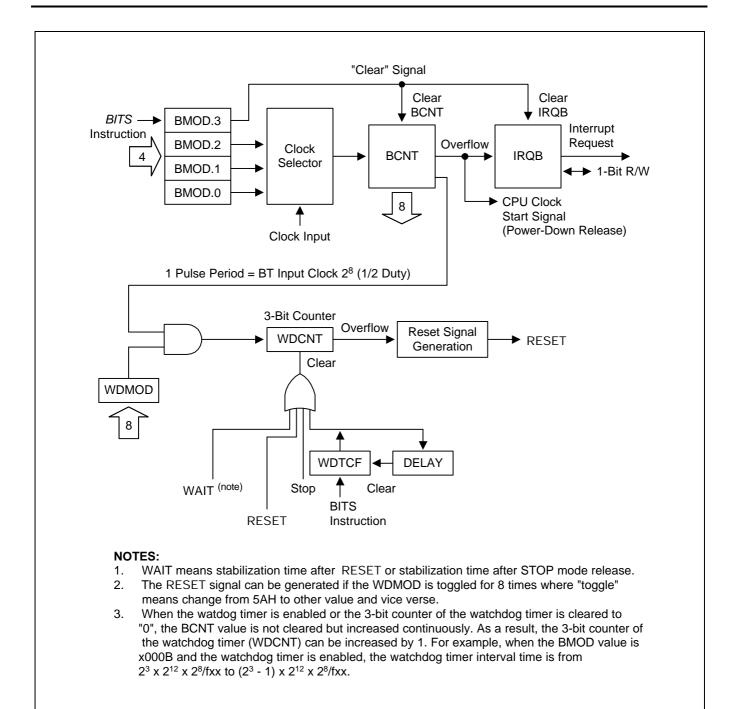

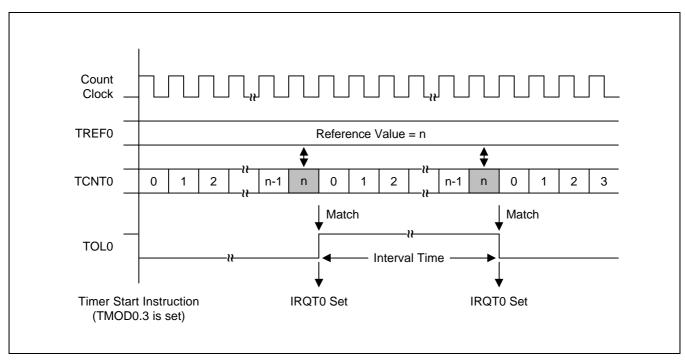

#### **8-Bit Basic Timer**

- 4 interval timer functions

- Watchdog timer

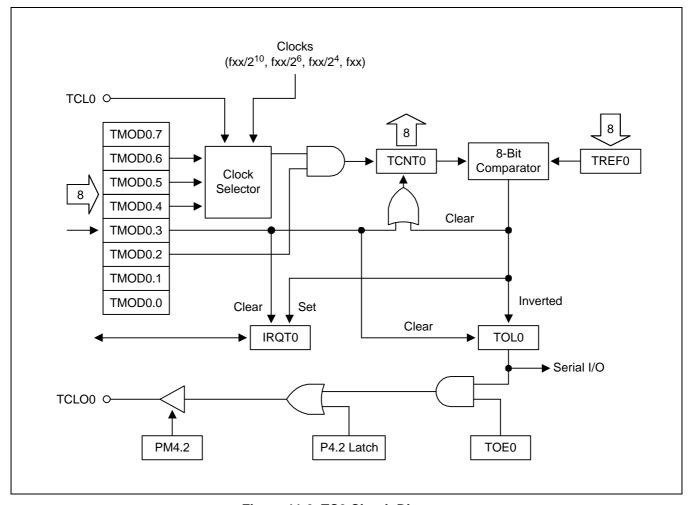

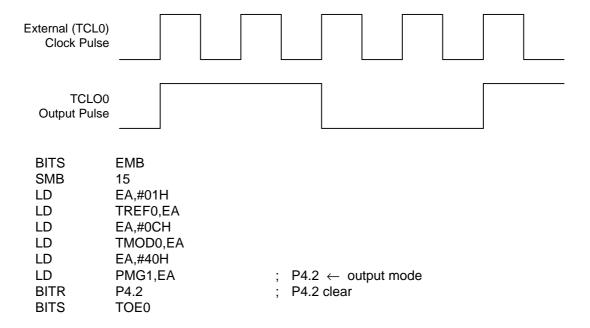

#### 8-Bit Timer/Counter

- Programmable 8-bit timer

- External event counter

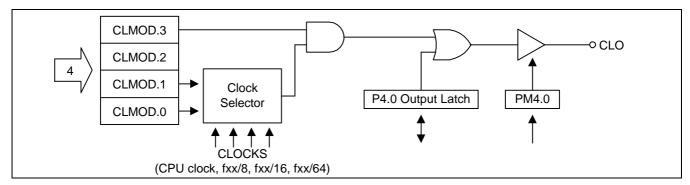

- Arbitrary clock frequency output

- External clock signal divider

- Serial I/O interface clock generator

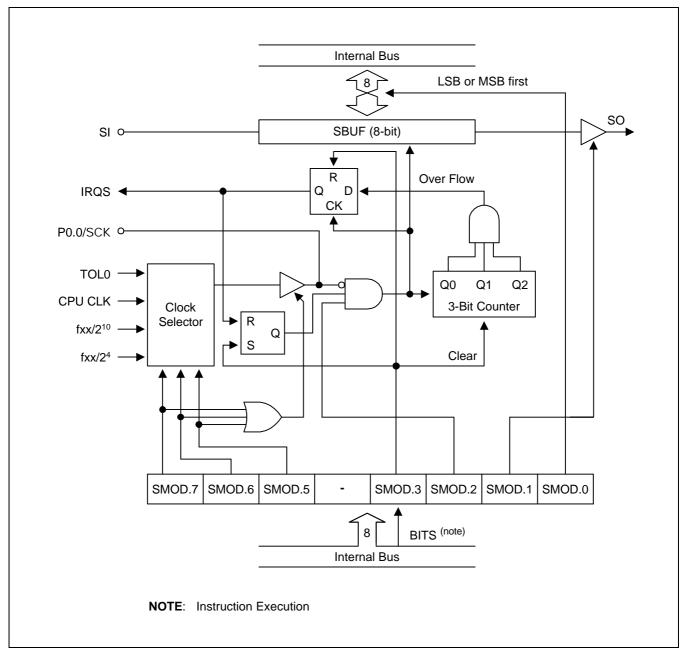

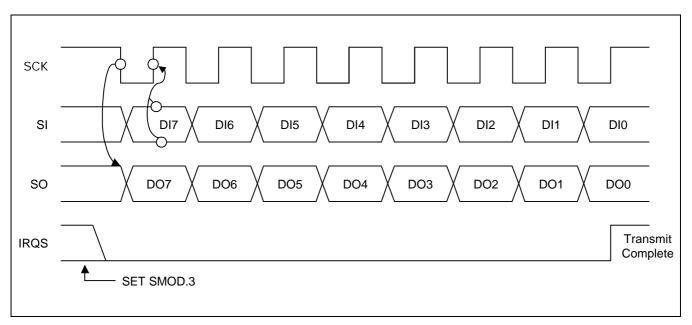

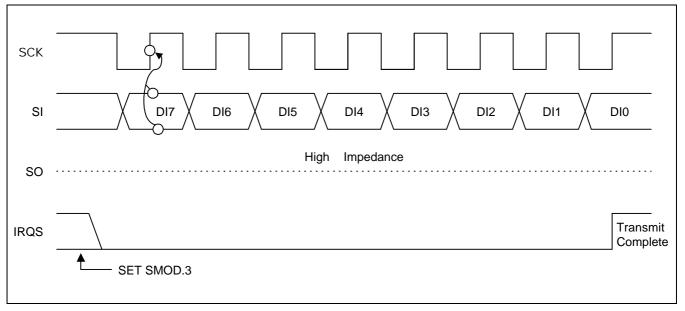

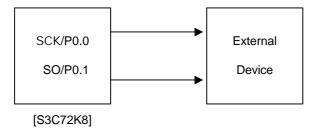

## 8-Bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive only mode

- LSB-first or MSB-first transmission selectable

- Internal or external clock source

#### **Bit Sequential Carrier**

Support 16-bit serial data transfer in arbitrary format

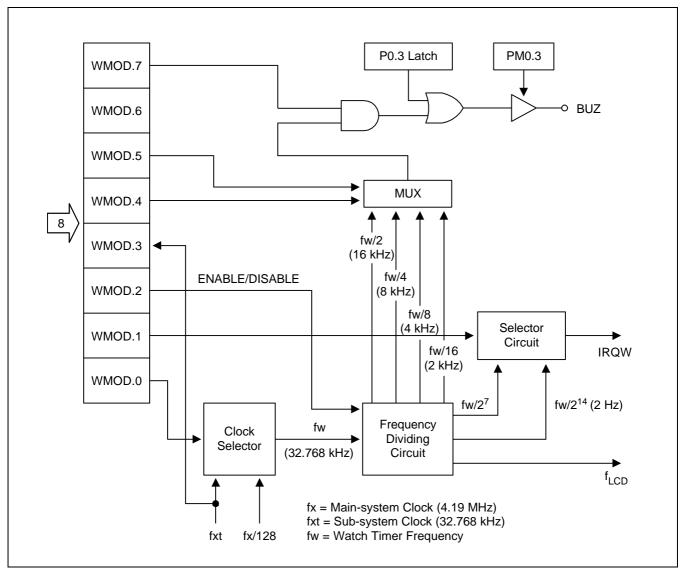

#### **Watch Timer**

- Timer interval generation:

0.5 s, 3.9 ms at 32,768 Hz

- Four frequency outputs to BUZ pin

- Clock source generation for LCD

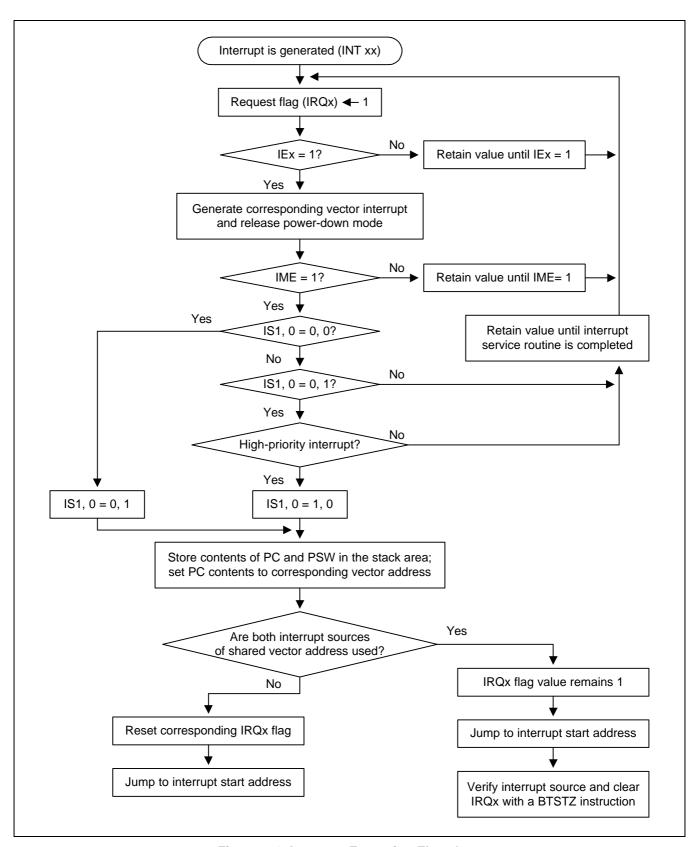

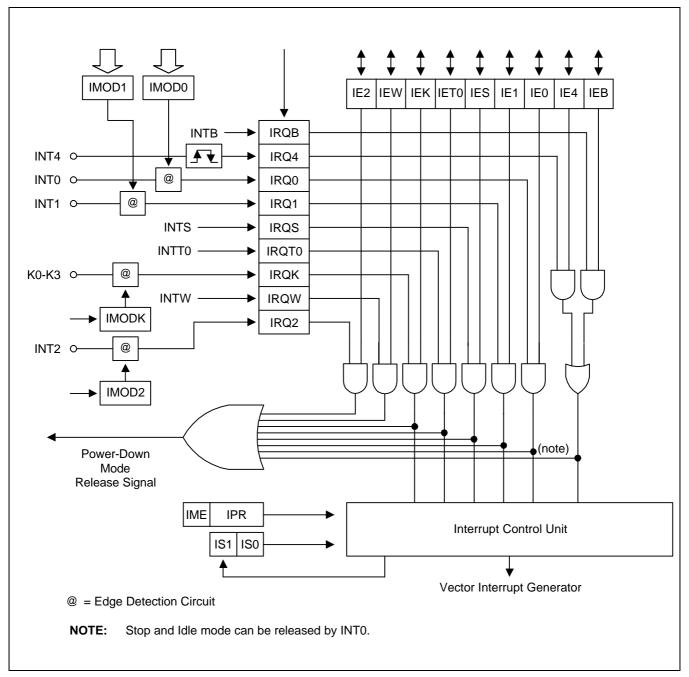

#### Interrupts

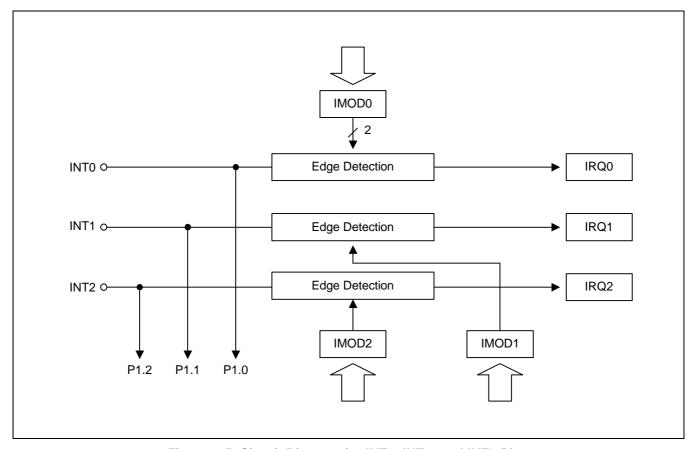

- Three internal vectored interrupts: INTB, INTTO, INTS

- Four external vectored interrupts: INT0, INT1, INT4, INTK

- Two quasi-interrupts: INT2, INTW

## Memory-Mapped I/O Structure

Data memory bank 15

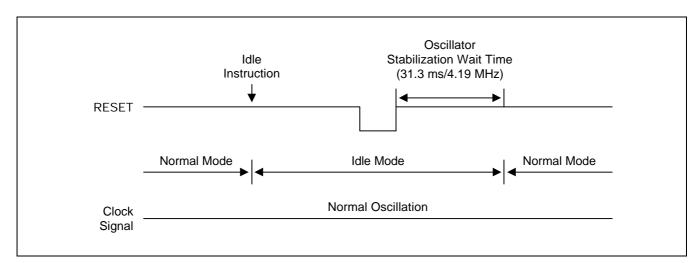

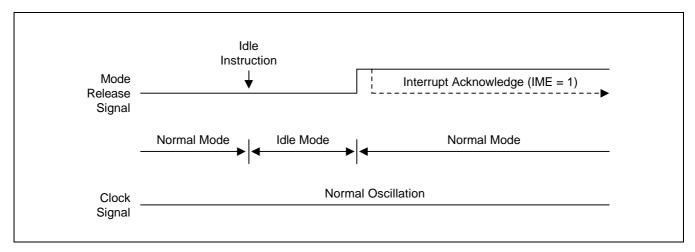

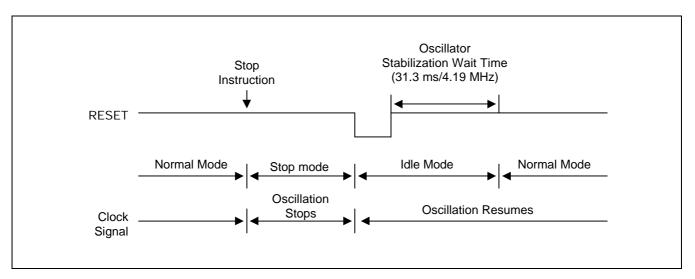

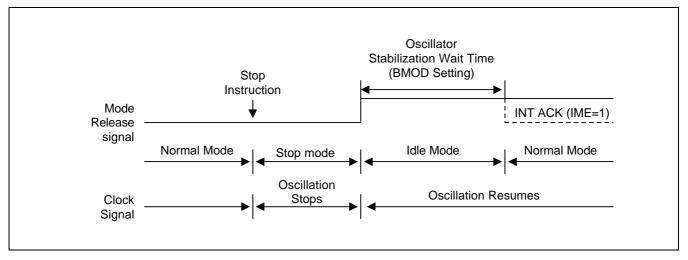

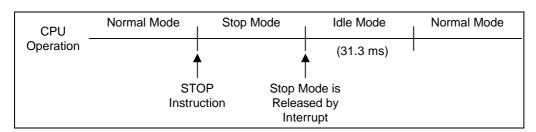

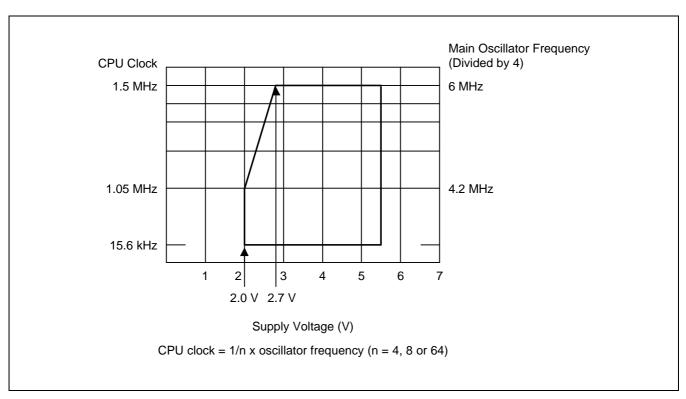

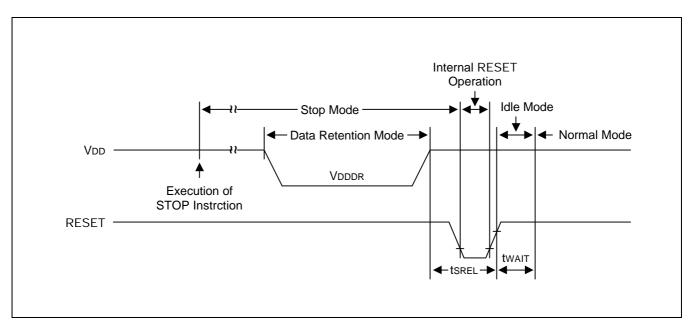

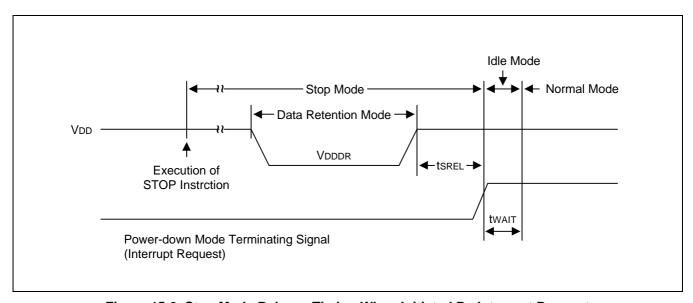

#### **Two Power-Down Modes**

- Idle mode (only CPU clock stops)

- Stop mode (main system oscillation stops)

- Subsystem clock stop mode

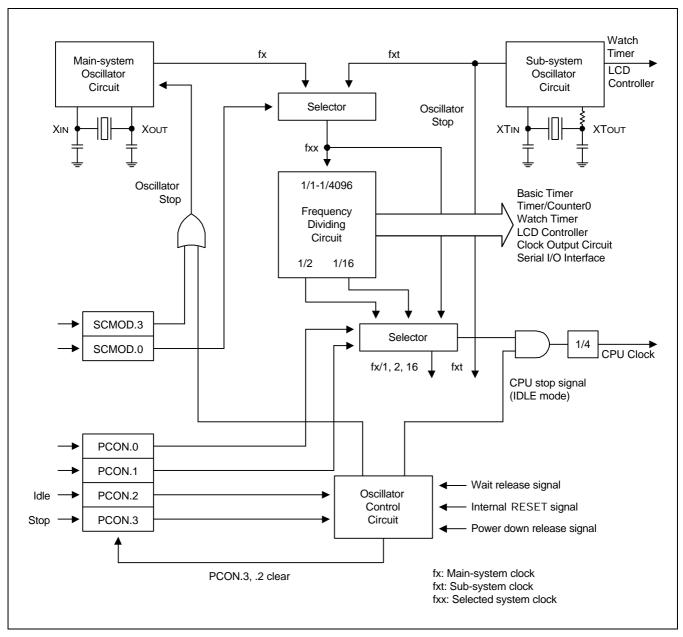

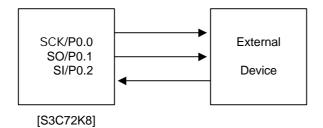

## **Oscillation Sources**

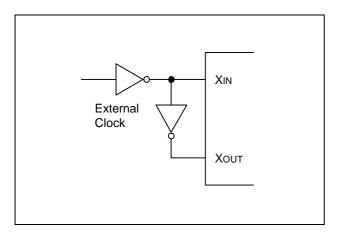

- Crystal, ceramic, or External RC for system clock

- Main system clock frequency: 0.4 MHz–6 MHz

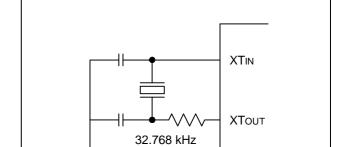

- Subsystem clock frequency: 32,768 kHz

- CPU clock divider circuit (by 4, 8, or 64)

## **Instruction Execution Times**

- 0.67 us at 6 MHz (minimum)

- 0.95 μs at 4.19 MHz (minimum)

- 122 μs at 32,768 kHz (minimum)

#### **Operating Temperature**

- -40 °C to 85 °C

## **Operating Voltage Range**

— 2.0 V to 5.5 V

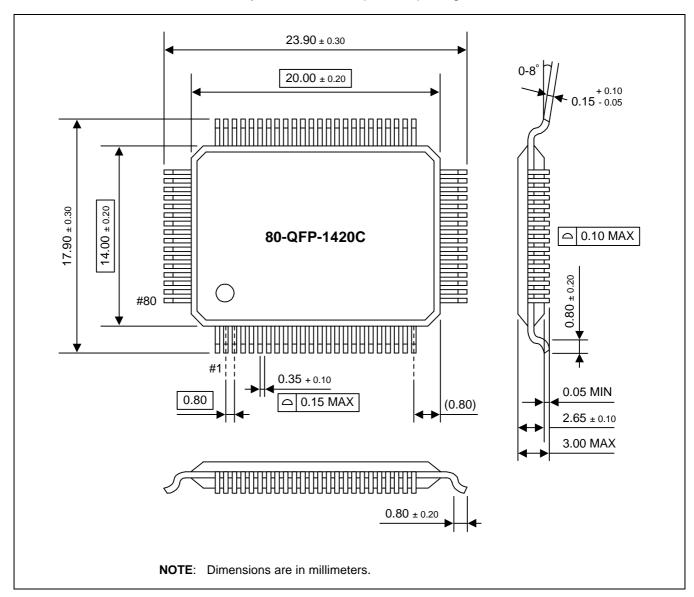

# Package Type

- 80-pin QFP

S3C72K8/P72K8 PRODUCT OVERVIEW

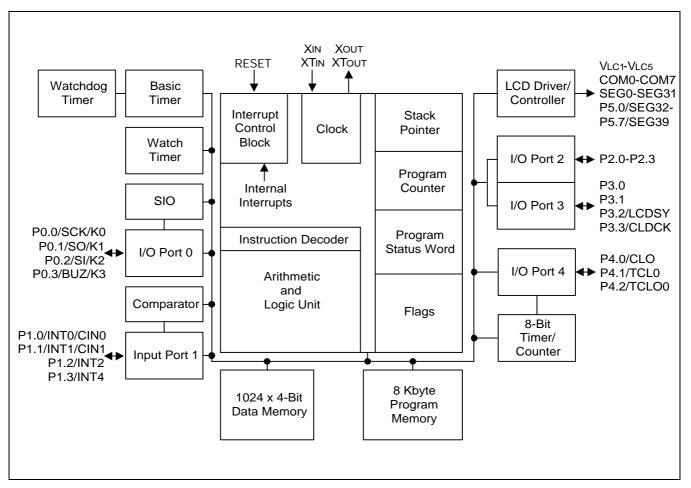

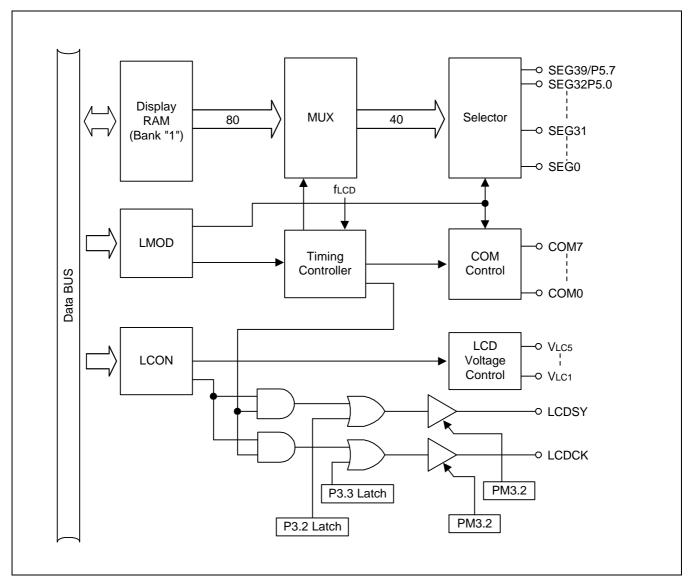

## **BLOCK DIAGRAM**

Figure 1-1. S3C72K8 Simplified Block Diagram

PRODUCT OVERVIEW S3C72K8/P72K8

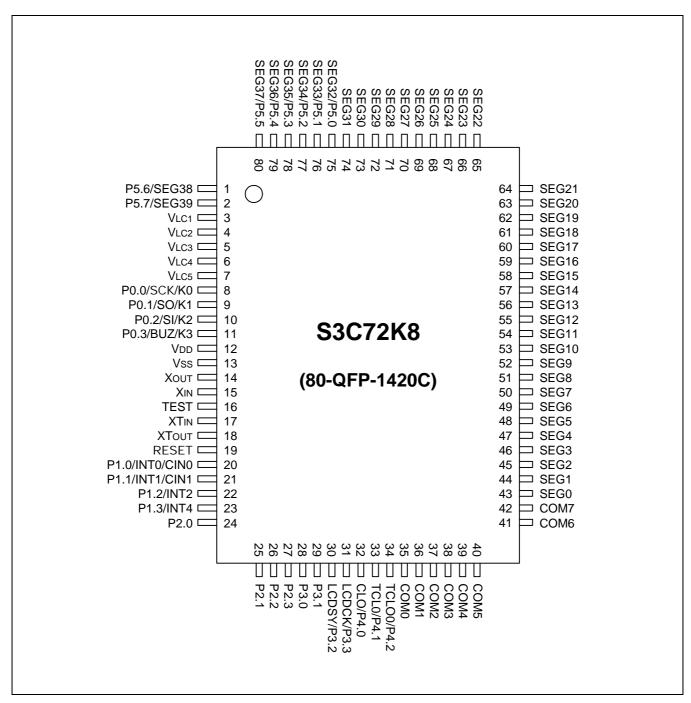

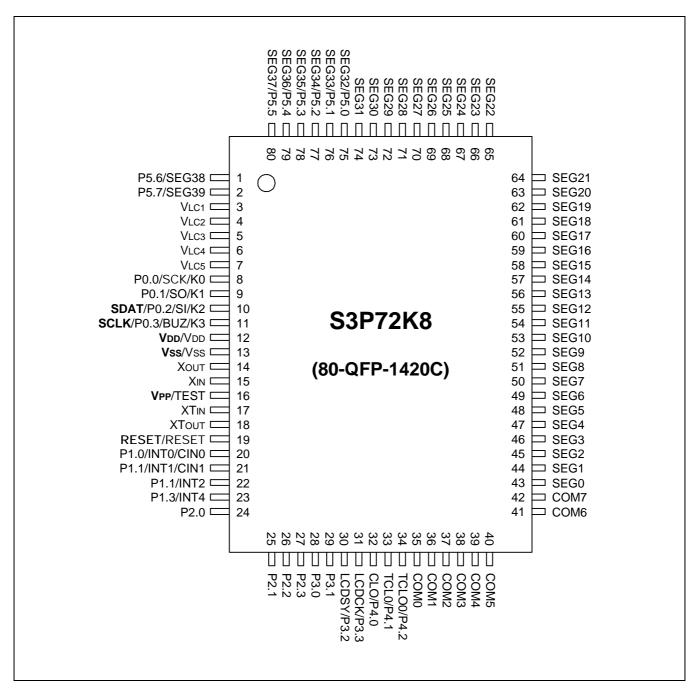

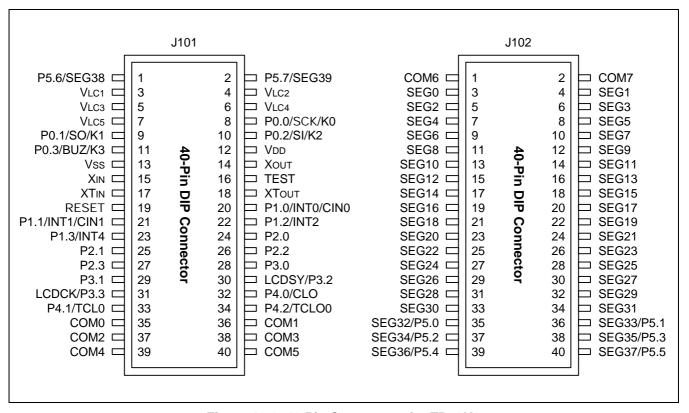

#### PIN ASSIGNMENTS

Figure 1-2. S3C72K8 80-QFP Pin Assignment

S3C72K8/P72K8 PRODUCT OVERVIEW

# **PIN DESCRIPTIONS**

Table 1-1. S3C72K8 Pin Descriptions

| Pin Name                     | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                              | Circuit<br>Type          | Pin<br>Number        | Share Pin                              |

|------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|----------------------------------------|

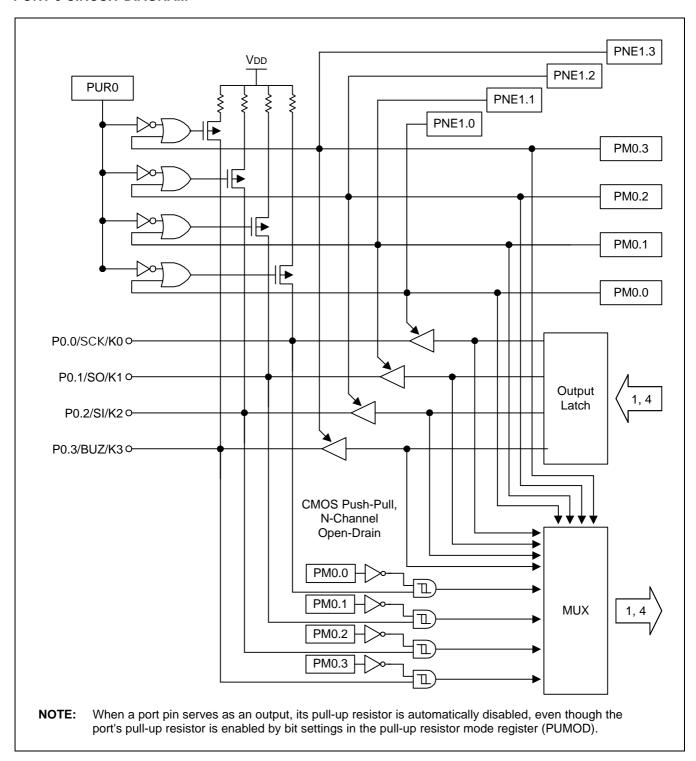

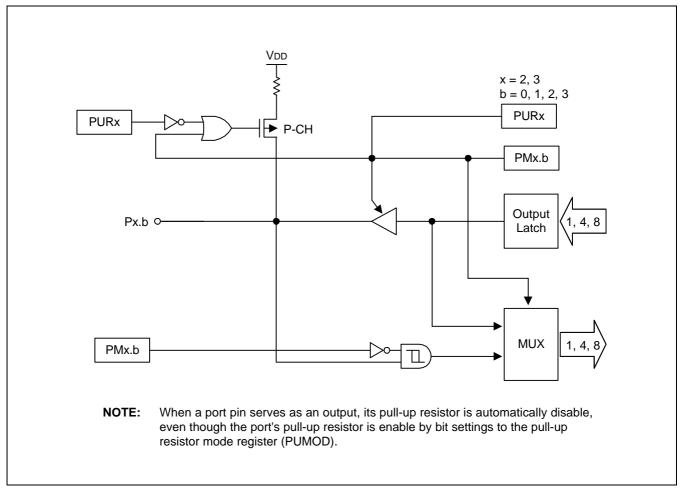

| P0.0<br>P0.1<br>P0.2<br>P0.3 | I/O         | 4-bit I/O port. 1-bit or 4-bit read/write and test is possible. Individual pins are software configurable as input or output. Individual pins are software configurable as opendrain or push-pull output. 4-bit pull-up resistors are software assignable; pull-up resistors are automatically disabled for output pins. | E-2                      | 8<br>9<br>10<br>11   | K0/SCK<br>K1/SO<br>K2/SI<br>K3/BUZ     |

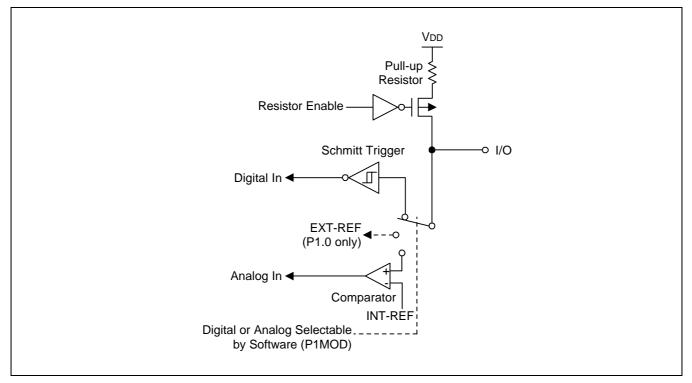

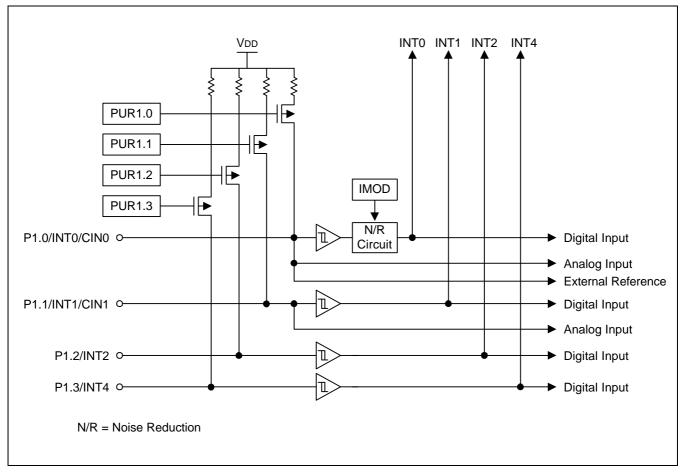

| P1.0<br>P1.1<br>P1.2<br>P1.3 | I           | 4-bit input port. 1-bit or 4-bit read and test are possible. The 1-bit unit pull-up resistors are assigned to input pins by software. An interrupt is generated by digital input at P1.0, P1.1.                                                                                                                          | F–4<br>F–4<br>A–3<br>A–3 | 20<br>21<br>22<br>23 | INTO/CINO<br>INT1/CIN1<br>INT2<br>INT4 |

| P2.0-P2.3                    | I/O         | Same as port 0 except that 8-bit read/write and test is possible.                                                                                                                                                                                                                                                        | E-2                      | 24–27                | _                                      |

| P3.0<br>P3.1<br>P3.2<br>P3.3 |             |                                                                                                                                                                                                                                                                                                                          |                          | 28<br>29<br>30<br>31 | -<br>LCDSY<br>LCDCK                    |

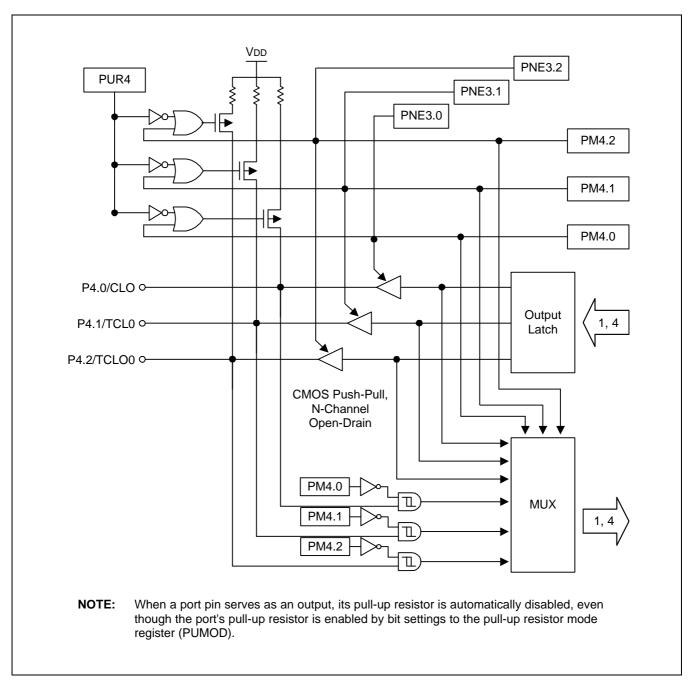

| P4.0<br>P4.1<br>P4.2         | I/O         | Same as port 0 except that port 4 is 3-bit I/O port.                                                                                                                                                                                                                                                                     | E-2                      | 32<br>33<br>34       | CLO<br>TCL0<br>TCLO0                   |

| P5.0-P5.7                    | 0           | Output port for 1-bit data                                                                                                                                                                                                                                                                                               | H–11                     | 75–<br>80,1,2        | SEG32-<br>SEG39                        |

| SCK                          | I/O         | Serial I/O interface clock signal                                                                                                                                                                                                                                                                                        | E-2                      | 8                    | P0.0/K0                                |

| SO                           | I/O         | Serial data output                                                                                                                                                                                                                                                                                                       | E-2                      | 9                    | P0.1/K1                                |

| SI                           | I/O         | Serial data input                                                                                                                                                                                                                                                                                                        | E-2                      | 10                   | P0.2/K2                                |

| BUZ                          | I/O         | 2 KHz, 4 KHz, 8 KHz or 16 KHz frequency output at the watch timer clock frequency of 32.768 kHz.                                                                                                                                                                                                                         | E-2                      | 11                   | P0.3/K3                                |

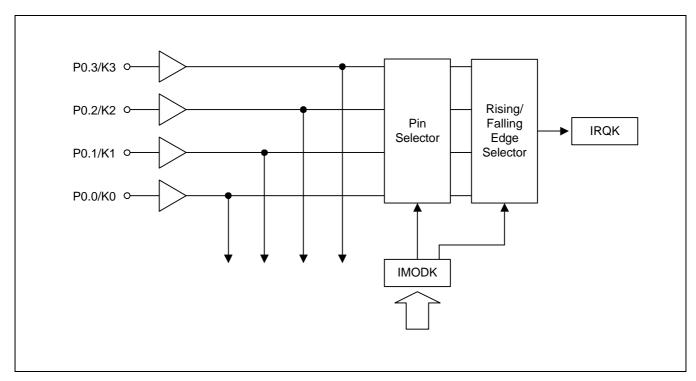

| K0-K3                        | I/O         | External interrupt. The triggering edge is selectable.                                                                                                                                                                                                                                                                   | E-2                      | 8–11                 | P0.0-P0.3                              |

| INT0<br>INT1                 | I           | External interrupts. The triggering edge for INT0 and INT1 is selectable.                                                                                                                                                                                                                                                | F–4                      | 20<br>21             | P1.0/CIN0<br>P1.1/CIN1                 |

| INT2                         | I           | Quasi-interrupt with detection of rising or falling edges                                                                                                                                                                                                                                                                | A–3                      | 22                   | P1.2                                   |

| INT4                         | I           | External interrupts with detection of rising and falling edges                                                                                                                                                                                                                                                           | A–3                      | 23                   | P1.3                                   |

PRODUCT OVERVIEW S3C72K8/P72K8

Table 1-1. S3C72K8 Pin Descriptions (Continued)

| Pin Name                               | Pin<br>Type | Description                                                                                                 | Circuit<br>Type | Pin<br>Number | Share Pin              |

|----------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------|-----------------|---------------|------------------------|

| CIN0<br>CIN1                           | I           | 2-channel comparator input. CIN0: comparator input or external reference input CIN1: comparator input only. | F-4             | 20<br>21      | P1.0/INT0<br>P1.1/INT1 |

| LCDSY                                  | I/O         | LCD synchronization clock output for display expansion                                                      | E-2             | 30            | P3.2                   |

| LCDCK                                  | I/O         | LCD clock output for display expansion                                                                      | E-2             | 31            | P3.3                   |

| CLO                                    | I/O         | Clock output                                                                                                | E-2             | 32            | P4.0                   |

| TCL0                                   | I/O         | External clock input for timer/counter 0                                                                    | E-2             | 33            | P4.1                   |

| TCLO0                                  | I/O         | Timer/counter 0 clock output                                                                                | E-2             | 34            | P4.2                   |

| SEG32-<br>SEG39                        | 0           | LCD segment signal output                                                                                   | H–11            | 75–<br>80,1,2 | P5.0-P5.7              |

| SEG0-<br>SEG31                         | 0           | LCD segment signal output                                                                                   | H–6             | 43–74         | -                      |

| COM0-<br>COM7                          | 0           | LCD common signal output                                                                                    | H–6             | 35–42         | _                      |

| V <sub>LC1</sub> -V <sub>LC5</sub>     | -           | LCD power supply. Voltage dividing resistors are assignable by mask option.                                 | _               | 3–7           | _                      |

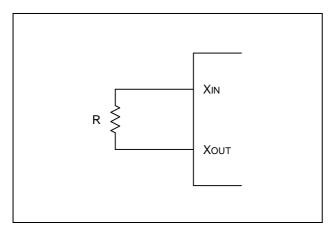

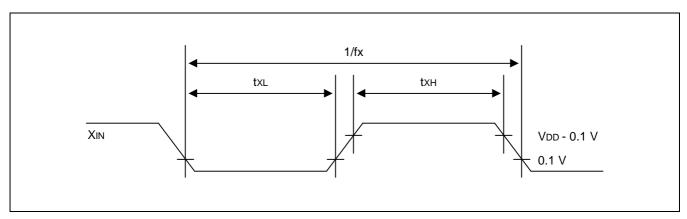

| X <sub>IN</sub> , X <sub>OUT</sub>     | -           | Crystal, ceramic or RC oscillator pins for system clock.                                                    | _               | 15, 14        | _                      |

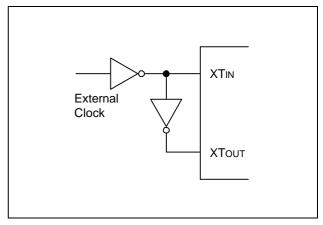

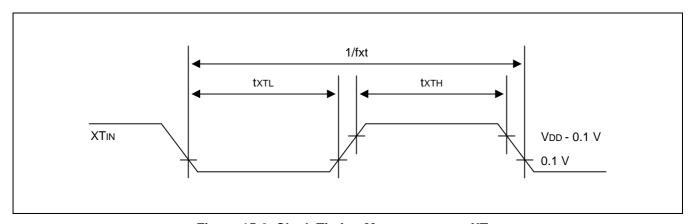

| XT <sub>IN,</sub><br>XT <sub>OUT</sub> | _           | Crystal oscillator pins for subsystem clock.                                                                | _               | 17, 18        | _                      |

| V <sub>DD</sub>                        | _           | Main power supply                                                                                           |                 | 12            | _                      |

| V <sub>SS</sub>                        | _           | Ground                                                                                                      | -               | 13            | _                      |

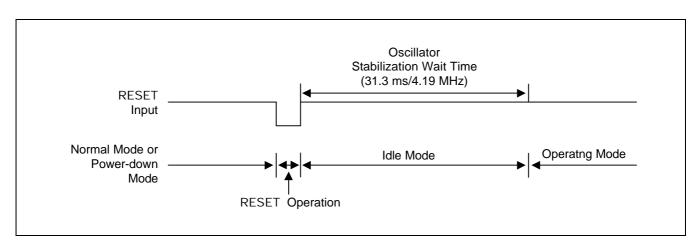

| RESET                                  | I           | Chip reset signal input                                                                                     | В               | 19            | -                      |

| TEST                                   | I           | Chip test signal input (must be connected to V <sub>SS</sub> )                                              | _               | 16            | _                      |

NOTE: Pull-up resistors for all I/O ports are automatically disabled if they are configured to output mode

S3C72K8/P72K8 PRODUCT OVERVIEW

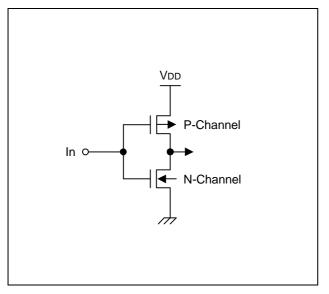

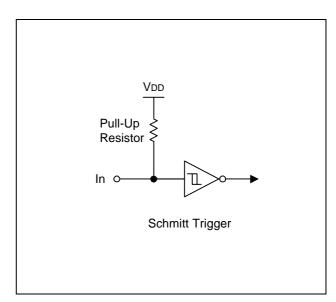

# **PIN CIRCUIT DIAGRAMS**

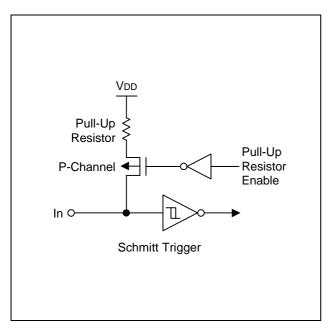

Figure 1-3. Pin Circuit Type A

Figure 1-5. Pin Circuit Type B

Figure 1-4. Pin Circuit Type A-3

Figure 1-6. Pin Circuit Type 7

PRODUCT OVERVIEW S3C72K8/P72K8

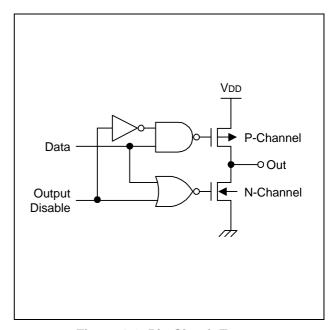

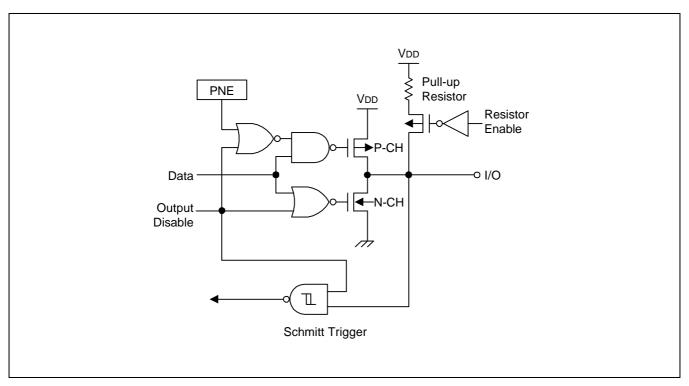

Figure 1-7. Pin Circuit Type E-2

Figure 1-8. Pin Circuit Type F-4

S3C72K8/P72K8 PRODUCT OVERVIEW

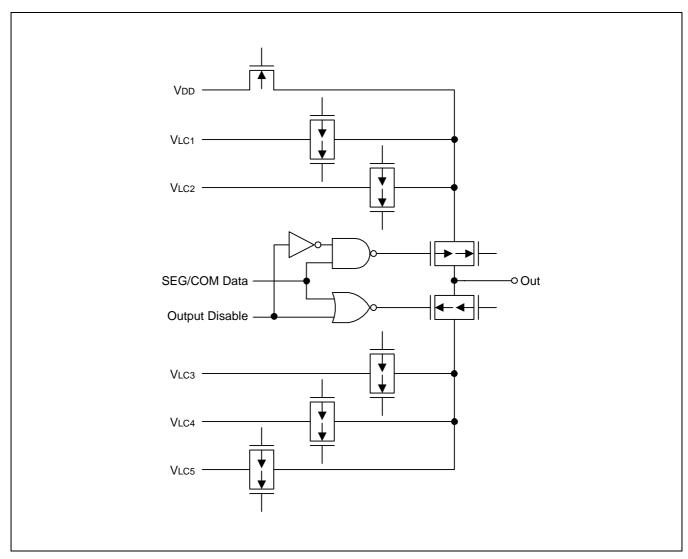

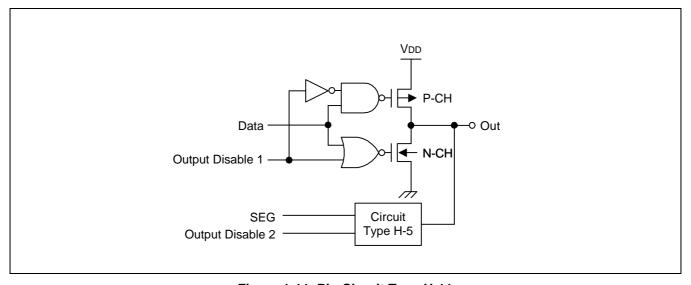

Figure 1-9. Pin Circuit Type H-5

PRODUCT OVERVIEW S3C72K8/P72K8

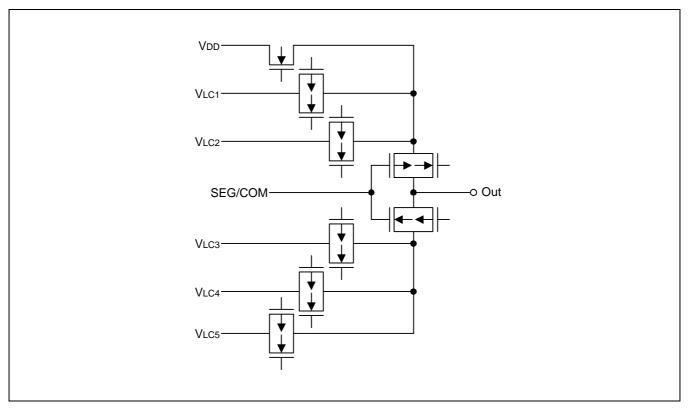

Figure 1-10. Pin Circuit Type H-6

Figure 1-11. Pin Circuit Type H-11

# 2

# **ADDRESS SPACES**

# PROGRAM MEMORY (ROM)

#### **OVERVIEW**

ROM maps for S3C72K8 devices are mask programmable at the factory. In its standard configuration, the device's  $8,192 \times 8$ -bit program memory has three areas that are directly addressable by the program counter (PC):

- 16-byte area for vector addresses

- 96-byte instruction reference area

- 16-byte general-purpose area

- 8,064-byte general-purpose area

#### **General-Purpose Program Memory**

Two program memory areas are allocated for general-purpose use: One area is 16 bytes in size and the other is 8,064 bytes.

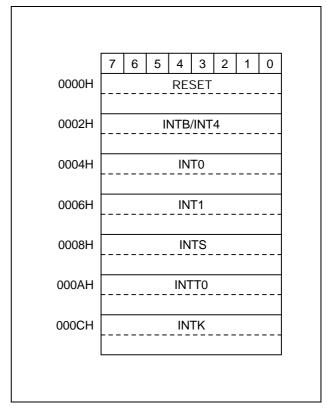

#### **Vector Addresses**

A 16-byte vector address area is used to store the vector addresses required to execute system resets and interrupts. Start addresses for interrupt service routines are stored in this area, along with the values of the enable memory bank (EMB) and enable register bank (ERB) flags that are used to set their initial value for the corresponding service routines. The 16-byte area can be used alternately as general-purpose ROM.

#### **REF Instructions**

Locations 0020H–007FH are used as a reference area (look-up table) for 1-byte REF instructions. The REF instruction reduces the byte size of instruction operands. REF can reference one 2-byte instruction, two 1-byte instructions, and 3-byte instructions which are stored in the look-up table. Unused look-up table addresses can be used as general-purpose ROM.

**Table 2-1. Program Memory Address Ranges**

| ROM Area Function                  | Address Ranges | Area Size (in Bytes) |

|------------------------------------|----------------|----------------------|

| Vector address area                | 0000H-000FH    | 16                   |

| General-purpose program memory     | 0010H-001FH    | 16                   |

| REF instruction look-up table area | 0020H-007FH    | 96                   |

| General-purpose program memory     | 0080H-1FFFH    | 8,064                |

#### **GENERAL-PURPOSE MEMORY AREAS**

The 16-byte area at ROM locations 000CH–001FH and the 8,064-byte area at ROM locations 0080H–1FFFH are used as general-purpose program memory. Unused locations in the vector address area and REF instruction look-up table areas can be used as general-purpose program memory. However, care must be taken not to overwrite live data when writing programs that use special-purpose areas of the ROM.

#### **VECTOR ADDRESS AREA**

The 16-byte vector address area of the ROM is used to store the vector addresses for executing system resets and interrupts. The starting addresses of interrupt service routines are stored in this area, along with the enable memory bank (EMB) and enable register bank (ERB) flag values that are needed to initialize the service routines. 16-byte vector addresses are organized as follows:

| EMB | ERB | 0   | PC12 | PC11 | PC10 | PC9 | PC8 |

|-----|-----|-----|------|------|------|-----|-----|

| PC7 | PC6 | PC5 | PC4  | PC3  | PC2  | PC1 | PC0 |

To set up the vector address area for specific programs, use the instruction VENTn. The programming tips on the next page explain how to do this.

Figure 2-1. ROM Address Structure

Figure 2-2. Vector Address Structure

# PROGRAMMING TIP — Defining Vectored Interrupts

The following examples show you several ways you can define the vectored interrupt and instruction reference areas in program memory:

1. When all vector interrupts are used:

```

ORG

0000H

; EMB \leftarrow 1, ERB \leftarrow 0; Jump to RESET address

VENT0

1,0,RESET

VENT1

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTB address

0,0,INTB

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INT0 address

VENT2

0.0,INT0

VENT3

0,0,INT1

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INT1 address

VENT4

0,0,INTS

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTS address

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTT0 address

VENT5

0,0,INTT0

VENT6

0,0,INTK

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTK address

```

2. When a specific vectored interrupt such as INT0, and INTT0 is not used, the unused vector interrupt locations must be skipped with the assembly instruction ORG so that jumps will address the correct locations:

```

ORG

0000H

VENT0

; EMB \leftarrow 1, ERB \leftarrow 0; Jump to RESET address

1.0.RESET

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTB address

VENT1

0,0,INTB

; INT0 interrupt not used

ORG

0006H

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INT1 address

VENT3

0.0.INT1

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTS address

VENT4

0,0,INTS

ORG

000CH

; INTT0 interrupt not used

VENT6

0,0,INTK

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTK address

```

3. If an INT0 interrupt is not used and if its corresponding vector interrupt area is not fully utilized, or if it is not written by a ORG instruction as in Example 2, a CPU malfunction will occur:

```

ORG

0000H

; EMB \leftarrow 1, ERB \leftarrow 0; Jump to RESET address

VENT0

1,0,RESET

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTB address

VENT1

0,0,INTB

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INT0 address

VENT3

0,0,INT1

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INT1 address

VENT4

0,0,INTS

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTS address

VENT5

0,0,INTT0

VENT6

0,0,INTK

; EMB \leftarrow 0, ERB \leftarrow 0; Jump to INTT0 address

ORG

0010H

```

General-purpose ROM area

In this example, when an INTS interrupt is generated, the corresponding vector area is not VENT4 INTS, but VENT5 INTT0. This causes an INTS interrupt to jump incorrectly to the INTT0 address and causes a CPU malfunction to occur.

#### **INSTRUCTION REFERENCE AREA**

Using 1-byte REF instructions, you can easily reference instructions with larger byte sizes that are stored in addresses 0020H–007FH of program memory. This 96-byte area is called the REF instruction reference area, or look-up table. Locations in the REF look-up table may contain two one-byte instructions, a single two-byte instruction, or three-byte instruction such as a JP (jump) or CALL. The starting address of the instruction you are referencing must always be an even number. To reference a JP or CALL instruction, it must be written to the reference area in a two-byte format: for JP, this format is TJP; for CALL, it is TCALL. In summary, there are three ways to the REF instruction:

By using REF instructions to execute instructions larger than one byte, you can improve program execution time considerably by reducing the number of program steps. In summary, there are three ways you can use the REF instruction:

- Using the 1-byte REF instruction to execute one 2-byte or two 1-byte instructions,

- Branching to any location by referencing a branch instruction stored in the look-up table,

- Calling subroutines at any location by referencing a call instruction stored in the look-up table.

# PROGRAMMING TIP — Using the REF Look-Up Table

Here is one example of how to use the REF instruction look-up table:

```

ORG

0020H

TJP

JMAIN

MAIN

; 0, MAIN

1, KEYFG CHECK

BTSF

KEYCK

KEYFG

WATCH

TCALL

CLOCK

; 2, CALL CLOCK

INCHL

LD

@HL,A

; 3, (HL) \leftarrow A

INCS

HL

ABC

LD

EA,#00H

: EA ← #00H

ORG

H0800

MAIN

NOP

NOP

; BTSF KEYFG (1-byte instruction)

KEYCK

REF

; KEYFG = 1, jump to MAIN (1-byte instruction)

REF

JMAIN

WATCH

; KEYFG = 0, CALL CLOCK (1-byte instruction)

REF

REF

INCHL

; LD @HL,A

INCS HL

REF

ABC

; LD EA,#00H (1-byte instruction)

```

# DATA MEMORY (RAM)

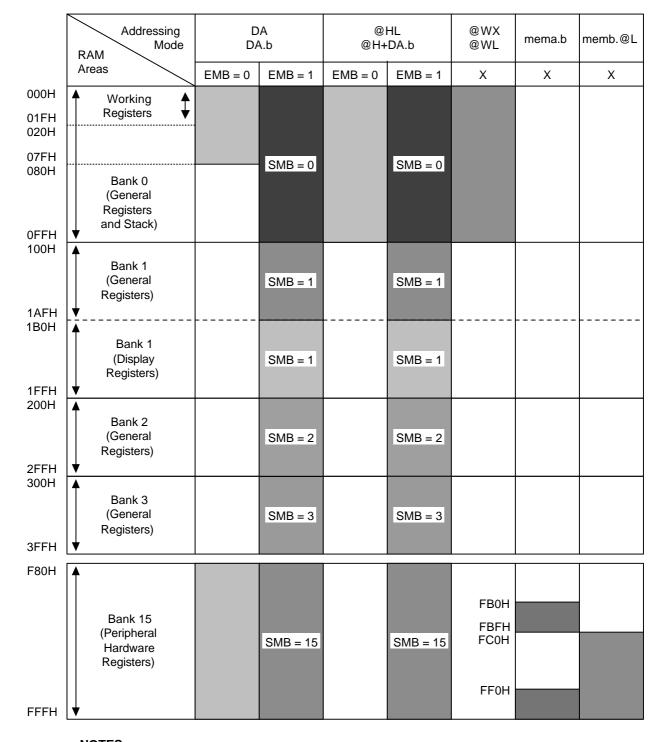

#### **OVERVIEW**

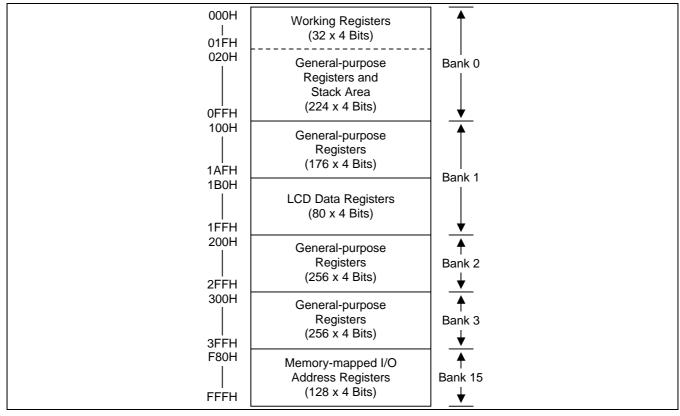

In its standard configuration, the 1,024 x 4-bit data memory has three areas:

- 32 × 4-bit working register area in bank 0

- 224 × 4-bit general-purpose area in bank 0 which is also used as the stack area

- 176 × 4-bit general-purpose area in bank 1

- 80 × 4-bit area for LCD data in bank 1

- 256 × 4-bit general-purpose area in bank 2

- 256 × 4-bit general-purpose area in bank 3

- 128 × 4-bit area in bank 15 for memory-mapped I/O addresses

To make it easier to reference, the data memory area has five memory banks — bank 0, bank 1, bank 2, babk 3, and bank 15. The select memory bank instruction (SMB) is used to select the bank you want to select as working data memory. Data stored in RAM locations are 1-, 4-, and 8-bit addressable.

Initialization values for the data memory area are not defined by hardware and must therefore be initialized by program software following power RESET. However, when RESET signal is generated in power-down mode, the data memory contents are held.

Figure 2-3. Data Memory (RAM) Map

#### Memory Banks 0, 1, and 15

| Bank 0  | (000H-0FFH) | The lowest 32 nibbles of bank 0 (000H–01FH) are used as working registers; the next 224 nibbles (020H–0FFH) can be used both as stack area and as general-purpose data memory. Use the stack area for implementing subroutine calls and returns, and for interrupt processing. |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bank 1  | (1E0H-1FFH) | The lowest 176 nibbles of bank 1 (100H–1AFH) are for general-purpose use; use the ramaining of 80 nibbles (1B0H–1FFH) as display registers or as general purpose memory.                                                                                                       |

| Bank 2  | (200H-2FFH) | 256 nibbles of bank 2 (200H–2FFH) are for general-purpose used                                                                                                                                                                                                                 |

| Bank 3  | (300H-3FFH) | 256 nibbles of bank 3 (300H–3FFH) are for general-purpose used                                                                                                                                                                                                                 |

| Bank 15 | (F80H–FFFH) | The microcontroller uses bank 15 for memory-mapped peripheral I/O. Fixed RAM locations for each peripheral hardware address are mapped into this area.                                                                                                                         |

#### **Data Memory Addressing Modes**

The enable memory bank (EMB) flag controls the addressing mode for data memory banks 0, 1, 2, 3 or 15. When the EMB flag is logic zero, the addressable area is restricted to specific locations, depending on whether direct or indirect addressing is used. With direct addressing, you can access locations 000H–07FH of bank 0 and bank 15. With indirect addressing, only bank 0 (000H–0FFH) can be accessed. When the EMB flag is set to logic one, all three data memory banks can be accessed according to the current SMB value.

For 8-bit addressing, two 4-bit registers are addressed as a register pair. Also, when using 8-bit instructions to address RAM locations, remember to use the even-numbered register address as the instruction operand.

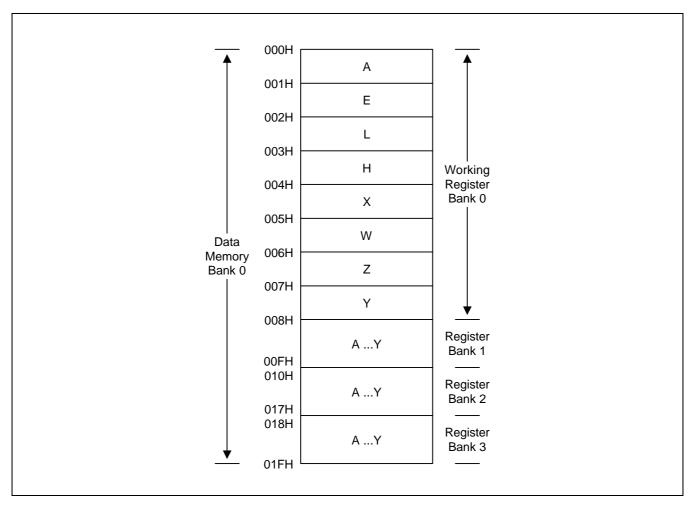

## **Working Registers**

The RAM working register area in data memory bank 0 is further divided into four *register* banks (bank 0, 1, 2, and 3). Each register bank has eight 4-bit registers and paired 4-bit registers are 8-bit addressable.

Register A is used as a 4-bit accumulator and register pair EA as an 8-bit extended accumulator. The carry flag bit can also be used as a 1-bit accumulator. Register pairs WX, WL, and HL are used as address pointers for indirect addressing. To limit the possibility of data corruption due to incorrect register addressing, it is advisable to use register bank 0 for the main program and banks 1, 2, and 3 for interrupt service routines.

## **LCD Data Register Area**

Bit values for LCD segment data are stored in data memory bank 1. Register locations in this area that are not used to store LCD data can be assigned to general-purpose use.

Table 2-2. Data Memory Organization and Addressing

| Addresses | Register Areas                      | Bank | EMB Value | SMB Value |

|-----------|-------------------------------------|------|-----------|-----------|

| 000H-01FH | Working registers                   | 0    | 0, 1      | 0         |

| 020H-0FFH | Stack and general-purpose registers |      |           |           |

| 100H-1AFH | General-purpose registers           | 1    | 1         | 1         |

| 1B0H-1FFH | LCD Data registers                  |      |           |           |

| 200H-2FFH | General-purpose registers           | 2    | 1         | 2         |

| 300H-3FFH | General-purpose registers           | 3    | 1         | 3         |

| F80H-FFFH | I/O- mapped hardware registers      | 15   | 0, 1      | 15        |

# PROGRAMMING TIP — Clearing Data Memory Banks 0 and 1

Clear banks 0 and 1 of the data memory area:

| RAMCLR<br>RMCL1 | SMB<br>LD<br>LD<br>LD<br>INCS<br>JR | 1<br>HL, #00H<br>A, #0H<br>@HL, A<br>HL<br>RMCL1 | ; | RAM (100H–1FFH) clear |

|-----------------|-------------------------------------|--------------------------------------------------|---|-----------------------|

| ;<br>RMCL0      | SMB<br>LD<br>LD<br>INCS<br>JR       | 0<br>HL, #20H<br>@HL, A<br>HL<br>RMCL0           | ; | RAM (020H–0FFH) clear |

#### **WORKING REGISTERS**

Working registers, mapped to RAM address 000H–01FH in data memory bank 0, are used to temporarily store intermediate results during program execution, as well as pointer values used for indirect addressing. Unused registers may be used as general-purpose memory. Working register data can be manipulated as 1-bit units, 4-bit units or, using paired registers, as 8-bit units.

Figure 2-4. Working Register Map

#### **Working Register Banks**

For addressing purposes, the working register area is divided into four register banks — bank 0, bank 1, bank 2, and bank 3. Any one of these banks can be selected as the working register bank by the register bank selection instruction (SRB n) and by setting the status of the register bank enable flag (ERB).

Generally, working register bank 0 is used for the main program, and banks 1, 2, and 3 for interrupt service routines. Following this convention helps to prevent possible data corruption during program execution due to contention in register bank addressing.

| ERB     | SRB Settings |   |   | Selected Register Bank |                      |

|---------|--------------|---|---|------------------------|----------------------|

| Setting | 3            | 2 | 1 | 0                      |                      |

| 0       | 0            | 0 | - | _                      | Always set to bank 0 |

|         |              |   | 0 | 0                      | Bank 0               |

| 1       | 0            | 0 | 0 | 1                      | Bank 1               |

|         |              |   | 1 | 0                      | Bank 2               |

|         |              |   | 1 | 1                      | Bank 3               |

Table 2-3. Working Register Organization and Addressing

NOTE: 'x' means don't care.

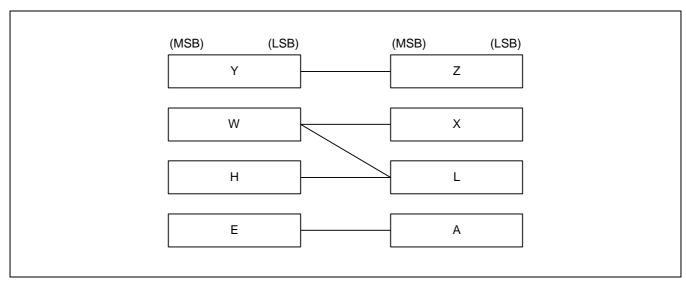

## **Paired Working Registers**

Each of the register banks is subdivided into eight 4-bit registers. These registers, named Y, Z, W, X, H, L, E, and A, can either be manipulated individually using 4-bit instructions, or together as register pairs for 8-bit data manipulation.

The names of the 8-bit register pairs in each register bank are EA, HL, WX, YZ, and WL. Registers A, L, X, and Z always become the lower nibble when registers are addressed as 8-bit pairs. This makes a total of eight 4-bit registers or four 8-bit double registers in each of the four working register banks.

Figure 2-5. Register Pair Configuration

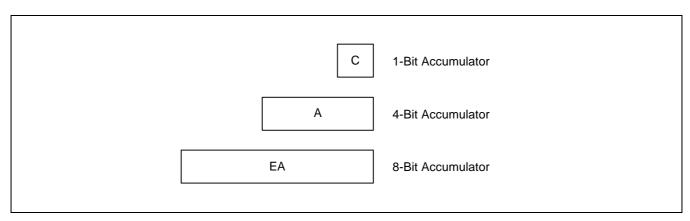

#### **Special-Purpose Working Registers**

Register A is used as a 4-bit accumulator and double register EA as an 8-bit accumulator. The carry flag can also be used as a 1-bit accumulator.

8-bit double registers WX, WL, and HL are used as data pointers for indirect addressing. When the HL register serves as a data pointer, the instructions LDI, LDD, XCHI, and XCHD can make very efficient use of working registers as program loop counters by letting you transfer a value to the L register and increment or decrement it using a single instruction.

Figure 2-6. 1-Bit, 4-Bit, and 8-Bit Accumulator

#### **Recommendation for Multiple Interrupt Processing**

If more than four interrupts are being processed at one time, you can avoid possible loss of working register data by using the PUSH RR instruction to save register contents to the stack before the service routines are executed in the same register bank. When the routines have executed successfully, you can restore the register contents from the stack to working memory using the POP instruction.

# PROGRAMMING TIP — Selecting the Working Register Area

The following examples show the correct programming method for selecting working register area:

1. When ERB = "0":

```

VENT2

1,0,INT0

; EMB \leftarrow 1, ERB \leftarrow 0, Jump to INT0 address

INT<sub>0</sub>

PUSH

SB

PUSH current SMB, SRB

SRB

2

Instruction does not execute because ERB = "0"

PUSH

HL

PUSH HL register contents to stack

PUSH

WX

; PUSH WX register contents to stack

PUSH

YΖ

; PUSH YZ register contents to stack

PUSH

EΑ

; PUSH EA register contents to stack

SMB

0

LD

EA,#00H

LD

80H,EA

LD

HL,#40H

INCS

HL

LD

WX,EA

LD

YZ,EA

POP

; POP EA register contents from stack

EΑ

POP

YΖ

POP YZ register contents from stack

POP

WX

POP WX register contents from stack

POP

HL

POP HL register contents from stack

POP

SB

POP current SMB, SRB

IRET

```

The POP instructions execute alternately with the PUSH instructions. If an SMB n instruction is used in an interrupt service routine, a PUSH and POP SB instruction must be used to store and restore the current SMB and SRB values, as shown in Example 2 below.

2. When ERB = "1":

```

VENT2

; EMB \leftarrow 1, ERB \leftarrow 1, Jump to INT0 address

1,1,INT0

INT<sub>0</sub>

PUSH

SB

Store current SMB, SRB

SRB

2

Select register bank 2 because of ERB = "1"

SMB

0

EA,#00H

LD

LD

80H,EA

LD

HL,#40H

INCS

HL

LD

WX,EA

LD

YZ,EA

POP

SB

; Restore SMB, SRB

IRET

```

#### STACK OPERATIONS

#### **STACK POINTER (SP)**

The stack pointer (SP) is an 8-bit register that stores the address used to access the stack, an area of data memory set aside for temporary storage of data and addresses. The SP can be read or written by 8-bit control instructions. When addressing the SP, bit 0 must always remain cleared to logic zero.

| F80H | SP3 | SP2 | SP1 | "0" |

|------|-----|-----|-----|-----|

| F81H | SP7 | SP6 | SP5 | SP4 |

There are two basic stack operations: writing to the top of the stack (push), and reading from the top of the stack (pop). A push decrements the SP and a pop increments it so that the SP always points to the top address of the last data to be written to the stack.

The program counter contents and program status word (PSW) are stored in the stack area prior to the execution of a CALL or a PUSH instruction, or during interrupt service routines. Stack operation is a LIFO (Last In-First Out) type. The stack area is located in general-purpose data memory bank 0.

During an interrupt or a subroutine, the PC value and the PSW are saved to the stack area. When the routine has completed, the stack pointer is referenced to restore the PC and PSW, and the next instruction is executed.

The SP can address stack registers in bank 0 (addresses 000H–0FFH) regardless of the current value of the enable memory bank (EMB) flag and the select memory bank (SMB) flag. Although general-purpose register areas can be used for stack operations, be careful to avoid data loss due to simultaneous use of the same register(s).

Since the RESET value of the stack pointer is not defined in firmware, we recommend that you initialize the stack pointer by program code to location 00H. This sets the first register of the stack area to 0FFH.

#### NOTE

A subroutine call occupies six nibbles in the stack; an interrupt requires six. When subroutine nesting or interrupt routines are used continuously, the stack area should be set in accordance with the maximum number of subroutine levels. To do this, estimate the number of nibbles that will be used for the subroutines or interrupts and set the stack area correspondingly.

# PROGRAMMING TIP — Initializing the Stack Pointer

To initialize the stack pointer (SP):

1. When EMB = "1":

SMB 15 ; Select memory bank 15

LD EA,#00H ; Bit 0 of SP is always cleared to "0"

LD SP,EA; Stack area initial address (0FFH)  $\leftarrow$  (SP) -1

2. When EMB = "0":

LD EA,#00H

LD SP,EA ; Memory addressing area (00H–7FH, F80H–FFFH)

#### **PUSH OPERATIONS**

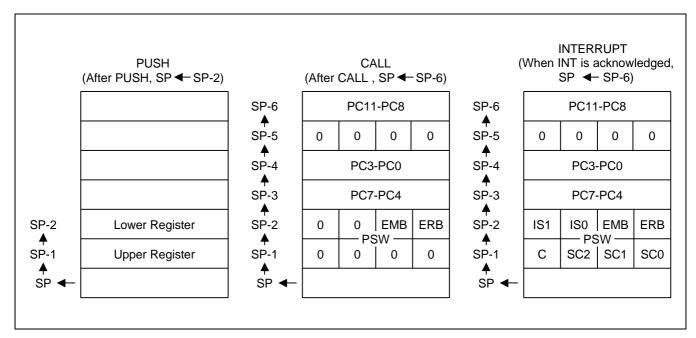

Three kinds of push operations reference the stack pointer (SP) to write data from the source register to the stack: PUSH instructions, CALL instructions, and interrupts. In each case, the SP is *decreased* by a number determined by the type of push operation and then points to the next available stack location.

#### **PUSH Instructions**

A PUSH instruction references the SP to write two 4-bit data nibbles to the stack. Two 4-bit stack addresses are referenced by the stack pointer: one for the upper register value and another for the lower register. After the PUSH has executed, the SP is decreased *by two* and points to the next available stack location.

#### **CALL Instructions**

When a subroutine call is issued, the CALL instruction references the SP to write the PC's contents to six 4-bit stack locations. Current values for the enable memory bank (EMB) flag and the enable register bank (ERB) flag are also pushed to the stack. Since six 4-bit stack locations are used per CALL, you may nest subroutine calls up to the number of levels permitted in the stack.

#### **Interrupt Routines**

An interrupt routine references the SP to push the contents of the PC and the program status word (PSW) to the stack. Six 4-bit stack locations are used to store this data. After the interrupt has executed, the SP is decreased *by six* and points to the next available stack location. During an interrupt sequence, subroutines may be nested up to the number of levels which are permitted in the stack area.

Figure 2-7. Push-Type Stack Operations

#### **POP OPERATIONS**

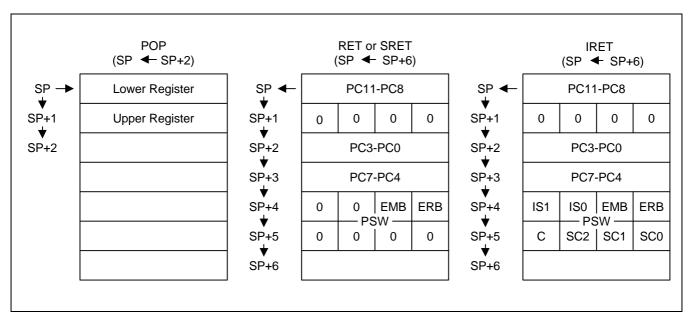

For each push operation there is a corresponding pop operation to write data from the stack back to the source register or registers: for the PUSH instruction it is the POP instruction; for CALL, the instruction RET or SRET; for interrupts, the instruction IRET. When a pop operation occurs, the SP is *incremented* by a number determined by the type of operation and points to the next free stack location.

#### **POP Instructions**

A POP instruction references the SP to write data stored in two 4-bit stack locations back to the register pairs and SB register. The value of the lower 4-bit register is popped first, followed by the value of the upper 4-bit register. After the POP has executed, the SP is incremented *by two* and points to the next free stack location.

#### **RET and SRET Instructions**

The end of a subroutine call is signaled by the return instruction, RET or SRET. The RET or SRET uses the SP to reference the six 4-bit stack locations used for the CALL and to write this data back to the PC, the EMB, and the ERB. After the RET or SRET has executed, the SP is incremented *by six* and points to the next free stack location.

#### **IRET Instructions**

The end of an interrupt sequence is signaled by the instruction IRET. IRET references the SP to locate the six 4-bit stack addresses used for the interrupt and to write this data back to the PC and the PSW. After the IRET has executed, the SP is incremented *by six* and points to the next free stack location.

Figure 2-8. Pop-Type Stack Operations

# **BIT SEQUENTIAL CARRIER (BSC)**

The bit sequential carrier (BSC) is a 16-bit general register that can be manipulated using 1-, 4-, and 8-bit RAM control instructions. RESET clears all BSC bit values to logic zero.

Using the BSC, you can specify sequential addresses and bit locations using 1-bit indirect addressing (memb.@L). (Bit addressing is independent of the current EMB value.) In this way, programs can process 16-bit data by moving the bit location sequentially and then incrementing or decreasing the value of the L register.

BSC data can also be manipulated using direct addressing. For 8-bit manipulations, the 4-bit register names BSC0 and BSC2 must be specified and the upper and lower 8 bits manipulated separately.

If the values of the L register are 0H at BSC0.@L, the address and bit location assignment is FC0H.0. If the L register content is FH at BSC0.@L, the address and bit location assignment is FC3H.3.

| Name | Address | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------|---------|--------|--------|--------|--------|

| BSC0 | FC0H    | BSC0.3 | BSC0.2 | BSC0.1 | BSC0.0 |

| BSC1 | FC1H    | BSC1.3 | BSC1.2 | BSC1.1 | BSC1.0 |

| BSC2 | FC2H    | BSC2.3 | BSC2.2 | BSC2.1 | BSC2.0 |

| BSC3 | FC3H    | BSC3.3 | BSC3.2 | BSC3.1 | BSC3.0 |

**Table 2-4. BSC Register Organization**

# PROGRAMMING TIP — Using the BSC Register to Output 16-Bit Data

To use the bit sequential carrier (BSC) register to output 16-bit data (5937H) to the P3.0 pin:

|     | BITS<br>SMB | EMB<br>15 |                                        |

|-----|-------------|-----------|----------------------------------------|

|     | LD          | EA,#37H   |                                        |

|     | LD          | BSC0,EA   | $BSC0 \leftarrow A, BSC1 \leftarrow E$ |

|     | LD          | EA,#59H   |                                        |

|     | LD          | BSC2,EA   | $BSC2 \leftarrow A, BSC3 \leftarrow E$ |

|     | SMB         | 0         |                                        |

|     | LD          | L,#0H     |                                        |

| AGN | LDB         | C,BSC0.@L |                                        |

|     | LDB         | P3.0,C    | ; P3.0 ← C                             |

|     | INCS        | L         |                                        |

|     | JR          | AGN       |                                        |

|     | RET         |           |                                        |

# PROGRAM COUNTER (PC)

A 12-bit program counter (PC) stores addresses for instruction fetches during program execution. Whenever a reset operation or an interrupt occurs, bits PC11 through PC0 are set to the vector address.

Usually, the PC is incremented by the number of bytes of the instruction being fetched. One exception is the 1-byte REF instruction which is used to reference instructions stored in the ROM.

# **PROGRAM STATUS WORD (PSW)**

The program status word (PSW) is an 8-bit word that defines system status and program execution status and which permits an interrupted process to resume operation after an interrupt request has been serviced. PSW values are mapped as follows:

|      | (MSB) |     |     | (LSB) |

|------|-------|-----|-----|-------|

| FB0H | IS1   | IS0 | EMB | ERB   |

| FB1H | С     | SC2 | SC1 | SC0   |

The PSW can be manipulated by 1-bit or 4-bit read/write and by 8-bit read instructions, depending on the specific bit or bits being addressed. The PSW can be addressed during program execution regardless of the current value of the enable memory bank (EMB) flag.

Part or all of the PSW is saved to stack prior to execution of a subroutine call or hardware interrupt. After the interrupt has been processed, the PSW values are popped from the stack back to the PSW address.

When a RESET is generated, the EMB and ERB values are set according to the RESET vector address, and the carry flag is left undefined (or the current value is retained). PSW bits IS0, IS1, SC0, SC1, and SC2 are all cleared to logical zero.

Table 2-5. Program Status Word Bit Descriptions

| PSW Bit Identifier | Description               | Bit Addressing | Read/Write |

|--------------------|---------------------------|----------------|------------|

| IS1, IS0           | Interrupt status flags    | 1, 4           | R/W        |

| EMB                | Enable memory bank flag   | 1              | R/W        |

| ERB                | Enable register bank flag | 1              | R/W        |

| С                  | Carry flag                | 1              | R/W        |

| SC2, SC1, SC0      | Program skip flags        | 8              | R          |

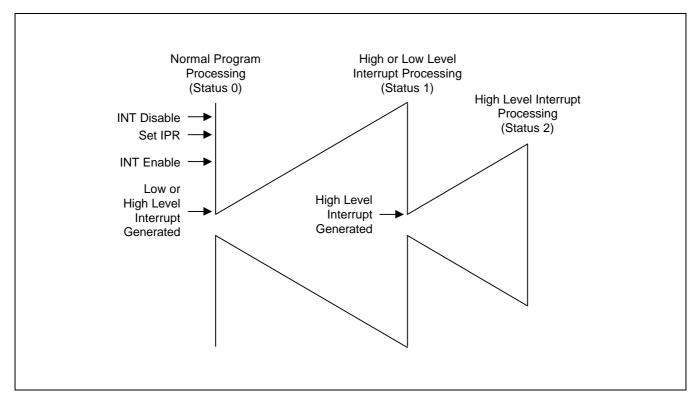

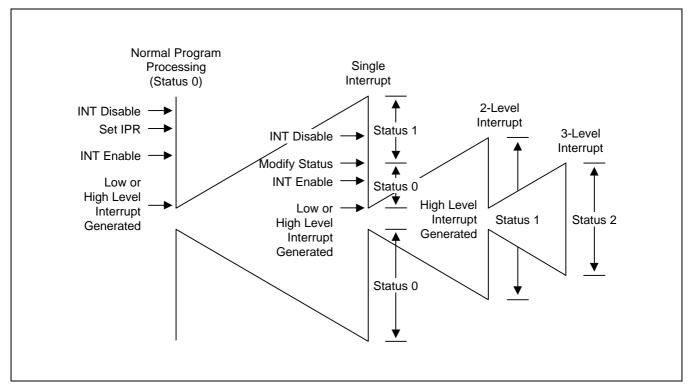

#### **INTERRUPT STATUS FLAGS (ISO, IS1)**

PSW bits IS0 and IS1 contain the current interrupt execution status values. You can manipulate IS0 and IS1 flags directly using 1-bit RAM control instructions

By manipulating interrupt status flags in conjunction with the interrupt priority register (IPR), you can process multiple interrupts by anticipating the next interrupt in an execution sequence. The interrupt priority control circuit determines the ISO and IS1 settings in order to control multiple interrupt processing. When both interrupt status flags are set to "0", all interrupts are allowed. The priority with which interrupts are processed is then determined by the IPR.

When an interrupt occurs, ISO and IS1 are pushed to the stack as part of the PSW and are automatically incremented to the next higher priority level. Then, when the interrupt service routine ends with an IRET instruction, ISO and IS1 values are restored to the PSW. Table 2-6 shows the effects of ISO and IS1 flag settings.

| IS1<br>Value | IS0<br>Value | Status of Currently<br>Executing Process | Effect of IS0 and IS1 Settings on Interrupt Request Control                                         |

|--------------|--------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 0            | 0            | 0                                        | All interrupt requests are serviced                                                                 |

| 0            | 1            | 1                                        | Only high-priority interrupt(s) as determined in the interrupt priority register (IPR) are serviced |

| 1            | 0            | 2                                        | No more interrupt requests are serviced                                                             |

| 1            | 1            | _                                        | Not applicable; these bit settings are undefined                                                    |

Table 2-6. Interrupt Status Flag Bit Settings

Since interrupt status flags can be addressed by write instructions, programs can exert direct control over interrupt processing status. Before interrupt status flags can be addressed, however, you must first execute a DI instruction to inhibit additional interrupt routines. When the bit manipulation has been completed, execute an EI instruction to re-enable interrupt processing.

# PROGRAMMING TIP — Setting ISx Flags for Interrupt Processing

The following instruction sequence shows how to use the IS0 and IS1 flags to control interrupt processing:

**INTB** DI ; Disable interrupt **BITR** IS1 ; IS1  $\leftarrow$  0

> **BITS** IS0 ; Allow interrupts according to IPR priority level

FI ; Enable interrupt

**IRET**

## **EMB FLAG (EMB)**

The EMB flag is used to allocate specific address locations in the RAM by modifying the upper 4 bits of 12-bit data memory addresses. In this way, it controls the addressing mode for data memory banks 0, 1, or 15.

When the EMB flag is "0", the data memory address space is restricted to bank 15 and addresses 000H–07FH of memory bank 0, regardless of the SMB register contents. When the EMB flag is set to "1", the general-purpose areas of bank 0, 1, and 15 can be accessed by using the appropriate SMB value.

# PROGRAMMING TIP — Using the EMB Flag to Select Memory Banks

EMB flag settings for memory bank selection:

1. When EMB = "0":

```

SMB

: Non-essential instruction since EMB = "0"

1

LD

A,#9H

LD

90H,A

; (F90H) ← A, bank 15 is selected

LD

34H,A

; (034H) ← A, bank 0 is selected

SMB

: Non-essential instruction since EMB = "0"

90H.A

(F90H) ← A, bank 15 is selected

LD

LD

34H.A

(034H) ← A, bank 0 is selected

SMB

; Non-essential instruction, since EMB = "0"

15

20H,A

; (020H) \leftarrow A, bank 0 is selected

LD

LD

90H,A

; (F90H) ← A, bank 15 is selected

```

2. When EMB = "1":

```

SMB

; Select memory bank 1

LD

A,#9H

LD

90H,A

(190H) \leftarrow A, bank 1 is selected

(1340H) ← A, bank 1 is selected

LD

34H,A

SMB

Select memory bank 0

0

LD

; (090H) ← A, bank 0 is selected

90H,A

LD

34H,A

; (034H) ← A, bank 0 is selected

SMB

Select memory bank 15

15

LD

20H.A

; Program error, but assembler does not detect it

LD

90H,A

(F90H) ← A, bank 15 is selected

```

#### **ERB FLAG (ERB)**

The 1-bit register bank enable flag (ERB) determines the range of addressable working register area. When the ERB flag is "1", the working register area from register banks 0 to 3 is selected according to the register bank selection register (SRB). When the ERB flag is "0", register bank 0 is the selected working register area, regardless of the current value of the register bank selection register (SRB).

When an internal RESET is generated, bit 6 of program memory address 0000H is written to the ERB flag. This automatically initializes the flag. When a vectored interrupt is generated, bit 6 of the respective address table in program memory is written to the ERB flag, setting the correct flag status before the interrupt service routine is executed.

During the interrupt routine, the ERB value is automatically pushed to the stack area along with the other PSW bits. Afterwards, it is popped back to the FB0H.0 bit location. The initial ERB flag settings for each vectored interrupt are defined using VENTn instructions.

# PROGRAMMING TIP — Using the ERB Flag to Select Register Banks

ERB flag settings for register bank selection:

1. When ERB = "0":

```

SRB

; Register bank 0 is selected (since ERB = "0", the

; SRB is configured to bank 0)

LD

EA,#34H

; Bank 0 EA ← #34H

; Bank 0 HL \leftarrow EA

LD

HL,EA

; Register bank 0 is selected

SRB

2

LD

YZ,EA

Bank 0 YZ \leftarrow EA

; Register bank 0 is selected

SRB

3

; Bank 0 WX ← EA

LD

WX,EA

```

2. When ERB = "1":

| SRB | 1       | ; | Register bank 1 is selected |

|-----|---------|---|-----------------------------|

| LD  | EA,#34H | ; | Bank 1 EA ← #34H            |

| LD  | HL,EA   | ; | Bank 1 HL ← Bank 1 EA       |

| SRB | 2       | ; | Register bank 2 is selected |

| LD  | YZ,EA   | ; | Bank 2 YZ ← Bank 2 EA       |

| SRB | 3       | ; | Register bank 3 is selected |

| LD  | WX,EA   | ; | Bank 3 WX ← Bank 3 EA       |

#### SKIP CONDITION FLAGS (SC2, SC1, SC0)

The skip condition flags SC2, SC1, and SC0 in the PSW indicate the current program skip conditions and are set and reset automatically during program execution. Skip condition flags can only be addressed by 8-bit read instructions. Direct manipulation of the SC2, SC1, and SC0 bits is not allowed.

#### **CARRY FLAG (C)**

The carry flag is used to save the result of an overflow or borrow when executing arithmetic instructions involving a carry (ADC, SBC). The carry flag can also be used as a 1-bit accumulator for performing Boolean operations involving bit-addressed data memory.

If an overflow or borrow condition occurs when executing arithmetic instructions with carry (ADC, SBC), the carry flag is set to "1". Otherwise, its value is "0". When a RESET occurs, the current value of the carry flag is retained during power-down mode, but when normal operating mode resumes, its value is undefined.

The carry flag can be directly manipulated by predefined set of 1-bit read/write instructions, independent of other bits in the PSW. Only the ADC and SBC instructions, and the instructions listed in Table 2-7, affect the carry flag.

| Operation Type        | Instructions         | Carry Flag Manipulation                                                                 |

|-----------------------|----------------------|-----------------------------------------------------------------------------------------|

| Direct manipulation   | SCF                  | Set carry flag to "1"                                                                   |

|                       | RCF                  | Clear carry flag to "0" (reset carry flag)                                              |

|                       | CCF                  | Invert carry flag value (complement carry flag)                                         |

|                       | BTST C               | Test carry and skip if C = "1"                                                          |

| Bit transfer          | LDB (operand) (1),C  | Load carry flag value to the specified bit                                              |

|                       | LDB C,(operand) (1)  | Load contents of the specified bit to carry flag                                        |

| Boolean manipulation  | BAND C,(operand) (1) | AND the specified bit with contents of carry flag and save the result to the carry flag |

|                       | BOR C,(operand) (1)  | OR the specified bit with contents of carry flag and save the result to the carry flag  |

|                       | BXOR C,(operand) (1) | XOR the specified bit with contents of carry flag and save the result to the carry flag |

| Interrupt routine     | INTn (2)             | Save carry flag to stack with other PSW bits                                            |

| Return from interrupt | IRET                 | Restore carry flag from stack with other PSW bits                                       |

**Table 2-7. Valid Carry Flag Manipulation Instructions**

#### NOTES:

- The operand has three bit addressing formats: mema.a, memb.@L, and @H + DA.b.

- 2. 'INTn' refers to the specific interrupt being executed and is not an instruction.

# PROGRAMMING TIP — Using the Carry Flag as a 1-Bit Accumulator

1. Set the carry flag to logic one:

SCF ;  $C \leftarrow 1$

LD EA,#0C3H ; EA  $\leftarrow$  #0C3H LD HL,#0AAH ; HL  $\leftarrow$  #0AAH

ADC EA,HL ; EA  $\leftarrow$  #0C3H + #0AAH + #1H, C  $\leftarrow$  1

2. Logical-AND bit 3 of address 3FH with P3.3 and output the result to P5.0:

LD H,#3H ; Set the upper four bits of the address to the H register

; value

LDB C,@H+0FH.3 ;  $C \leftarrow bit \ 3 \ of \ 3FH$  BAND C,P3.3 ;  $C \leftarrow C \ AND \ P3.3$

LDB P4.0,C ; Output result from carry flag to P4.0

S3C72K8/P72K8 ADDRESSING MODES

3

# **ADDRESSING MODES**

#### **OVERVIEW**

The enable memory bank flag, EMB, controls the two addressing modes for data memory. When the EMB flag is set to logic one, you can address the entire RAM area; when the EMB flag is cleared to logic zero, the addressable area in the RAM is restricted to specific locations.

The EMB flag works in connection with the select memory bank instruction, SMBn. You will recall that the SMBn instruction is used to select RAM bank 0, 1, 2, 3 or 15. The SMB setting is always contained in the upper four bits of a 12-bit RAM address. For this reason, both addressing modes (EMB = "0" and EMB = "1") apply specifically to the memory bank indicated by the SMB instruction, and any restrictions to the addressable area within banks 0, 1, 2, 3 or 15. Direct and indirect 1-bit, 4-bit, and 8-bit addressing methods can be used. Several RAM locations are addressable at all times, regardless of the current EMB flag setting.

Here are a few guidelines to keep in mind regarding data memory addressing:

- When you address peripheral hardware locations in bank 15, the mnemonic for the memory-mapped hardware component can be used as the operand in place of the actual address location.

- Always use an even-numbered RAM address as the operand in 8-bit direct and indirect addressing.

- With direct addressing, use the RAM address as the instruction operand; with indirect addressing, the instruction specifies a register which contains the operand's address.

ADDRESSING MODES S3C72K8/P72K8

# NOTES:

- 1. 'X' means don't care.

- 2. Blank columns indicate RAM areas that are not addressable, given the addressing method and enable memory bank (EMB) flag setting shown in the column headers.

Figure 3-1. RAM Address Structure

S3C72K8/P72K8 ADDRESSING MODES

#### **EMB AND ERB INITIALIZATION VALUES**

The EMB and ERB flag bits are set automatically by the values of the RESET vector address and the interrupt vector address. When a RESET is generated internally, bit 7 of program memory address 0000H is written to the EMB flag, initializing it automatically. When a vectored interrupt is generated, bit 7 of the respective vector address table is written to the EMB. This automatically sets the EMB flag status for the interrupt service routine. When the interrupt is serviced, the EMB value is automatically saved to stack and then restored when the interrupt routine has completed.

At the beginning of a program, the initial EMB and ERB flag values for each vectored interrupt must be set by using VENT instruction. The EMB and ERB can be set or reset by bit manipulation instructions (BITS, BITR) despite the current SMB setting.

# PROGRAMMING TIP — Initializing the EMB and ERB Flags

**EMB**

The following assembly instructions show how to initialize the EMB and ERB flag settings:

```

; ROM address assignment

ORG

H0000

VENT0

1,0,RESET

; EMB \leftarrow 1, ERB \leftarrow 0, branch RESET

VENT1

0,1,INTB

; EMB \leftarrow 0, ERB \leftarrow 1, branch INTB

; EMB \leftarrow 0, ERB \leftarrow 1, branch INT0

VENT2

0,1,INT0

VENT3

0,1,INT1

; EMB \leftarrow 0, ERB \leftarrow 1, branch INT1

; EMB \leftarrow 0, ERB \leftarrow 1, branch INTS

VENT4

0,1,INTS

VENT5

0,1,INTT0

; EMB \leftarrow 0, ERB \leftarrow 1, branch INTT0

VENT6

; EMB \leftarrow 0, ERB \leftarrow 1, branch INTK

0,1,INTK

```

RESET

**BITR**

ADDRESSING MODES S3C72K8/P72K8

#### **ENABLE MEMORY BANK SETTINGS**

#### EMB = "1"

When the enable memory bank flag EMB is set to logic one, you can address the data memory bank specified by the select memory bank (SMB) value (0, 1, 2, 3 or 15) using 1-, 4-, or 8-bit instructions. You can use both direct and indirect addressing modes. The addressable RAM areas when EMB = "1" are as follows:

| If $SMB = 0$ ,  | 000H-0FFH |

|-----------------|-----------|

| If $SMB = 1$ ,  | 100H-1FFH |

| If $SMB = 2$ ,  | 200H-2FFH |

| If $SMB = 3$ ,  | 300H-3FFH |

| If $SMB = 15$ , | F80H-FFFH |

## EMB = "0"

When the enable memory bank flag EMB is set to logic zero, the addressable area is defined independently of the SMB value, and is restricted to specific locations depending on whether a direct or indirect address mode is used.

If EMB = "0", the addressable area is restricted to locations 000H–07FH in bank 0 and to locations F80H–FFFH in bank 15 for direct addressing. For indirect addressing, only locations 000H–0FFH in bank 0 are addressable, regardless of SMB value.

To address the peripheral hardware register (bank 15) using indirect addressing, the EMB flag must first be set to "1" and the SMB value to "15". When a RESET occurs, the EMB flag is set to the value contained in bit 7 of ROM address 0000H.

#### **EMB-Independent Addressing**

At any time, several areas of the data memory can be addressed independent of the current status of the EMB flag. These exceptions are described in Table 3-1.

Table 3-1. RAM Addressing Not Affected by the EMB Value

| Address                | Addressing Method                                                                            | Affected Hardware             | Program Examples             |

|------------------------|----------------------------------------------------------------------------------------------|-------------------------------|------------------------------|

| 000H-0FFH              | 4-bit indirect addressing using WX and WL register pairs; 8-bit indirect addressing using SP | Not applicable                | LD A,@WX PUSH EA POP EA      |

| FB0H–FBFH<br>FF0H–FFFH | 1-bit direct addressing                                                                      | PSW, SCMOD,<br>IEx, IRQx, I/O | BITS EMB<br>BITR IE4         |

| FC0H-FFFH              | 1-bit indirect addressing using the L register                                               | BSC, I/O                      | BTST FC3H.@L<br>BAND C,P3.@L |

S3C72K8/P72K8 ADDRESSING MODES

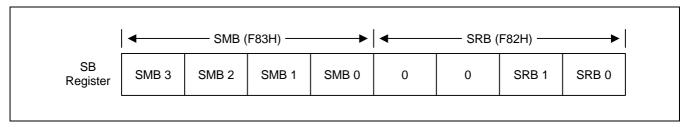

#### **SELECT BANK REGISTER (SB)**

The select bank register (SB) is used to assign the memory bank and register bank. The 8-bit SB register consists of the 4-bit select register bank register (SRB) and the 4-bit select memory bank register (SMB), as shown in Figure 3-2.

During interrupts and subroutine calls, SB register contents can be saved to stack in 8-bit units by the PUSH SB instruction. You later restore the value to the SB using the POP SB instruction.

Figure 3-2. SMB and SRB Values in the SB Register

## Select Register Bank (SRB) Instruction

The select register bank (SRB) value specifies which register bank is to be used as a working register bank. The SRB value is set by the 'SRB n' instruction, where n = 0, 1, 2, 3.

One of the four register banks is selected by the combination of ERB flag status and the SRB value that is set using the 'SRB n' instruction. The current SRB value is retained until another register is requested by program software. PUSH SB and POP SB instructions are used to save and restore the contents of SRB during interrupts and subroutine calls. RESET clears the 4-bit SRB value to logic zero.

#### Select Memory Bank (SMB) Instruction

To select one of the four available data memory banks, you must execute an SMB n instruction specifying the number of the memory bank you want (0, 1, 2, 3 or 15). For example, the instruction 'SMB 1' selects bank 1 and 'SMB 15' selects bank 15. (And remember to enable the selected memory bank by making the appropriate EMB flag setting.)

The upper four bits of the 12-bit data memory address are stored in the SMB register. If the SMB value is not specified by software (or if a RESET does not occur) the current value is retained. RESET clears the 4-bit SMB value to logic zero.

The PUSH SB and POP SB instructions save and restore the contents of the SMB register to and from the stack area during interrupts and subroutine calls.

ADDRESSING MODES S3C72K8/P72K8

### **DIRECT AND INDIRECT ADDRESSING**

1-bit, 4-bit, and 8-bit data stored in data memory locations can be addressed directly using a specific register or bit address as the instruction operand.

Indirect addressing specifies a memory location that contains the required direct address. The S3C7 instruction set supports 1-bit, 4-bit, and 8-bit indirect addressing. For 8-bit indirect addressing, an even-numbered RAM address must always be used as the instruction operand.

### 1-BIT ADDRESSING

Table 3-2. 1-Bit Direct and Indirect RAM Addressing

| Operand<br>Notation | Addressing Mode<br>Description                                                                                                    | EMB Flag<br>Setting | Addressable<br>Area    | Memory<br>Bank | Hardware I/O<br>Mapping                               |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|----------------|-------------------------------------------------------|

|                     |                                                                                                                                   |                     | 000H-07FH              | Bank 0         | _                                                     |

| DA.b                | Direct: bit is indicated by the RAM address (DA), memory bank selection, and specified bit number (b).                            | 0                   | F80H-FFFH              | Bank 15        | All 1-bit<br>addressable<br>peripherals<br>(SMB = 15) |

|                     |                                                                                                                                   | 1                   | 000H-FFFH              | SMB = 0-3,15   |                                                       |

| mema.b              | Direct: bit is indicated by addressable area (mema) and bit number (b).                                                           | х                   | FB0H–FBFH<br>FF0H–FFFH | Bank 15        | ISO, IS1, EMB,<br>ERB, IEx, IRQx,<br>Pn.n             |

| memb.@L             | Indirect: lower two bits of register L as indicated by the upper 10 bits of RAM area (memb) and the upper two bits of register L. | Х                   | FC0H-FFFH              | Bank 15        | BSCn.x<br>Pn.n                                        |

| @H + DA.b           | Indirect: bit indicated by the lower four bits of the address (DA), memory bank selection, and the H register identifier.         | 0                   | 000H-0FFH              | Bank 0         | -                                                     |

|                     |                                                                                                                                   | 1                   | 000H-FFFH              | SMB = 0-3,15   | All 1-bit<br>addressable<br>peripherals<br>(SMB = 15) |

NOTE: 'x' means don't care.

S3C72K8/P72K8 ADDRESSING MODES

## PROGRAMMING TIP — 1-Bit Addressing Modes

### 1-Bit Direct Addressing

```

1. If EMB = "0":

AFLAG

EQU

34H.3

BFLAG

EQU

85H.3

CFLAG

EQU

0BAH.0

SMB

0

BITS

AFLAG

; 34H.3 ← 1

; F85H.3 ← 1

BITS

BFLAG

BTST

CFLAG

; If FBAH.0 = 1, skip

BITS

BFLAG

; Else if, FBAH.0 = 0, F85H.3 (BMOD.3) \leftarrow 1

BITS

P3.0

; FF3H.0 (P3.0) \leftarrow 1

2. If EMB = "1":

AFLAG

EQU

34H.3

BFLAG

85H.3

EQU

CFLAG

EQU

0BAH.0

SMB

0

BITS

AFLAG

; 34H.3 ← 1

; 85H.3 ← 1

BITS

BFLAG

CFLAG

; If 0BAH.0 = 1, skip

BTST

BFLAG

; Else if 0BAH.0 = 0, 085H.3 \leftarrow 1

BITS

BITS

P3.0

; FF3H.0 (P3.0) \leftarrow 1

```

#### 1-Bit Indirect Addressing

```

1. If EMB = "0":

AFLAG

EQU

34H.3

BFLAG

EQU

85H.3

CFLAG

EQU

0BAH.0

SMB

0

; H ← #0BH

LD

H.#0BH

BTSTZ

@H+CFLAG

; If 0BAH.0 = 1, 0BAH.0 \leftarrow 0 and skip

; Else if 0BAH.0 = 0, FBAH.0 \leftarrow 1

BITS

CFLAG

2. If EMB = "1":

AFLAG

EQU

34H.3

BFLAG

EQU

85H.3

CFLAG

EQU

0BAH.0

SMB

0

H,#0BH

; H ← #0BH

LD

; If 0BAH.0 = 1, 0BAH.0 \leftarrow 0 and skip

BTSTZ

@H+CFLAG

```

; Else if 0BAH.0 = 0,  $0BAH.0 \leftarrow 1$

**BITS**

**CFLAG**

3-7

ADDRESSING MODES S3C72K8/P72K8

### **4-BIT ADDRESSING**

Table 3-3. 4-Bit Direct and Indirect RAM Addressing

| Operand<br>Notation | Addressing Mode<br>Description                                                              | EMB Flag<br>Setting | Addressable<br>Area | Memory<br>Bank | Hardware I/O<br>Mapping                               |

|---------------------|---------------------------------------------------------------------------------------------|---------------------|---------------------|----------------|-------------------------------------------------------|

|                     |                                                                                             |                     | 000H-07FH           | Bank 0         | _                                                     |

| DA                  | Direct: 4-bit address indicated<br>by the RAM address (DA) and<br>the memory bank selection | 0                   | F80H-FFFH           | Bank 15        | All 4-bit<br>addressable<br>peripherals               |

|                     |                                                                                             | 1                   | 000H-FFFH           | SMB = 0-3,15   | (SMB = 15)                                            |

| @HL                 | Indirect: 4-bit address indi-<br>cated by the memory bank<br>selection and register HL      | 0                   | 000H-0FFH           | Bank 0         | -                                                     |

|                     |                                                                                             | 1                   | 000H-FFFH           | SMB = 0-3,15   | All 4-bit<br>addressable<br>peripherals<br>(SMB = 15) |

| @WX                 | Indirect: 4-bit address indicated by register WX                                            | Х                   | 000H-0FFH           | Bank 0         | -                                                     |

| @WL                 | Indirect: 4-bit address indicated by register WL                                            | Х                   | 000H-0FFH           | Bank 0         |                                                       |

NOTE: 'x' means don't care.

## PROGRAMMING TIP — 4-Bit Addressing Modes

### 4-Bit Direct Addressing

```

1. If EMB = "0":

```

EQU ADATA 46H **BDATA** EQU 8EH ; Non-essential instruction, since EMB = "0" SMB 15 LD A,P3 ;  $A \leftarrow (P3)$ ; Non-essential instruction, since EMB = "0" SMB 0 ; (046H) ← A LD ADATA,A LD BDATA,A ; (F8EH (LCON))  $\leftarrow$  A 2. If EMB = "1": ] **ADATA** EQU 46H **BDATA** EQU 8EH SMB 15 LD A,P3 ;  $A \leftarrow (P3)$ SMB LD ADATA,A; (046H) ← A BDATA,A;  $(08EH) \leftarrow A$ LD

S3C72K8/P72K8 ADDRESSING MODES

## PROGRAMMING TIP — 4-Bit Addressing Modes

### 4-Bit Indirect Addressing (Example 1)

1. If EMB = "0", compare bank 0 locations 040H-046H with bank 0 locations 060H-066H:

```

ADATA EQU 46H

BDATA EQU 66H

```

SMB 1 ; Non-essential instruction, since EMB = "0"

LD HL,#BDATA LD WX,#ADATA

COMP LD A, @WL ; A  $\leftarrow$  bank 0 (040H–046H)

CPSE A,@HL ; If bank 0 (060H-066H) = A, skip

**SRET**

DECS L JR COMP

RET

2. If EMB = "1", compare bank 0 locations 040H-046H with bank 1 locations 160H-166H:

ADATA EQU 46H BDATA EQU 66H SMB 1

> LD HL,#BDATA LD WX,#ADATA

COMP LD A,@WL ;  $A \leftarrow bank \ 0 \ (040H-046H)$  CPSE A,@HL ; If  $bank \ 1 \ (160H-166H) = A$ , skip

> SRET DECS L JR COMP

RET

### 4-Bit Indirect Addressing (Example 2)

1. If EMB = "0", exchange bank 0 locations 040H-046H with bank 0 locations 060H-066H:

ADATA EQU 46H BDATA EQU 66H

SMB 1 ; Non-essential instruction, since EMB = "0"

LD HL,#BDATA LD WX,#ADATA

TRANS LD A,@WL ;  $A \leftarrow bank 0 (040H-046H)$

XCHD A,@HL ; If bank 0 (060H–066H)  $\leftrightarrow$  A, skip

JR TRANS

2. If EMB = "1", exchange bank 0 locations 040H–046H with bank 1 locations 160H–166H:

ADATA EQU 46H BDATA EQU 66H SMB 1

LD HL,#BDATA LD WX,#ADATA

TRANS LD A,@WL ;  $A \leftarrow bank 0 (040H-046H)$

XCHD A,@HL ; If bank 1 (160H–166H)  $\leftrightarrow$  A, skip

JR TRANS

3-9

ADDRESSING MODES S3C72K8/P72K8

## **8-BIT ADDRESSING**

Table 3-4. 8-Bit Direct and Indirect RAM Addressing

| Instruction<br>Notation | Addressing Mode<br>Description                                                                                                          | EMB Flag<br>Setting | Addressable<br>Area | Memory<br>Bank | Hardware I/O<br>Mapping                               |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|----------------|-------------------------------------------------------|

|                         |                                                                                                                                         |                     | 000H-07FH           | Bank 0         | _                                                     |

| DA                      | Direct: 8-bit address indicated by the RAM address ( <i>DA</i> = even number) and memory bank selection                                 | 0                   | F80H-FFFH           | Bank 15        | All 8-bit<br>addressable<br>peripherals               |

|                         |                                                                                                                                         | 1                   | 000H-FFFH           | SMB = 0-3,15   | (SMB = 15)                                            |

| @HL                     | Indirect: the 8-bit address indicated by the memory bank selection and register HL; (the 4-bit L register value must be an even number) | 0                   | 000H-0FFH           | Bank 0         | -                                                     |

|                         |                                                                                                                                         | 1                   | 000H-FFFH           | SMB = 0-3,15   | All 8-bit<br>addressable<br>peripherals<br>(SMB = 15) |

S3C72K8/P72K8 ADDRESSING MODES

## PROGRAMMING TIP — 8-Bit Addressing Modes

### 8-Bit Direct Addressing

1. If EMB = "0":

```

ADATA

EQU

46H

BDATA

EQU

8EH

; Non-essential instruction, since EMB = "0"

SMB

15

LD

EA, P4

; E \leftarrow (P5), A \leftarrow (P4)

SMB

0

; (046H) \leftarrow A, (047H) \leftarrow E

LD

ADATA, EA

LD

BDATA, EA

; (F8EH) \leftarrow A, (F8FH) \leftarrow E

```

2. If EMB = "1":

```

ADATA

EQU

46H

BDATA

8EH

EQU

SMB

15

LD

EA,P4

; E \leftarrow (P5), A \leftarrow (P4)

SMB

0

LD

ADATA,EA

; (046H) \leftarrow A, (047H) \leftarrow E

LD

BDATA, EA

; (08EH) \leftarrow A, (08FH) \leftarrow E

```

### 8-Bit Indirect Addressing

1. If EMB = "0":

```

ADATA EQU 46H SMB 1 ; Non-essential instruction, since EMB = "0" LD HL,#ADATA LD EA,@HL ; A \leftarrow (046H), E \leftarrow (047H) 2. If EMB = "1":

```

ADATA EQU 46H

SMB 1

LD HL,#ADATA

LD EA,@HL ;

LD EA,@HL ; A  $\leftarrow$  (146H), E  $\leftarrow$  (147H)

4

## **MEMORY MAP**

### **OVERVIEW**

To support program control of peripheral hardware, I/O addresses for peripherals are memory-mapped to bank 15 of the RAM. Memory mapping lets you use a mnemonic as the operand of an instruction in place of the specific memory location.

Access to bank 15 is controlled by the select memory bank (SMB) instruction and by the enable memory bank flag (EMB) setting. If the EMB flag is "0", bank 15 can be addressed using direct addressing, regardless of the current SMB value. 1-bit direct and indirect addressing can be used for specific locations in bank 15, regardless of the current EMB value.

#### I/O MAP FOR HARDWARE REGISTERS

Table 4-1 contains detailed information about I/O mapping for peripheral hardware in bank 15 (register locations F80H–FFFH). Use the I/O map as a quick-reference source when writing application programs. The I/O map gives you the following information:

- Register address

- Register name (mnemonic for program addressing)

- Bit values (both addressable and non-manipulable)

- Read-only, write-only, or read and write addressability

- 1-bit, 4-bit, or 8-bit data manipulation characteristics

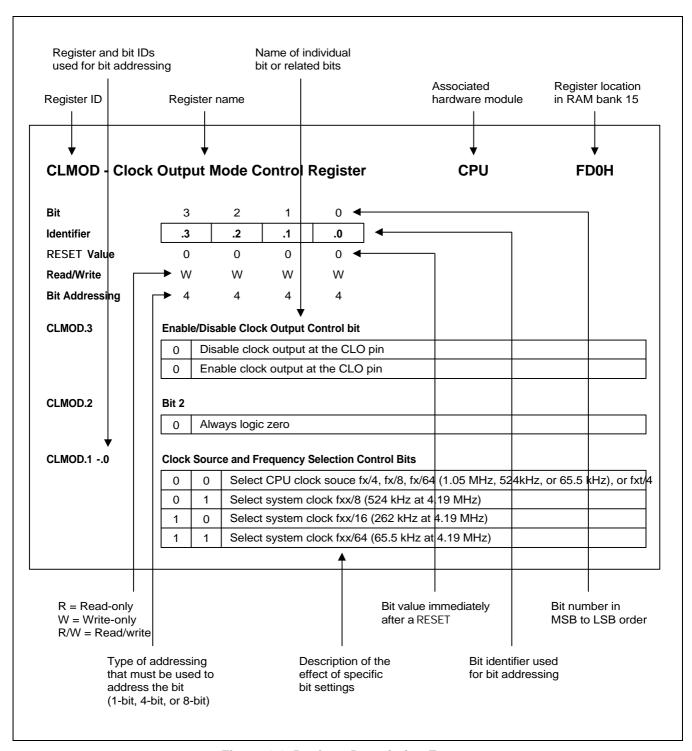

Table 4-1. I/O Map for Memory Bank 15