### THE ADVANCED 64-BIT WINDOWS-95 AND DIRECTDRAW ACCELERATOR

### **1. INTRODUCTION**

The MX86250 is a new generation of fully integrated graphics and video accelerator. On a single chip, it integrates a 64-bit graphics CoProcessor, a true-color video processor, 135 MHz RAMDAC and dual programmable clock synthesizer. The MX86250 not only delivers extreme high performance in conventional GUI acceleration, it also provides very rich functionality for motion video applications. The MX86250 true color video processor allows full screen full motion playback of AVI and MPEG video from software based Codec's such as MPEG, Cinepak and Indeo. For even higher quality MPEG video playback, the MX86250 Media port supports the VMI connector linking to an external MPEG-1 decoder chip. The Media port also provides for playback and capture of live video input from TV tuner or video camera.

One key design goal of the MX86250 is to achieve the highest possible memory bandwidth in the display memory subsystem using main stream and cost effective EDO DRAM chips. By applying the RISC design technique of super pipelining, the MX86250 graphics

#### **1.1 FEATURES**

High Performance 64 bit Graphics CoProcessor www.DataSheet4U.com

- Uniformly accelerated graphics operations in all pixel formats : 256 color, High color and True color

- Optimized graphics engine for BitBLTs, rectangle fill, pattern fill, line draw, color expansion, text transfer, and clipping

- Raster Operations (ROPs) with 3 operand BitBLT ALU

- One chip 8x8x24 pattern memory achieves highest thrughput in the most common BitBLT in Windows the Pattern BLT

- Deep on-chip Source and Destination FIFOs for sus tained burst cycles in BitBLTs

- Double buffered CoProcessor registers allows concur rent processing with CPU

- Built in Hardware cursor

#### Extremely high bandwidth

Achieves single clock cycle DRAM access in Graphics Processor, Video Processor and Display Processor CoProcessor can execute one bitblt operation in every clock cycle. When running at 50 Mhz and above, using -50 or faster EDO DRAM (20ns page mode cycle time), the bandwidth can reach 400 MB/sec and above. This extremely high bandwidth gives top-notch Windows GUI performance and fast frame rate in motion video playback.

For mainstream software Codec delivered video playback, the MX86250 provides video acceleration by a second generation" video processor consisting of YUV to RGB converter, scaler, and two dimensional bilinear filter. The scaler can zoom the video windows at arbitrary ratios. The bilinear filter provides both horizontal and vertical interpolation which is absent from 1st generation video chips.

For Windows 95 Games, the MX86250 supports DirectDraw with a rich set of features such as fast transparent Blts, double buffering and page flipping so that Windows 95 based games can achieve high speed sprite animation.

- Provides 400 MB/sec memory bandwidth using -50 EDO DRAM chips

- Even higher performance can be achieved by using -35 EDO DRAM for 533 MB/sec bandwidth which is comparable to synchronous DRAM

#### Fully Integrated for Lower system cost

- Integrated 24 bit True Color RAMDAC supports 135 Mhz pixel rate and 256x18 look-up table with High Color and True color bypass mode support

- Integrated dual clock synthesizers

- Glueless PCI local bus interface

- Two wire interface to EEPROM, VESA DDC inter face or I<sup>2</sup>C channel

#### **Flexible Display Memory configuration**

- 1,2, or 4 MB display memory.

- 256K x 4, 256K x 8, and 256K x 16 dual CAS or dual WE DRAM.

- Fast-page and Hyper-page EDO

#### **Motion Video Codec Acceleration**

- YUV/YCrCb conversion of industry standard YUV 4.2.2 or 2.1.1 formats

- Non-integer zoom in both X and Y direction

- Interpolation with Bi-linear filters in both Horizontal and Vertical dimensions

- Color Key supports video overlay, Chroma key sup ports transparency effect or blue screen video

- Edge Blending for smooth looking Blue screen video

- Video window is double buffered for smooth video play back.

- Independent video window mode allowing true-color video, independent of graphics color depth.

#### Windows 95 Game acceleration

- Designed to accelerate Windows 95 DirecDraw for game acceleration

- Fast Transparent BitBLT for sprite animation

- Linear access to offscreen DirectDraw surface storing multiple sprites

- Double buffer to support page flipping which is syn chronized to vertical retrace

## Media Port interface to MPEG decoder chips or Video Capture frontend

Glueless interface to VMI (Video Module Interface) connector to allow plug-in daughtercard of hardware

www.DatasMPEEG.cbisupport

- Glueless interface to Phillips 7110 for live video input

- Dual aperture for simultaneous access to display memory from Graphics and Video

- Built in FIFO and flexible decimator

#### High speed PCI local bus

- Support zero wait state PCI burst cycles for maximum CPU write bandwidth

- Support version 2.1 PCI disconnect and retry cycles to free CPU from status polling overhead

- · level command and data FIFO

#### **Unified Memory Architecture (UMA) support**

- Support VESA UMA (VUMA) standard

- Programmable wait states in DRAM access cycles to work with slower main memory DRAM chips

- DRAM interface buffers have programmable drive strength for optimal power versus performance tradeoff

#### **Extended Display Resolution support**

- 1600x1200, 64K color (int)

- 1280x1024, 64K color @ 75 Hz

- 1024x768, 16M color @ 60 Hz

#### "Green PC"" power management

- Support VESA DPMS (Display Power Management) standard

- Built in advanced power management techniques such as internal DAC power down mode and clock idle modes

#### **Multiple peripheral interfaces**

- VESA Display Data Channel (DDC-2B) protocol support

- Two wire EEPROM interface

- I<sup>2</sup>C channel

- VESA standard and advanced Feature Connector (VAFC) Support

- General purpose I/O pins

#### Complete Hardware compatibility

- Windows 95 Plug and Play compliant

- VGA Hardware, register, and BIOS compatible

- PCI revision 2.1 compatible

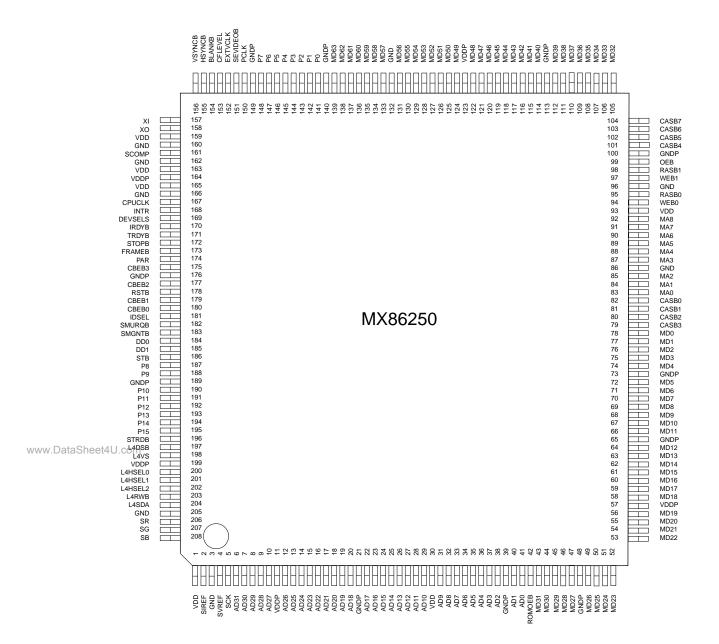

#### Low-Power 0.5 um CMOS technology

208 pin PQFP package

### **2.**Functional Description

This chapter describes the architecture and function blocks of te architecturtecture and function blocks of the MX86250.

#### 2.1 Overview

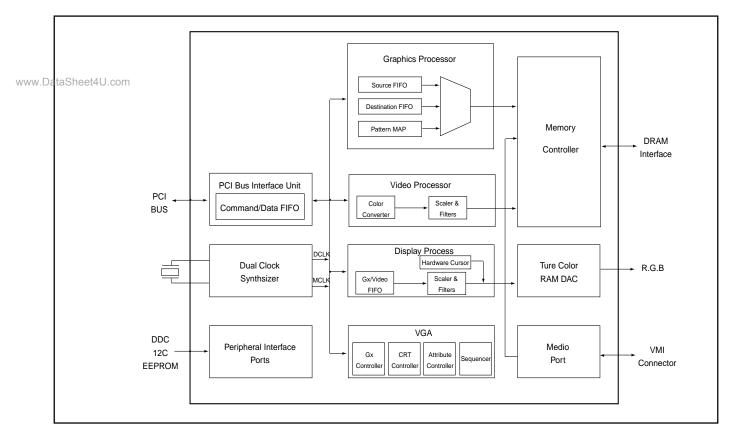

The MX86250 architecture is described in Figure 2.1, MX86250 function block diagram. As shown in the diagram, the major function blocks are as follows :

- 64 bit Graphics Co-processor

- Memory Controller

- PCI Bus Interface Unit

- Video Processor

- Media Port

- True color RAMDAC

- Dual Clock Synthesizer

- DDC/I<sup>2</sup>C/EEPROM interface ports

- VGA Controller

The function block modules are connected with 64-bit buses. Multiple FIFOs buffer data flows within the tight pipeline structures allowing concurrent operations and maximum bandwidth.

#### Figure 1 : MX86250 Function Block Diagram

#### 2.2 64-BIT Graphics Co-processor

The MX86250 Graphics Co-processor accelerates common Graphics User Interface drawing functions , including Bitblt, Rectangle Fill, Pattern Fill, Bresenham Line Draw, and Text Transfer. Hardware clipping and hardware cursor further reduce software driver overhead, including Bitblt, Rectangle Fill, Pattern Fill, Bresenham Line Draw, and Text Transfer. Hardware clipping and hardware cursor further reduce software driver overhead to the minimum.

The Graphics Co-processor supports scrardware cursor further rr further reduce software driver overhead to the minimum.

The Graphics Co-processor supports screen widths of 640, 800, 1024, 1152, 1280, 1600 and 2048. Pixel depth can be 8, 16, and 32 bits. The display memory size can be 1,2 or 4 megabytes. All Co-processor drawing operations are programmed with 32 bit registers in a linear address aperture.

#### **Three Operand Bitblt**

www.D

The Graphics Co-processor executes Bitblt operations between three operands: the Source bitmap, the Destination bitmap, and the Pattern bitmap. There are 256 operations on bitmaps, called Raster Operations (ROP). An ALU with three operand inputs is implemented to execute any of the 256 ROP's in a single cycle, unlike earlier generation GUI chips which used only two operands and implemented only 16 ROPs. This forced the software driver to decompose those 3-operand bitblt into two or three 2-operand BitBLTs significantly slowing down the drawing process.

#### **Source/Destination FIFOs**

The three inputs to the Bitblt ALU are from the Source FIFO, the Destination FIFO and the Pattern Map Buffer. The Source and Destination FIFO are 64 bit wide and 8 levels deep. They allow the fetch cycles for Source and Destination pixels to be run in page mode cycles. By having Destination FIFO, the MX86250 can run Destination read-modify-write operations in page mode reads followed by page mode writes which is substantially faster than the read-modify-write cycles in an EDO-DRAM based system.

#### Pattern Map Buffer

The most common Bitblt operation in Windows is the PatBlt which means painting a large window background using a brush which is an 8 by 8 pattern bitmap. Many GUI chips store the brush pattern bitmap in offscreen memory. During Patblt, the pattern are fetched repeatedly.

To accelerate Patblt, the MX86250 has on-chip memory to store a full 8 by 8 pattern bitmap. Unlike others which can only store 8-bit pixels, The MX86250 can store pixel maps of 8, 16, and 32 bit pixels. This complete implementation of Pattern Map, enables the MX86250 to execute the Patblts at peak memory bandwidth using a long burst of page mode writes and thus achieving the best drawing performance.

#### Text / Font drawing acceleration

Drawing text characters or fonts are another very common Windows drawing operation. The fonts are monochrome bitmaps that get expanded into color pixel maps in the Graphics Co-processor. The MX86250 optimizes this process in several ways.

Font bitmaps can be stored in system memory and transferred to the Co-processor for color expansion. The MX86250 provides a screen port to facilitate this memory to screen transfer. The screen port is mapped in a linear address aperture of 64K bytes. The monochrome font pixels are buffered in the Source FIFO so that concurrent operations are enabled for font transfer from system memory and color expansion in the Co-processor. The display driver can also cache font bitmaps in offscreen memory using the so called font-cache scheme. The MX86250 provides direct support of offscreen packed monochrome bitmap to color map expansion. This operation greatly accelerates the performance of font cache.

#### Windows 95 Direct Draw acceleration

Windows 95 Direct Draw is aimed to turn the Windows GUI environment into a Game platform with high speed sprite animation. The key to sprite animation is Transparent Blt. The MX86250 implements a flexible Color Key mechanism to enable high speed Transparent Blt. A Transparent Blt writes to screen a source bitmap, that is, a sprite, which is in an irregular shape such as a cartoon

figure. The background pixels which should not be overwritten are coded in the special Key color. The Color Compare function block in the Graphics Co-processor checks each pixel against the Key color. If a match is found, the pixel is not written, preserving the background around the sprite. Thus, an irregular shape is BLTed using a fast rectangle draw.

In the MX86250, the Color Key can be in the Source or the Destination bitmap. Transparent Blt uses Source Color Key. The Destination Color Key can be used to protect screen areas. A mask register is defined to allow the key color be a range of color values instead of a single value.

#### 2.3 Memory Controller

The MX86250 Memory Controller module interfaces to the frame buffer DRAM chips which can operate in either fast page mode, or Extended Data Out (EDO) mode. The frame buffer size can be 1, 2, or 4 Megabytes. Industry standard 256K by 4, by 8, or by 16 DRAM chips are supported. The Memory Controller performs the page mode cycle in either 2 clock cycle or 1 clock cycle, depending on the DRAM types being used. The highest bandwidth is delivered using -50 EDO DRAM with 20 ns page cycle time and a 50 MHz memory clock, yielding a 400MB peak bandwidth. The MX86250 is capable of even higher Memory clock speed. As faster EDO DRAM (-35 with 15ns page mode cycle time) enters volume production, www.DatherMX86250 will deliver 533 MB/sec bandwidth which is comparable to premium priced DRAMs such as 66 Mhz SGRAM / SDRAM, or RAMBUS RDRAM.

The center of the Memory Controller is an intricate arbiter which receives memory access requests from the Graphics Co-processor for Bitblt cycles, the Display controller for screen fetch, the Video Processor for video playback, the PCI Bus interface for CPU access, the Hardware Cursor for cursor bitmap fetch, and the DRAM refresh cycle request. The arbiter allocates memory cycles according to priority. For example, the Display Processor has higher priority than the Graphics Co-processor.

A 32-level 64-bit FIFO is implemented to buffer the pixels fetched from display memory for the screen refresh and video playback. The FIFO entries can be flexibly allocated between three different processors: Graphics, Video line 1 and Video line 2. This flexibility works to optimize performance across various screen resolutions and video playback operations. The Memory Controller generates all DRAM cycles. Its logic is carefully designed to optimize DRAM cycle timing parameters. For example, the DRAM entry cycle which is the time from RAS precharge to the end of first CAS cycle is optimized to the minimum of 4 clock cycles, versus the commonly seen 5 or 6 clock cycles in other GUI chips. Another example is that of EDO DRAM read cycle. The MX86250 eliminates the one extra clock cycle at the end of page mode cycles.

#### **Unified Memory Architecture**

The MX86250 fully supports the VESA Unified Memory Architecture (VUMA) standard. The Memory Controller implements the VUMA standard RQ/GNT state machine which supports two request priorities. Bus parking is provided to minimize bus switch overhead. DRAM read and write operations in UMA mode can have programmable number of wait states to accommodate the wide variation in main system DRAM module access speed. In addition, the DRAM interface drivers have programmable drive strength to work with wide range of DRAM interface loading on system motherboards.

#### 2.4 PCI Bus Interface Unit

The MX86250 Bus Interface Unit (BIU) implements a glueless connection to industry standard PCI local bus which is compliant with Windows 95 Plug'n'Play requirement.

PCI bus speed can be up to 33 MHz. For peak transfer rate between host CPU and the MX86250, zero wait state PCI burst cycles are supported. The resultant 133 MB per second bandwidth greatly enhances the performance level of Graphics intensive software such as Windows GUI and AutoCAD that do lots of direct accesses to video memory.

The BIU has an 8 level command and data FIFOs to buffer host transfers and enables concurrent operations of the host CPU, the graphics engine and the Video Processor. The PCI Rev. 2.1 disconnect and retry protocol is fully supported eliminating the delays of host CPU polling for BIU FIFO status.

#### 2.5 Video Processor

The MX86250 Video Processor accelerates the playback of AVI or MPEG video decoded by a software Codec such as Cinepak, Indeo, or MPEG-1. Profiling of the task load showed that about one third time each is spent in decompression, color conversion and pixel transfer to screen. The Video Processor implements the color conversion and pixel transfer in hardware, leaving only the decompression task to CPU. Thus, the video play frame rate which used to be 8 to 10 fps from software Codec is approximately tripled to the full motion rate of 30 fps by the MX86250.

Video clips are typically in QCIF or CIF format which are relatively small when viewed on the SVGA display. It is very desirable to scale up the video window to at least 640x480 or even full screen at 1024x768. The scale up can be just duplicating the pixels (Zoom) which produces blocky pictures. In high end broadcast quality video processing, a smoothing filter is typically used to remove the blocky artifacts. The MX86250 Video Processor implements both Scaler and smoothing Filters so that full motion video can play in full screen without degradation.

#### Horizontal and Vertical interpolation

The Video Processor performs the filtering in both Horizontal and Vertical dimension. While most first generation Video chips only have one horizontal filter. The MX86250 provides three filters to fit the particular needs of different video decoders. The vertical interpolation filter further enhances the appearance of video images by eliminating staircasing diagonal lines and illegible text commonly seen in video played by 1<sup>st</sup> generation video chips.

#### **Pixel Formats**

www.D

The Video Processor supports many pixel formats. The Video pixels can be in RGB formats such as KRGB-1.5.5.5, RGB-5.6.5, XRGB-8.8.8. The KRGB has 1 key bit which works as a color key. More likely, the video pixels are in YUV format such as YUV-16 (4:2:2), YUV-8 (2:1:1), or YCbCr-16 (4:2:2). The YUV format pixel has a range of value from 0 to 255, while the YCbCr format pixel values are in the range of 16 to 240.

#### **Direct Draw feature support**

The Video Processor fully support Windows 95 Direct Draw with features such as Chroma Key, Page flipping and Blending.

The Chroma key is designed for Blue Screen video which is very useful in games where video sprites are employed. The new Indeo 4.0 transparency feature also makes heavy use of the Chroma key mechanism.

The video window can be double-buffered to avoid tearing. The Video Processor executes page flipping in synchronization with Vertical blanking. A status bit is provided to inform software of the completion of page flipping.

#### Edge Blending

The MX86250 "edge blending" is an unique new feature. It is implemented to enhance the edge quality of Chroma keyed video sprites. DirectDraw does provide API calls which support the use of edge blending.

The Blending feature provides 16 levels of alpha mixing of the video and graphics window. This can be used to do a very smooth dissolve or fade which are popular visual effects often used in edutainment titles.

#### 2.6 Media Port

The Media Port is a direct interface to MPEG and Video decoders. A MX86250 based graphics card can deliver very extensive multimedia functionality by fully utilizing the Media Port. An MPEG-1 decoder chip can be incorporated on board to deliver higher quality MPEG video. Video Front end such as the Philips SA7110 can be built in for Video Capture and live TV window.

The Media Port can accept pixel data streams from either the pixel port or the PCI bus interface. The pixel data stream pass through a FIFO before it gets written into the frame buffer. A flexible decimation unit can be used to reduce the input video frame size – usually required for capturing camera input.

The video window for Media Port video stream is also double buffered for anti-tearing. Interlaced video input can be captured in two ways: one field only, or converted to non-interlaced frame.

#### VMI connector

To support a wide variety of Video and MPEG decoders, the Media Port supports the VMI (Video Module Interface) standard. The VMI specifies a 40-pin connector which, in addition to the VGA connector, contain an 8-bit YUV pixel bus and an 8-bit Host data bus. The pixel bus transfers 8-bit packed format YUV pixels from Video decoders to the Media port. The host bus transfers compressed MPEG data stream from the Media Port to the MPEG decoder chip. A small daughter card carrying the decoder chip plugs into the 40 and 26 pin connectors.

To support the Philips 7110 chip 16-bit YUV pixel format. the MX86250 Media Port has a special mode where the VMI host bus pins are used for the upper 8 bits of YUV pixels.

#### 2.7 True Color RAMDAC

The MX86250 internal 24 bit RAMDAC provides three 256-entry 6-bit word color look-up table (LUT) RAMs feeding three 8-bit DACs for 8-bit per pixel modes. A clock doubled mode is also provided. A 24 bit LUT bypass is used in High Color (15/16 bits/pixel) and True Color (24 bits/pixel) modes.

The RAMDAC works at pixel clock rate up to 160 MHz. Many high resolution display modes are possible at this high pixel clock rate. For example, with a 2 MB card, the following video mode provides flicker free displays,

> 1280x1024, 256 color, @80 Hz 1024x768, 64K color, @120 Hz 800x600, 16M color, @120 Hz

#### 2.8 Dual Clock Synthesizers

The MX86250 contains two phase locked loop (PLL) frequency synthesizers. They generate the dot clock (DCLK) for display logic and memory clock (MCLK) for memory controller and graphics engine.

Each PLL scales the input reference frequency to a programmed clock frequency. The reference frequency comes from either the crystal oscillator across the XIN and Xout pin or from a clock input from XIN pin. The PLL generate its output clock frequency based on two programmed values, the M and N value, and according to the following formula :

$f_{OUT} = f_{REF} * (M+2) / (N+2) * 2^{R}$ where R is the 2 bit scale value.

#### 2.9 Peripheral Interface ports

The MX86250 has interface ports designed to support the VESA DDC monitor interface, the I<sup>2</sup>C channel, and serial EEPROM.

#### **VESA DDC standard**

The VESA DDC (Display Data Channel) standard specifies a two pin serial channel between the display monitor and the graphics controller. The display monitor sends its capability and configuration datum to the graphics controller chip for the display driver to set up video display mode accordingly. Windows 95 Plug'n'Play interface for display monitors is based on the DDC standard. The MX86250 provides fully compliant implementation of the DDC using the DD0 and DD1 pin.

#### I<sup>2</sup>C and EEPROM support

The I<sup>2</sup>C channel is also a two pin serial bus as defined by Philips. Many video components such as the SA7110 video decoder relies on the I<sup>2</sup>C channel. The MX86250 provides the SCK and SDA pin for interface to I<sup>2</sup>C channel.

Some graphics cards are designed to store certain card configuration or setup information in non-volatile memory storage. The MX86250 can support such a card using serial EEPROM. The DD0 and DD1 pin can be programmed to form an interface to serial EEPROM chips.

#### 2.10 Power-on Reset Strapping

#### MD[3:0]: RASTCTRL[3:0]

These 4 bits are used for RAS precharge/low timing controls. The selection is listed below :

| RASTCTRL[3:0] | RAS precharge | RAS low   |

|---------------|---------------|-----------|

|               | (in MCLK)     | (in MCLK) |

| 0000          | 3.5           | 5.5       |

| 0001          | 3.5           | 4.5       |

| 0010          | 3.5           | 3.5       |

| 0011          | 2.5           | 4.5       |

| 0100          | 2.5           | 3.5       |

| 0101          | 2.5           | 2.5       |

| 0110          | 1.5           | 3.5       |

| 0111          | 1.5           | 2.5       |

| 1000          | 3             | 6         |

| 1001          | 3             | 5         |

| 1010          | 3             | 4         |

| 1011          | 2             | 5         |

| 1100          | 2             | 4         |

| 1101          | 2             | 3         |

| 1110          | Reserved      | Reserved  |

| 1111          | Reserved      | Reserved  |

|               |               |           |

www.DaMD[5:4]UDRAMCYC[1:0]

| DRAMCYC[1:0] | DRAM CYCLES                   |

|--------------|-------------------------------|

| 00           | 2 cycles Fast Page DRAM cycle |

| 01           | 2 cycles EDO DRAM cycle       |

| 10           | 1 cycles EDO DRAM cycle       |

| 11           | Reserved                      |

MD6: DUALCAS 0--Dual WE DRAM 1--Dual CAS DRAM

MD7: ENUMA 0--Disable UMA 1--Enable UMA

MD8: Reserved

MD9: Reserved

#### MD10: MA9OUTSE

This is used to select MA9 output pin if UMA is enabled. 0--MA9 output through WEB1 1--MA9 output through OEB

MD11: Reserved

MD12: EXTMCLK

0--Use internal MCLK

1--Use external MCLK. For UMA, external MCLK will come from CPU clock.

#### MD13: EXTDCLK

0--Use internal DCLK 1--Use external DCLK

#### MD14: FC8

0--16-bit or No Feature Connector 1--8-bit Feature Connector

#### MD15: ENSTVW

0--Stereo View off.

1--Enable Stereo View. DD1 is used for stereo view control. DD1 is high for odd field, low for even field during interlaced display.

For non-interlaced display, DD1 is always low.

#### MD16: RETRYOFF

0--Enable Bus Retry.

1--Disable Bus Retry.

#### MD17: CROMRETRYOFF

- 0--Enable disconnect function for Configuration and ROM accesses.

- 1--Disable disconnect function for Configuration and ROM accesses.

## 2.11 Pin Description

#### **PCI Bus Interface Pins:**

|        | Pin Name        | Pin No. | Type | Description                                                                            |

|--------|-----------------|---------|------|----------------------------------------------------------------------------------------|

|        | RSTB#           | 178     |      | This input is PCI bus RESET#, it is an active low signal used to initialize the GUI    |

|        | NOTD#           | 170     | I    |                                                                                        |

|        |                 |         |      | to a known state. The trailing edge of this input loads the power on strapping inputs  |

|        |                 |         |      | through MD0 to MD17. The power on strapping input pins each has an internally          |

|        |                 |         |      | weakly pulled down resistor (about 50K Ohm). If a power on reset input status "0"      |

|        |                 |         |      | is needed, then the corresponding pin doesn need an externally pulled up resistor.     |

|        |                 |         |      | If a power on reset input status "1"is needed, then the corresponding pin must be      |

| ,      |                 |         |      | pulled up by a 10K Ohm resistor.                                                       |

|        | CPUCLK          | 167     | Ι    | This input is the PCI bus clock. It is an 1X clock of 33MHz.                           |

|        | FRAMEB          | 173     | I    | This input is FRAME#, it is low to indicate the GUI that a valid address is present    |

|        |                 |         |      | on the PCI address bus and a New bus cycle or Burst bus cycles are starting.           |

|        |                 |         |      | When sampling this signal low, GUI would latch the address and bus commands.           |

|        | IRDYB           | 170     | I    | This input is Initiator RDY#, it is generated from an PCI Bus Master. When it is       |

|        |                 |         |      | low, IRDYB indicates that the Initiator is able to complete the current bus            |

|        |                 |         |      | transaction if and only if the TRDY# is also low.                                      |

| ,      | TRDYB           | 171     | STO  | This output is Target RDY#, it is generated by GUI if the current bus cycle            |

|        |                 |         |      | belongs to the GUI. When it is low, TRDY# indicates that the GUI is able to            |

|        | taSheet4U.com   |         |      | complete the current bus transaction which already targeted onto it if and only if     |

| www.Da | 1431166140.0011 |         |      | the IRDY# is also low. It remains low until this current cycle ends, then goes into    |

|        |                 |         |      | high for one PCI clock cycle, after that then goes into tri-state.                     |

|        | DEVSELB         | 169     | STO  | This output is DEVSEL#. When driven low, it indicates that GUI will respond to the     |

|        |                 |         |      | current cycle. It remains low until this current cycle ends, then goes into high for   |

|        |                 |         |      | one PCI clock cycle, after that then goes into tri-state.                              |

|        | STOPB           | 172     | STO  | This output is STOP#. When driven low, it indicates that GUI will request the          |

|        |                 |         |      | current bus master to stop the current bus transfer.                                   |

|        |                 |         |      | There are two configurations about this signal. One is called disconnect. Under        |

|        |                 |         |      | this configuration, GUI will complete the current transaction as the last one. In this |

|        |                 |         |      | case, STOP# will be active at the same time that TRDY# is active. The other            |

|        |                 |         |      | configuration is called retry. In this case, GUI just request the bus master to        |

|        |                 |         |      | terminate the current cycle and retry again. TRDY# will not be generated in this       |

|        |                 |         |      | cycle. Once asserted, it remains low until this current cycle ends then goes into      |

|        |                 |         |      | high for one PCI clock cycle, after that then goes into tri-state.                     |

|        |                 |         |      | nightor one For clock cycle, alter that then goes into the state.                      |

## PCI Bus Interface Pins:(continued)

|        | Pin Name       | Pin No. | Туре | Description                                   |                                                                     |

|--------|----------------|---------|------|-----------------------------------------------|---------------------------------------------------------------------|

|        | PAR            | 174     | ТО   | This output is PAF                            | R. It is only driven during PCI bus master doing read accesses      |

|        |                |         |      | from GUI. When c                              | driven, it will provide an even parity across the AD[31:0], and     |

|        |                |         |      | C/BE#[3:0]. This s                            | signal is an tri-state output.                                      |

|        | INTRB          | 168     | то   | This output is INT                            | A#. It is and interrupt request signal to system interrupt          |

|        |                |         |      | controller. This sid                          | gnal always hard wired to the PCI bus INTA# signal pin. It is an    |

|        |                |         |      | -                                             | but. This pin is typically unused in display subsystem design, but  |

|        |                |         |      |                                               | d to IRQ9 via PCI configuration register.                           |

|        | IDSEL          | 181     | 1    | -                                             | EL. It is used as an Initialization Device Select during PCI bus    |

|        | IDSEL          | 101     | I    |                                               |                                                                     |

|        |                |         |      | -                                             | n cycles. When high, it indicates that GUI is now selected as a     |

|        |                |         |      | -                                             | configuration cycles.                                               |

|        | CBE0#          | 180     | I    | This multiplexed in                           | nput is part of a PCI bus Command definition or a Byte Enable for   |

|        |                |         |      | byte lane 0. Durin                            | g address phase of a PCI bus transaction, it defines the            |

|        |                |         |      | Command. During                               | g data phase of a PCI bus transaction, it defines if byte lane 0 is |

|        |                |         |      | engaged in the tra                            | ansfer or not.                                                      |

|        | CBE1#          | 179     | I    | This is bit 1 of bus command and byte enable. |                                                                     |

|        | CBE2#          | 177     | I    | This is bit 2 of bus                          | s command and byte enable.                                          |

|        | CBE3#          | 175     | 1    | This is bit 3 of bus                          | s command and byte enable.                                          |

|        |                |         |      | The PCI bus Com                               | nmands supported are listed below:                                  |

| www.Da | ataSheet4U.com |         |      | C\BE[3:0]#                                    | PCI bus Command Type                                                |

|        |                |         |      | 0000                                          | (Interrupt Acknowledge)                                             |

|        |                |         |      | 0001                                          | (Special Cycle)                                                     |

|        |                |         |      | 0010                                          | I/O Read                                                            |

|        |                |         |      | 0011                                          | I/O Write                                                           |

|        |                |         |      | 0100                                          | reserved                                                            |

|        |                |         |      | 0101                                          | reserved                                                            |

|        |                |         |      | 0110                                          | Memory Read                                                         |

|        |                |         |      | 0111                                          | Memory Write                                                        |

|        |                |         |      | 1000                                          | reserved                                                            |

|        |                |         |      | 1001                                          | reserved                                                            |

|        |                |         |      | 1010                                          | Configuration Read                                                  |

|        |                |         |      | 1010                                          | Configuration Write                                                 |

|        |                |         |      | 1100                                          | Memory Read Multiple                                                |

|        |                |         |      | 1101                                          | (Dual Address Cycle)                                                |

|        |                |         |      | 1110                                          | Memory Read Line                                                    |

|        |                |         |      |                                               |                                                                     |

## PCI Bus Interface Pins:(continued)

|           | Pin Name  | Pin No. | Туре | Description                                                                  |

|-----------|-----------|---------|------|------------------------------------------------------------------------------|

|           | AD0       | 41      | I/O  | AD[31:0] is the multiplexed Address and Data bus for PCI, which 32-bit wide. |

|           | AD1       | 40      |      |                                                                              |

|           | AD2       | 38      |      |                                                                              |

|           | AD3       | 37      |      |                                                                              |

|           | AD4       | 36      |      |                                                                              |

|           | AD5       | 35      |      |                                                                              |

|           | AD6       | 34      |      |                                                                              |

|           | AD7       | 33      |      |                                                                              |

|           | AD8       | 32      |      |                                                                              |

|           | AD9       | 31      |      |                                                                              |

|           | AD10      | 29      |      |                                                                              |

|           | AD11      | 28      |      |                                                                              |

|           | AD12      | 27      |      |                                                                              |

|           | AD13      | 26      |      |                                                                              |

|           | AD14      | 25      |      |                                                                              |

|           | AD15      | 24      |      |                                                                              |

|           | AD16      | 23      |      |                                                                              |

|           | AD17      | 22      |      |                                                                              |

|           | AD18      | 20      |      |                                                                              |

|           | AD19      | 19      |      |                                                                              |

|           | AD20      | 18      |      |                                                                              |

| www.Datas | sAD21.com | 17      |      |                                                                              |

|           | AD22      | 16      |      |                                                                              |

|           | AD23      | 15      |      |                                                                              |

|           | AD24      | 14      |      |                                                                              |

|           | AD25      | 13      |      |                                                                              |

|           | AD26      | 12      |      |                                                                              |

|           | AD27      | 10      |      |                                                                              |

|           | AD28      | 9       |      |                                                                              |

|           | AD29      | 8       |      |                                                                              |

|           | AD30      | 7       |      |                                                                              |

|           | AD31      | 6       |      |                                                                              |

#### DRAM INTERFACE PINS:

|           | Pin Name   | Pin No. | Туре | Description                                                                          |

|-----------|------------|---------|------|--------------------------------------------------------------------------------------|

|           | RASB0      | 95      | ТО   | This output is RAS0#, it is the RAS address strobe for bank 0, i.e. the first 2MB of |

|           |            |         |      | 4MB DRAM memory. Dual CAS or dual WE of fast page or EDO DRAM can be                 |

|           |            |         |      | supported.In UMA interface, this output will be tristated if GUI is not granted to   |

|           |            |         |      | access the memory bus.                                                               |

|           | RASB1      | 98      | то   | This output is RAS1#, it is the RAS address strobe for bank 1, i.e. the second 2MB   |

|           |            |         |      | of 4MB DRAM memory. In UMA interface, this output will be tristated if GUI is not    |

|           |            |         |      | granted to access the memory bus.                                                    |

|           | CASB0      | 82      | ТО   | For dual CAS DRAM type configuration, this output is CAS0#. It is the CAS            |

|           |            |         |      | address strobe of byte lane 0.                                                       |

|           |            |         |      | For dual WE DRAM type configuration, this output is WE0#, it is the WE# control      |

|           |            |         |      | signal of byte lane 0.                                                               |

|           |            |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the  |

|           |            |         |      | memory bus.                                                                          |

|           | CASB1      | 81      | ТО   | For dual CAS DRAM type configuration, this output is CAS1#. It is the CAS            |

|           |            |         |      | address strobe of byte lane 1.                                                       |

|           |            |         |      | For dual WE DRAM type configuration, this output is WE1#, it is the WE# control      |

|           |            |         |      | signal of byte lane 1.                                                               |

|           |            |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the  |

| www.DataS | heet4U.com |         |      | memory bus.                                                                          |

|           | CASB2      | 80      | ТО   | For dual CAS DRAM type configuration, this output is CAS2#. It is the CAS            |

|           |            |         |      | address strobe of byte lane 2.                                                       |

|           |            |         |      | For dual WE DRAM type configuration, this output is WE2#, it is the WE# control      |

|           |            |         |      | signal of byte lane 2.                                                               |

|           |            |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the  |

|           |            |         |      | memory bus.                                                                          |

|           | CASB3      | 79      | то   | For dual CAS DRAM type configuration, this output is CAS3#. It is the CAS            |

|           |            |         |      | address strobe of byte lane 3.                                                       |

|           |            |         |      | For dual WE DRAM type configuration, this output is WE3#, it is the WE# control      |

|           |            |         |      | signal of byte lane 3.                                                               |

|           |            |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the  |

|           |            |         |      | memory bus.                                                                          |

| Pin Name | Pin No. | Туре | Description                                                                         |

|----------|---------|------|-------------------------------------------------------------------------------------|

| CASB4    | 101     | то   | For dual CAS DRAM type configuration, this output is CAS4#. It is the CAS           |

|          |         |      | address strobe of byte lane 4.                                                      |

|          |         |      | For dual WE DRAM type configuration, this output is WE4#, it is the WE#             |

|          |         |      | control signal of byte lane 4.                                                      |

|          |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|          |         |      | memory bus.                                                                         |

| CASB5    | 102     | ТО   | For dual CAS DRAM type configuration, this output is CAS5#. It is the CAS ad        |

|          |         |      | dress strobe of byte lane 5.                                                        |

|          |         |      | For dual WE DRAM type configuration, this output is WE5#, it is the WE#             |

|          |         |      | control signal of byte lane 5.                                                      |

|          |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|          |         |      | memory bus.                                                                         |

| CASB6    | 103     | ТО   | For dual CAS DRAM type configuration, this output is CAS6#. It is the CAS ad        |

|          |         |      | dress strobe of byte lane 6.                                                        |

|          |         |      | For dual WE DRAM type configuration, this output is WE6#, it is the WE# control     |

|          |         |      | signal of byte lane 6.                                                              |

|          |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|          |         |      | memory bus.                                                                         |

| CASB7    | 104     | то   | For dual CAS DRAM type configuration, this output is CAS7#. It is the CAS           |

|          |         |      | address strobe of byte lane 7.                                                      |

|          |         |      | For dual WE DRAM type configuration, this output is WE7#, it is the WE# control     |

|          |         |      | signal of byte lane 7.                                                              |

|          |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|          |         |      | memory bus.                                                                         |

| WEB0     | 94      | ТО   | For dual CAS DRAM type configuration, this output is WE0#. It is the WE# control    |

|          |         |      | signal of bank 0.                                                                   |

|          |         |      | For dual WE DRAM type configuration, this output is CAS0#, it is the CAS            |

|          |         |      | address strobe of bank 0.                                                           |

|          |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|          |         |      | memory bus.                                                                         |

| Pin Name          | Pin No. | Туре | Description                                                                         |

|-------------------|---------|------|-------------------------------------------------------------------------------------|

| WEB1              | 97      | то   | For dual CAS DRAM type configuration, this output is WE1#. It is the WE# contro     |

|                   |         |      | signal of bank 1.                                                                   |

|                   |         |      | For dual WE DRAM type configuration, this output is CAS1#, it is the CAS address    |

|                   |         |      | strobe of bank 1.                                                                   |

|                   |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|                   |         |      | memory bus. If GUI is granted, this has the above function when MA9OUTSE is 1.      |

|                   |         |      | If MA9OUTSE is 0, it is the MA9, which is necessary for asymmetrical DRAM.          |

| OEB               | 99      | то   | This output is OE#, it is the OE# control signal for both banks of DRAM.            |

|                   |         |      | In UMA interface, this output will be tristated if GUI is not granted to access the |

|                   |         |      | memory bus.                                                                         |

|                   |         |      | If GUI is granted, this has the above function when MA9OUTSE is 0. If MA9OUTSE      |

|                   |         |      | is 1, it is the MA9, which is necessary for asymmetrical DRAM.                      |

| MAO               | 83      | то   | The outputs MA[8:0] is the DRAM memory address bus for both banks.                  |

| MA1               | 84      |      | It is used to pass the RAS address and CAS address to DRAMs. In UMA interface       |

| MA2               | 85      |      | these outputs will be tristated if GUI is not granted to access the memory bus.     |

| MA3               | 87      |      |                                                                                     |

| MA4               | 88      |      |                                                                                     |

| MA5               | 89      |      |                                                                                     |

| w.DataSheat4U.com | 90      |      |                                                                                     |

| MA7               | 91      |      |                                                                                     |

| MA8               | 92      |      |                                                                                     |

| MD0               | 78      | I/O  | MD[7:0] is the DRAM data bus of memory plane 0 of bank 0 or bank 1.                 |

| MD1               | 77      |      | In BIOS ROM accesses, these are the data inputs[7:0] of external ROM.               |

| MD2               | 76      |      | They are also served as power-on strapping inputs.                                  |

| MD3               | 75      |      |                                                                                     |

| MD4               | 74      |      |                                                                                     |

| MD5               | 72      |      |                                                                                     |

| MD6               | 71      |      |                                                                                     |

| MD7               | 70      |      |                                                                                     |

| Pi              | in Name | Pin No. | Туре | Description                                                               |

|-----------------|---------|---------|------|---------------------------------------------------------------------------|

| M               | 1D8     | 69      | I/O  | MD[15:8] is the DRAM data bus of memory plane 1 of bank 0 or bank 1.      |

| М               | 1D9     | 68      |      | They are also served as power-on strapping inputs.                        |

| М               | 1D10    | 67      |      |                                                                           |

| М               | 1D11    | 66      |      |                                                                           |

| М               | 1D12    | 64      |      |                                                                           |

| М               | 1D13    | 63      |      |                                                                           |

| М               | 1D14    | 62      |      |                                                                           |

| М               | 1D15    | 61      |      |                                                                           |

| M               | 1D16    | 60      | I/O  | MD[23:16] is the DRAM data bus of memory plane 2 of bank 0 or bank 1.     |

| М               | 1D17    | 59      |      | MD[17:16] are also used as power-on strapping inputs.                     |

| М               | 1D18    | 58      |      |                                                                           |

| М               | 1D19    | 56      |      |                                                                           |

| М               | 1D20    | 55      |      |                                                                           |

| М               | 1D21    | 54      |      |                                                                           |

| М               | 1D22    | 53      |      |                                                                           |

| М               | 1D23    | 52      |      |                                                                           |

| M               | 1D24    | 51      | I/O  | MD[31:24] is the DRAM data bus of memory plane 3 of bank 0 or bank 1.     |

| М               | 1D25    | 50      |      | In BIOS ROM accesses, MD[31:16] are the address outputs[15:0] for externa |

| ww.DataShe<br>M | 1D26    | 49      |      | ROM.                                                                      |

| М               | 1D27    | 47      |      |                                                                           |

| М               | 1D28    | 46      |      |                                                                           |

| М               | 1D29    | 45      |      |                                                                           |

| М               | 1D30    | 44      |      |                                                                           |

| М               | 1D31    | 43      |      |                                                                           |

| M               | 1D32    | 105     | I/O  | MD[39:32] is the DRAM data bus of memory plane 4 of bank 0 or bank 1.     |

| М               | 1D33    | 106     |      |                                                                           |

| М               | 1D34    | 107     |      |                                                                           |

| М               | 1D35    | 108     |      |                                                                           |

| М               | 1D36    | 109     |      |                                                                           |

| М               | 1D37    | 110     |      |                                                                           |

| М               | 1D38    | 111     |      |                                                                           |

|                 | 1D39    | 112     |      |                                                                           |

|          | Pin Name             | Pin No. | Туре | Description                                                           |

|----------|----------------------|---------|------|-----------------------------------------------------------------------|

| _        | MD40                 | 114     | I/O  | MD[47:40] is the DRAM data bus of memory plane 5 of bank 0 or bank 1. |

|          | MD41                 | 115     |      |                                                                       |

|          | MD42                 | 116     |      |                                                                       |

|          | MD43                 | 117     |      |                                                                       |

|          | MD44                 | 118     |      |                                                                       |

|          | MD45                 | 119     |      |                                                                       |

|          | MD46                 | 120     |      |                                                                       |

|          | MD47                 | 121     |      |                                                                       |

| _        | MD48                 | 122     | I/O  | MD[55:48] is the DRAM data bus of memory plane 6 of bank 0 or bank 1. |

|          | MD49                 | 124     |      |                                                                       |

|          | MD50                 | 125     |      |                                                                       |

|          | MD51                 | 126     |      |                                                                       |

|          | MD52                 | 127     |      |                                                                       |

|          | MD53                 | 128     |      |                                                                       |

|          | MD54                 | 129     |      |                                                                       |

|          | MD55                 | 130     |      |                                                                       |

| -        | MD56                 | 131     | I/O  | MD[63:56] is the DRAM data bus of memory plane 7 of bank 0 or bank 1. |

|          | MD57                 | 133     |      |                                                                       |

| www.Data | aSheet4U.com<br>MD58 | 134     |      |                                                                       |

|          | MD59                 | 135     |      |                                                                       |

|          | MD60                 | 136     |      |                                                                       |

|          | MD61                 | 137     |      |                                                                       |

|          | MD62                 | 138     |      |                                                                       |

|          | MD63                 | 139     |      |                                                                       |

#### UMA Interface Pins:

| Pin Name | Pin No. | Туре | Description                                                                      |

|----------|---------|------|----------------------------------------------------------------------------------|

| SMURQB   | 182     | 0    | This is the MREQ# signal for VESA UMA interface. GUI uses this signal to request |

|          |         |      | memory accesses on UMA.                                                          |

| SMGNTB   | 183     | Ι    | This is the MGNT# signal from VESA UMA interface. GUI will drive DRAM            |

|          |         |      | interface signals when this signal is active in UMA configuration.               |

### **ROM BIOS Interface Pins:**

| Pin Name | Pin No | . Туре | Description                                                                  |

|----------|--------|--------|------------------------------------------------------------------------------|

| ROMOEB   | 42     | 0      | This output is ROMOE#. It may be connected to either one or both of the BIOS |

|          |        |        | ROM chip select and output enable pins directly.                             |

### Internal VCG Related Interface Pins:

| -       | Pin Name Pin No. Type |     | Туре | Description                                                                           |  |  |

|---------|-----------------------|-----|------|---------------------------------------------------------------------------------------|--|--|

| -       | XI                    | 157 | Ι    | This input is used as a Reference Frequency Input for internally implemented          |  |  |

|         |                       |     |      | oscillator.                                                                           |  |  |

| www.Dat | taSheet4U.com         |     |      | An external crystal or oscillator of 14.318Mhz may be used. If an external crystal is |  |  |

|         |                       |     |      | used, it must be connected between XIN and XOUT. If an external oscillator is         |  |  |

|         |                       |     |      | used, it must connect to XIN. In this case, the XOUT must be left open.               |  |  |

| -       | ХО                    | 158 | 0    | This is used as a Reference Frequency output for internally implemented               |  |  |

|         |                       |     |      | oscillator. If an external crystal is used, it must be connected between XIN and      |  |  |

| _       |                       |     |      | XOUT. If an external oscillator is used, the XOUT must be left open.                  |  |  |

#### Internal RAMDAC Related Interface Pins:

| Pin Name Pin No. Type                                          |           | Туре                                                                                 | Description                                                                         |  |

|----------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| SVREF                                                          | SVREF 4 I |                                                                                      | This pin is the Voltage Reference of 1.2V for internal DAC and Monitor Sence Ic     |  |

|                                                                |           |                                                                                      | It must be connected with a 0.1u capacitor to AVCC of RAMDAC.                       |  |

| SCOMP                                                          | 161       | I                                                                                    | This pin is the Compensation input for internal DAC. It must be connected with a    |  |

|                                                                |           |                                                                                      | 0.1u capacitor to AVCC of RAMDAC.                                                   |  |

| SIREF                                                          | 2         | Ι                                                                                    | This pin is the Current Reference.                                                  |  |

| SR                                                             | 206       | 0                                                                                    | This pin is the analog output of the pixel color Red component to monitor. It has a |  |

|                                                                |           |                                                                                      | voltage level of 0.0V(blank) to 0.7V(full scale) when terminated with 75 ohm double |  |

|                                                                |           |                                                                                      | loads.                                                                              |  |

| SG                                                             | 207       | 0                                                                                    | This pin is the analog output of the pixel color Green component to monitor. It has |  |

|                                                                |           |                                                                                      | a voltage level of 0.0V(blank) to 0.7V(full scale) when terminated with 75 ohm      |  |

|                                                                |           |                                                                                      | double loads.                                                                       |  |

| SB 208 O This pin is the analog output of the pixel color Blue |           | This pin is the analog output of the pixel color Blue component to monitor. It has a |                                                                                     |  |

|                                                                |           |                                                                                      | voltage level of 0.0V(blank) to 0.7V(full scale) when terminated with 75 ohm double |  |

|                                                                |           |                                                                                      | loads.                                                                              |  |

| -      | Pin Name            | Pin No | . Туре | Description                                                                        |

|--------|---------------------|--------|--------|------------------------------------------------------------------------------------|

|        | P0<br>taSheet4U.com | 141    | Ю      | P[7:0] is the pixel or video data bus from/to external Feature Connector or Video  |

| www.Da | P1                  | 142    |        | Module Interfaces.                                                                 |

|        | P2                  | 143    |        |                                                                                    |

|        | P3                  | 144    |        |                                                                                    |

|        | P4                  | 145    |        | For 8-bit Feature Connector or VAFC, this is a bidirectional pixel data bus.       |

|        | P5                  | 146    |        | When EVIDEO# is low, it functions as inputs. The pixel data from external display  |

|        | P6                  | 147    |        | or video card will be passed to the internal RAMDAC for display.                   |

|        | P7                  | 148    |        | If EVIDEO# is high, the internal RAMDAC uses pixel data internally generated for   |

|        |                     |        |        | display. In this case, if PA output control for DPMS, which is defined in bit 6 of |

|        |                     |        |        | register 3?5/26, is set to normal operation, GUI will drive out pixel data.        |

|        |                     |        |        | Otherwise, it will tristate the output.                                            |

|        |                     |        |        | If VMI is used, P[7:0] is the video data inputs.                                   |

|        |                     |        |        | This chip supports SAA7110 video decoder and CL480 MPEG decoder interfaces.        |

|        |                     |        |        | For SAA7110 interfaces, P[7:0] is the lower byte of the 16-bit video data inputs.  |

|        |                     |        |        | For CL480 interfaces, it's the 8-bit video data inputs.                            |

| -      | Pin Name                    | Pin No. | Туре | Description                                                                           |  |  |

|--------|-----------------------------|---------|------|---------------------------------------------------------------------------------------|--|--|

| -      | P8                          | 187     | IO   | P[15:8] is the pixel data bus from/to external Feature                                |  |  |

|        | P9188IOP10190IOP11191IO     |         | Ю    | Connector or host data bus from/to VMI.                                               |  |  |

|        |                             |         | Ю    |                                                                                       |  |  |

|        |                             |         | Ю    | For VAFC or 16-bit Feature Connector, P[15:8] functions as pixel output or video      |  |  |

|        | P12                         | 192     | Ю    | input. When EVIDEO# is low, it is used for video input, which will be passed to       |  |  |

|        | P13                         | 193     | Ю    | the internal RAMDAC for display. If EVIDEO# is high, the internally generated         |  |  |

|        | P14                         | 194     | Ю    | pixel data will be driven out to video card if PA output control for DPMS             |  |  |

|        | P15                         | 195     | Ю    | is set to normal operation.                                                           |  |  |

|        |                             |         |      | If VMI is used, P[15:8] is used as the host data bus, which is bidirectional. Through |  |  |

|        |                             |         |      | this bus, CPU can access the VMI module. For SAA7110 interfaces, P[15:8] is the       |  |  |

|        |                             |         |      | higher byte of the 16-bit video data inputs. For CL480, it's the 8-bit host data bus  |  |  |

|        |                             |         |      | which is inputs in read cycles, and outputs in write cycles.                          |  |  |

| -      | PCLK                        | 150     | 10   | This is the pixel clock input/output pin.                                             |  |  |

|        |                             |         |      | For 8-bit Feature Connector, it is an input when EVIDEO# is low. In this case, it is  |  |  |

|        |                             |         |      | used for internal RAMDAC display. When EVIDEO# is high, the internally                |  |  |

|        |                             |         |      | generated pixel clock is driven out through this pin.                                 |  |  |

|        |                             |         |      | For VAFC, it's always an pixel clock output. The internal pixel clock for RAMDAC is   |  |  |

|        |                             |         |      | also driven to this pin.                                                              |  |  |

| ww.Dat | taSheet4U.com               |         |      | For VMI connection, PCLK is always put in tri-state. RAMDAC use internal pixel        |  |  |

|        |                             |         |      | clock for display.                                                                    |  |  |

|        |                             |         |      | If external DCLK is used, only 8-bit Feature Connector configuration is allowed,      |  |  |

|        |                             |         |      | i.e. other video interfaces are not applicable.                                       |  |  |

|        | **** Shouls be divided by 8 |         |      | In test mode, this is the DCLK output from internal VCG.                              |  |  |

| -      | SEVIDEOB 151 I              |         |      | This is the EVIDEO# pin used as bidirection control for 8-bit Feature Connector o     |  |  |

|        |                             |         |      | VAFC interfaces. When set to 1, GUI will drive P[15:0], BLANK#, HSYNC, VSYNC          |  |  |

|        |                             |         |      | and PCLK to the Feature Connector. When set to 0, all of these signal pins are        |  |  |

|        |                             |         |      | tri-stated.                                                                           |  |  |

|        |                             |         |      | If video interface is enabled, i.e. either SAA7110 or CL480 is used for video data    |  |  |

|        |                             |         |      | input, this pin loses its function.                                                   |  |  |

| -      | EXTVCLK                     | 152     | 1    | This is the video clock input pin for video interface and VAFC. If external DCLK is   |  |  |

|        |                             |         |      | used, it is taken for external pixel clock input. In that case, video interface and   |  |  |

|        |                             |         |      | VAFC are not allowed.                                                                 |  |  |

| -      |                             |         |      |                                                                                       |  |  |

|          | Pin Name    | Pin No. | Туре | Description                                                                                   |

|----------|-------------|---------|------|-----------------------------------------------------------------------------------------------|

|          | BLANKB      | 154     | IO   | This is a multi-function pin.                                                                 |

|          |             |         |      | For 8-bit Feature Connector or VAFC, when EVIDEO# is high, the internal BLANK                 |

|          |             |         |      | signal is used to control RAMDAC display. In this case, it is an output pin if the            |

|          |             |         |      | BLANK control for DPMS, which is defined in bit [1:0] of register 3?5/26, is not se           |

|          |             |         |      | to 11. Otherwise, it will be tri-stated. When EVIDEO# is set to 0, it's an input from         |

|          |             |         |      | Feature Connector. GUI uses it to control RAMDAC display.                                     |

|          |             |         |      | For VMI or SAA7110, it's the HREF input. And for CL480 it's the HSYNC# input                  |

|          |             |         |      | In either case, it indicates that video data of a scanline is coming in.                      |

|          | HSYNCB      | 155     | то   | It's the HSYNC# output pin, which is the horizontal sync to analog monitor. For 8             |

|          |             |         |      | bit Feature Connector or VAFC, it is enabled when EVIDEO# is high and HSYNC                   |

|          |             |         |      | control for DPMS,                                                                             |

|          |             |         |      | which is defined in bit [3:2] of register 3?5/26, is set to value other than 11.              |

|          |             |         |      | Otherwise, it is tri-stated. But if either SAA7110 or CL480 is select, it is enabled          |

|          |             |         |      | also.                                                                                         |

|          | VSYNCB      | 156     | ТО   | It's the VSYNC# output pin, which is the vertical sync to analog monitor. For 8-bi            |

|          |             |         |      | Feature Connector or VAFC, it is enabled when EVIDEO# is high and VSYNC                       |

|          |             |         |      | control for DPMS, which is defined in bit [5:4] of register 3?5/26, is set to value           |