# **Low Power Dual Operational Amplifier**

## KK358

The KK358 contains two independent high gain operational amplifiers with internal frequency compensation. The two op-amps operate over a wide voltage range from a single power supply. Also use a split power supply. The device has low power supply current drain, regardless of the power supply voltage. The low power drain also makes the KK358 a good choice for battery operation.

When your project calls for a traditional op-amp function, now you can streamline your design with a simple single power supply. Use ordinary +5VDC common to practically any digital system or personal computer application, without requiring an extra 15V power supply just to have the interface electronics you need.

The KK358 is a versatile, rugged workhorse with a thousand-and-one uses, from amplifying signals from a variety of transducers to dc gain blocks, or any op-amp function. The attached pages offer some recipes that will have your project cooking in no time.

- Internally frequency compensated for unity gain

- Large DC voltage gain: 100dB

- Wide power supply range:  $3V \sim 32V \text{ (or } \pm 1.5V \sim \pm 16V)$

- Input common-mode voltage range includes ground

- Large output voltage swing: 0V DC to V<sub>CC</sub>-1.5V DC

- Power drain suitable for battery operation

- Low input offset voltage and offset current

- Differential input voltage range equal to the power supply voltage

- Possible to exchange the position of Pin9 for Pin1 because of Pin Connection being symmetric(KK358S only)

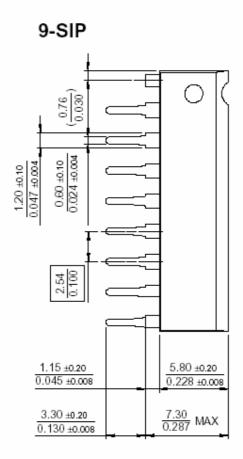

KK358D SOIC KK358S SIP-8

$T_A = -40^{\circ}$  to 85° C for all packages.

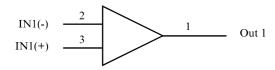

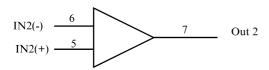

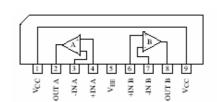

## **LOGIC DIAGRAM**

PIN 4 = GNDPIN  $8=V_{CC}$

#### PIN ASSIGNMENT

### MAXIMUM RATINGS\*

| Symbol           | Parameter                                      | Value       | Unit                 |

|------------------|------------------------------------------------|-------------|----------------------|

| $V_{CC}$         | Power Supply Voltages                          |             |                      |

|                  | Single Supply<br>Split Supplies                | 32<br>±16   | V                    |

| $V_{IDR}$        | Input Differential Voltage Range (1)           | ±32         | V                    |

| V <sub>ICR</sub> | Input Common Mode Voltage Range                | -0.3 to 32  | V                    |

| $I_{SC}$         | Output Short Circuit Duration                  | Continuous  |                      |

| $T_{J}$          | Junction Temperature                           |             |                      |

|                  | Plastic Packages                               | 150         | $^{\circ}\mathrm{C}$ |

| Tstg             | Storage Temperature                            |             | °C                   |

|                  | Plastic Packages                               | -55 to +125 |                      |

| $I_{IN}$         | Input Current, per pin (2)                     | 50          | mA                   |

| $T_{L}$          | Lead Temperature, 1mm from Case for 10 Seconds | 260         | °C                   |

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the Recommended Operating Conditions.

+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°C

SOIC Package: : - 7 mW/°C from 65° to 125°C

#### Notes:

- 1. Split Power Supplies.

- 2.  $V_{IN}$ <-0.3V. This input current will only exist when voltage at any of the input leads is driven negative.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter                                | Min         | Max       | Unit |

|-----------------|------------------------------------------|-------------|-----------|------|

| V <sub>CC</sub> | DC Supply Voltage                        | ±2.5 or 5.0 | ±15 or 30 | V    |

| $T_{A}$         | Operating Temperature, All Package Types | -40         | +85       | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation,  $V_{IN}$  and  $V_{OUT}$  should be constrained to the range  $GND \le (V_{IN}) \le V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{\text{CC}}$ ). Unused outputs must be left open.

## **DC ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=-40 to +85°C)

|                          |                                                |                                                                                                                 | Gua             | ranteed L | imit              |          |

|--------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------|-------------------|----------|

| Symbol                   | Parameter                                      | Test Conditions                                                                                                 | Min             | Тур       | Max               | Unit     |

| V <sub>IO</sub>          | Maximum Input Offset<br>Voltage                | $V_{O}$ =1.4V $V_{CC}$ =5.0-30V; $R_{S}$ =0 $\Omega$ $V_{ICM}$ =0V to $V_{CC}$ -1.7V                            |                 |           | 9.0<br>5.0*       | mV       |

| $\Delta V_{IO}/\Delta T$ | Input Offset Voltage<br>Drift                  | $R_S=0\Omega$ , $V_{CC}=30V$                                                                                    |                 | 7.0       |                   | μV/°C    |

| I <sub>IO</sub>          | Maximum Input Offset<br>Current                | V <sub>CC</sub> =5.0V                                                                                           |                 |           | 150<br>50*        | nA       |

| $\Delta I_{IO}/\Delta T$ | Input Offset Current<br>Drift                  | $R_S=0\Omega$ , $V_{CC}=30V$                                                                                    |                 | 10        |                   | pA/°C    |

| $I_{\mathrm{IB}}$        | Maximum Input Bias<br>Current                  | V <sub>CC</sub> =5.0V                                                                                           |                 |           | 500<br>250*       | nA       |

| V <sub>ICR</sub>         | Input Common Mode<br>Voltage Range             | V <sub>CC</sub> =30V                                                                                            | 0               |           | 28                | V        |

| I <sub>CC</sub>          | Maximum Power Supply<br>Current                | $R_L = \infty, V_{CC} = 30V, V_0 = 0V$<br>$R_L = \infty, V_{CC} = 5V, V_0 = 0V$                                 |                 |           | 3<br>1.2          | mA       |

| A <sub>VOL</sub>         | Minimum Large Signal<br>Open-Loop Voltage Gain | $V_{CC}=15V, R_L \ge 2K\Omega$                                                                                  | 15<br>25*       |           |                   | V/mV     |

| V <sub>OH</sub>          | Minimum Output High-<br>Level Voltage Swing    | $V_{CC} = 30V, R_L = 2K\Omega$ $V_{CC} = 30V, R_L = 10K\Omega$                                                  | 26<br>27        |           |                   | V        |

| $V_{OL}$                 | Maximum Output Low-<br>Level Voltage Swing     | $V_{CC}$ =5V, $R_L$ =10K $\Omega$                                                                               |                 |           | 20                | mV       |

| CMR                      | Common Mode<br>Rejection                       | $V_{CC}$ =30V, $R_S$ =10K $\Omega$                                                                              | 65*             |           |                   | dB       |

| PSR                      | Power Supply Rejection                         | V <sub>CC</sub> =30V                                                                                            | 65*             |           |                   | dB       |

| CS                       | Channel Separation                             | f=1KHz to 20KHz,V <sub>CC</sub> =30V                                                                            | -120*           |           |                   | dB       |

| $I_{SC}$                 | Maximum Output Short<br>Circuit to GND         | V <sub>CC</sub> =5.0V<br>V <sub>0</sub> =0V                                                                     |                 |           | 60*               | mA       |

| I <sub>source</sub>      | Minimum Source Output<br>Current               | V <sub>IN+</sub> =1V, V <sub>IN-</sub> =0V, V <sub>CC</sub> =15V, V <sub>0</sub> =2V                            | 10              |           |                   | mA       |

| $I_{\mathrm{sink}}$      | Minimum Output Sink<br>Current                 | $V_{IN+}$ =0V, $V_{IN-}$ =1V, $V_{CC}$ =15V, $V_0$ =2V $V_{IN+}$ =0V, $V_{IN-}$ =1V, $V_{CC}$ =15V, $V_0$ =0.2V | 5<br>10*<br>12* |           |                   | mA<br>μA |

| $V_{\rm IDR}$            | Differential Input<br>Voltage Range            | All V <sub>IN</sub> ≥GND or V-Supply (if used)                                                                  |                 |           | V <sub>CC</sub> * | V        |

<sup>\*=@25°</sup>C

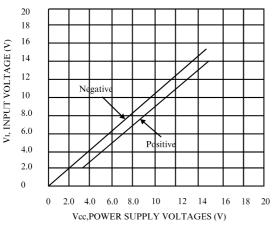

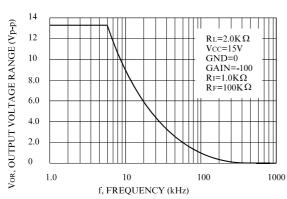

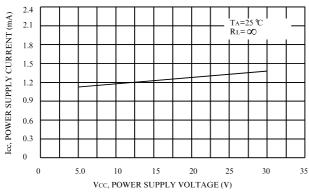

#### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 1.Input Voltage Range

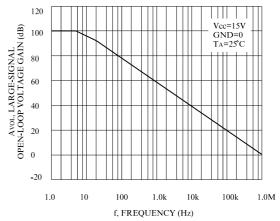

Figure 3. Large-Signal Frequency Response

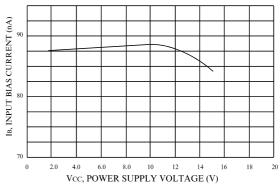

Figure 5. Power Supply Current versus Power Supply Voltage

Figure 2. Open-Loop Frequency

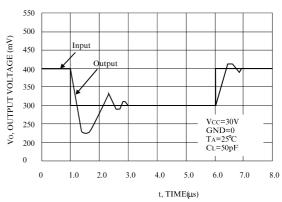

Figure 4. Small-Signal Voltage Follower Pulse Response (Noninverting)

Figure 6. Input Bias Current versus Power Supply Voltage

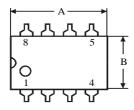

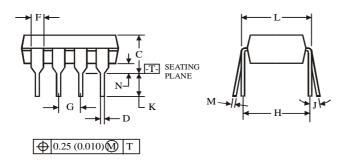

### N SUFFIX PLASTIC DIP (MS – 001BA)

#### NOTES:

Dimensions "A", "B" do not include mold flash or protrusions.

Maximum mold flash or protrusions 0.25 mm (0.010) per side.

|        | Dimension, mm |       |  |

|--------|---------------|-------|--|

| Symbol | MIN           | MAX   |  |

| A      | 8.51          | 10.16 |  |

| В      | 6.1 7.11      |       |  |

| C      |               | 5.33  |  |

| D      | 0.36          | 0.56  |  |

| F      | 1.14          | 1.78  |  |

| G      | 2.54          |       |  |

| Н      | 7.62          |       |  |

| J      | 0°            | 10°   |  |

| K      | 2.92          | 3.81  |  |

| L      | 7.62          | 8.26  |  |

| M      | 0.2           | 0.36  |  |

| N      | 0.38          |       |  |

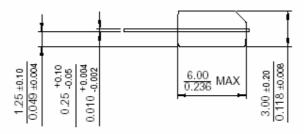

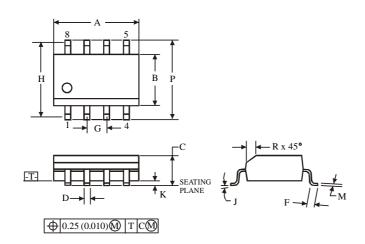

#### D SUFFIX SOIC (MS - 012AA)

#### NOTES:

- 1. Dimensions A and B do not include mold flash or protrusion.

- 2. Maximum mold flash or protrusion 0.15 mm (0.006) per side for A; for B 0.25 mm (0.010) per side.

|        | Dimension, mm |      |  |

|--------|---------------|------|--|

| Symbol | MIN           | MAX  |  |

| A      | 4.8           | 5    |  |

| В      | 3.8           | 4    |  |

| C      | 1.35          | 1.75 |  |

| D      | 0.33          | 0.51 |  |

| F      | 0.4           | 1.27 |  |

| G      | 1.27          |      |  |

| Н      | 5.72          |      |  |

| J      | 0°            | 8°   |  |

| K      | 0.1           | 0.25 |  |

| M      | 0.19          | 0.25 |  |

| P      | 5.8           | 6.2  |  |

| R      | 0.25 0.5      |      |  |

## Mechanical Dimensions (Continued)

### Package