#### **8W/CH STEREO CLASS-D AUDIO POWER AMPLIFIER**

Advanced Information July 2012

#### **GENERAL DESCRIPTION**

The IS31AP2117 is an 8W/CH, dual channel, Class-D stereo driver in our audio amplifier family. It is suitable for powering the audio components of various equipments, including typical consumer electronics, high performance audio speakers.

IS31AP2117 has several key features which distinguishes itself from other alternatives on the market. On-board AGC, EMI suppression, and 92% typical operating efficiency are key features of this part. EMI suppression circuit, which eliminates LC, filters at the outputs. These features simplify customer design, reduces system cost and PCB area.

The IS31AP2117 integrates automatic gain control function with adjustable power limit. When output power goes over the power limit, IS31AP2117 can reduce gain automatically to pull down the output power, so that keep the output power around power limit while the input level is high. The IS31AP2117 has short circuit and thermal protection features integrated on board.

#### **FEATURES**

- Mono 6W, at 8Ω @ 1% THD, V<sub>CC</sub>=12V

- Mono 15W, at 8Ω @ 10% THD, V<sub>CC</sub>=16V

- Dual 8W/CH, at 8Ω @ 10% THD, V<sub>CC</sub> =24V

- 92% typical operating efficiency

- 8V< V<sub>IN</sub> <26V</li>

- Filter-less EMI suppression

- Integrated AGC with adjustable power limit

- Four selectable, gain preset levels: 20dB, 26dB, 32dB, 36dB

- High SNR, low THD+N

- Thermal and short-circuit protection

- Over/under-voltage protection

- Mute features

- Clock selection

- TSSOP-28 package

#### **APPLICATIONS**

- Consumer audio equipment

- HDTV, home theater equipment

- Automotive audio amplifier

- Performance stereo speakers

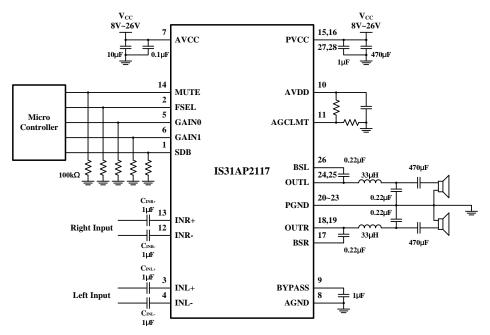

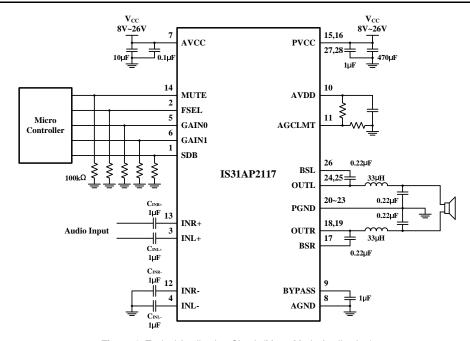

## **TYPICAL APPLICATION CIRCUIT**

Figure 1 Typical Application Circuit (Stereo Mode Application)

Figure 2 Typical Application Circuit (Mono Mode Application)

#### **PIN CONFIGURATION**

| Package  | Pin Configuration (Top View) |  |  |  |

|----------|------------------------------|--|--|--|

| TSSOP-28 | SDB                          |  |  |  |

# ORDERING INFORMATION INDUSTRIAL RANGE: -40°C TO +85°C

| Order Part No.  | Package             | QTY/Tube |  |  |

|-----------------|---------------------|----------|--|--|

| IS31AP2117-ZLS2 | TSSOP-28, Lead-free | 30       |  |  |

Copyright © 2012 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

### PIN DESCRIPTION

| _      | PIN DESCRIPTION |                                                                                                                                                |  |  |  |  |  |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No.    | Pin             | Description                                                                                                                                    |  |  |  |  |  |

| 1      | SDB             | Shutdown control. Active low.                                                                                                                  |  |  |  |  |  |

| 2      | FSEL            | Frequency select input pin. (low = 300kHz, high = 400kHz)                                                                                      |  |  |  |  |  |

| 3      | INL+            | Positive audio input for left channel.                                                                                                         |  |  |  |  |  |

| 4      | INL-            | Negative audio input for left channel.                                                                                                         |  |  |  |  |  |

| 5      | GAIN0           | Gain select least significant bit.                                                                                                             |  |  |  |  |  |

| 6      | GAIN1           | Gain select most significant bit.                                                                                                              |  |  |  |  |  |

| 7      | AVCC            | Analog power supply.                                                                                                                           |  |  |  |  |  |

| 8      | AGND            | Analog signal ground.                                                                                                                          |  |  |  |  |  |

| 9      | BYPASS          | Reference for pre-amplifier inputs. Nominally equal to AVDD/2.                                                                                 |  |  |  |  |  |

| 10     | AVDD            | 5V regulated output. Connect 2.2μF to AGND.                                                                                                    |  |  |  |  |  |

| 11     | AGCLMT          | Power limit level adjusting pin. Connect a resistor divider from AVDD to AGND to set power limit. Connect directly to AVDD for no power limit. |  |  |  |  |  |

| 12     | INR-            | Negative audio input for right channel.                                                                                                        |  |  |  |  |  |

| 13     | INR+            | Positive audio input for right channel.                                                                                                        |  |  |  |  |  |

| 14     | MUTE            | Mute mode control.                                                                                                                             |  |  |  |  |  |

| 15, 16 | PVCC            | Power supply for right channel H-bridge. PVCCR and PVCCL must be connected together on the PCB.                                                |  |  |  |  |  |

| 17     | BSR             | Bootstrap I/O for right channel, high-side FET.                                                                                                |  |  |  |  |  |

| 18, 19 | OUTR            | Class-D H-bridge output for right channel.                                                                                                     |  |  |  |  |  |

| 20~23  | PGND            | Power ground for the H-bridges.                                                                                                                |  |  |  |  |  |

| 24, 25 | OUTL            | Class-D H-bridge output for left channel.                                                                                                      |  |  |  |  |  |

| 26     | BSL             | Bootstrap I/O for left channel, high-side FET.                                                                                                 |  |  |  |  |  |

| 27, 28 | PVCC            | Power supply for left channel H-bridge. PVCCR and PVCCL must be connected together on the PCB.                                                 |  |  |  |  |  |

|        | Thermal Pad     | Connect to GND.                                                                                                                                |  |  |  |  |  |

|        |                 |                                                                                                                                                |  |  |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage (AVCC, PVCC), V <sub>CC</sub>    | -0.3V ~ +30.0V                  |

|-------------------------------------------------|---------------------------------|

| Voltage at SDB, GAIN0, GAIN1, FSEL, MUTE pins   | $-0.3V \sim V_{CC} + 0.3V$      |

| Voltage at IN, AGCLMT pins                      | -0.3 to V <sub>AVDD</sub> +0.3V |

| Voltage at OUTR, OUTL                           | -0.3 to V <sub>CC</sub> +0.3V   |

| Voltage at AVDD                                 | −0.3V ~ +6.0V                   |

| Maximum junction temperature, T <sub>JMAX</sub> | 150°C                           |

| Storage temperature range, T <sub>STG</sub>     | −65°C ~ +150°C                  |

| Operating temperature range, T <sub>A</sub>     | −40°C ~ +85°C                   |

#### Note:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

$V_{CC}$ =12V,  $T_A$ =25°C,  $R_L$ =8 $\Omega$  (unless otherwise noted).

| Symbol              | Parameter                                               | Condition                                    | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>CC</sub>     | Supply voltage                                          |                                              | 8    |      | 26   | V    |

| I <sub>CC</sub>     | Quiescent current                                       | V <sub>SDB</sub> = 2V, no load (without LC)  |      | 12   |      | mA   |

| I <sub>SD</sub>     | Shutdown current                                        | V <sub>SDB</sub> = 0.8V                      |      | 200  |      | μA   |

| R <sub>DS(ON)</sub> | Drain-source on-state resistance                        | I <sub>O</sub> = 500mA                       |      | 150  |      | mΩ   |

| V <sub>os</sub>     | Class-D output offset voltage (measured differentially) | V <sub>I</sub> = 0, Gain = 36dB              |      | 1.5  |      | mV   |

|                     | Gain                                                    | Gain1= 0.8V, Gain0= 0.8V                     |      | 20   |      | dB   |

| G                   |                                                         | Gain1= 0.8V, Gain0= 2V                       |      | 26   |      |      |

|                     |                                                         | Gain1= 2V, Gain0= 0.8V                       |      | 32   |      |      |

|                     |                                                         | Gain1= 2V, Gain0= 2V                         |      | 36   |      |      |

| t <sub>ON</sub>     | Turn-on time                                            | V <sub>SDB</sub> = 2V                        |      | 50   |      | ms   |

| t <sub>OFF</sub>    | Turn-off time                                           | V <sub>SDB</sub> = 0.8V                      |      | 2    |      | μs   |

| AVDD                | Internal regulated output                               | I <sub>O</sub> = 5mA                         |      | 5    |      | V    |

| $R_L$               | Speaker resistance                                      |                                              | 3.6  |      |      | Ω    |

| Logic Elec          | ctrical Characteristics (SDB, FS                        | SEL, GAIN0, GAIN1, MUTE)                     |      |      |      |      |

| $V_{IH}$            | High level threshold voltage                            |                                              | 2    |      | AVCC | V    |

| V <sub>IL</sub>     | Low level threshold voltage                             |                                              | 0    |      | 0.8  | V    |

| I <sub>IH</sub>     | High level threshold current                            | V <sub>I</sub> = 2V, V <sub>CC</sub> = 18V   |      | 50   |      | μA   |

| I <sub>IL</sub>     | Low level threshold current                             | V <sub>I</sub> = 0.8V, V <sub>CC</sub> = 18V |      | 5    |      | μA   |

## **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}$ =12V,  $T_A$ =25°C,  $R_L$ =8 $\Omega$  (unless otherwise noted).

| Symbol           | Parameter                         | Condition                                                                    | Min. | Тур. | Max. | Unit                   |

|------------------|-----------------------------------|------------------------------------------------------------------------------|------|------|------|------------------------|

| PSRR             |                                   | 200mV <sub>P-P</sub> ripple at 1kHz, Gain = 20 dB, Inputs ac-coupled to AGND |      | -60  |      | dB                     |

| Po               |                                   | THD+N = 10%, f = 1kHz, $R_L$ = $4\Omega$                                     |      | 5    |      | W                      |

| THD+N            | Total harmonic distortion + noise | f = 1kHz, P <sub>O</sub> = 1W (half-power)                                   |      | 0.1  |      | %                      |

| V <sub>N</sub>   | Output integrated noise           | 20Hz ~ 22kHz, A-weighted filter, Gain = 20dB                                 |      | 65   |      | μV                     |

| SNR              | Signal-to-noise ratio             | Maximum output at THD+N < 1%, f = 1kHz, Gain = 20dB, A-weighted              |      | 102  |      | dB                     |

| F <sub>osc</sub> | Ossillator fraguency              | V <sub>FSEL</sub> = 0.8V                                                     |      | 290  |      | kHz                    |

|                  | Oscillator frequency              | V <sub>FSEL</sub> = 2V                                                       |      | 390  |      |                        |

|                  | Thermal trip point                |                                                                              |      | 160  |      | $^{\circ}\!\mathbb{C}$ |

|                  | Thermal hysteresis                |                                                                              |      | 60   |      | $^{\circ}\!\mathbb{C}$ |

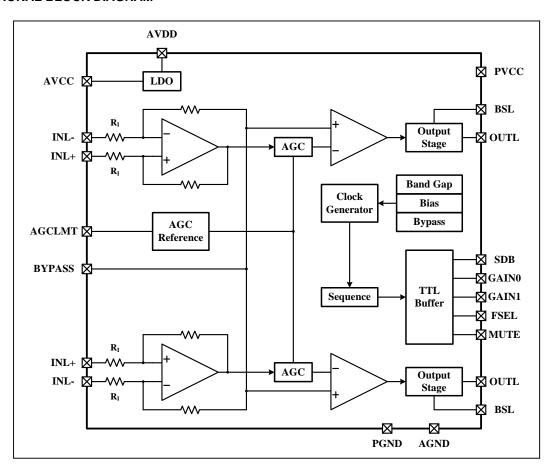

## **FUNCTIONAL BLOCK DIAGRAM**

#### **FUNCTION DESCRIPTION**

The IS31AP2117 is an 8W, dual channel, Class-D stereo which is suitable for powering the audio components of various equipments, including typical consumer electronics, high performance audio speakers.

The MUTE pin is an input for controlling the output state of the IS31AP2117. A logic high on this terminal will shut down the outputs. A logic low on this pin enables the outputs.

The gain of the IS31AP2117 is set by two input terminals, GAIN0 and GAIN1. Different input logic for GAIN0 and GAIN1 cause input gain in 4 levels (20dB, 26dB, 32dB, 36dB).

The IS31AP2117 also provides thermal and over current protection functions to prevent permanent damage to the device.

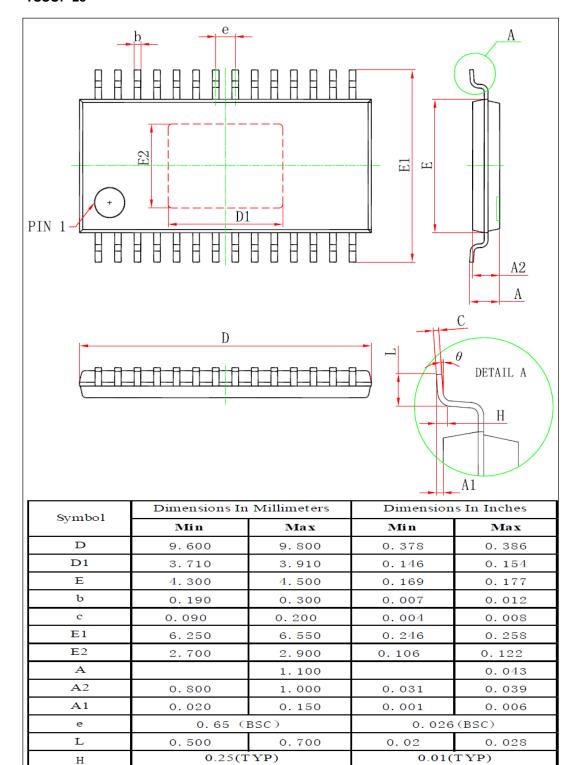

#### **PACKAGE INFORMATION**

#### TSSOP-28

Note: All dimensions in millimeters unless otherwise stated.