# Using the DR65-0109 to Drive SPDT PIN Switches

Rev. V2

#### Introduction

For use as a replacement part to the DR65-0003 PIN Driver.

This Application Note describes how to use the M/A-COM DR65-0109 Single Channel Driver for FET Switches as a SP2T PIN Diode Driver. When configured per the directions herein, the DR65-0109 will provide the same functionality as the DR65-0003 in the same package style, HOWEVER THE PINOUT IS DIFFERENT. USING THE DR65-0109 AS A DIRECT DROP-IN REPLACEMENT WITHOUT DOING A PCB CHANGE WILL NOT

#### **Pin Assignments**

| Pin# | Function    | Pin# | Function                |  |  |

|------|-------------|------|-------------------------|--|--|

| 1    | Vcc         | 5    | Ground                  |  |  |

| 2    | Logic Input | 6    | Non-Inverting<br>Output |  |  |

| 3    | Vdd         | 7    | Inverting Output        |  |  |

| 4    | Ground      | 8    | Vee                     |  |  |

## Electrical Specifications: $T_A = +25$ °C, $+Vcc = +Vdd = +5.0V \pm 5$ %, $-Vee = -5.0V \pm 5$ %

| Parameter                                   | Test Conditions                                                       | Units    | Min      | Typical     | Max         |

|---------------------------------------------|-----------------------------------------------------------------------|----------|----------|-------------|-------------|

| Switching Speed <sup>1</sup> Delay<br>Rt/Ft | Spike current into 10 ohm load<br>50 % TTL to 90%<br>10%-90%; 90%-10% | nS<br>nS |          | 25<br>2     | 35<br>5     |

| PRF                                         | 50% duty cycle                                                        | MHz      | DC       | _           | 5           |

| Output Voltage Drop, No Load                | With reference to supply voltage                                      | V        | _        | _           | .25         |

| DC Output Current Peak Spike Output Current | Load Dependent<br>Spiking Capacitor in Circuit                        | mA<br>mA |          | ±30<br>±150 | ±50<br>±200 |

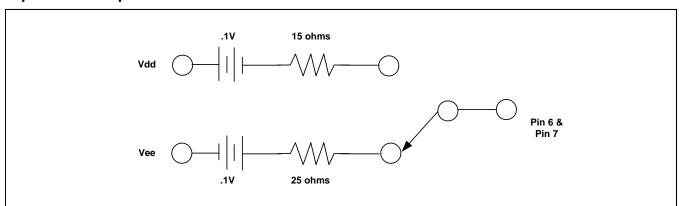

| Output Stage on Resistance                  | Positive Output FET, Qp<br>Negative Output FET, Qn                    | W<br>W   | 1 1      | 15<br>25    |             |

| Quiescent Supply Currents                   | +5V<br>-5V                                                            | mA<br>mA |          | _           | 1.0<br>.2   |

| TTL Levels                                  | Logic "0" @ 20 μA sink current<br>Logic "1" @ 20 μA source current    | V<br>V   | 0<br>2.0 | _           | .8<br>5.0   |

| Package Dissipation                         | _                                                                     | mW       | _        | _           | 200         |

<sup>1.</sup> Decoupling capacitors (.01 µF) are required on power supply lines.

## **Equivalent Output Circuit for Pins 6 & 7**

<sup>•</sup> India Tel: +91.80.4155721

<sup>•</sup> China Tel: +86.21.2407.1588

## Using the DR65-0109 to Drive SPDT PIN Switches

Rev. V2

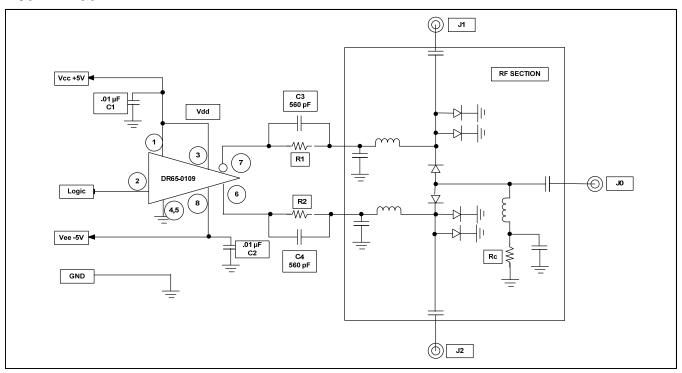

#### **Typical Application for SP2T Circuit**

#### **Description of Circuit**

The DR65-0109 provides 2 complementary outputs that are each capable of driving a maximum of  $\pm 50$  mA into a load. In addition, with proper capacitor selection (C3 & C4) used in parallel with the current setting resistor (R1 & R2), a maximum of  $\pm 200$  mA of spiking current can be achieved. Configurations using DC steering diodes and a lower Vdd supply will decrease the peak spiking current available to the user.

To achieve the Non-Inverting and Inverting complementary voltages, each output is switched between two internal FETs. The FETs are connected to Vdd for the positive output and Vee for the negative output. Vdd and Vee are adjustable for various configurations and have the following limitations: Vee can be no more negative than – 5.5 volts; Vdd can be no more positive than 5.5 volts AND Vdd must always be less than or equal to Vcc. Increasing Vdd beyond Vcc will prevent the device from switching states when commanded to by the logic input. Recommended configurations are to drive Vee at –5.0 volts and Vcc and Vdd should be tied together at 5 volts.