RC144ACi and RC144ACL Integrated High Speed Data/Fax/Voice Modem Device Set with Cellular Direct Connect Support

# INTRODUCTION

The Rockwell RC144ACi and RC144ACL integrated data/fax/voice modem device set families support high speed data and high speed fax operation in the US or world-wide operation over a dial-up telephone line and, for US versions, a cellular phone (Table 1 lists the models).

As a data modem, the modem operates at line speeds to 14400 bps. Error correction (V.42/MNP 2-4) and data compression (V.42 bis/MNP5) maximize data transfer integrity and boost average data throughput up to 57.6 kbps. Non-error-correcting mode is also supported.

As a fax modem, the modem supports Group 3 send and receive rates up to 14400 bps and supports T.30 protocol.

In voice mode, enhanced Adaptive Differential Pulse Coded Modulation coding and decoding supports efficient digital storage of voice using 2-bit or 4-bit compression and decompression at 7200 bps. Coder silence deletion and decoder silence interpolation is available to significantly increase compression rates.

Voice models operating with the parallel host bus also support business audio and the Integrated Communications System (ICS) program. Record and playback of monophonic (mono) audio data in 8-bit unsigned linear pulse code modulation (PCM) or 16-bit signed linear PCM format at 11.025 kHz or 7200 Hz sampling rate is supported. These features can be used in applications such as digital answering machine, voice annotation, audio file play and record, and text-to speech.

In voice and data modem modes, data throughput greater than 176 kbps is achieved using the Rockwell High Speed Interface (RHSI). RHSI allows slower PCs such as 16 MHz 386-based PCs to sustain data rates of over 115.2 kbps.

Cellular direct connect operation is supported by licensed firmware unique to a specific cellular phone type.

"AT" commands provide data, fax class 1 and class 2, MNP 10, voice/audio, cellular, and W-class functions while using minimal external ROM, RAM, and optional NVRAM.

The ACi device set is best for desktop applications while the lower power, smaller package, ACL device set is ideal for laptop, notebook, and palmtop applications. The ACi and ACL are functional equivalent.

Use of AccelerATor kits for PC half cards and PCMCIA PC cards minimize application design time and costs. The kits also include design layout files on floppy disk, sample modem devices, crystals, and full documentation.

PC-based "ConfigurACE™" software allows MCU firmware to customized to application and country requirements.

# FEATURES

- Data modem throughput up to 57.6 kbps (beyond 57.6 kbps when RHSI is active)

- V.32 bis, V.32, V.22 bis, V.22A/B, V.23, and V.21; Bell 212A and 103

- V.42 LAPM and MNP 2-4 error correction

- V.42 bis and MNP 5 data compression

- MNP 10 data throughput enhancement

- Fax modern send and receive rates up to 14400 bps

V.17, V.29, V.27 ter, and V.21 channel 2

- Cellular direct connect

- Voice mode (option)

- Enhanced ADPCM compression/decompression

- Tone detection/generation and call discrimination

- Concurrent DTMF detection

Timing marks

- Business audio mode (with parallel bus interface)

- Record or playback mono data using 8-bit or 16-bit audio data encoding at 11.025 kHz or 7200 Hz

- Concurrent DTMF/tone detection

- World-class operation (option)

- Call progress and blacklisting parameters

- Multiple country support

- Hayes AutoSync (option)

- Communication software compatible command sets - AT, fax class 1 and 2, and voice commands

- NVRAM directory and stored profiles

- Built-in DTE interfaces

- DTE speed to 57.6 kbps

- Parallel 16450 or 16550A UART interface

- Serial CCITT V.24 (EIA/TIA-232-E)

- Rockwell High Speed Interface (RHSI)

- Automatic format/speed sensing to 57.6 kbps

- Flow control and speed buffering

- Serial sync/async data; parallel async data

- · Auto dial and auto answer

- · Tone and pulse dialing

- Calling Number Delivery (Caller ID) detect

- Extended operating temperature models available

|             | poraling temper |                          |

|-------------|-----------------|--------------------------|

| Flexible pa | ckaging options |                          |

| Device      | RC144ACi        | RC144ACL                 |

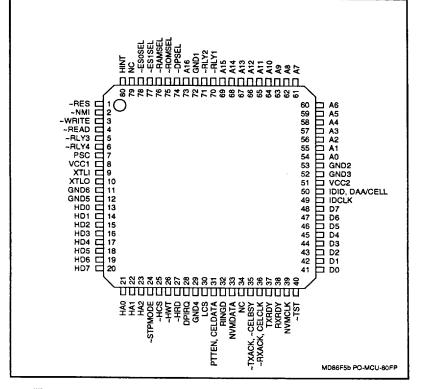

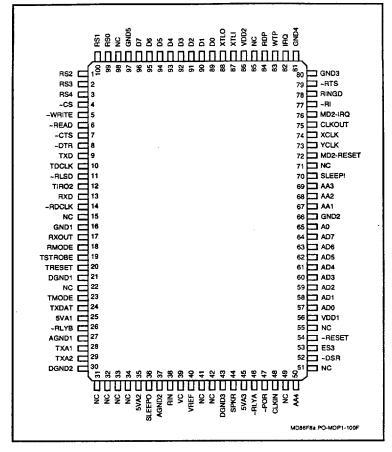

| MCU         | 84-pin PLCC     | 80-pin PQFP              |

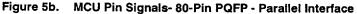

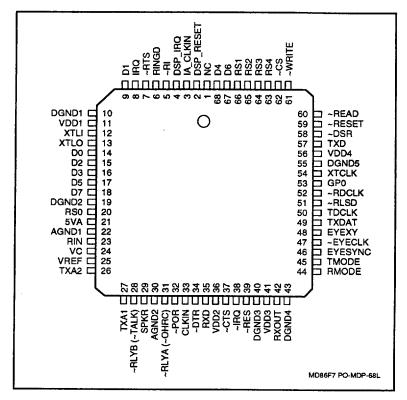

| MDP         | 68-pin PLCC     | 68-pin PLCC or           |

|             |                 | 100-pin PQFP/80-pin PQFI |

|             |                 | · · · ·                  |

• +5V operation; typical power consumption (C40 MCU):

| Mode       | RC144ACI | RC144ACL |

|------------|----------|----------|

| Operating  | 850 mW   | 540 mW   |

| Sleep mode | 21 mW    | 21 mW    |

Data Sheet (Preliminary) Order No. MD86 Rev. 3, November 21, 1994 (Supersedes MD86R2, MD103, and MD106)

7811073 0024296 517 🖿

|                                                                                                                                                                                                                                                                                                                                          |                                    | Supported Functions |       |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|-------|-----------|

| Model                                                                                                                                                                                                                                                                                                                                    | Data/Fax                           | W-Class             | Voice | Country   |

| RC144ACL(/U)                                                                                                                                                                                                                                                                                                                             | V.32 bis/V.17                      | _                   | -     | US/Canada |

| RC144ACLWD(/U)                                                                                                                                                                                                                                                                                                                           | V.32 bis/No fax                    | S                   | -     | Multiple  |

| RC144ACLW(/U)                                                                                                                                                                                                                                                                                                                            | V.32 bis/V.17                      | S                   | -     | Multiple  |

| RCV144ACL-BA                                                                                                                                                                                                                                                                                                                             | V.32 bis/V.17                      |                     | S     | US/Canada |

| RCV144ACLW(E)-B                                                                                                                                                                                                                                                                                                                          | A V.32 bis/V.17                    | s                   | S     | Multiple  |

| RC96ACL(/U)                                                                                                                                                                                                                                                                                                                              | V.32/V.29                          |                     | _     | US/Canada |

| RC96ACLWD(/U)                                                                                                                                                                                                                                                                                                                            | V.32/No fax                        | s                   | -     | Multiple  |

| RC96ACLW(/U)                                                                                                                                                                                                                                                                                                                             | V.32/V.29                          | S                   | -     | Multiple  |

| RCV96ACL-BA                                                                                                                                                                                                                                                                                                                              | V.32/V.29                          | -                   | S     | US/Canada |

| RCV96ACLW-BA                                                                                                                                                                                                                                                                                                                             | V.32/V.29                          | s                   | S     | Multiple  |

| RC144ACi(/U)                                                                                                                                                                                                                                                                                                                             | V.32 bis/V.17                      | -                   | -     | US/Canada |

| RC144ACiWD(/U)                                                                                                                                                                                                                                                                                                                           | V.32 bis/No fax                    | S                   | -     | Multiple  |

| RC144ACiW(/U)                                                                                                                                                                                                                                                                                                                            | V.32 bis/V.17                      | S                   | -     | Multiple  |

| RCV144ACi/-BA                                                                                                                                                                                                                                                                                                                            | V.32 bis/V.17                      | -                   | S     | US/Canada |

| RCV144ACiW-BA                                                                                                                                                                                                                                                                                                                            | V.32 bis/V.17                      | S                   | S     | Multiple  |

| RC96ACi(/U)                                                                                                                                                                                                                                                                                                                              | V.32/V.29                          | -                   | _     | US/Canada |

| RC96ACiWD(/U)                                                                                                                                                                                                                                                                                                                            | V.32/No fax                        | S                   | -     | Multiple  |

| RC96ACiW(/U)                                                                                                                                                                                                                                                                                                                             | V.32/V.29                          | S                   |       | Multiple  |

| RCV96ACi-BA                                                                                                                                                                                                                                                                                                                              | V.32/V.29                          | _                   | S     | US/Canada |

| RCV96ACiW-BA                                                                                                                                                                                                                                                                                                                             | V.32/V.29                          | S                   | S     | Multiple  |

| Notes:         1. Model options:         BA       Business audio.         D       Data only (no fax).         V       Voice functions.         W       World class support.         (E)       Optional industrial temperature range.         (/U)       Optional 16550A interface.         U       Available only with 16550A interface. |                                    |                     |       |           |

| <ol> <li>Supported functions (S = Supported; - = Not supported):</li> </ol>                                                                                                                                                                                                                                                              |                                    |                     |       |           |

| Fax                                                                                                                                                                                                                                                                                                                                      | Fax class 1 and class 2 command fi | unctions.           |       |           |

| W-Class World class functions supporting multiple country requirements.                                                                                                                                                                                                                                                                  |                                    |                     |       |           |

| Voice                                                                                                                                                                                                                                                                                                                                    | Voice and business audio command   | tunctions.          |       |           |

# Table 1. Modem Models and Functions

ConfigurACE is a trademark of Rockwell International. MNP is a trademark of Microcom Systems, Inc. Hayes is a trademark of Hayes Microcomputer Products, Inc.

MD86

# TH 7811073 0024297 453 MM

# **TECHNICAL SPECIFICATIONS**

## GENERAL DESCRIPTION

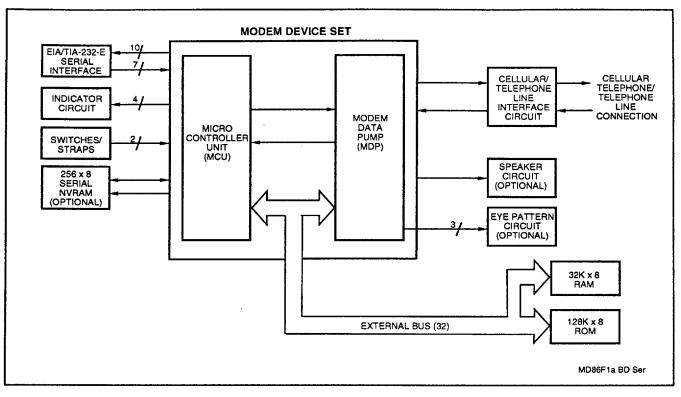

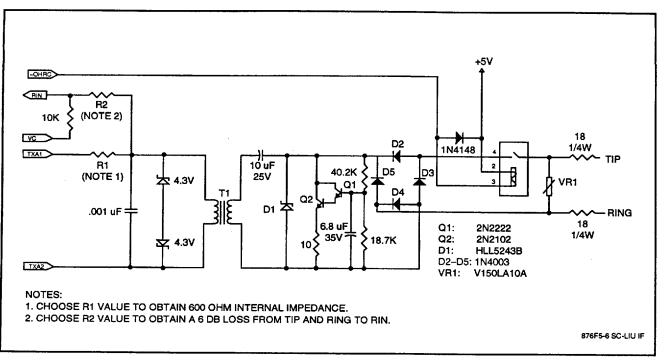

The modem device set provides the processing core of the modem. The OEM adds a crystal, discrete components, and a digital access arrangement (DAA) and/or cellular interface circuit to complete the modem system.

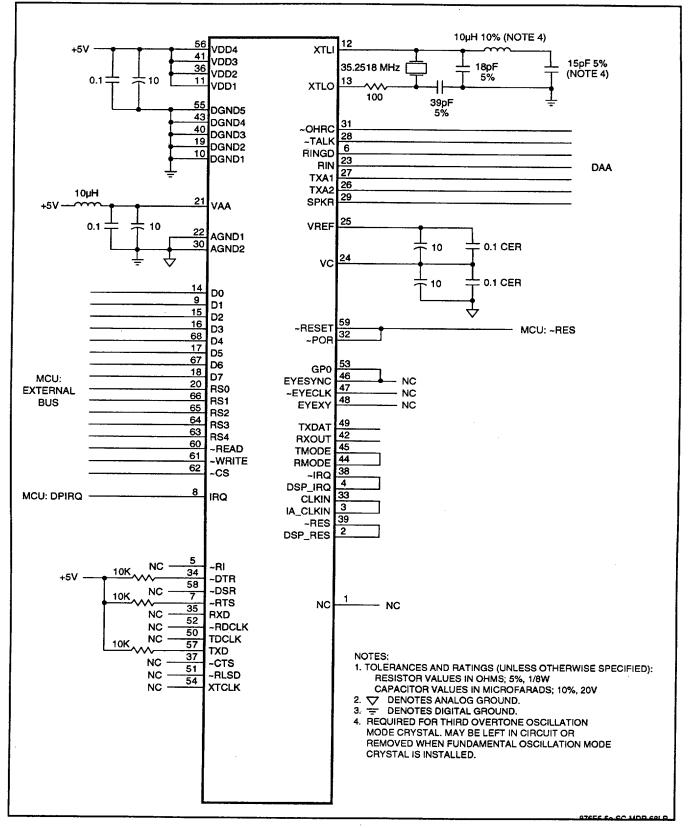

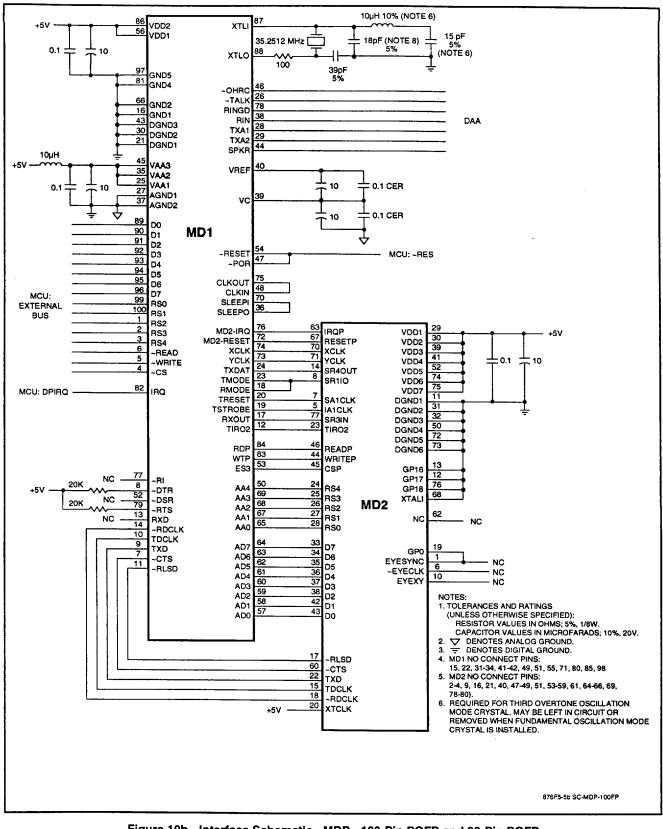

## Modem Data Pump (MDP)

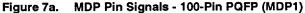

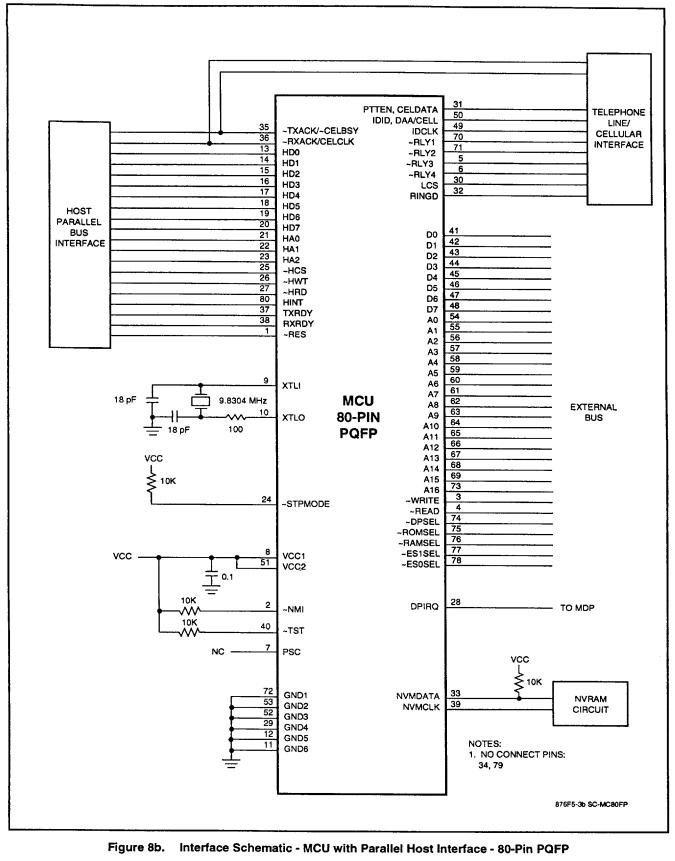

The modem data pump (MDP) in ACi models is a Rockwell RC144DPi or RC96DPi data/fax/voice modem data pump. The MDP in ACL models is a Rockwell RC144DPL or RC96DPL data/fax/voice modem data pump. The crystal frequency is 35.2512 MHz.

As a data modem, the MDP can operate in 2-wire, fullduplex, synchronous/asynchronous modes at line rates up to 14400 bps (RC144DPi/DPL) or 9600 bps (RC96DPi/DPL).

As a fax modem, the MDP fully supports Group 3 facsimile send and receive speeds of 14400 (RC144DPi/DPL), 12000 (RC144DPi/DPL), 9600, 7200, 4800, and 2400 bps.

ADPCM voice processing in the MDP is supported in ACi/ACL models supporting voice commands.

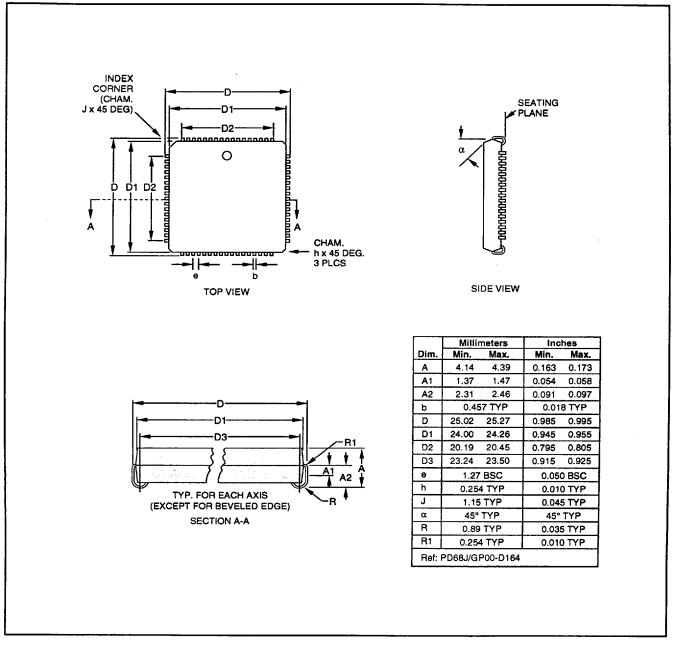

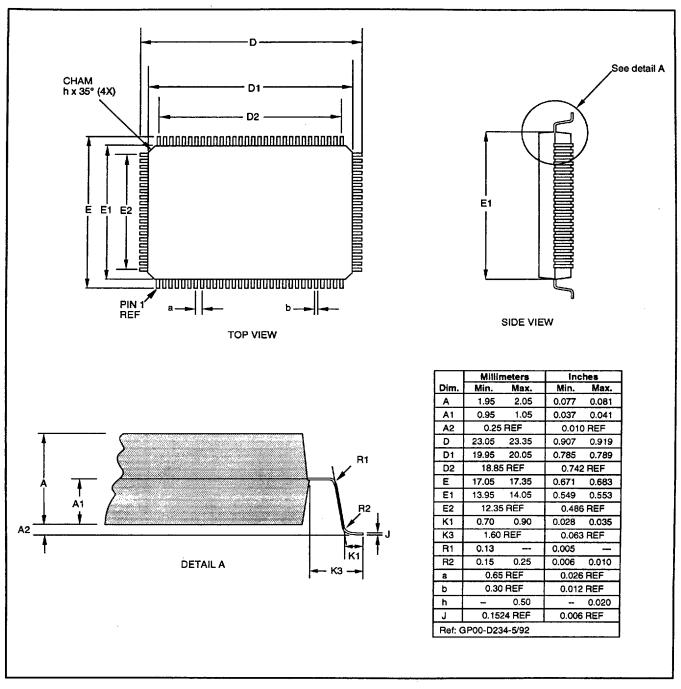

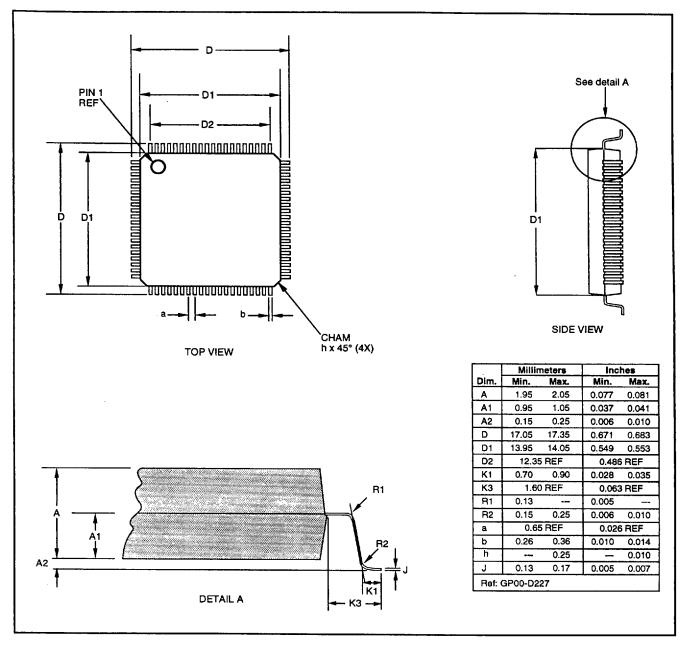

The RC144DPi/RC96DPi MDP is provided in a 68-pin PLCC. The RC144DPL/RC96DPL MDP is provided in a 68-pin PLCC or in two PQFPs (a 100-pin and an 80-pin package).

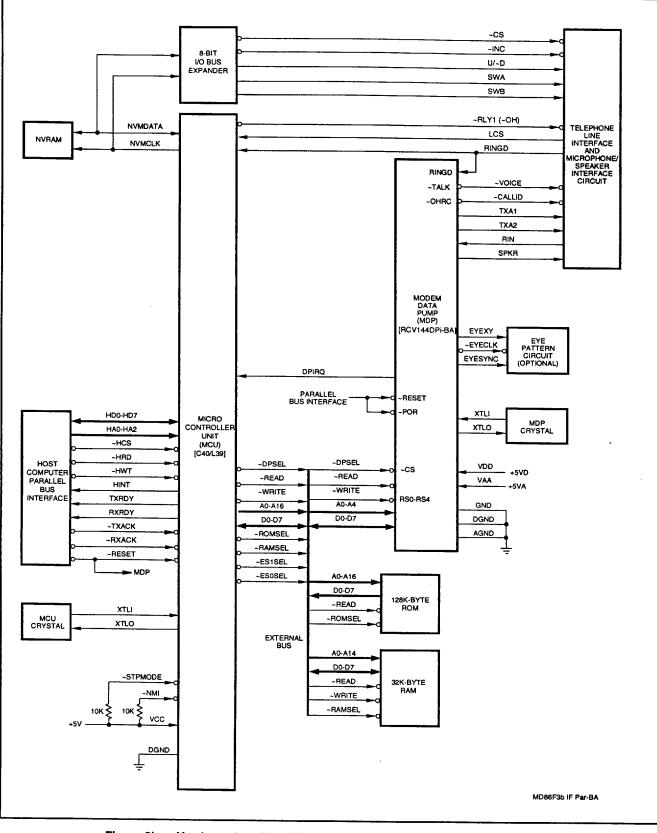

## **Microcontroller (MCU)**

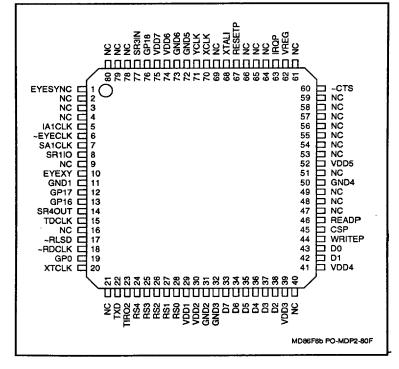

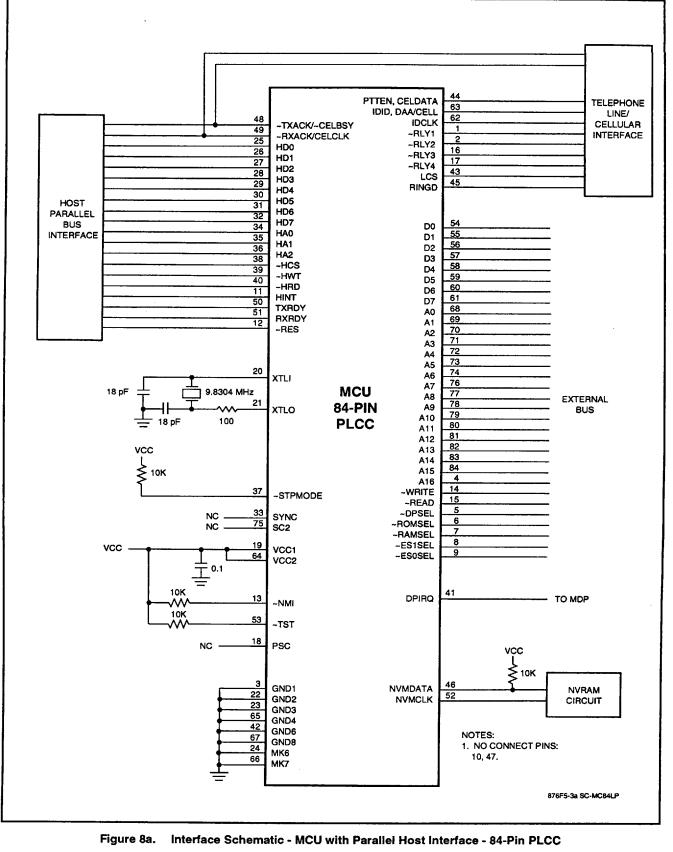

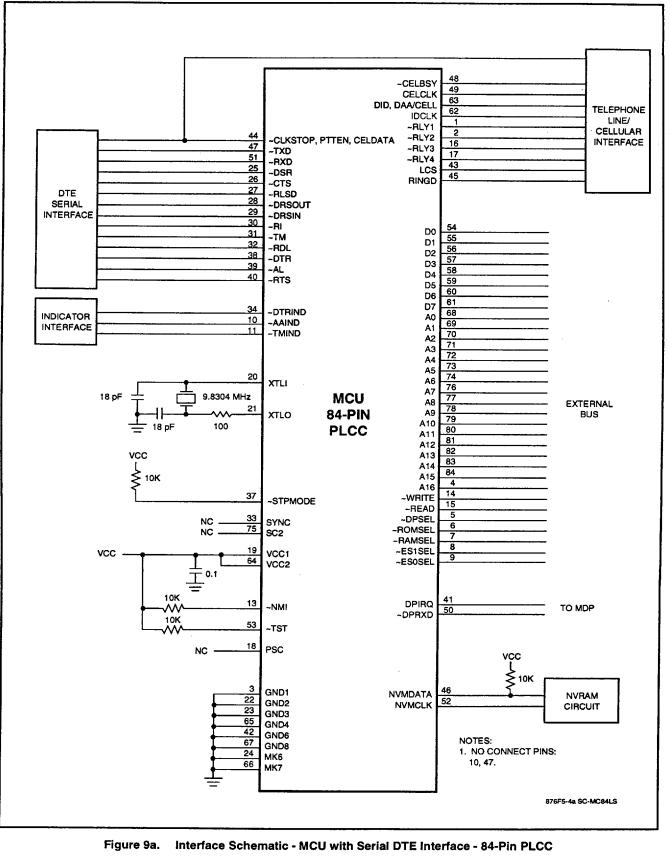

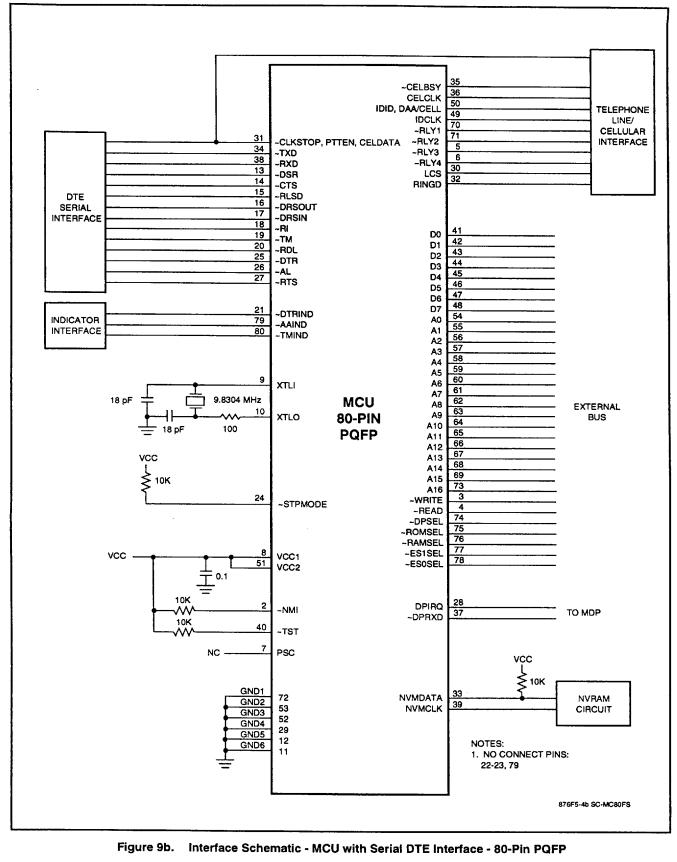

The MCU is a Rockwell C40, L39, or P39 microcomputer. The MCU performs the command processing and host interface functions. The crystal frequency is 9.8304 MHz.

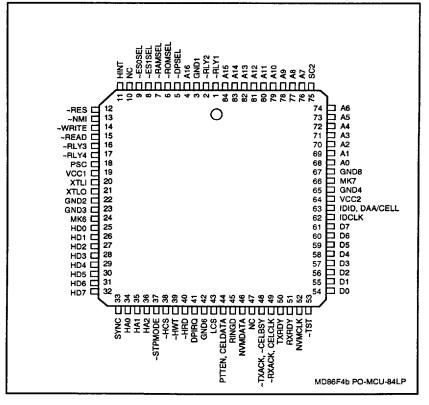

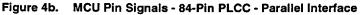

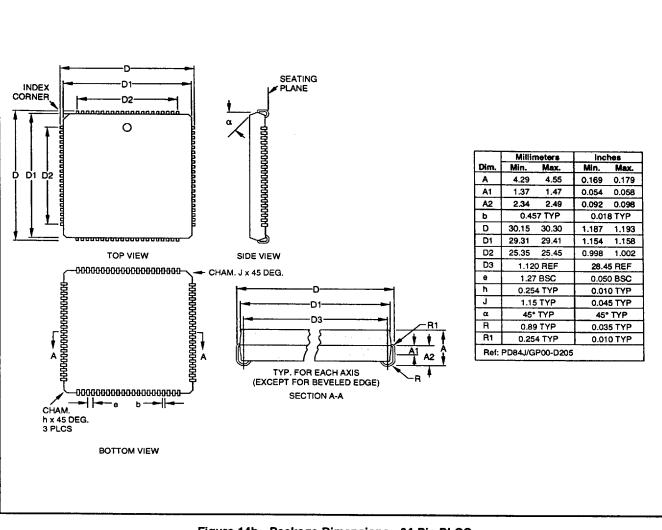

The C40 and L39 MCUs are packaged in an 84-pin PLCC for the RC144ACi/RC96ACi or in an 80-pin PQFP for the RC144ACL/RC96ACL.

The C40 or L39 MCU connects to the host via a V.24 (EIA/TIA-232-E) serial interface or a parallel microcomputer bus depending on installed MCU firmware. In parallel interface operation, the MCU can connect to a PCMCIA connector using a Rockwell PCMCIA Interface Control Adapter (PICA) device (see data sheet Order No. MD99) and a PCMCIA Card Information Structure (CIS) memory device.

The P39 MCU performs all the functions as the C40 or L39 MCU and, in addition, incorporates a built-in PCMCIA interface and CIS memory allowing the P39 MCU to directly connect to the PCMCIA connector without requiring these two external parts. The P39 MCU is packaged in an 128-pin TQFP. The P39 MCU interface is described in Application Note 1057, "P39 MCU (8-Bit Microcontroller with PCMCIA Interface) Application to Rockwell 14400 bps and 28800 bps Low Power Modems".

The MCU connects to the MDP via dedicated lines and the external bus. The MCU external bus also connects to OEM-supplied ROM and RAM. The ROM size is 128k bytes and the RAM size is 32k bytes.

For all models, 256 bytes NVRAM can optionally be connected to the MCU over a dedicated serial interface.

### MCU Firmware

MCU firmware performs processing of general modem control, command sets, error correction, data compression, MNP 10, fax class 1 and class 2, voice/audio, HSI, and DTE/host interface functions. Configurations of the MCU firmware are provided to support parallel host bus interface operation or serial DTE interface operation. The MCU firmware is provided in object code form for the OEM to program into external ROM. The MCU firmware may also be provided in source code form under a source code addendum license agreement.

## SUPPORTED INTERFACES

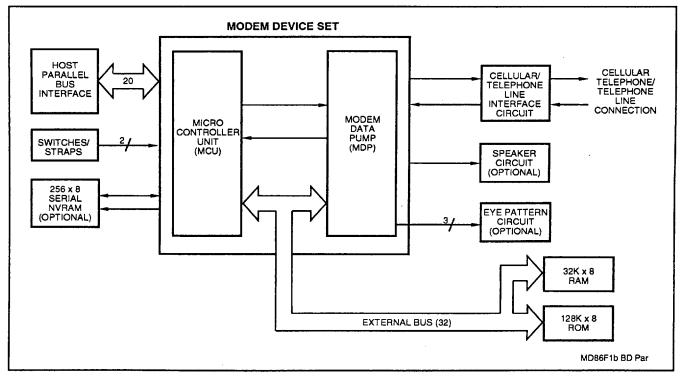

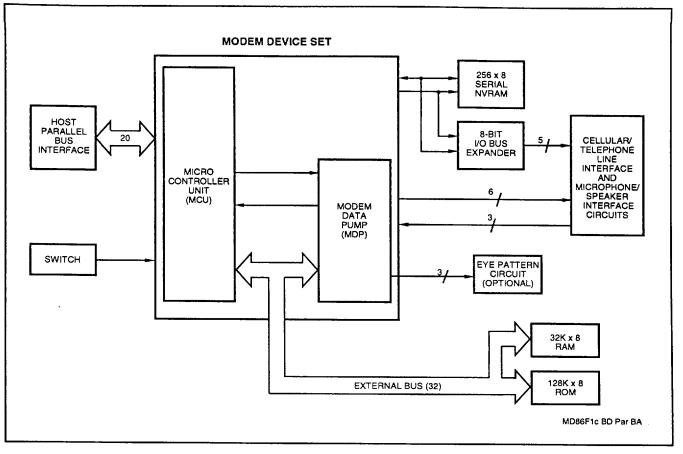

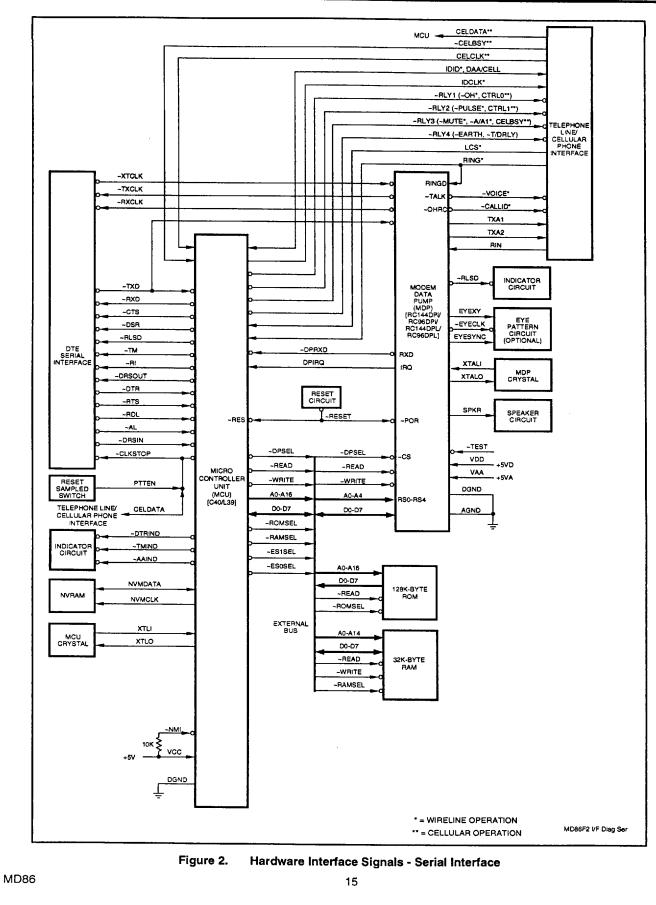

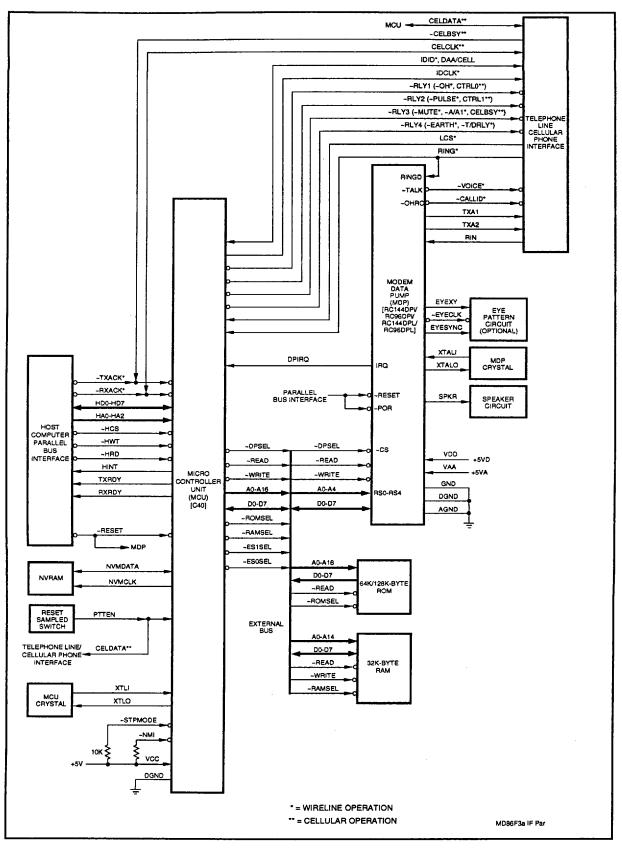

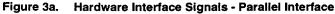

The major hardware signal interfaces of the modem device set are illustrated in Figure 1.

## Parallel Host Bus Interface

A 16450-compatible or 16450/16550A UART-compatible parallel interface is provided depending upon modem model. Eight data lines, three address lines, four DMA request/acknowledge lines, four control/status lines, and a reset line are supported.

### **DTE Serial Interface and Indicator Outputs**

A DTE serial interface and indicator/control outputs are supported.

V.24/EIA/TIA-232-E DTE Serial Interface. A V.24/EIA/TIA-232-E logic-compatible DTE serial interface is supported. A clock stop signal is provided which can be used to turn off transmitter and receiver clocks to the DTE in asynchronous modes.

Indicator Outputs. Four indicator outputs are supported.

### **NVRAM Interface**

A serial interface to an optional OEM-supplied non-volatile RAM (NVRAM) is provided. Data stored in NVRAM can take precedence over the factory default settings. A 256byte NVRAM can store up to two user-selectable configurations and can store up to four 35-digit dial strings.

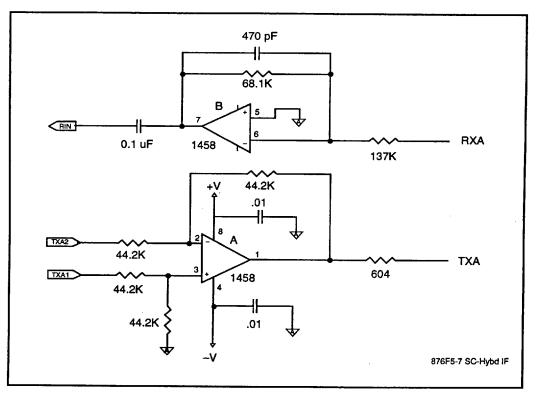

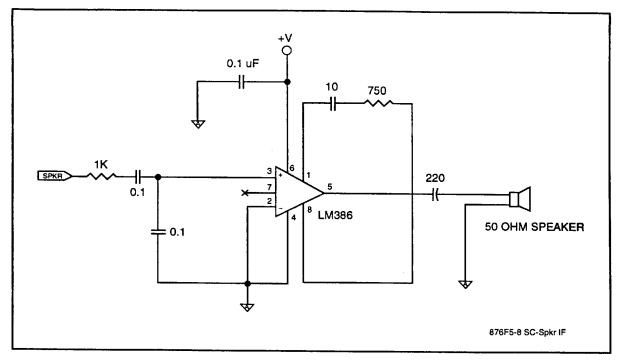

### Speaker Interface

A speaker output, controlled by AT commands, is provided for an optional OEM-supplied speaker circuit.

### **External Bus Interface**

The MCU external bus connects to the MDP and to OEMsupplied ROM and RAM. This non-multiplexed bus supports eight bidirectional data lines and 17 address output lines. Read enable, write enable and chip select outputs (MDP select, ROM select, and RAM select) are also supported.

MD86

3

7811073 0024298 39T 🖿

# Integrated Data/Fax/Voice Modem Device Set

Figure 1b. Block Diagram - Parallel Interface

MD86

M 7811073 0024299 226 M

# RC144ACi and RC144ACL

Figure 1c. Block Diagram - Parallel Interface with Business Audio

MD86

5

## 🖬 78JJ073 0024300 878 📰

## Integrated Data/Fax/Voice Modem Device Set

#### Telephone Line Interface

**MCU.** Wireline operation is selected when a DAA interface is indicated on the DAA/CELL input or when a cellular *interface is indicated* on the DAA/CELL input but no cellular firmware driver is loaded. Four relay control outputs to the line interface are supported. These outputs may be used to control relays such as off-hook, pulse, mute, A/A1, earth, and talk/data. The MCU accepts ring signal and line current sense from the line interface.

**MDP.** A receive analog input, two transmit analog outputs, two relay driver outputs, and a ring signal input are supported. The relay outputs may be used to drive Caller ID and voice relays.

#### **Business Audio Interface**

The MCU outputs two encoded analog switch control signals to select RIN and TXA1/TXA2 routing. In addition, three outputs are provided to select volume control, control volume up/down direction, and volume increment.

#### **Cellular Phone Interface**

**MCU.** Cellular operation is selected when a cellular interface is indicated on the DAA/CELL input and a cellular firmware driver is loaded. Signals supported are two encoded control outputs (CTRL0 and CTRL1), a bidirectional serial data line (CELDATA), a data clock input (CELCLK), a cellular busy output (CELBSY), and a cellular busy input (~CELBSY). Host DMA is not available in parallel interface operation when cellular is selected.

**MDP.** A receive analog input, two transmit analog outputs, two relay driver outputs, and a ring signal input are supported.

#### **Eye Pattern Generator Interface**

Eye pattern data, clock, and sync interface signals are provided to allow an external eye pattern generator circuit to be easily added in order to observe data modem performance relative to line impairments.

**Microsoft Windows Interface.** Microsoft Windows is supported in the host using the proprietary RHSI. The use of RHSI overcomes the limitation of predefined UART speeds. Support for RHSI is in the form of modem microcomputer firmware and Windows driver RHSICOMM.DRV. The Rockwell RHSICOMM.DRV driver is downward compatible with the standard Microsoft Windows communications driver COMM.DRV.

#### COMMANDS

The modem supports data modem, fax class 1 and 2, and MNP 10 commands, and S Registers (see Tables 2 and 3, respectively) in accordance with modem model options.

Data Modem Operation. Data modem functions operate in response to the basic AT commands when +FCLASS=0. Default parameters support US/Canada operation.

**MNP 10 Operation.** MNP 10 functions operate in response to MNP 10 commands.

AutoSync Operation. AutoSync operates in response to the &Q4 command.

**Fax Modem Operation.** Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or #CLS=1 or to fax class 2 commands when +FCLASS=2 or #CLS=2.

**Voice Operation.** Voice mode functions operate in response to voice/audio commands when #CLS=8 and #VBS=2 or #VBS=4 is selected.

Audio Operation. Audio mode functions operate in response to voice/audio commands when #CLS=8 and #VBS=8 or #VBS=16 is selected. Sampling rate is determined by #VSR=11025 or #VSR=7200.

**Cellular Operation.** Cellular functions operate when a cellular phone driver is loaded and a cellular phone interface is detected.

World Class (W-Class) Operation. W-class functions operate in response to W-class AT commands.

### DTE SERIAL INTERFACE OPERATION

## Automatic Speed/Format Sensing

The modem can automatically determine the speed and format of the data sent from the DTE. The modem can sense speeds of 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 19200, 38400, and 57600 bps, and the following data formats:

| Parity | Data Length<br>(No. of Bits) | No. of<br>Stop Bits | Character<br>Length<br>(No. of<br>Bits) |

|--------|------------------------------|---------------------|-----------------------------------------|

| None   | 7                            | 2                   | 10                                      |

| Odd    | 7                            | 1                   | 10                                      |

| Even   | 7                            | 1                   | 10                                      |

| None   | 8                            | 1                   | 10                                      |

| Odd    | 8                            | 1                   | 11*                                     |

| Even   | 8                            | 1                   | 11*                                     |

|        |                              |                     |                                         |

\* 11-bit characters are sensed, but the parity bits are stripped off during data transmission in Normal and Error Correction modes. Direct mode does not strip off the parity bits.

The modem can speed sense data with mark or space parity and configures itself as follows:

| DTE Configuration | Modem Configuration |

|-------------------|---------------------|

| 7 mark            | 7 none              |

| 7 space           | 8 none              |

| 8 mark            | 8 none              |

| 8 space           | 8 even              |

### HOST PARALLEL BUS INTERFACE OPERATION

The modem can operate at rates up to 57600 bps by programming the Divisor Latch in the parallel interface registers.

7811073 0024301 704 📟

<sup>6</sup>

AT Commands

Table 2.

### **ESTABLISHING DATA MODEM CONNECTIONS**

### **Telephone Number Directory**

The modern supports four telephone number entries in a directory that can be saved in a serial NVRAM. Each telephone number can be up to 35 characters in length. A telephone number can be saved using the &Zn=x command, and a saved telephone number can be dialed using the DS=n command.

#### Dialing

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with CCITT Q.23. The transmit tone level complies with Bell Publication 47001.

**Pulse Dialing.** Pulse dialing is supported in accordance with EIA/TIA-496-A.

Blind Dialing. The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

### Modem Handshaking Protocol

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

#### **Answer Tone Detection**

Answer tone can be detected over the frequency range of 2100  $\pm$  40 Hz in CCITT modes and 2225  $\pm$  40 Hz in Bell modes.

#### **Ring Detection**

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

#### **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to allow transmission of the billing signal.

#### **Connection Speeds**

The possible data connection modes/speeds are in Table 4.

Two methods of establishing a connection are supported: use of the F command and use of N command, speed sense, and S37 register combination.

#### Automode

Automode detection can be enabled by the N1 or F0 commands to allow the modem to connect to a remote modem in accordance with EIA/TIA-PN2330.

| Command   | Function                                      |

|-----------|-----------------------------------------------|

|           | Basic AT Commands                             |

| A/        | Re-execute command                            |

| Α         | Answer a call                                 |

| Bn        | Set CCITT or Bell mode                        |

| Cn        | Carrier control                               |

| Dn        | Dial (originate a call)                       |

| E         | Command echo                                  |

| Fn        | Select line modulation                        |

| Hn        | Disconnect (hang-up)                          |

| In        | Identification                                |

| Ln        | Speaker volume                                |

| Mn        | Speaker control                               |

| Nn        | Automode enable                               |

| On        | Return to on-line data mode                   |

| P         | Set pulse dial default                        |

| Qn        | Quiet results codes control                   |

| Sn=x      | Write to S Register                           |

| Sn?       | Read S Register                               |

| T         | Set tone dial default                         |

| Vn        | Result code form                              |

| Wn        | Error correction message control              |

| Xn        | Extended result codes                         |

| Yn        | Long space disconnect                         |

| Zn        | Soft reset and restore profile                |

| &Cn       | RLSD (DCD) option                             |

| &Dn       | DTR option                                    |

| &F        | Restore factory configuration (profile)       |

| &Gn       | Select guard tone                             |

| &Jn       | Telephone jack control                        |

| &Kn       | Flow control                                  |

| &Ln       | Leased line operation                         |

| &Mn       | Asynchronous/synchronous mode selection       |

| &Pn       | Select pulse dial make/break ratio            |

| &Qn       | Asynchronous/synchronous mode selection       |

| &Rn       | RTS/CTS option                                |

| &Sn       | DSR override                                  |

| &Tn       | Test and diagnostic                           |

| &V        | Display current configuration and stored      |

| ~*        | profiles                                      |

| &Wn       | Store current configuration                   |

| &Xn       | Select synchronous clock source               |

| &Yn       | Designate a default reset profile             |

| &Zn=x     | Store phone number                            |

| %En       | Enable/disable line quality monitor and auto- |

|           | retrain or fallback/fall forward              |

| %L        | Report line signal level                      |

| %Q        | Report line signal quality                    |

| %TTn      | PTT testing utilities                         |

| \Kn       | Break control                                 |

| \Nn       | Operating mode                                |

| #CID      | Caller ID detection and reporting             |

| **        | Download to flash memory                      |

|           | Cellular Commands                             |

| 100       |                                               |

| ^C2       | Download Cellular Phone Driver                |

| <u>^ </u> | Identify Cellular Phone Driver                |

| ^T6       | Indicate Status Of Cellular Phone             |

**MD86**

## 7811073 0024302 640 🛙

### Powered by ICminer.com Electronic-Library Service CopyRight 2003

| Table 2. | AT Commands | (Cont'd)       |

|----------|-------------|----------------|

|          |             | ( <del>-</del> |

| Command    | Function                                 |

|------------|------------------------------------------|

|            | ECC AT Commands                          |

| %С         |                                          |

| ∿C<br>IVAn | Select data compression                  |

|            | Maximum MNP block size                   |

| \Bn        | Transmit BREAK to remote                 |

|            | MNP 10 AT Commands                       |

| )Mn        | Enable/disable cellular power level      |

|            | adjustment                               |

| * Hn       | Set link negotiation speed               |

| -Kn        | MNP extended services                    |

| -Qn        | Enable fallback to V.22 bis/V.22         |

| @Mn        | Select initial transmit level            |

| :E         | Compromise equalizer enable              |

|            | Fax Class 1 AT+F Commands                |

| +FCLASS=n  | Service class                            |

| +FAE       | Data/fax auto answer                     |

| +FTS=n     | Stop transmission and wait               |

| +FRS=n     | Receive silence                          |

| +FTM=n     | Transmit data                            |

| +FRM=n     | Receive data                             |

| +FTH=n     | Transmit data with HDLC framing          |

| +FRH=n     | Receive data with HDLC framing           |

|            | Fax Class 2 AT+F Commands                |

| +FCLASS=n  | Service class                            |

|            | Class 2 Action Commands                  |

| +FCIG      | Set the polled station identification    |

| +FDT       | Data transmission                        |

| +FET=N     | Transmit page punctuation                |

| +FDR       | Begin or continue Phase C receive data   |

| +FK        | Terminate session                        |

| +FLPL      | Document for polling                     |

| +FSPL      | Enable polling                           |

|            | Class 2 DCE Responses                    |

| +FCIG:     | Report the polled station identification |

| +FCON      | Facsimile connection response            |

| +FDCS:     | Report current session                   |

| +FDIS:     | Report remote capabilities               |

| +FDTC:     | Report the polled station capabilities   |

| +FCFR      | Indicate confirmation to receive         |

| +FTSI:     | Report the transmit station ID           |

| +FCSI:     | Report the called station ID             |

| +FPTS:     | Page transfer status                     |

| +FET:      | Post page message response               |

| +FHNG:     | Call termination with status             |

| +FPOLL     | Indicates polling request                |

| -          | Class 2 Session Parameters               |

| +FMFR?     | Identify manufacturer                    |

| +FMDL?     | Identify model                           |

| +FREV?     | Identify revision                        |

| +FDCC      | DCE capabilities parameters              |

| +FDIS      | Current sessions parameters              |

| +FDCS      | Current session results                  |

| +FLID      | Local ID string                          |

| +FPTS      | Page transfer status                     |

| +FCR       | Capability to receive                    |

| +FAA       | Adaptive answer                          |

| +FBUF?     | Buffer size (read only)                  |

| +FPHCTO    | Phase C time out                         |

| +FAXERR?   | Fax error value                          |

| +FBOR      | Phase C data bit order                   |

|            |                                          |

| Table 2. | AT Commands | (Cont'd) |

|----------|-------------|----------|

|          |             |          |

| Command | Function                                 |

|---------|------------------------------------------|

|         | Voice AT# Commands                       |

| #BDR    | Select baud rate                         |

| #CLS    | Select data, fax, or voice               |

| #MDL?   | Identify model                           |

| #MFR?   | Identify manufacturer                    |

| #REV?   | Identify revision level                  |

| #VBQ?   | Query buffer size                        |

| #VBS    | Bits per sample                          |

| #VBT    | Beep tone timer                          |

| #VCI?   | Identify compression method              |

| #VLS    | Voice line select                        |

| #VRA    | Ringback goes away timer (originate)     |

| #VRN    | Ringback never came timer (originate)    |

| #VRX    | Voice receive mode                       |

| #VSD    | Enable silence deletion                  |

| #VSK    | Buffer skid setting                      |

| #VSP    | Silence detection period (voice receive) |

| #VSR    | Sampling rate selection                  |

| #VSS    | Silence detection tuner (voice receive)  |

| #VTD    | DTMF/tone reporting                      |

| #VTS    | Generate tone signals                    |

| #VTX    | Voice transmit mode                      |

|         | W-Class AT Commands                      |

| *B      | Display blacklisted numbers              |

| *D      | Display delayed numbers                  |

| *NCnn   | Country select                           |

8

7811073 0024303 587

MD86

# RC144ACi and RC144ACL

## Table 3. S Registers

| S0       Rings to auto-answer         S1       Ring counter         S2       Escape character         S3       Carriage return character         S4       Line feed character         S5       Backspace character         S6       Maximum time to wait for dial tone         S7       Wait for carrier         S8       Pause time for dial delay modifier         S9       Carrier detect response time         S11       DTMF Tone Duration         S12       Escape code guard time         S13       Reserved         S14       General bit mapped options         S15       Reserved         S16       Test timer         S19-S20       Reserved         S21       V24/general bit mapped options         S22       Speaker/results bit mapped options         S23       General bit mapped options         S24       Sleep inactivity timer         S25       Delay to DTR (CT108) off         S26       Reserved         S31       General bit mapped options         S28       General bit mapped options         S29       Flash modifier time         S31       General bit-mapped options <td< th=""><th>Register</th><th>Function</th></td<> | Register | Function                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------|

| S1       Ring counter         S2       Escape character         S3       Carriage return character         S4       Line feed character         S5       Backspace character         S6       Maximum time to wait for dial tone         S7       Wait for carrier         S8       Pause time for dial delay modifier         S9       Carrier detect response time         S10       Carrier loss disconnect time         S11       DTMF Tone Duration         S12       Escape code guard time         S13       Reserved         S14       General bit mapped options         S15       Reserved         S16       Test mode bit mapped options (&T)         S17       Reserved         S18       Test timer         S19-S20       Reserved         S21       V24/general bit mapped options         S22       Speaker/results bit mapped options         S23       General bit mapped options         S24       Sleep inactivity timer         S33       General bit mapped options         S24       Sleep inactivity timer         S33       XOFF character         S34       General bit-mapped options      S                                     | SO       | Rings to auto-answer           |

| S2Escape characterS3Carriage return characterS4Line feed characterS5Backspace characterS6Maximum time to wait for dial toneS7Wait for carrierS8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS34Delay before forced hangupS39Flow controlS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93ReservedS44SleepiretS36LAPM failure controlS42-S                                                                                                                                                                     | S1       | -                              |

| S3Carriage return characterS4Line feed characterS5Backspace characterS6Maximum time to wait for dial toneS7Wait for carrierS8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS32XON characterS33XOFF characterS34Sleps for forced hangupS39Flow controlS41General bit-mapped optionsS41General bit-mapped optionsS42SkesrvedS36Leay before forced hangupS39Flow controlS42-S45ReservedS41General bit-mapped optionsS42SkesrvedS41General bit-mapped optionsS42ReservedS37Line connection speedS38                                                                                                                                                                          | S2       | -                              |

| S4Line feed characterS5Backspace characterS6Maximum time to wait for dial toneS7Wait for carrierS8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS32XON characterS33XOFF characterS34S35S34Delay before forced hangupS39Flow controlS42-S45ReservedS41General bit-mapped optionsS42-S45ReservedS36LAPM failure controlS46Data compression controlS46Data compression controlS46Data compression controlS42Break handling controlS43S35S44S45S45S45S45S45S45S                                                                                                                                                                                                              | S3       |                                |

| S5Backspace characterS6Maximum time to wait for dial toneS7Wait for carrierS8Pause time for dial delay modifierS9Carrier loss disconnect timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS34Delay before forced hangupS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93ReservedS41General bit-mapped optionsS42-S45ReservedS36LAPM failure controlS46Data compression controlS46Data compression controlS46Data compression controlS46Dat                                                                                                                                                   | S4       | -                              |

| S6Maximum time to wait for dial toneS7Wait for carrierS8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34Delay before forced hangupS34Delay before forced hangupS34Delay before forced hangupS34ReservedS37Line connection speedS36Delay before forced hangupS41General bit-mapped optionsS41General bit-mapped optionsS42St ransmit attenuation levelS35ReservedS41General bit-mapped optionsS42St ransmit attenuation level <tr< td=""><td>S5</td><td></td></tr<>                                                                                               | S5       |                                |

| S7Wait for carrierS8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XOFF characterS33XOFF characterS34-S35ReservedS37Line connection speedS41General bit-mapped optionsS41General bit-mapped optionsS41General bit-mapped optionsS42S24S44SeervedS41General bit-mapped optionsS42S25ReservedS41General bit-mapped optionsS42SeervedS43Delay before forced hangupS44SeervedS45ReservedS46Data compr                                                                                                                                                                                                | S6       |                                |

| S8Pause time for dial delay modifierS9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS40General bit-mapped optionsS41General bit-mapped optionsS41General bit-mapped optionsS41General bit-mapped optionsS42SPERvedS33XOFF characterS34S5ReservedS31General bit-mapped optionsS41General bit-mapped optionsS42SPERvedS33XOFF characterS34S5ReservedS39Flow controlS40General bit-mapped opti                                                                                                                                                                                       | S7       |                                |

| S9Carrier detect response timeS10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42SPervedS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42SPervedS34SPErvedS35ReservedS41General bit-mapped optionsS42SPErvedS41General bit-mapped optionsS42SPErvedS41General bit-mapped optionsS42ReservedS41General bi                                                                                                                                                                                                         | S8       |                                |

| S10Carrier loss disconnect timeS11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XOFF characterS33XOFF characterS34-S35ReservedS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS46Data compression controlS46Data compression controlS46Data compression controlS46Data compression controlS46Data compression controlS46<                                                                                                                                          | S9       | Carrier detect response time   |

| S11DTMF Tone DurationS12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (C1108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93ReservedS91PSTN transmit attenuation levelS92Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiatio                                                                                                                                                   |          |                                |

| S12Escape code guard timeS13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS22XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS44Superistion controlS46Data compression controlS46Data compression controlS48V.42 negotiation controlS48S42-S45S95Reselltace                                                                                                                                                        |          |                                |

| S13ReservedS14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit-mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS41General bit-mapped optionsS42ServedS37Line connection speedS41General bit-mapped optionsS42ServedS36Delay before forced hangupS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS92Fax transmit attenuation levelS92Fax transmit attenuation levelS92Sensit code messages controlS36LAPM failure controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS49Break handling controlS40Cel                                                                                                                                                   |          |                                |

| S14General bit mapped optionsS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93LAPM failure controlS46Data compression controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V                                                                                                                        |          |                                |

| S15ReservedS15ReservedS16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS94Sace servedS91PSTN failure controlS46Data compression controlS48V.42 negotiation controlS49Break handling controlS49Break handli                                                                                                                                                   |          |                                |

| S16Test mode bit mapped options (&T)S17ReservedS18Test timerS19-S20ReservedS21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS92Fax transmit attenuation levelS93Result code messages controlS94S16S36LAPM failure controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48S16S48V.42 negotiation controlS46S48S46S48S46S48S46S48S46S48S46S48S46S48S46S48S46S48 </td <td></td> <td></td>                                                                                                                                                                                                             |          |                                |

| \$17Reserved\$18Test timer\$19-\$20Reserved\$21V24/general bit mapped options\$22Speaker/results bit mapped options\$23General bit mapped options\$24Sleep inactivity timer\$25Delay to DTR (CT108) off\$26RTS-to-CTS (CT105-to-CT106) delay\$27General bit mapped options\$28General bit-mapped options\$29Flash modifier time\$30Inactivity timer\$31General bit-mapped options\$32XON character\$33XOFF character\$34-S35Reserved\$37Line connection speed\$38Delay before forced hangup\$39Flow control\$40General bit-mapped options\$42-S45Reserved\$91PSTN transmit attenuation level\$92Fax transmit attenuation level\$93Reserved\$94S7\$95Result code messages control\$95Result code messages control\$95Result code messages control\$95Result code messages control\$96LAPM failure control\$97Sata compression control\$98V.42 negotiation control\$99Break handling control\$90Result code messages control\$91PSTN transmit attenuation level\$92Fax transmit attenuation level\$93Result code messages control\$94Data compression control <t< td=""><td>-</td><td></td></t<>                                                             | -        |                                |

| \$18Test timer\$19-S20Reserved\$21V24/general bit mapped options\$22Speaker/results bit mapped options\$23General bit mapped options\$24Sleep inactivity timer\$25Delay to DTR (CT108) off\$26RTS-to-CTS (CT105-to-CT106) delay\$27General bit mapped options\$28General bit-mapped options\$29Flash modifier time\$30Inactivity timer\$31General bit-mapped options\$32XON character\$33XOFF character\$34-S35Reserved\$37Line connection speed\$38Delay before forced hangup\$39Flow control\$40General bit-mapped options\$41General bit-mapped options\$42-S45Reserved\$91PSTN transmit attenuation level\$92Fax transmit attenuation level\$93Result code messages control\$94Data compression control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$49Break handling control                                                                                                                                                                                                                                                                                                      |          |                                |

| \$19-\$20Reserved\$21V24/general bit mapped options\$22Speaker/results bit mapped options\$23General bit mapped options\$24Sleep inactivity timer\$25Delay to DTR (CT108) off\$26RTS-to-CTS (CT105-to-CT106) delay\$27General bit mapped options\$28General bit-mapped options\$29Flash modifier time\$30Inactivity timer\$31General bit-mapped options\$32XON character\$33XOFF character\$34-\$35Reserved\$37Line connection speed\$38Delay before forced hangup\$39Flow control\$40General bit-mapped options\$41General bit-mapped options\$42-\$45Reserved\$91PSTN transmit attenuation level\$92Fax transmit attenuation level\$93Result code messages control\$94Data compression control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$49Break handling control                                                                                                                                                                                                                                                                                                                 |          |                                |

| S21V24/general bit mapped optionsS22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS94ECC S RegistersS36LAPM failure controlS48V.42 negotiation controlS48 <t< td=""><td></td><td></td></t<>                                                                                    |          |                                |

| S22Speaker/results bit mapped optionsS23General bit mapped optionsS24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS93Result code messages controlS94S95S36LAPM failure controlS42Sat compression controlS46Data compression controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS49Break handling control                                                                                                                                                                                                                                                                                                                                                                      |          |                                |

| \$23General bit mapped options\$24Sleep inactivity timer\$25Delay to DTR (CT108) off\$26RTS-to-CTS (CT105-to-CT106) delay\$27General bit mapped options\$28General bit-mapped options\$29Flash modifier time\$30Inactivity timer\$31General bit-mapped options\$32XON character\$33XOFF character\$34-S35Reserved\$37Line connection speed\$38Delay before forced hangup\$39Flow control\$40General bit-mapped options\$41General bit-mapped options\$42-S45Reserved\$91PSTN transmit attenuation level\$92Fax transmit attenuation level\$93Result code messages control\$29ECC S Registers\$36LAPM failure control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$48V.42 negotiation control\$49Break handling control                                                                                                                                                                                                                                                                                                                                                                                             |          | v24/general bit mapped options |

| S24Sleep inactivity timerS25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS48V.4                                                                                                                        |          |                                |

| S25Delay to DTR (CT108) offS26RTS-to-CTS (CT105-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS49Break handling controlS40Saters                                                                                                                                                                                                        |          |                                |

| S26RTS-to-CTS (CT105)-to-CT106) delayS27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS49Break handling controlS40Cellular Registers                                                                                                                                                                                                                                                                                                     |          |                                |

| S27General bit mapped optionsS28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48S42S48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48Serek handling controlS48Serek handling control                                                                                                                                                                                                                                                                                                                                |          |                                |

| S28General bit-mapped optionsS29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS48V.42 negotiation controlS48V.42 negotiation controlS48S42S48V.42 negotiation controlS48V.42 negotiation control <tr< td=""><td></td><td></td></tr<>                                                                                                 |          |                                |

| S29Flash modifier timeS30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS82Break handling controlS82Break handling control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                |

| S30Inactivity timerS31General bit-mapped optionsS32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS46Data compression controlS48V.42 negotiation controlS82Break handling controlCellular Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |                                |

| S31       General bit-mapped options         S32       XON character         S33       XOFF character         S34-S35       Reserved         S37       Line connection speed         S38       Delay before forced hangup         S39       Flow control         S40       General bit-mapped options         S41       General bit-mapped options         S42-S45       Reserved         S91       PSTN transmit attenuation level         S92       Fax transmit attenuation level         S95       Result code messages control         S36       LAPM failure control         S48       V.42 negotiation control         S48       V.42 negotiation control         S82       Break handling control                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                                |

| S32XON characterS33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS92Fax transmit attenuation levelS95Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS82Break handling controlCellular Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                |

| S33XOFF characterS34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS82Break handling controlCellular Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                |

| S34-S35ReservedS37Line connection speedS38Delay before forced hangupS39Flow controlS40General bit-mapped optionsS41General bit-mapped optionsS42-S45ReservedS91PSTN transmit attenuation levelS92Fax transmit attenuation levelS95Result code messages controlS36LAPM failure controlS48V.42 negotiation controlS82Break handling controlCellular Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                                |