### Thin Film Technology. Delay Lines. Because Timing is Everything.<sup>tm</sup>

### **T**ABLE of **C**ONTENTS

| Contents                                                                                             |           |

|------------------------------------------------------------------------------------------------------|-----------|

| Introduction                                                                                         |           |

| Definitions                                                                                          | 4         |

| Delay Line Test Methods                                                                              | 5         |

| High Frequency Delay Lines<br>Single In Line DL1 Series                                              | 6-7       |

| Surface Mount GL1 Series<br>Surface Mount GL2 Differential Series                                    |           |

| Intermediate Frequency Delay Lines<br>Single In Line DS1 Series                                      | 12-13     |

| Chip Delay Line CL Series                                                                            | 14        |

| Bandwith Considerations                                                                              |           |

| Complimentary Products<br>Positive Emitter Coupled Logic (PECL) Terminator<br>Calibration Standards. |           |

| Footprint Layouts                                                                                    |           |

| Notes                                                                                                |           |

| World Wide Sales OfficesBa                                                                           | ick Cover |

Copyright © by Thin Film Technology 1999

Published by the philter circuits Division, 1980 Commerce Drive, N. Mankato, MN 56003 All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission. Printed in the United States of America.

The component needs for future systems design will be met with higher technology. Thin Film Technology.

igh speed system design needs full wave regime implementation in order to maintain signal fidelity. Harmonics not considered at slower speeds must be accounted for when fast rise times and high bandwidths are to be used. When edge rates and circuit speeds enter the sub-nanosecond regime, all components used in a system design must obey high speed design rules, whether they be packages, devices, integrated circuits, interconnects, or printed circuit boards.

Thin film component design is uniquely appropriate for high frequency design: the precision of pattern features, purity of film, stability of substrate materials, and advanced assembly technologies offer solutions for high speed design. Wave propagation through correctly designed thin film elements provide for precise impedance control, a reduction in capacitive and inductive parasitics, and elimination of ground bounce. Shielded designs protect for electro-magnetic and radio-frequency interference.

I hin Film Technology Corporation manufactures high speed delay lines based on microstrip, stripline, and multi-conductor transmission lines. Available in leaded, surface mount, and chip configuration, these products have performance to 5 gigahertz. New designs and materials are under continuous development to extend this range. It is our philosophy that higher technology components can improve your system performance and lower your costs, both now and in the future.

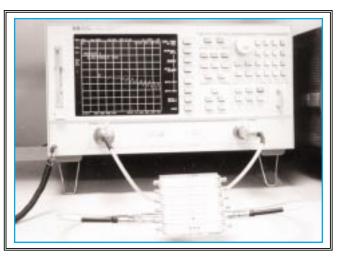

igh frequency measurement is essential to assure correct device characterization. Attention to field patterns is necessary when representing transmission lines in order to understand reflections, mismatches, and skin effects. Test design layout should replicate the field patterns that will actually occur with the real package, so that accurate device characteristics represented by scattering parameters can be made. Proper calibration standards used at the device under test are sine qua non.

### **D**EFINITIONS

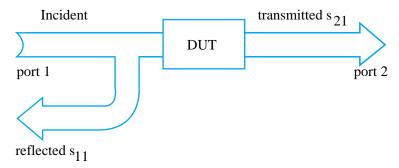

**Scattering Parameters (S-parameters):** a two port numbering convention used commonly at high frequencies relating to network measurements. The first number represents the port where the energy is emerging from the device and the second number is the port where the energy is entering the device.

**Parameter s21:** The forward transmission coefficient indicating the ratio of energy emerging from port 2 to the energy incident to port 1.

**Parameter s11:** The reflected transmission coefficient indicating the ratio of energy emerging from port 1 to the energy incident to port 1.

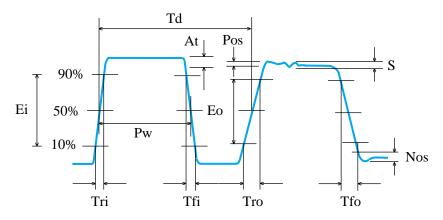

**Time Delay (Td):** The elapsed time from the 50% on the leading edge of the input pulse to the 50% point on the leading edge of the delayed pulse.

**Network Risetime and Fall time(Tr):** The true measure of delayed pulse risetime performance expressed by the following:

$$Tr = \sqrt{(T_r \text{ output})^2 - (T_r \text{ input})^2}$$

**Input Risetime and Falltime (Tri and Tfi):** The time between the 10% and 90% of the input voltage. **Output Risetime and Falltime (Tro and Tfo):** The time between the 10% and 90% of the output voltage. **Input and Output Voltage (Ei and Eo):** The amplitude of the input and output voltages, respectively. **Attenuation (At):** The difference in amplitude between input and output pulses. Attenuation is caused primarily by the Direct Current (DC) resistance of the delay line.

**Pulsewidth (Pw):** The time difference between the 50% point of the leading edge and the 50% point of the trailing edge of the pulse.

**Pulse Distortion (S):** The maximum spurious % change, either positive or negative, relative to the pulse amplitude.

**Pulse Edge Over/Undershoot: (Pos, Nos):** Peak amplitudes occurring at either the top or bottom of the output pulse.

## **D**ELAY **L**INE **T**EST **M**ETHODS

#### Frequency Domain Measurement

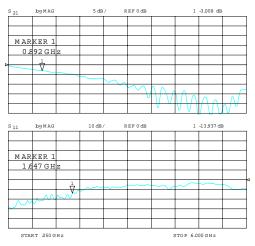

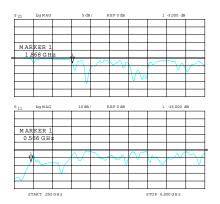

Network analysis may be used to measure insertion loss, return loss, phase and group delay, with signal stimulus both forward and reverse to the device. For our passive delay lines, performance is indicated as loss in the frequency domain.

The graphed information presented in this databook is labeled according

to traditional Scattering parameters (S-parameters).  $S_{21}$  and  $S_{11}$  on the following pages indicates insertion loss (energy incident but lost through the device) and return loss (energy incident but reflected away from the device). The data is presented in summary form, but frequency performance data may be requested for specific part numbers.

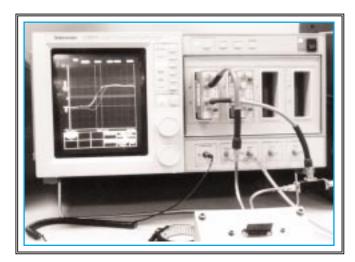

#### Time Domain Measurement

High speed (Rise Time <55 ps) digital signals are used to stimulate the device for Rise time (Tro) and Fall time (Tfo) performance. Data is presented in the time domain, and is another measure indicating frequency performance. Sampling measurements can be used to demonstrate signal fidelity and can be processed by a variety of techniques.

Additionally, Time Domain Reflectometry (TDR) measurements may be made to provide time delay performance as well as detailed impedance mapping of the device transmission structure. TDR measurements can be performed either in a single end driven mode, or in a dual end (differential) driven mode, which is necessary for the GL2L Series Differential Delay Line product.

## **DL** SERIES **D**ELAY **L**INES

U.S. Patent 4,641,113

<u>Application note:</u> for precise high speed digital timing deskew, socket the delay line for custom timing adjustments against lot to lot propagation delay variations in IC devices.

| DL1L5 SERIES 50 ohm                                                     |                                      |                           |                        |         |         |          |  |  |

|-------------------------------------------------------------------------|--------------------------------------|---------------------------|------------------------|---------|---------|----------|--|--|

| P/N                                                                     | Td<br>(ns)                           | Insertion Loss<br>(-3 dB) | Return Loss<br>(15 dB) | Tro     | Tfo     | DCRV     |  |  |

| DL1L5WK010S<br>DL1L5WK020S<br>DL1L5WK030S                               | 0.10<br>0.20<br>0.30                 |                           |                        |         |         | <0.2 ohm |  |  |

| DL1L5WK040S<br>DL1L5WK050S<br>DL1L5XK060S<br>DL1L5XK070S                | 0.40<br>0.50<br>0.60<br>0.70         | >4.5 GHz                  |                        | <200 ps | <200 ps |          |  |  |

| DL1L5XK080S<br>DL1L5XK090S<br>DL1L5XK100S<br>DL1L5XK110S                | 0.80<br>0.90<br>1.00<br>1.10         |                           |                        | <250 ps | <250 mg | <0.4 ohm |  |  |

| DL1L5XK120S<br>DL1L5XK130S<br>DL1L5XK140S                               | 1.20<br>1.30<br>1.40                 |                           |                        | ~250 ps | <250 ps |          |  |  |

| DL1L5XK150S<br>DL1L5XK160S<br>DL1L5XK170S<br>DL1L5XK180S<br>DL1L5XK190S | 1.50<br>1.60<br>1.70<br>1.80<br>1.90 | >2.5 GHz                  |                        | <300 ps | <300 ps | <0.6 ohm |  |  |

| DL1L5XK200S<br>DL1L5XK210S<br>DL1L5XK220S<br>DL1L5XK230S                | 2.00<br>2.10<br>2.20<br>2.30         |                           |                        | <350 ps | <350 ps |          |  |  |

| DL1L5XK240S<br>DL1L5XK250S<br>DL1L5XK260S<br>DL1L5YK270S                | 2.40<br>2.50<br>2.60<br>2.70         |                           | >0.9 GHz               |         |         | <1.0 ohm |  |  |

| DL1L5YK280S<br>DL1L5YK290S<br>DL1L5YK300S<br>DL1L5YK310S<br>DL1L5YK310S | 2.80<br>2.90<br>3.00<br>3.10         | >2.0 GHz                  |                        | <400 ps | <400 ps |          |  |  |

| DL1L5YK320S<br>DL1L5YK330S<br>DL1L5YK340S<br>DL1L5YK350S<br>DL1L5ZK360S | 3.20<br>3.30<br>3.40<br>3.50<br>3.60 |                           |                        | <450 ps | <450 ps | <1.2 ohm |  |  |

| DL1L5ZK370S<br>DL1L5ZK380S<br>DL1L5ZK390S<br>DL1L5ZK400S                | 3.70<br>3.80<br>3.90<br>4.00         | >1.5 GHz                  |                        |         |         | <1.4 ohm |  |  |

| DL1L5ZK410S<br>DL1L5ZK420S<br>DL1L5ZK430S<br>DL1L5ZK440S                | 4.10<br>4.20<br>4.30<br>4.40         |                           |                        | <500 ps | <500 ps | <1.6 ohm |  |  |

| DL1L5ZK450S<br>DL1L5ZK460S<br>DL1L5ZK470S<br>DL1L5ZK480S<br>DL1L5ZK490S | 4.50<br>4.60<br>4.70<br>4.80<br>4.90 | >1.0 GHz                  |                        | <550 ps | <550 ps | <2.0 ohm |  |  |

| DL1L5ZK500S<br>DL1L5ZK510S                                              | 5.00<br>5.10                         |                           |                        |         |         |          |  |  |

## **DL** SERIES **D**ELAY **L**INES

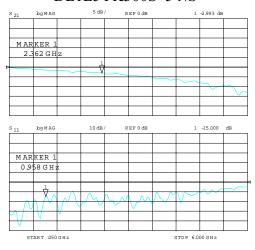

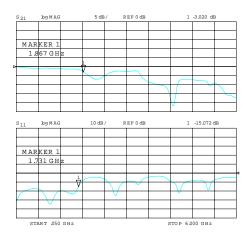

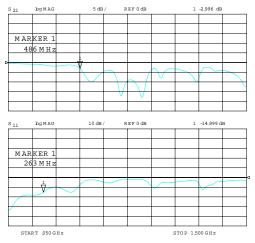

#### DL1L5XK100S 1 NS bgMAG 5 dB REF 0 dB 1 -3.011 dE 21 MARKER 1 4.935 G H z Ť REF 0 dB 1 -15.006 dE s <sub>11</sub> bg M AG 10 dB/ MARKER 1 1.342 G H 2 1 V START 0.050 GHz STOP 6.000 GHz DL1L5YK300S 3 NS

DL1L5ZK500S 5 NS

#### DL1L5 \*\* \*\*\* S

U.S. Patent 4,641,113

DL1L5ZK400S 4 NS

|                            |              | GLI                       | L5 SERIES 5            | <u>su onm</u> |         |          |

|----------------------------|--------------|---------------------------|------------------------|---------------|---------|----------|

| P/N                        | Td<br>(ns)   | Insertion Loss<br>(-3 dB) | Return Loss<br>(15 dB) | Tro           | Tfo     | DCRV     |

| GL1L5LS010S                | 0.10         |                           |                        |               |         |          |

| GL1L5LS020S                | 0.20         |                           |                        |               |         |          |

| GL1L5LS030S                | 0.30         |                           |                        |               |         |          |

| GL1L5LS040S                | 0.40         | >2.50 GHz                 | >0.60 GHz              | <200          | <200    | <1.0 -1  |

| GL1L5LS050S<br>GL1L5LS060S | 0.50<br>0.60 |                           |                        | <200 ps       | <200 ps | <1.0 ohm |

| GL1L5LS080S<br>GL1L5LS070S | 0.80         |                           |                        |               |         |          |

| GL1L5LS080S                | 0.80         |                           |                        |               |         |          |

| GL1L5LS0805                | 0.80         |                           |                        |               |         |          |

| GL1L5LS100S                | 1.00         |                           |                        |               |         |          |

| GL1L5MS110S                | 1.10         | >2.00 GHz                 |                        |               |         |          |

| GL1L5MS120S                | 1.20         |                           |                        |               |         |          |

| GL1L5MS130S                | 1.30         |                           |                        |               |         |          |

| GL1L5MS140S                | 1.40         |                           |                        |               |         |          |

| GL1L5MS150S                | 1.50         |                           |                        |               |         | <2.0 ohm |

| GL1L5MS160S                | 1.60         |                           |                        |               |         |          |

| GL1L5MS170S                | 1.70         |                           |                        |               |         |          |

| GL1L5MS180S                | 1.80         |                           |                        |               |         |          |

| GL1L5MS190S                | 1.90         | >1.50 GHz                 |                        | <400 ps       | <400 ps |          |

| GL1L5MS200S                | 2.00         |                           |                        |               |         |          |

| GL1L5MS210s                | 2.10         |                           |                        |               |         |          |

| GL1L5MS220S                | 2.20         |                           |                        |               |         |          |

| GL1L5MS230S                | 2.30         |                           |                        |               |         |          |

| GL1L5MS240S                | 2.40<br>2.50 |                           |                        |               |         | <3.0 ohm |

| GL1L5MS250S<br>GL1L5MS260S | 2.50         |                           |                        |               |         | <3.0 omn |

| GL1L5MS270S                | 2.00         |                           |                        |               |         |          |

| GL1L5MS280S                | 2.80         |                           |                        |               |         |          |

| GL1L5MS290S                | 2.90         |                           |                        |               |         |          |

| GL1L5MS300S                | 3.00         | >1.00 GHz                 |                        |               |         |          |

| GL1L5MS310S                | 3.10         |                           |                        |               |         |          |

| GL1L5MS320S                | 3.20         |                           |                        |               |         |          |

| GL1L5MS330S                | 3.30         |                           |                        |               |         |          |

| GL1L5MS340S                | 3.40         |                           |                        |               |         |          |

| GL1L5MS350S                | 3.50         |                           |                        |               |         | <4.0 ohm |

| GL1L5MS360S                | 3.60         |                           |                        |               |         |          |

| GL1L5MS370S                | 3.70         |                           |                        |               |         |          |

| GL1L5MS380S                | 3.80         |                           |                        | <600 ps       | <600 ps |          |

| GL1L5MS390S                | 3.90         |                           |                        |               |         |          |

| GL1L5MS400S                | 4.00         |                           |                        |               |         |          |

| GL1L5MS410S                | 4.10         | >0.75 GHz                 |                        |               |         |          |

| GL1L5MS420S                | 4.20         |                           |                        |               |         |          |

| GL1L5MS430S                | 4.30         |                           |                        |               |         |          |

| GL1L5MS440S                | 4.40         |                           |                        |               |         | <5.0 ohm |

| GL1L5MS450S                | 4.50         |                           |                        |               |         | <5.0 onm |

| GL1L5MS460S<br>GL1L5MS470S | 4.60<br>4.70 | >0.50 GHz                 |                        |               |         |          |

| ULILJW134/05               | 4.70         | ~0.50 GHZ                 | 1                      |               |         |          |

|                            | 1 00         |                           |                        |               |         |          |

| GL1L5MS480S<br>GL1L5MS490S | 4.80<br>4.90 |                           |                        |               |         |          |

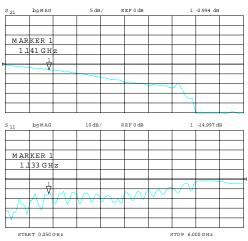

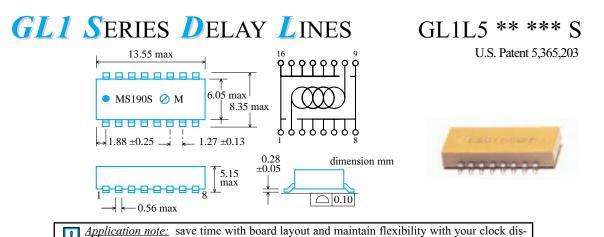

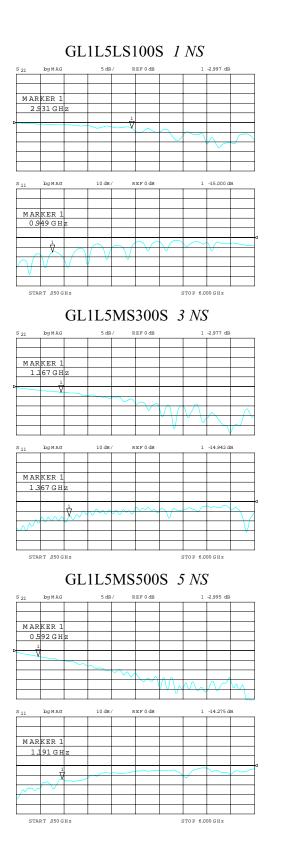

### **GL1 S**ERIES **D**ELAY **L**INES

GL1L5 \*\* \*\*\* S

U.S. Patent 5,365,203

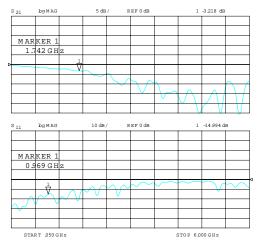

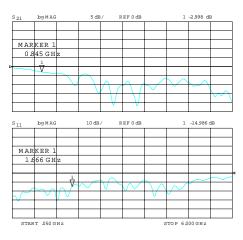

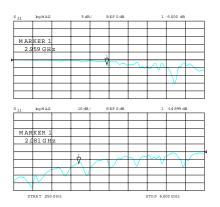

#### GL1L5MS200S 2 NS

GL1L5MS400S 4 NS

## **GL2 S**ERIES **D**ELAY **L**INES

GL2L5 \*\* \*\*\*D U.S. Patent 5,815,050

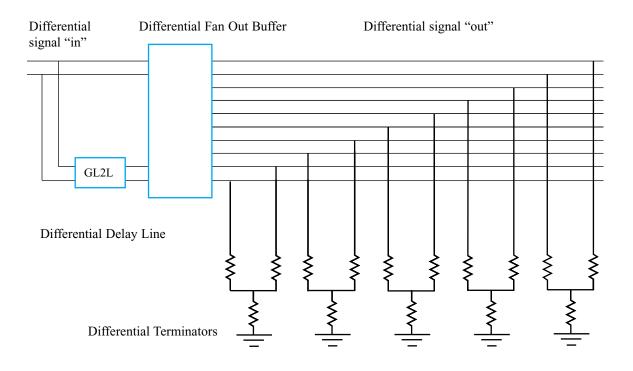

Application note: apply to Positive Emitter Coupled Logic (PECL) or other differentially driven circuits to produce a precisely cotrolled clock distribution network (see page 17).

| Td<br>(ns)   | Insertion Loss R<br>(-3 dB)                          |                                                                                    | Tro                                                                                | Tfo     | DCDU                                       |

|--------------|------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------|--------------------------------------------|

|              |                                                      | Insertion Loss Return Loss<br>(-3 dB) (15 dB)                                      |                                                                                    | 110     | DCRV                                       |

| 0.50<br>1.00 | >1.80 GHz                                            | >0.60 GHz                                                                          | <400 ps                                                                            | <400 ps | <1.0 ohm                                   |

| 1.50         | >0.80 GHz                                            |                                                                                    |                                                                                    |         | <2.0 ohm                                   |

| 2.00         |                                                      |                                                                                    |                                                                                    |         |                                            |

| 2.50         | >0.45 GHz                                            |                                                                                    |                                                                                    |         | <3.0 ohm                                   |

| 3.00         |                                                      |                                                                                    | <800 ps                                                                            | <800 ps |                                            |

| 3.50         |                                                      |                                                                                    |                                                                                    |         | <4.0 ohm                                   |

| 4.00         | >0.25 GHz                                            |                                                                                    |                                                                                    |         |                                            |

| 4.50         |                                                      |                                                                                    |                                                                                    |         | <5.0 ohm                                   |

|              | 1.00<br>1.50<br>2.00<br>2.50<br>3.00<br>3.50<br>4.00 | 1.00<br>1.50 >0.80 GHz<br>2.00<br>2.50 >0.45 GHz<br>3.00<br>3.50<br>4.00 >0.25 GHz | 1.00<br>1.50 >0.80 GHz<br>2.00<br>2.50 >0.45 GHz<br>3.00<br>3.50<br>4.00 >0.25 GHz | 1.00    | 1.00    1    1    1      1.50    >0.80 GHz |

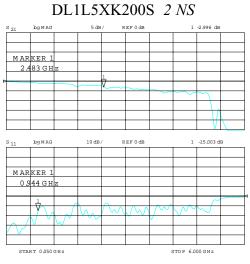

### **GL2 S**ERIES **D**ELAY **L**INES

GL2L5 \*\* \*\*\*D

U.S. Patent 5,815,050

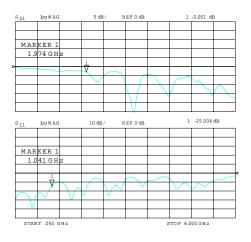

#### GL2L5LS050D 0.5 NS

#### GL2L5MS200D 2 NS

#### GL2L5LS100D 1 NS

GL2L5MS300D 3 NS

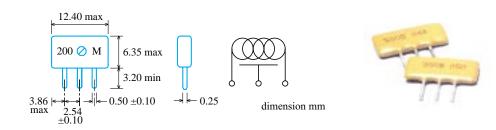

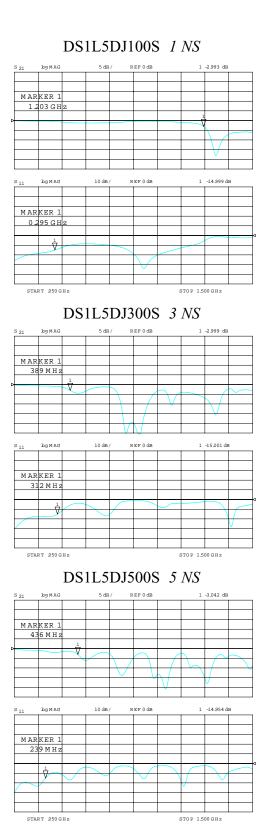

### **DS S**ERIES **D**ELAY **L**INES

Application note: Use the DS delay lines in series with the GL2 delay line during board prototype to define the required timing delay.

| DS1L5 SERIES 50 ohm |            |                               |                            |             |             |               |  |

|---------------------|------------|-------------------------------|----------------------------|-------------|-------------|---------------|--|

| P/N                 | Td<br>(ns) | Insertion Loss<br>GHz (-3 dB) | Return Loss<br>GHz (15 dB) | Tro<br>(ns) | Tfo<br>(ns) | DCRV<br>(ohm) |  |

| DS1L5DJ010S         | 0.10       | >1.000                        | >1.000                     |             |             | < 0.10        |  |

| DS1L5DJ020S         | 0.20       | 0.900                         | 0.750                      |             |             | 0.20          |  |

| DS1L5DJ030S         | 0.30       | 0.700                         | 0.650                      |             |             | 0.30          |  |

| DS1L5DJ040S         | 0.40       | 0.650                         | 0.475                      | < 0.50      | < 0.50      | 0.40          |  |

| DS1L5DJ050S         | 0.50       | 0.600                         | 0.450                      |             |             | 0.50          |  |

| DS1L5DJ060S         | 0.60       | 0.550                         | 0.375                      |             |             | 0.60          |  |

| DS1L5DJ070S         | 0.70       | 0.500                         | 0.350                      |             |             | 0.70          |  |

| DS1L5DJ080S         | 0.80       | 0.500                         | 0.300                      |             |             | 0.80          |  |

| DS1L5DJ090S         | 0.90       | 1.200                         |                            | 0.50        | 0.50        |               |  |

| DS1L5DJ100S         | 1.00       | 1.100                         | 0.300                      | 0.55        | 0.55        | 0.25          |  |

| DS1L5DJ110S         | 1.10       | 1.000                         |                            | 0.60        | 0.60        |               |  |

| DS1L5DJ120S         | 1.20       | 1.000                         |                            | 0.65        | 0.65        |               |  |

| DS1L5DJ130S         | 1.30       | 0.950                         | 0.275                      | 0.70        | 0.70        | 0.30          |  |

| DS1L5DJ140S         | 1.40       | 0.900                         |                            | 0.75        | 0.75        |               |  |

| DS1L5DJ150S         | 1.50       | 0.850                         |                            | 0.80        | 0.80        |               |  |

| DS1L5DJ160S         | 1.60       | 0.800                         |                            | 0.85        | 0.85        | 0.50          |  |

| DS1L5DJ170S         | 1.70       | 0.750                         | 0.250                      | 0.90        | 0.90        |               |  |

| DS1L5DJ180S         | 1.80       | 0.700                         |                            | 0.95        | 0.95        |               |  |

| DS1L5DJ190S         | 1.90       | 0.650                         |                            | 1.00        | 1.00        | 0.70          |  |

| DS1L5DJ200S         | 2.00       | 0.600                         | 0.550                      | 1.05        | 1.05        |               |  |

| DS1L5DJ225S         | 2.25       | 0.550                         | 0.500                      | 1.10        | 1.10        |               |  |

| DS1L5DJ250S         | 2.50       | 0.500                         | 0.450                      | 1.25        | 1.25        |               |  |

| DS1L5DJ275S         | 2.75       | 0.450                         | 0.400                      | 1.35        | 1.35        | 1.00          |  |

| DS1L5DJ300S         | 3.00       | 0.400                         | 0.300                      | 1.45        | 1.45        |               |  |

| DS1L5DJ325S         | 3.25       | 0.550                         |                            |             |             | 1.10          |  |

| DS1L5DJ350S         | 3.50       |                               |                            | 1.00        | 1.00        | 1.20          |  |

| DS1L5DJ375S         | 3.75       | 0.450                         | 0.250                      |             |             | 1.30          |  |

| DS1L5DJ400S         | 4.00       |                               |                            |             |             | 1.40          |  |

| DS1L5DJ425S         | 4.25       | 0.425                         |                            |             |             | 1.50          |  |

| DS1L5DJ450S         | 4.50       |                               |                            | 1.10        | 1.10        | 1.60          |  |

| DS1L5DJ475S         | 4.75       | 0.400                         |                            |             |             | 1.70          |  |

| DS1L5DJ500S         | 5.00       |                               | 0.225                      |             |             | 1.80          |  |

| DS1L5VJ550S         | 5.50       | 0.375                         |                            |             |             | 2.00          |  |

| DS1L5VJ600S         | 6.00       | 0.350                         |                            | 1.15        | 1.15        | 2.20          |  |

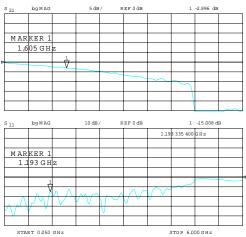

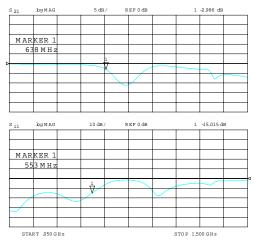

### **DS S**ERIES **D**ELAY **L**INES

#### DS1L5 \*\* \*\*\* S

U.S. Patent 4,641,113

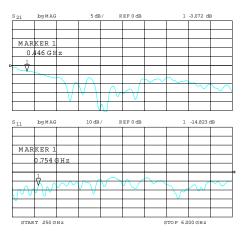

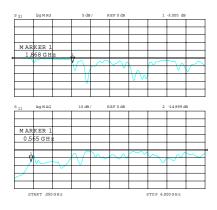

#### DS1L5DJ200S 2 NS

DS1L5DJ400S 4 NS

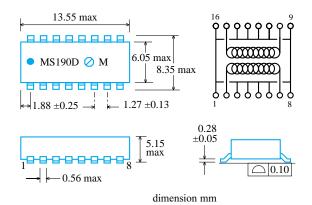

## **CL** SERIES **D**ELAY **L**INES

**1** <u>Application note:</u> Use for ultra-precise delay adjustments where circuit trace is nearly adequate on the smallest of boards. Use for phase-locked loop timing schemes.

| CL1L5 SERIES 50 ohm |            |                                |                          |             |             |               |  |

|---------------------|------------|--------------------------------|--------------------------|-------------|-------------|---------------|--|

| P/N                 | Td<br>(ps) | Insertion Loss<br>GHz(-3 dB) G | Return Loss<br>Hz(15 dB) | Tro<br>(ps) | Tfo<br>(ps) | DCRV<br>(ohm) |  |

| CL1L52H002S         | 20         | 2.4                            | 0.600                    |             |             |               |  |

| CL1L52H004S         | 40         | 2.3                            |                          | <10         | <10         | < 0.30        |  |

| CL1L52H006S         | 60         | 2.2                            |                          |             |             |               |  |

| CL1L52H008S         | 80         | 2.1                            |                          |             |             |               |  |

| CL1L52H010S         | 100        | 2.0                            |                          |             |             |               |  |

| CL1L52H012S         | 120        | 1.9                            |                          |             |             |               |  |

| CL1L52H014S         | 140        | 1.8                            |                          |             |             |               |  |

| CL1L52H016S         | 160        | 1.7                            |                          | 20          | 20          | 0.60          |  |

| CL1L52H018S         | 180        | 1.6                            |                          |             |             |               |  |

| CL1L52H020S         | 200        | 1.5                            |                          |             |             |               |  |

#### CL1L52H002S 0.02 NS

#### CL1L52H020S 0.20 NS

#### CL1L52H016S 0.16 NS

### **B**ANDWIDTH **C**ONSIDERATIONS

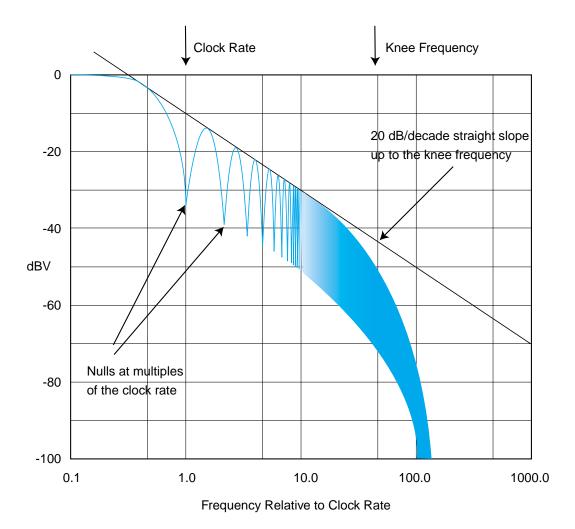

igh frequency signals with fast rise and fall times can push circuit elements to their limit in high speed digital design. Below illustrates what happens in the relationship between a random digital pulse train and the important part of the frequency spectrum when an output is flip-flop clocked at a rate of Fclock with a risetime Tr that is 1% of the clock period.

The plotted spectral power density displays nulls at multiples of the clock rate and an overall -20dB/decade slope from  $F_{clock}$  up to  $F_{knee}$ , where the roll off is faster. The knee frequency for a digital signal is related to the rise and fall times, not the clock rate:

$$F_{\text{knee}} = \frac{0.5}{\text{Tr}}$$

,  $F_{\text{knee}} =$  the frequency which most energy in digital pulses concentrates

$T_{\text{r}} =$  pulse rise time

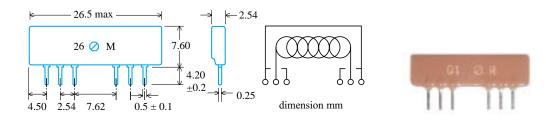

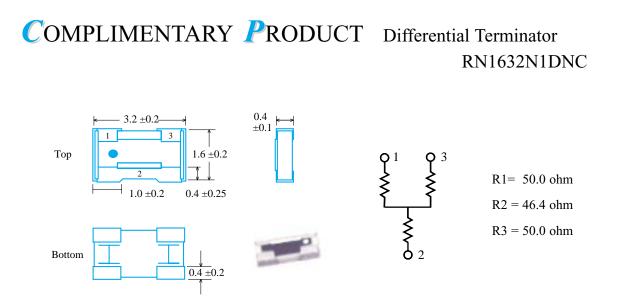

This standard 1206 size chip resistor network is popular for Positive Emitter Coupled Logic (PECL) applications as a terminator. Because this single chip contains three resistors, it reduces pick and place actions from three to one.

<u>Clock Distribution Network Example Using</u> <u>GL2L Delay Line and RN1632 Terminators</u>

### **COMPLIMENTARY PRODUCTS**

#### SLOT sets PSKT\*\*\*N\*

*I* ypical high frequency calibration routines call for a series of nulling procedures that use electrical shorts, opens, loads, and throughs that are connected to the cable ends that feed the test instrument. These will effectively null out undesired matching, loading, frequency response, etc., of the test system to the cable ends. However, the Device Under Test (DUT) requires a socket or fixture to mate with the cable connector. The actual measurement taken includes both the DUT *and* the test fixture.

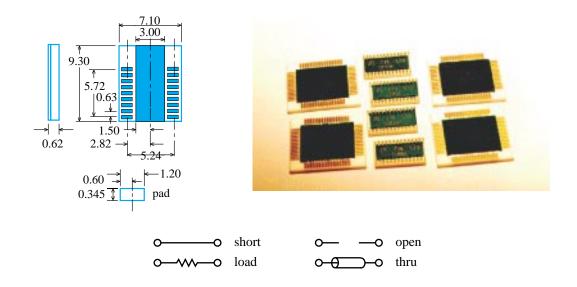

The PSKT\*\*\*N\* series calibration standards are for de-embedding the test fixture effects in these high speed measurements, because the calibration routine is performed at the test fixture. Essentially a custom set of products containing an electrical short, open, load, and through, specifically designed for the targeted schematic, these are used during the calibration routine with a network analyzer or other high speed test equipment. The end result is that the device under test performance is more accurate.

Available in SIP and DIP form factors, these calibration standards have gold finished electrodes and are intended for surface mount applications.

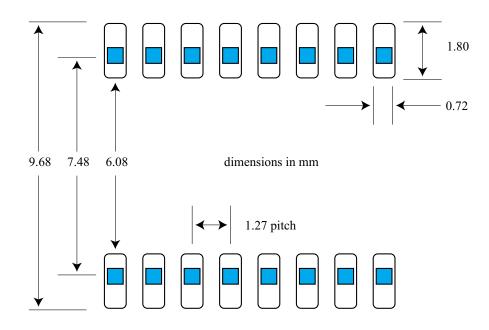

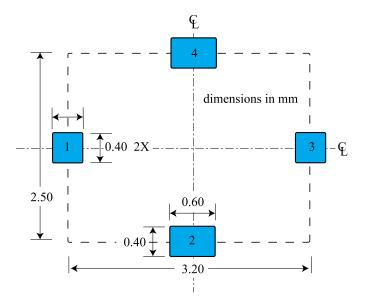

### **F**OOTPRINT **L**AYOUTS

## **GL1L** and **GL2L S**ERIES

**CL1L** SERIES

The above land dimensions are suggested for the surface mount products GL1L/GL2L and CL1L series delay lines. Optimized geometries will vary depending on assembly process parameters. Since each assembly engineer is familiar with character unique to their process, these dimensions are a starting point, not to be recognized as a definitive solution.

Because Timing is Everything.<sup>tm</sup>

# **THIN FILM TECHNOLOGY**

1980 COMMERCE DRIVE NORTH MANKATO, MINNESOTA 56003

> 507 625-8445 507 625-3523 facsimile http://www.thin-film.com