# 8. ELECTRICAL SPECIFICATIONS

This section contains electrical specifications and associated timing information for the TMP68010.

## 8.1 MAXIMUM RATINGS

| Rating                         | Symbol | Value       | Unit |

|--------------------------------|--------|-------------|------|

| Supply Voltage                 | Vcc    | -0.3~+7.0   | ٧    |

| Input Voltage                  | Vin    | -0.3~+7.0   | V    |

| Operating Temperature<br>Range | Та     | 0~+70       | °C   |

| Storage Temperature            | Tstg   | - 55~ + 150 | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages of electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either GND or Vcc).

# 8.2 DC ELECTRICAL CHARACTERISTICS

$(Vcc = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70^{\circ}C)$

| •                                                                                                                                                                                                         | .0. 20/01 | <u> </u>    |                          |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|--------------------------|------|

| Characteristic                                                                                                                                                                                            | Symbol    | Min         | Max                      | Unit |

| Input High Voltage                                                                                                                                                                                        | VIH       | 2.0         | Vcc                      | V    |

| Input Low Voltage                                                                                                                                                                                         | VIL       | GND-0.3     | 0.8                      | V    |

| Input Leakage Current (5.25V)  BERR, BGACK, BR,  DTACK, CLK,  IPLO~IPLZ, VPA  HALT, RESET                                                                                                                 | lìn       | 1           | 2.5                      | μΑ   |

| Three-State (Off State) input Current ( 2.4V/0.4V) — ĀŠ, A1~A23, D0~D15, FC0~FC2, LDS, R/W, UDS, VMA                                                                                                      | ITSI      | -           | 20                       | μΑ   |

| Output High Voltage (IOH = - 400μA) E*  E**, ĀŚ, Α1~Α23, Β̈Ğ,  D0~D15, FC0~FC2, ŪĎŠ,  R/W, ŪĎŠ, VMĀ                                                                                                       | νон       | Vcc-0.75    | -                        | v    |

| Output Low Voltage         (IOL = 1.6mA)       HALT         (IOL = 3.2mA)       A1~A23, 8G, FC0~FC2         (IOL = 5.0mA)       RESET         (IOL = 5.3mA)       E, AS, D0~D15, LDS, RW         UDS, VMA | VOL       | -<br>-<br>- | 0.5<br>0.5<br>0.5<br>0.5 | V    |

| Power Dissipation***                                                                                                                                                                                      | PD        | -           | 1.50                     | w    |

| Capacitance<br>(V <sub>.n</sub> = 0V, T <sub>a</sub> = 25 °C : Frequency = 1MHz)****                                                                                                                      | Cin       |             | 20.0                     | pF   |

| Characteristic         | Symbol     | 81/      | 1Hz        | 101      | /IHz       | 12.5     | MHz        | Unia |  |

|------------------------|------------|----------|------------|----------|------------|----------|------------|------|--|

| Characteristic         | Symbol     | Min      | Max        | Min      | Max        | Min      | Max        | Unit |  |

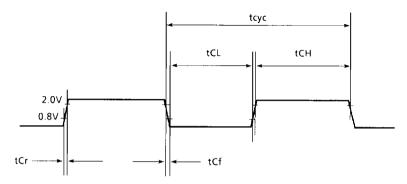

| Frequency of Operation | f          | 4.0      | 8.0        | 4.0      | 10.0       | 4.0      | 12.5       | MHz  |  |

| Cycle Time             | tcyc       | 125      | 250        | 100      | 250        | 80       | 250        | ns   |  |

| Clock Pulse Width      | tCL<br>tCH | 55<br>55 | 125<br>125 | 45<br>45 | 125<br>125 | 35<br>35 | 125<br>125 | ns   |  |

| Rise and Fall Times    | tCr<br>tCf | _        | 10<br>10   | _        | 10<br>10   | _<br>_   | 5          | ns   |  |

# 8.3 AC ELECTRICAL SPECIFICATIONS-CLOCK TIMING (See Figure 8.1)

Figure 8.1 Clock Input Timing Diagram

# 8.4 AC ELECTRICAL SPECIFICATION DEFINITIONS

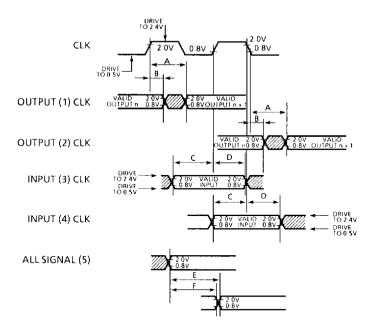

The AC specifications presented consist of output delays, input setup and hold times, and signal skew times. All signals are specified relative to an appropriate edge of the clolk and possibly to one or more other signals.

The measurement of the AC specifications is defined by the waveforms shown in Figure 8.2. In order to test the parameters guaranteed by TOSHIBA, inputs must be driven to the voltage levels specified in this figure. Outputs are specified with minimum and /or maximum limits, as appropriate, and are measured as shown in Figure 8.2. Inputs are specified with minimum setup and hold times, and are measured as shown. Finally, the measurement for signal-to-signal specifications are also shown.

Note: The testing levels used to verify conformance to the AC specifications does not affect the guaranteed DC operation of the device as specified in the DC electrical character-istics.

# Notes:

- 1 This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2 This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3 This input timing is applicable to all parameters specified relative to the rising edge of the

- 4 This input timing is applicable to all parameters specified relative to the falling edge of the

- 5 This timing is applicable to all parameters specified relative to the assertion / negation of another signal.

## Legend:

- A Maximum output delay specification.

- B Minimum output hold time.

- C Minimum input setup time specification.

- D Minimum input hold time specification.

- E Signal valid to signal valid specification (maximum or minimum).

- F Signal valid to signal invalid specification (maximum to minimum).

Figure 8.2 Drive Levels and Test Points for AC Specifications

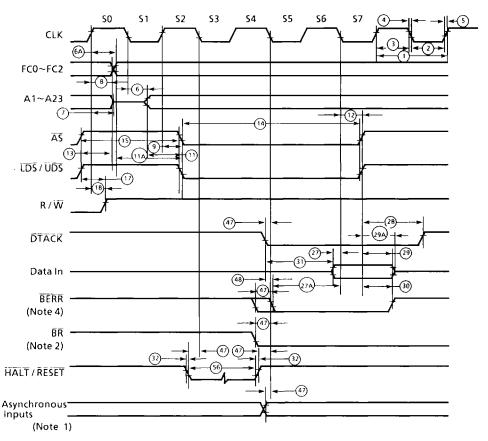

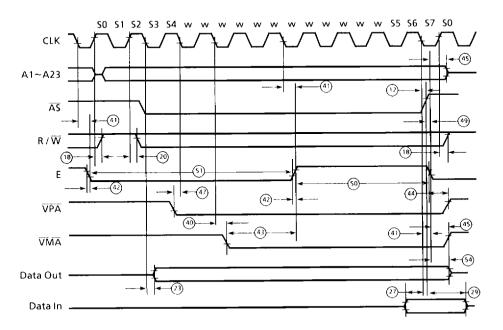

# 8.5 AC ELECTRICAL SPECIFICATIONS-READ AND WRITE CYCLES (1/4)

$(Vcc = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70^{\circ}C; see Figures 8.3 and 8.4)$

| (VCC = 5.0V ± 5 %, GND = 0V, 1a = 0 |                                                                                                          |                            |     | ,,,, | u u, |     |      |     |        |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|-----|------|------|-----|------|-----|--------|

| Num.                                | Characteristic                                                                                           | Symbol                     | N8  | lHz  | 101  | ЛHz | 12.5 | MHz | Unit   |

| 740111.                             | enaracteristic                                                                                           | 3,111001                   | Min | Max  | Min  | Max | Min  | Max | Office |

| 1                                   | Clock Period                                                                                             | †cyc                       | 125 | 250  | 100  | 250 | 80   | 250 | ns     |

| 2                                   | Clock Width Low                                                                                          | <sup>t</sup> CL            | 55  | 125  | 45   | 125 | 35   | 125 | ns     |

| 3                                   | Clock Width High                                                                                         | ·СН                        | 55  | 125  | 45   | 125 | 35   | 125 | ns     |

| 4                                   | Clock Fall Time                                                                                          | ¹Cf                        | -   | 10   | _    | 10  | -    | 5   | ns     |

| 5                                   | Clock Rise Time                                                                                          | ¹Cr                        | _   | 10   | -    | 10  |      | 5   | ns     |

| 6                                   | Clock Low to Address Valid                                                                               | tCLAV                      | _   | 62   | _    | 50  | _    | 50  | ns     |

| 6A                                  | Clock High to FC Valid                                                                                   | tCHFCV                     | _   | 62   |      | 50  | -    | 45  | ns     |

| 7                                   | Clock High to Address, Data Bus<br>High Impedance (Maximum)                                              | tCHADZ                     |     | 80   | _    | 70  | -    | 60  | ns     |

| 8                                   | Clock High to Address, FC Invalid (Minimum)                                                              | ¹CHAFI                     | 0   | -    | 0    | -   | 0    | _   | ns     |

| 91                                  | Clock High to AS, DS Low                                                                                 | <sup>t</sup> CH <b>S</b> L | 3   | 60   | 3    | 50  | 3    | 40  | ns     |

| 112                                 | Address Valid to AS, DS Low (Read)<br>/ AS Low (Write)                                                   | ¹AV\$L                     | 30  | ~    | 20   | -   | 15   | _   | ns     |

| 11A <sup>2</sup>                    | FC Valid to $\overrightarrow{AS}$ , $\overrightarrow{DS}$ Low (Read) / $\overrightarrow{AS}$ Low (Write) | ¹FCVSL                     | 90  | ~    | 70   | _   | 60   | -   | ns     |

| 121                                 | Clock Low to AS, DS High                                                                                 | tCLSH                      |     | 62   | _    | 50  | _    | 40  | ns     |

| 132                                 | AS, DS HIGH to Address / FC Invalid                                                                      | <sup>t</sup> SHAFI         | 40  | -    | 30   | _   | 20   |     | ns     |

| 142                                 | AS, DS Width Low (Read) / AS Low<br>(Write)                                                              | †SL                        | 270 | -    | 195  |     | 160  | _   | ns     |

| 14A2                                | DS Width Low (Write)                                                                                     | †D <b>S</b> L              | 140 | -    | 95   | _   | 80   | -   | ns     |

| 152                                 | ÀŚ, ŌS Width High                                                                                        | t <b>S</b> H               | 150 | -    | 105  | _   | 65   | -   | ns     |

| 16                                  | Clock High to Control Bus High<br>Impedance                                                              | ¹CHCZ                      | -   | 80   | _    | 70  | -    | 60  | ns     |

| 172                                 | AS, DS High to R / W High (Read)                                                                         | tSHRH                      | 40  | _    | 30   | _   | 20   | -   | ns     |

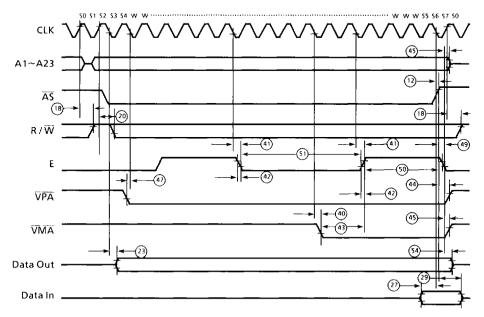

# 8.5 AC ELECTRICAL SPECIFICATIONS - READ AND WRITE CYCLES (2/4)

$(Vcc = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70\%$ ; see Figures 8.3 and 8.4)

| $(VCC = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70C$ ; see Figures |                                                       |               |     |     |     |     |      | 0.3 a11 | u 0.4)      |

|----------------------------------------------------------------|-------------------------------------------------------|---------------|-----|-----|-----|-----|------|---------|-------------|

| Num.                                                           | Characteristic                                        | Symbol        | 8M  | lHz | 101 | ЛНZ | 12.5 | MHz     | Unit        |

|                                                                |                                                       | 3711001       | Min | Max | Min | Max | Min  | Max     | Offic       |

| 181                                                            | Clock High to R / W High                              | †CHRH         | 0   | 55  | 0   | 45  | 0    | 40      | ns          |

| 201                                                            | Clock High to R / W Low                               | †CHRL         | 0   | 55  | 0   | 45  | 0    | 40      | ns          |

| 20A2.6                                                         | ÄŠ Low to R / W Valid (Write)                         | tASRV         | _   | 10  | _   | 10  | -    | 10      | ns          |

| 212                                                            | Address Valid to R / W Low (Write)                    | ¹AVRL         | 20  | _   | 0   | -   | 0    | -       | ns          |

| 21A <sup>2</sup>                                               | FC Valid to R/W Low (Write)                           | tFCVRL        | 60  | -   | 50  | _   | 30   | -       | ns          |

| 222                                                            | R/W Low to DS Low (Write)                             | †RLSL         | 80  | _   | 50  | _   | 30   | _       | ns          |

| 23                                                             | Clock Low to Data Out Valid<br>(Write)                | tCLDO         | -   | 62  | -   | 50  | _    | 50      | ns          |

| <b>25</b> <sup>2</sup>                                         | AS, DS High to Data Out Invalid<br>(Write)            | tSHDOI        | 40  | _   | 30  | -   | 20   | _       | ns          |

| 262                                                            | Data Out Valid to DS Low (Write)                      | †DOSL         | 40  | _   | 30  | _   | 20   | -       | ns          |

| 275                                                            | Data in to Clock Low (Setup Time on Read)             | †DICL         | 10  | _   | 10  | _   | 10   | -       | ns          |

| 27A <sup>5</sup>                                               | Late BERR Low to Clock Low<br>(Setup Time)            | ¹BELCL        | 45  | -   | 45  | _   | 45   | _       | ns          |

| 282                                                            | AS, DS High to DTACK High                             | tSHDAH        | 0   | 240 | 0   | 190 | 0    | 150     | ns          |

| 29                                                             | AS, DS High to Data In Invalid<br>(Hold Time on Read) | tSHDII        | 0   | _   | 0   | -   | 0    | _       | ns          |

| 29A                                                            | AS, DS Negated to Data In High<br>Impedance           | tSHDZ         |     | 187 | _   | 150 | _    | 120     | ns          |

| 30                                                             | ĀŠ, DS High to BERR High                              | <b>ISHBEH</b> | 0   | _   | 0   | _   | 0    | -       | ns          |

| 312.5                                                          | DTACK Low to Data in (Setup<br>Time)                  | †DALDI        | -   | 90  | ı   | 65  |      | 50      | ns          |

| 32                                                             | HALT and RESET Input Transition<br>Time               | ¹RHr, f       | 0   | 200 | 0   | 200 | 0    | 200     | ns          |

| 33                                                             | Clock High to BG Low                                  | tCHGL         | _   | 62  | _   | 50  | _    | 40      | ns          |

| 34                                                             | Clock High to BG High                                 | †CHGH         | _   | 62  | _   | 50  |      | 40      | ns          |

| 35                                                             | BR Low to BG Low                                      | †BRLGL        | 1.5 | 3.5 | 1.5 | 3.5 | 1.5  | 3 5     | Clk.<br>Per |

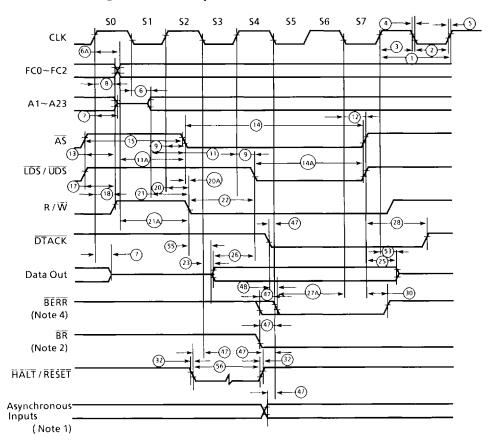

# 8.5 AC ELECTRICAL SPECIFICATIONS-READ AND WRITE CYCLES (3/4)

$(Vcc = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70^{\circ}C; see Figures 8.3 and 8.4)$

|                 | (VCC = 3,0V I                                                    |                     |      | lHz           |      | 1Hz           | 12.5MHz |               | 5. 17       |

|-----------------|------------------------------------------------------------------|---------------------|------|---------------|------|---------------|---------|---------------|-------------|

| Num.            | Characteristic                                                   | Symbol              | Min  | Max           | Min  | Max           | Min     | Max           | Unit        |

| 36 <sup>7</sup> | BR High to BG High                                               | ¹BŖHGH              | 1.5  | 3.5           | 1.5  | 3.5           | 1.5     | 3.5           | Clk.<br>Per |

| 37              | BGACK Low to BG High                                             | <sup>t</sup> GALGH  | 1.5  | 3.5           | 1.5  | 3.5           | 1.5     | 3 5           | Clk.<br>Per |

| 37A8            | BGĀČŔ Low to BŘ High                                             | <sup>1</sup> GALBRH | 20   | 1.5<br>Clocks | 20   | 1.5<br>Clocks | 20      | 1.5<br>Clocks | ns          |

| 38              | BG Low to Control, Address, Data<br>Bus High Impedance (AS High) | †GLZ                | -    | 80            |      | 70            | -       | 60            | ns          |

| 39              | 8G Width High                                                    | ţGН                 | 1.5  | _             | 1.5  | -             | 1.5     |               | Clk.<br>Per |

| 40              | Clock Low to VMA Low                                             | tCLVML              |      | 70            | -    | 70            | -       | 70            | ns          |

| 41              | Clock Low to E Transition                                        | tCLET               | -    | 55            | -    | 45            | -       | 35            | ns          |

| 42              | E Output Rise and Fall Time                                      | tEr, f              | _    | 15            | _    | 15            |         | 15            | ns          |

| 43              | VMA Low to E High                                                | *VMLEH              | 200  | _             | 150  | _             | 90      | -             | ns          |

| 44              | ÄŠ, ĎŠ High to VPA High                                          | *SHVPH              | 0    | 120           | 0    | 90            | 0       | 70            | ns          |

| 45              | E Low to Control Address Bus<br>Invalid (Address Hold Time)      | ¹ELCAI              | 30   | -             | 10   |               | 10      | -             | ns          |

| 46              | BGACK Width                                                      | ¹GAL                | 1.5  | -             | 1.5  | _             | 1.5     | -             | Clk.<br>Per |

| 475             | Asynchronous Input Setup Time                                    | tA\$I               | 10   | -             | 10   | _             | 10      | -             | ns          |

| 482,3.5         | DTACK Low to BERR Low                                            | †DALBEL             | -    | 80            | _    | 55            | _       | 35            | ns          |

| 499             | AS, DS High to E Low                                             | tSHEL               | - 70 | 70            | - 55 | 55            | - 45    | 45            | ns          |

| 50              | E Width High                                                     | ₹EH                 | 450  | -             | 350  | -             | 280     | _             | ns          |

| 51              | E Width Low                                                      | tEL                 | 700  | -             | 550  |               | 440     | _             | ns          |

| 53              | Clock High to Data Out Invalid                                   | †CHDOI              | 0    | _             | 0    | -             | 0       | _             | ns          |

| 54              | E Low to Data Out Invalid                                        | tELDOI              | 30   | _             | 20   |               | 15      | _             | ns          |

| 55              | R / W to Data Bus Driven                                         | †RLDBD              | 30   | -             | 20   | -             | 10      | -             | ns          |

| 564             | HALT / RESET Pulse Width                                         | 1HRPW               | 10   | _             | 10   | _             | 10      |               | Clk.<br>Per |

# 8.5 AC ELECTRICAL SPECIFICATIONS-READ AND WRITE CYCLES (4/4)

$(Vcc = 5.0V \pm 5\%, GND = 0V, Ta = 0 \sim 70^{\circ}C; see Figures 8.3 and 8.4)$

|                  | <b>6</b> 1                         | <b>5</b> | 8MHz |     | 10MHz |     | 12.5MHz |     | Unit        |

|------------------|------------------------------------|----------|------|-----|-------|-----|---------|-----|-------------|

| Num.             | Characteristic                     | Symbol   | Min  | Max | Min   | Max | Min     | Max | Unit        |

| 57               | BGACK High to Control Bus Driven   | tGABD    | 1.5  | -   | 1.5   | -   | 1.5     | 1   | Clk.<br>Per |

| 57A              | BGACK Negated to FC, VMA<br>Driven | tGAFD    | 1    |     | 1     | -   | 1       | 1   | Clks        |

| 587              | BG High to Control Bus Driven      | ¹GHBD    | 1.5  | _   | 1.5   | -   | 1.5     | _   | Clk.<br>Per |

| 58A <sup>7</sup> | BR Negated to FC, VMA Driven       | ¹RHFD    | 1    | -   | 1     | -   | 1       | -   | Cłks        |

- 1. For a loading capacitance of less than or equal to 50 picofarads, subtract 5 nanoseconds from the values given in these columns.

- 2. Actual value depends on clock period.

- 3. In the absence of DTACK, BERR is an asynchronous input using the asynchronous input setup time (#47)

- For power up, the MPU must be held in RESET state for 100 ms to allow stabilization of on-chip circuitry. After the system is powered up, #56 refers to the minimum pulse width required to reset the system.

- 5. If the asynchronous setup time (#47) requirements are satisfied, the DTACK-low to data setup time (#31) and DTACK-low to BERR-low setup time (#48) requirements can be ignored. The data must only satisfy the data-in to clock-low setup time (#27) for the following clock cycle, BERR must only satisfy the late-BERR-low to clock-low setup time (#27A) for the following clock cycle.

- When AS and R/W are equally loaded (±20%), subtract 10 nanoseconds from the values in these columns.

- The processor will negate BG and begin driving the bus again if external arbitration logic negates BR before asserting BGACK.

- 8. The minimum value must be met to guarantee proper operation. If the maximum value is exceeded,  $\overline{BG}$  may be reasserted.

- 9. The falling edge of S6 triggers both the negation of the strobes (AS and DS) and the falling edge of E. Either of these events can occur first, depending upon the loading on each signal. Specification #49 indicates the absolute maximum skew that will occur between the rising edge of the strobes and the falling edge of the E clock.

- Setup time for the asynchronous inputs IPLô/Z, IPL1, and VPA guarantees their recognition at the next falling edge of the clock.

- BR need fall at this time only in order to insure being recognized at the end of this bus

cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

- The timing for the first falling edge (47) of BERR are for BERR without DTACK, the timings for the second falling edge (27Λ and 48) are for BERR with DTACK.

Figure 8.3 Read Cycle Timing Diagram

- Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

- Because of loading variations, R / W may valid after AS even though both are initiated by the rising edge of S2 (Specification 20A).

- 3. The timing for the first falling edge (47) of  $\overrightarrow{BERR}$  are for  $\overrightarrow{BERR}$  without  $\overrightarrow{DTACK}$ ; the timings for the second falling edge (27A and 48) are for  $\overrightarrow{BERR}$  with  $\overrightarrow{DTACK}$ .

Figure 8.4 Write Cycle Timing Diagram

# 8.6 AC ELECTRICAL SPECIFICATIONS-TMP68010 TO 6800 PERIPHERAL

(Vcc =  $5.0V \pm 5\%$ , GND = 0V,  $T_a = 0 \sim 70^{\circ}C$ ; see Figures 8.5 and 8.6)

|      |                                                          |                   | 81/  | Hz  | 10MHz |     | 12.5MHz |     |                                              |

|------|----------------------------------------------------------|-------------------|------|-----|-------|-----|---------|-----|----------------------------------------------|

| Num. | Characteristic                                           | Symbol            | Min  | Max | Min   | Max | Min     | Max | Unit  ns |

| 121  | Clock Low to AS, DS High                                 | <sup>†</sup> CLSH |      | 62  | _     | 50  | -       | 40  | ns                                           |

| 181  | Clock High to R / W High (Read)                          | <sup>t</sup> CHRH | 0    | 55  | 0     | 45  | 0       | 40  | ns                                           |

| 201  | Clack High to R/W Low                                    | ¹CHRL             | 0    | 55  | 0     | 45  | 0       | 40  | ns                                           |

| 23   | Clock Low to Data Out Valid<br>(Write)                   | 'CLDO             |      | 62  |       | 50  | -       | 50  | ns                                           |

| 27   | Data in to Clock Low (Setup Time on Read)                | †DICL             | 10   |     | 10    |     | 10      |     | ns                                           |

| 29   | AŠ, DŠ Negated to Data-In Invalid<br>(Hold Time on Read) | tSHDII            | 0    | _   | 0     | _   | 0       | _   | ns                                           |

| 40   | Clock Low to VMA Low                                     | ¹CLVML            | _    | 70  | -     | 70  | -       | 70  | ns                                           |

| 41   | Clock Low to E Transition                                | †CLET             | -    | 55  | _     | 45  | -       | 35  | ns                                           |

| 42   | E Output Rise and Fall Time                              | tEr, f            | _    | 15  | _     | 15  | -       | 15  | ns                                           |

| 43   | VMA Low to E High                                        | tVMLEH            | 200  | -   | 150   | -   | 90      | -   | ns                                           |

| 44   | AŚ, DŚ High to VPA High                                  | tSHVPH            | 0    | 120 | 0     | 90  | 0       | 70  | ns                                           |

| 45   | E Low to Control Address Bus<br>(Address Hold Time)      | 1ELCA1            | 30   | _   | 10    |     | 10      | -   | ns                                           |

| 47   | Asynchronous Input Setup Time                            | tASI              | 10   | _   | 10    | _   | 10      | -   | ns                                           |

| 492  | AS, DS High to E Low                                     | 1SHEL             | - 70 | 70  | - 55  | 55  | - 45    | 45  | ns                                           |

| 50   | E Width High                                             | чЕН               | 450  | -   | 350   | _   | 280     |     | ns                                           |

| 51   | E Width Low                                              | tEL               | 700  | -   | 550   | _   | 440     | -   | ns                                           |

| 54   | E Low to Data Out Invalid                                | 1ELDOI            | 30   | _   | 20    | _   | 15      | _   | ns                                           |

- 1. For a loading capacitance of less than or equal to 50 picofarads, subtract 5 nanoseconds from the values given in these columns.

- 2. The falling edge of S6 triggers both the negation of the strobes (ĀS and DS) and the falling edge of E. Either of these events can occur first, depending upon the loading on each signal. Specification #49 indicates the absolute maximum skew that will occur between the rising edge of the strobes and the falling edge of the E clock.

Note: The timing diagram is included for those who wish to design their own circuit to generate  $\overline{VMA}$  it shows the best case possibly attainable

Figure 8.5 TMP68010 to 6800 Peripheral Timing Diagram - Best Case

Note: This timing diagram is included for those who wish to design their own circuit to generate  $\overline{VMA}$ . It shows the worst case possibly attainable.

Figure 8.6 TMP68010 to 6800 Peripheral Timing Diagram - Worst Case

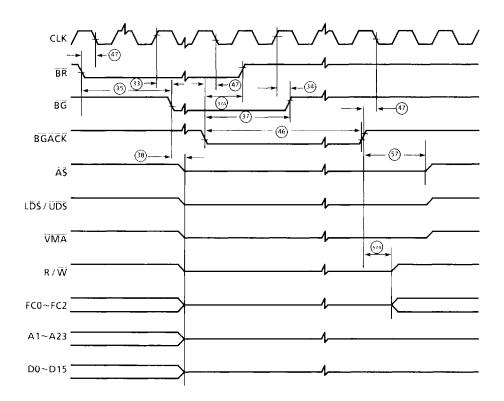

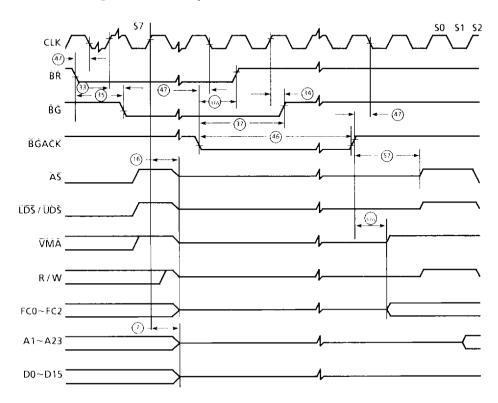

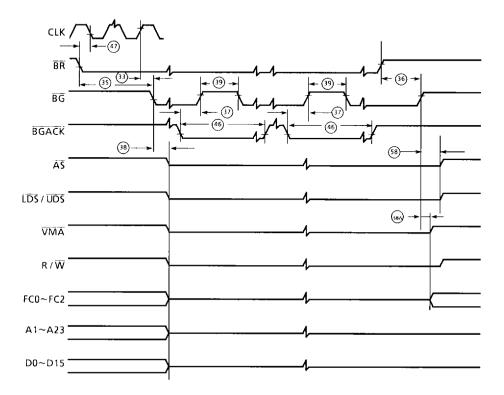

# AC ELECTRICAL SPECIFICATIONS-BUS ARBITRATION

$(Vcc = 5.0V \pm 5\% : GND = 0V : T_2 = 0 \sim 70^{\circ}C : See Figures 8.7, 8.8 and 8.9)$

|                  | (Vcc = 5.0V ± 5% ; C                                             | טט = טאנ | ; I <sub>a</sub> = | 0~70          | c ; see | Figure        | es 8.7, | 8.8 an        | u 8.9)      |

|------------------|------------------------------------------------------------------|----------|--------------------|---------------|---------|---------------|---------|---------------|-------------|

| Num.             | Characteristic                                                   | Symbol   | <b>№</b>           | lHz           | 10N     | ИНZ           | 12.5    | MHz           | Unit        |

| NUIII.           | Characteristic                                                   | Symbol   | Min                | Max           | Min     | Max           | Min     | Max           | Offic       |

| 7                | Clock High to Address, Data Bus<br>High Impedance (Maximum)      | tCHADZ   | _                  | 80            | -       | 70            | _       | 60            | ns          |

| 16               | Clock High to Control Bus High<br>Impedance                      | tCHCZ    | _                  | 80            | _       | 70            | _       | 60            | ns          |

| 33               | Clock High to BG Low                                             | †CHGL    | -                  | 62            | _       | 50            | -       | 40            | ns          |

| 34               | Clock High to BG High                                            | tСНGН    | -                  | 62            | _       | 50            | -       | 40            | ns          |

| 35               | BR Low to BG Low                                                 | ¹BRLGL   | 1.5                | 3.5           | 1.5     | 3.5           | 1.5     | 3.5           | Clk.<br>Per |

| 361              | BR High to BG High                                               | †BRHGH   | 1.5                | 3.5           | 1.5     | 3.5           | 1.5     | 3.5           | Clk.<br>Per |

| 37               | BGACK Low to BG High                                             | tGALGH   | 1.5                | 3.5           | 1.5     | 3.5           | 1.5     | 3.5           | Clk.<br>Per |

| 37A <sup>2</sup> | BGACK Low to BR High                                             | †GALBRH  | 20                 | 1.5<br>Clocks | 20      | 1.5<br>Clocks | 20      | 1.5<br>Clocks | ns          |

| 38               | BG Low to Control, Address, Data<br>Bus High Impedance (AS High) | tGLZ     | _                  | 80            | -       | 70            | -       | 60            | ns          |

| 39               | BĞ Width High                                                    | tGН      | 1.5                | _             | 1.5     | _             | 1.5     | _             | Clk.<br>Per |

| 46               | BGACK Width                                                      | †GAL     | 1.5                | _             | 1.5     | _             | 1.5     | _             | Cik.<br>Per |

| 47               | Asynchronous Input Setup Time                                    | †ASI     | 10                 | _             | 10      | _             | 10      | _             | ns          |

| 572              | BGACK High to Control Bus Driven                                 | tGABD    | 1.5                | -             | 1.5     | _             | 1.5     | _             | Clk.<br>Per |

| 57A              | BGACK Negated to FC, VMA<br>Driven                               | tGAFD    | 1                  | -             | 1       | -             | 1       | _             | Clk.<br>Per |

| 581              | BG High to Control Bus Driven                                    | †GHBD    | 1.5                | -             | 1.5     |               | 1.5     | _             | Clk.<br>Per |

| 58A1             | 8R Negated to FC, VMA Driven                                     | tRHFD    | 1                  | _             | 1       | _             | 1       | _             | Clk.<br>Per |

Notes:

The processor will negate BG and begin driving the bus again if external arbitration logic negates BR before asserting BGACK.

The minimum value must be met to guarantee proper operation. If the maximum value is

Figure~8.7~~Bus~Arbitration~Timing-Idle~Bus~Case

Figure 8.8 Bus Arbitration Timing - Active Bus Case

Figure 8.9 Bus Arbitration Timing - Multiple Bus Requests