# LatticeECP/EC Family Handbook

HB1000 Version 03.3, March 2010

# LatticeECP/EC Family Handbook Table of Contents

March 2010

| Section I. LatticeECP/EC Family Data Sheet   |      |

|----------------------------------------------|------|

| Introduction                                 |      |

| Features                                     |      |

| Introduction                                 |      |

| Architecture                                 |      |

| Architecture Overview                        |      |

| PFU and PFF Blocks                           | 2-3  |

| Slice                                        |      |

| Routing                                      | 2-7  |

| Clock Distribution Network                   | 2-7  |

| Primary Clock Sources                        | 2-7  |

| Secondary Clock Sources                      | 2-8  |

| Clock Routing                                |      |

| sysCLOCK Phase Locked Loops (PLLs)           | 2-9  |

| Dynamic Clock Select (DCS)                   | 2-11 |

| sysMEM Memory                                | 2-12 |

| sysMEM Memory Block                          |      |

| Bus Size Matching                            |      |

| RAM Initialization and ROM Operation         |      |

| Memory Cascading                             |      |

| Single, Dual and Pseudo-Dual Port Modes      |      |

| Memory Core Reset                            |      |

| EBR Asynchronous Reset                       |      |

| sysDSP Block                                 |      |

| sysDSP Block Approach Compare to General DSP |      |

| sysDSP Block Capabilities                    |      |

| MULT sysDSP Element                          |      |

| MAC sysDSP Element                           |      |

| MULTADD sysDSP Element                       |      |

| MULTADDSUM sysDSP Element                    |      |

| Clock, Clock Enable and Reset Resources      |      |

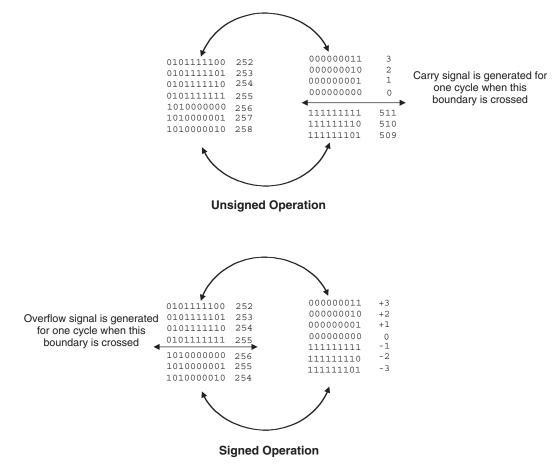

| Signed and Unsigned with Different Widths    |      |

| OVERFLOW Flag from MAC                       |      |

| IPexpress™                                   |      |

| Optimized DSP Functions                      |      |

| Resources Available in the LatticeECP Family |      |

| DSP Performance of the LatticeECP Family     |      |

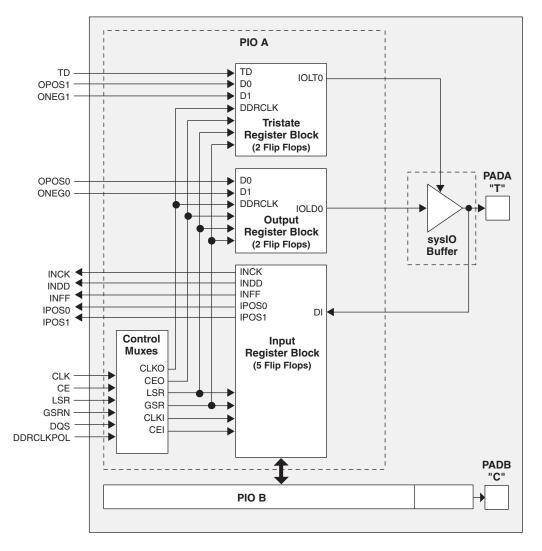

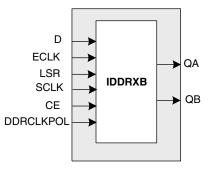

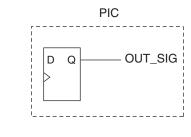

| Programmable I/O Cells (PIC)                 |      |

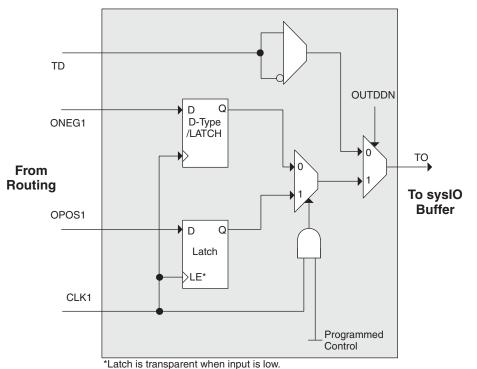

| PIO                                          |      |

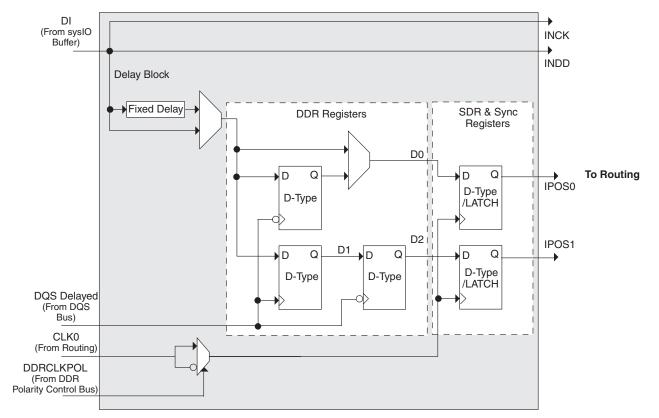

| DDR Memory Support                           |      |

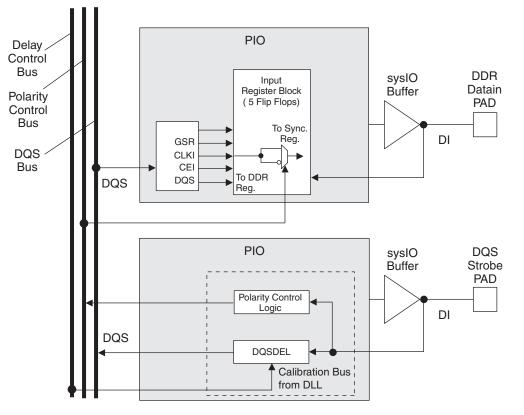

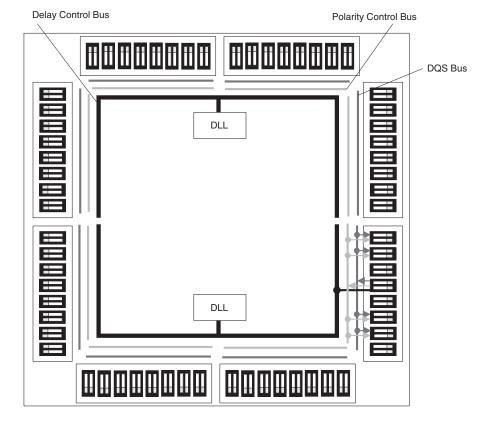

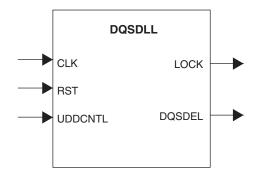

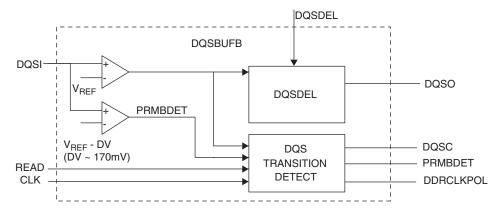

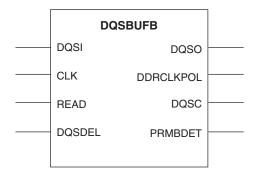

| DLL Calibrated DQS Delay Block               |      |

| Polarity Control Logic                       |      |

| sysIO Buffer                                 |      |

| sysiO Buffer Banks                           |      |

| Typical I/O Behavior During Power-up         |      |

| Supported Standards                          |      |

| Hot Socketing                                |      |

| Configuration and Testing                    |      |

|                                              |      |

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| IEEE 1149.1-Compliant Boundary Scan Testability                                                               | 2-31 |

|---------------------------------------------------------------------------------------------------------------|------|

| Device Configuration                                                                                          | 2-32 |

| Internal Logic Analyzer Capability (ispTRACY)                                                                 | 2-32 |

| External Resistor                                                                                             |      |

| Oscillator                                                                                                    | 2-33 |

| Density Shifting                                                                                              |      |

| DC and Switching Characteristics                                                                              |      |

| Absolute Maximum Ratings                                                                                      |      |

| Recommended Operating Conditions                                                                              |      |

| Hot Socketing Specifications                                                                                  |      |

| DC Electrical Characteristics                                                                                 |      |

| Supply Current (Standby)                                                                                      |      |

| Initialization Supply Current                                                                                 |      |

| sysIO Recommended Operating Conditions                                                                        |      |

| sysIO Single-Ended DC Electrical Characteristics                                                              |      |

| sysIO Differential Electrical Characteristics                                                                 |      |

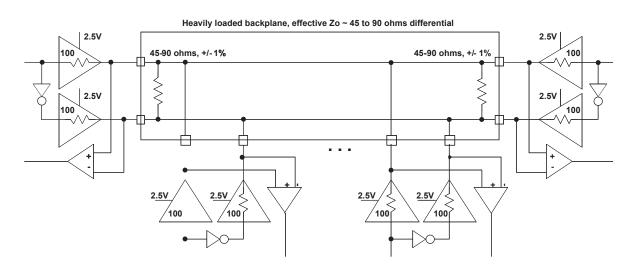

| LVDS                                                                                                          |      |

| Differential HSTL and SSTL                                                                                    |      |

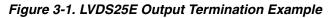

| LVDS25E                                                                                                       |      |

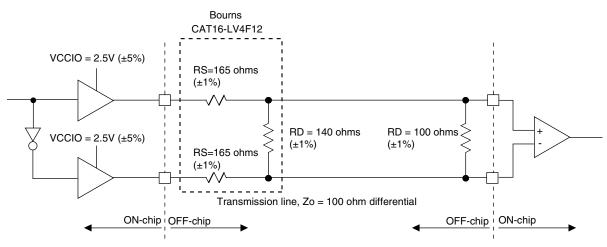

| BLVDS                                                                                                         |      |

| LVPECL                                                                                                        | 3-10 |

| RSDS                                                                                                          | 3-11 |

| Typical Building Block Function Performance                                                                   | 3-12 |

| Pin-to-Pin Performance (LVCMOS25 12mA Drive)                                                                  | 3-12 |

| Register-to-Register Performance1                                                                             | 3-12 |

| Derating Timing Tables                                                                                        |      |

| LatticeECP/EC External Switching Characteristics                                                              |      |

| LatticeECP/EC Internal Switching Characteristics                                                              |      |

| Timing Diagrams                                                                                               |      |

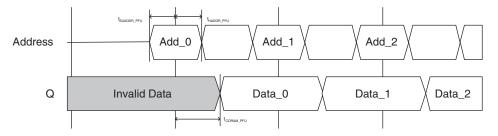

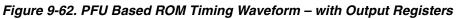

| PFU Timing Diagrams                                                                                           |      |

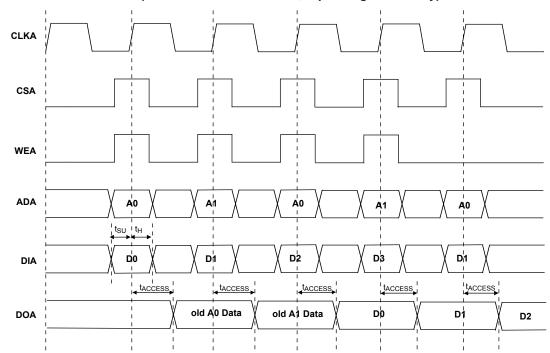

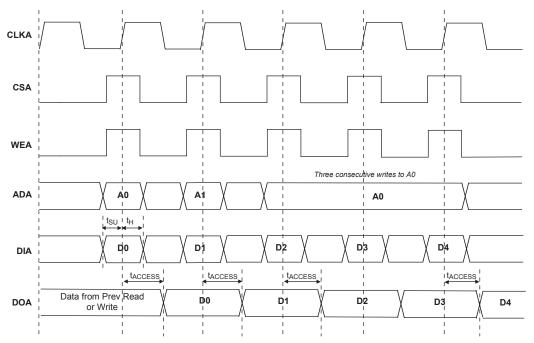

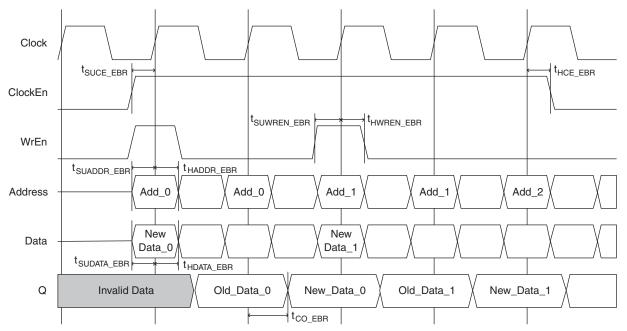

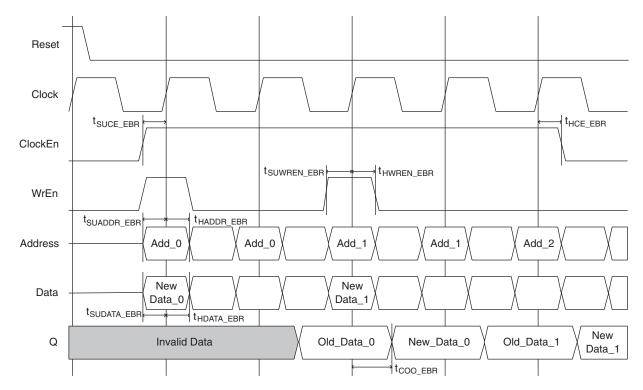

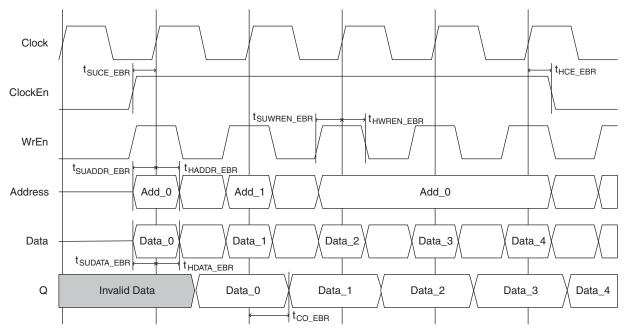

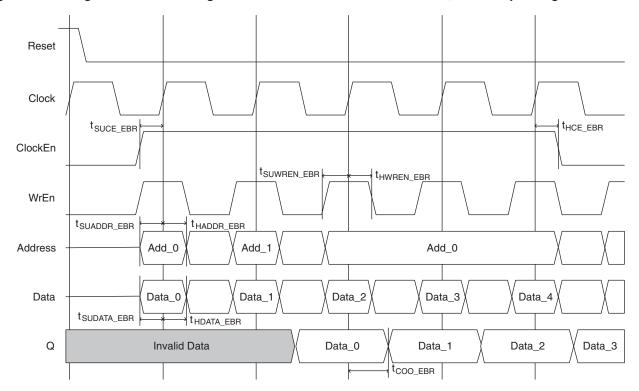

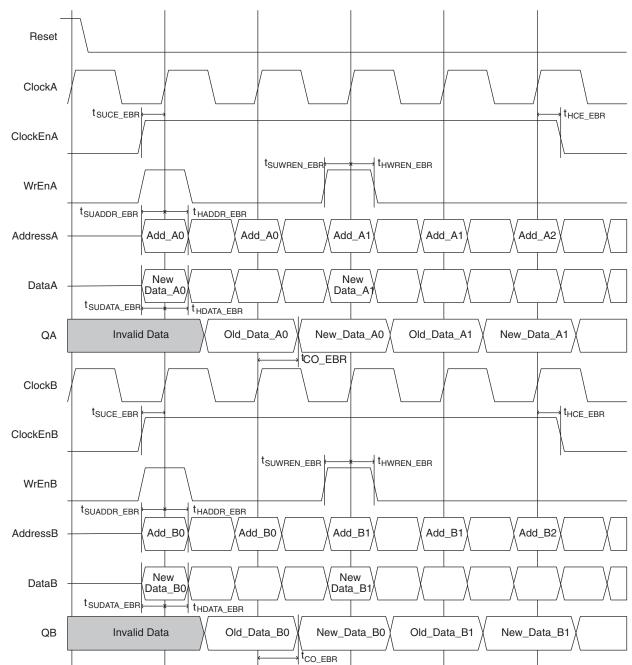

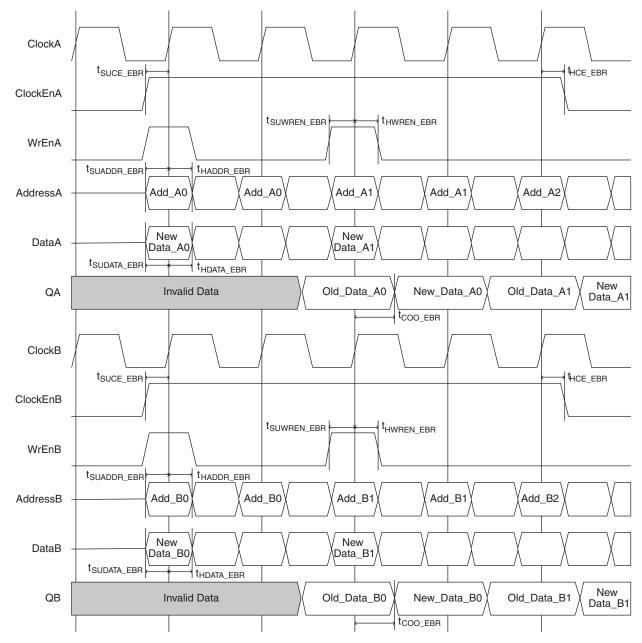

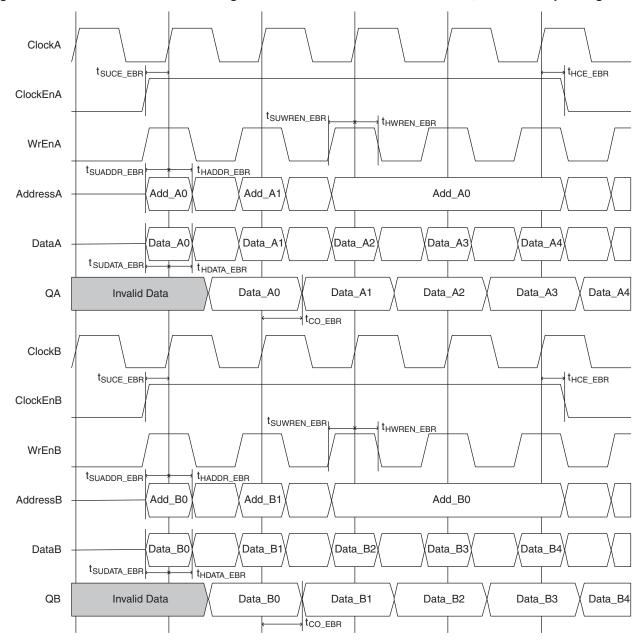

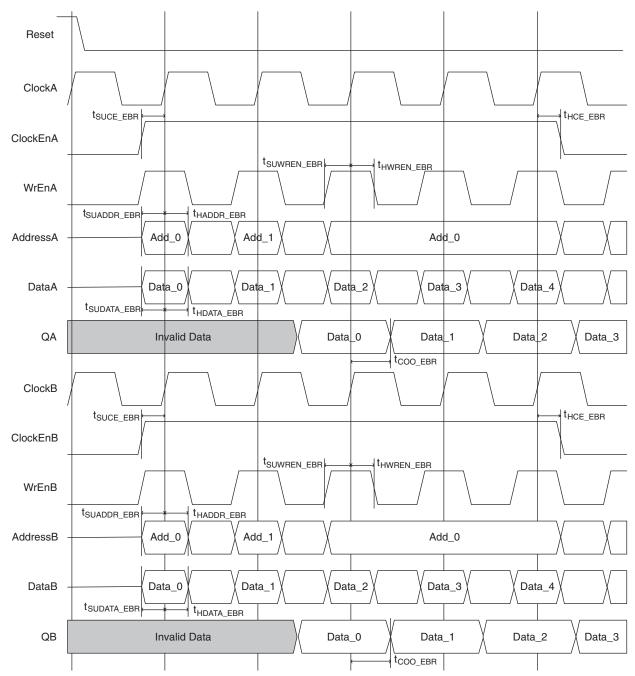

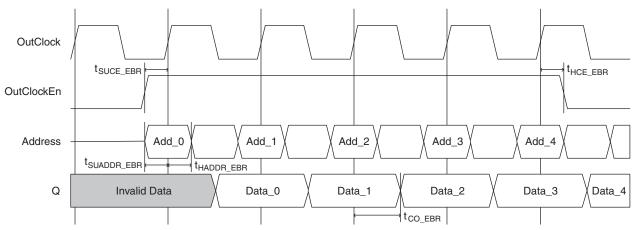

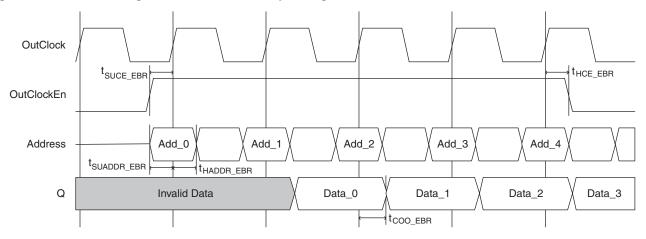

| EBR Memory Timing Diagrams                                                                                    |      |

| LatticeECP/EC Family Timing Adders                                                                            |      |

| sysCLOCK PLL Timing                                                                                           |      |

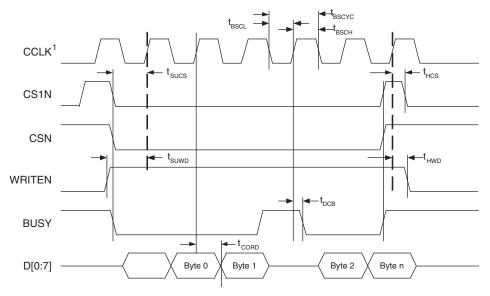

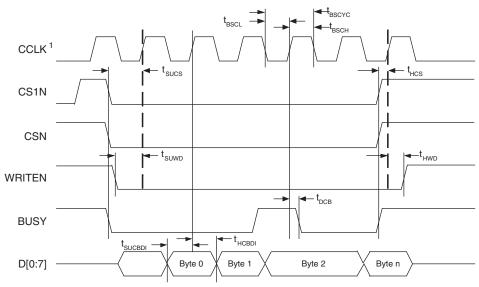

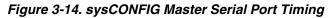

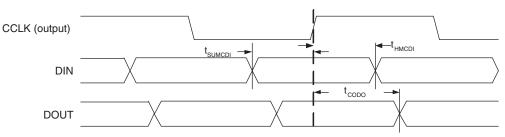

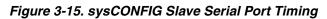

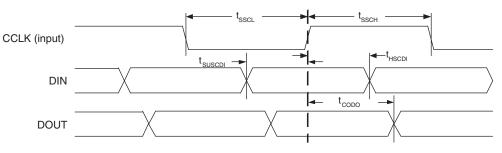

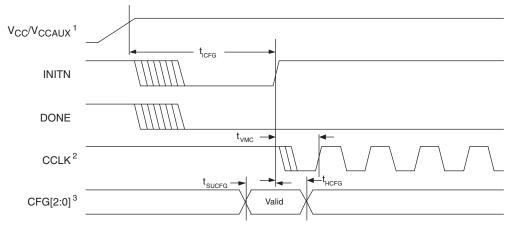

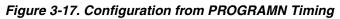

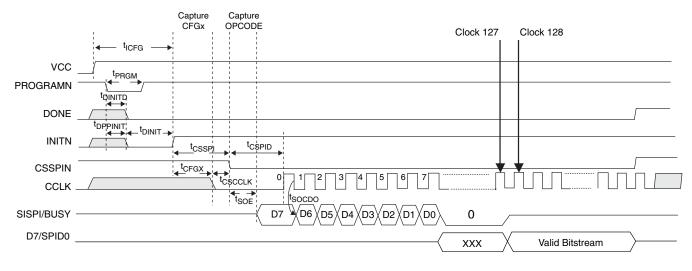

| LatticeECP/EC sysCONFIG Port Timing Specifications                                                            |      |

| Master Clock                                                                                                  |      |

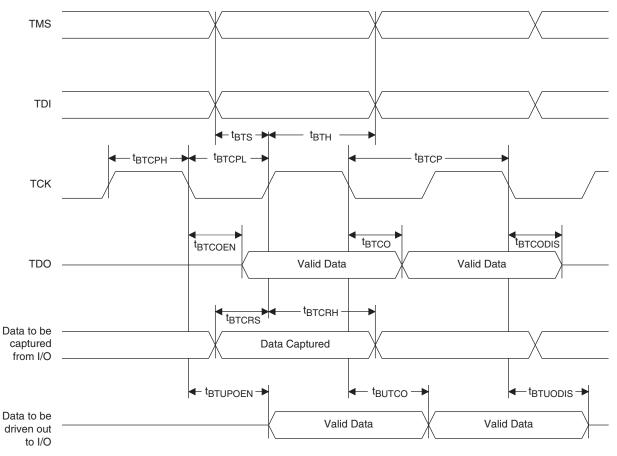

| JTAG Port Timing Specifications                                                                               |      |

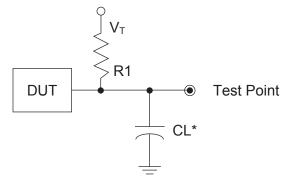

| Switching Test Conditions                                                                                     |      |

| Pinout Information                                                                                            |      |

| Signal Descriptions                                                                                           |      |

| PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin                                          |      |

| Pin Information Summary                                                                                       |      |

| Pin Information Summary (Cont.)                                                                               |      |

| Power Supply and NC Connections                                                                               |      |

| Power Supply and NC Connections (Cont.)                                                                       |      |

| LFEC1, LFEC3 Logic Signal Connections: 100 TQFP                                                               |      |

| LFEC1, LFEC3, LFECP/EC6 Logic Signal Connections: 144 TQFP<br>LFEC1, LFEC3 Logic Signal Connections: 208 PQFP | 4-۱۱ |

| LFEC7, LFEC3 Logic Signal Connections: 208 PQFP<br>LFECP/EC6, LFECP/EC10 Logic Signal Connections: 208 PQFP   |      |

| LFEC9/EC6, LFECP/EC6 Logic Signal Connections: 208 PQFP                                                       |      |

| LFECP/EC10 and LFECP/EC15 Logic Signal Connections: 256 fpBGA                                                 |      |

| LFECP/EC6, LFECP/EC10, LFECP/EC15 Logic Signal Connections: 484 fpBGA                                         |      |

| LFECP/EC0 and LFECP/EC33 Logic Signal Connections: 484 fpBGA                                                  |      |

| LFECP/EC20, LFECP/EC33 Logic Signal Connections: 672 fpBGA                                                    |      |

| Thermal Management                                                                                            |      |

| ······································                                                                        |      |

| For Further Information                                                    |     |

|----------------------------------------------------------------------------|-----|

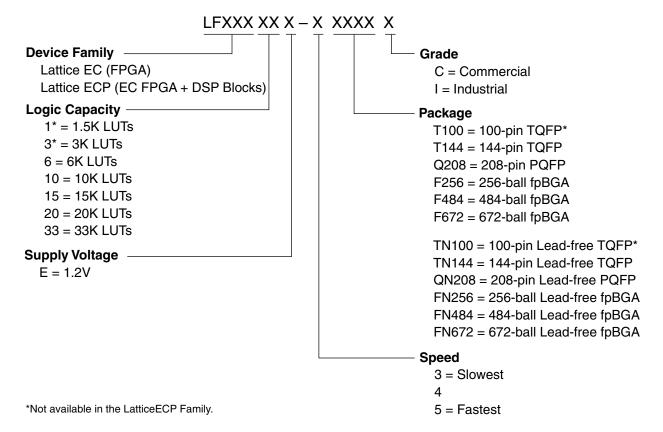

| Ordering Information                                                       |     |

| Part Number Description                                                    |     |

| Ordering Information                                                       | 5-1 |

| Conventional Packaging                                                     |     |

| Lead-Free Packaging                                                        |     |

| Supplemental Information                                                   |     |

| For Further Information                                                    | 6-1 |

| LatticeECP/EC Family Data Sheet Revision History                           |     |

| LatticeECP/EC Family Data Sheet Revision History                           | 7-1 |

|                                                                            |     |

| Section II. LatticeECP/EC Family Technical Notes                           |     |

| LatticeECP/EC and LatticeXP sysIO Usage Guide                              |     |

| Introduction                                                               |     |

| sysIO Buffer Overview                                                      |     |

| Supported sysIO Standards                                                  |     |

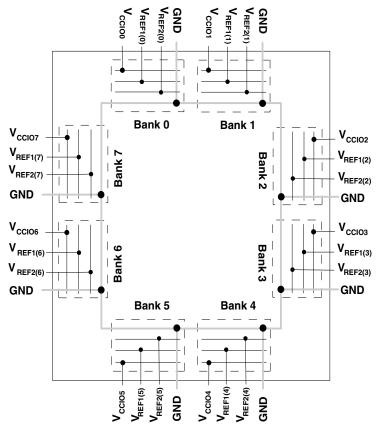

| sysIO Banking Scheme                                                       |     |

| V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)                               |     |

| V <sub>CCAUX</sub> (3.3V)                                                  |     |

| V <sub>CCJ</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)                                |     |

| Input Reference Voltage (V <sub>REF1</sub> , V <sub>REF2</sub> )           |     |

| V <sub>REF1</sub> for DDR Memory Interface                                 |     |

| Mixed Voltage Support in a Bank                                            |     |

| sysIO Standards Supported in Each Bank                                     |     |

| LVCMOS Buffer Configurations                                               |     |

| Programmable Pull-up/Pull-Down/Buskeeper                                   |     |

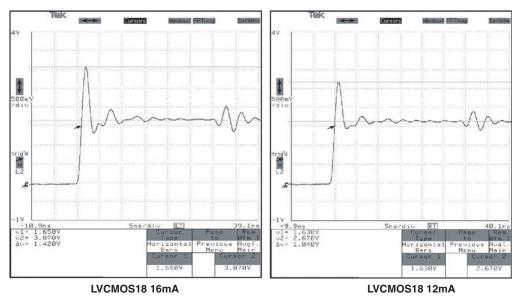

| Programmable Drive                                                         |     |

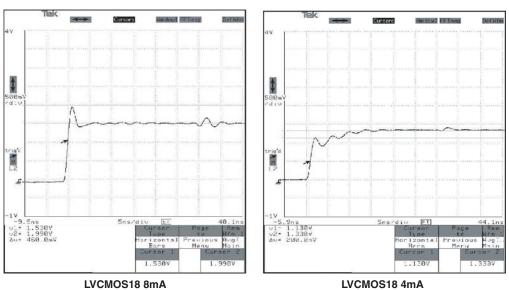

| Programmable Slew Rate                                                     |     |

| Open Drain Control                                                         |     |

| Differential SSTL and HSTL Support                                         |     |

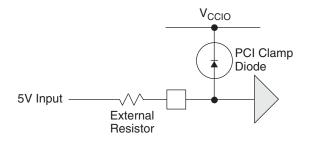

| PCI Support with Programmable PCICLAMP                                     |     |

| 5V Interface with PCI Clamp Diode                                          |     |

| Programmable Input Delay                                                   |     |

| Software sysIO Attributes                                                  |     |

|                                                                            |     |

|                                                                            |     |

|                                                                            |     |

|                                                                            |     |

|                                                                            | -   |

| SLEWRATE<br>FIXEDDELAY                                                     |     |

| DIN/DOUT                                                                   |     |

| LOC                                                                        |     |

| Design Considerations and Usage                                            |     |

| Banking Rules                                                              |     |

| Differential I/O Rules                                                     |     |

| Assigning V <sub>BEF</sub> / V <sub>BEF</sub> Groups for Referenced Inputs |     |

| Differential I/O Implementation.                                           |     |

| LVDS                                                                       |     |

| BLVDS                                                                      |     |

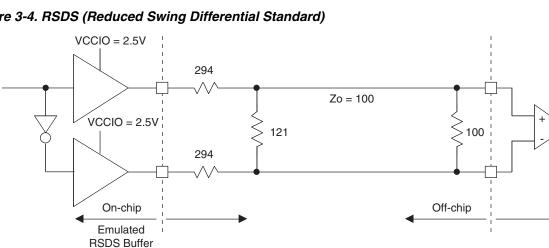

| RSDS                                                                       |     |

| LVPECL                                                                     |     |

| Differential SSTL and HSTL                                                 |     |

|                                                                            |     |

| Technical Support Assistance                                               |     |

| Appendix A. HDL Attributes for Synplify <sup>®</sup> and Precision <sup>®</sup> RTL Synthesis |     |

|-----------------------------------------------------------------------------------------------|-----|

| VHDL Synplify/Precision RTL Synthesis                                                         |     |

| Syntax                                                                                        |     |

| Examples                                                                                      |     |

| Verilog for Synplify                                                                          |     |

| Syntax                                                                                        |     |

| Examples                                                                                      |     |

| Verilog for Precision RTL Synthesis                                                           |     |

| Syntax                                                                                        |     |

| Example                                                                                       |     |

| Appendix B. sysIO Attributes Using Preference Editor User Interface                           |     |

| Appendix C. sysIO Attributes Using Preference File (ASCII File)                               |     |

| IOBUF                                                                                         |     |

| LOCATE                                                                                        |     |

| USE DIN CELL                                                                                  |     |

| USE DOUT CELL                                                                                 |     |

| PGROUP VREF                                                                                   |     |

|                                                                                               |     |

| Memory Usage Guide for LatticeECP/EC and LatticeXP Devices<br>Introduction                    | 0.1 |

| Memories in LatticeECP/EC and LatticeXP Devices                                               |     |

|                                                                                               |     |

| Utilizing IPexpress.                                                                          |     |

| IPexpress Flow                                                                                |     |

| Memory Modules                                                                                |     |

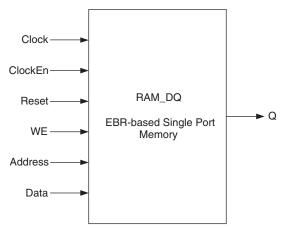

| Single Port RAM (RAM_DQ) – EBR Based                                                          |     |

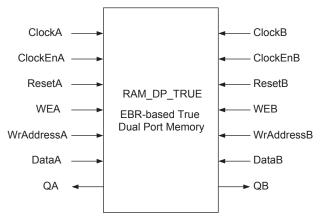

| True Dual Port RAM (RAM_DP_TRUE) – EBR Based                                                  |     |

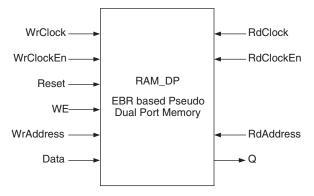

| Pseudo Dual Port RAM (RAM_DP) – EBR-Based                                                     |     |

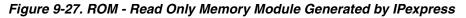

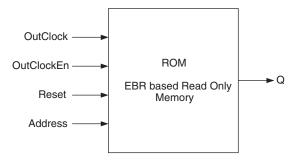

| Read Only Memory (ROM) – EBR Based                                                            |     |

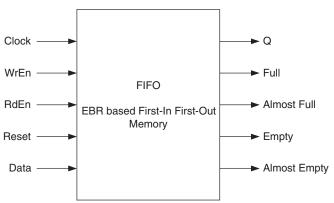

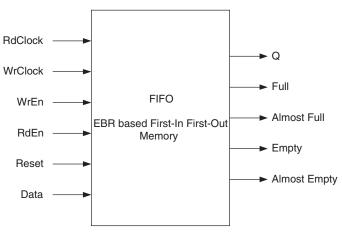

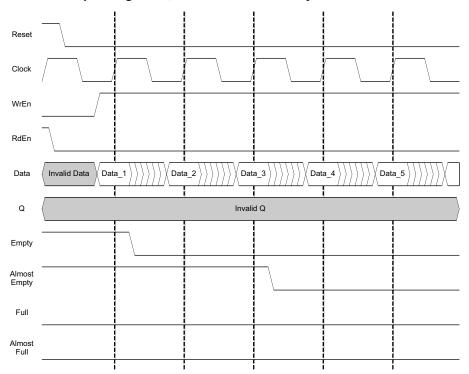

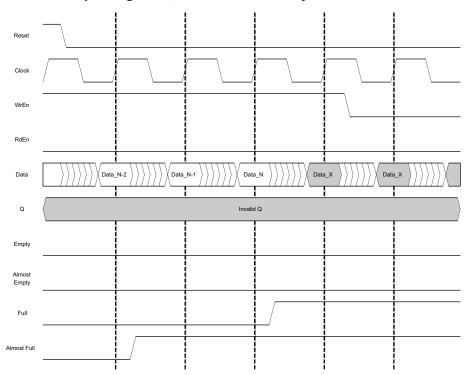

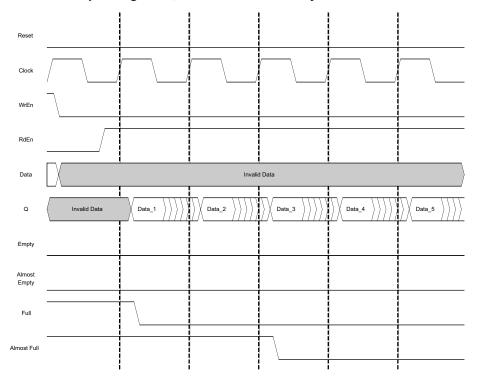

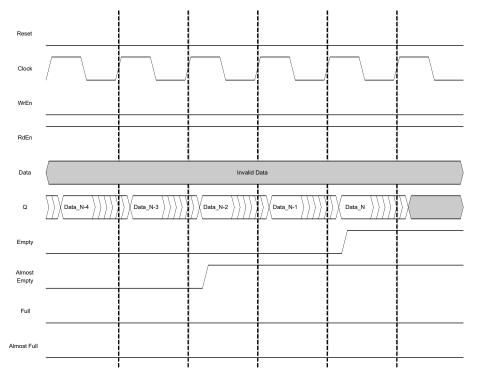

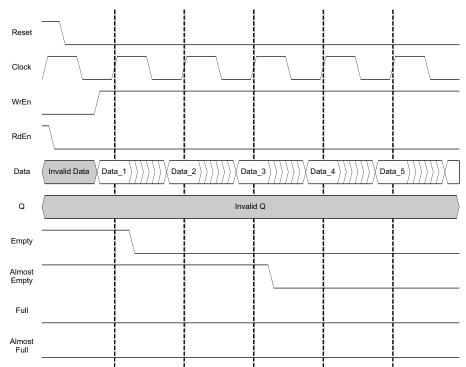

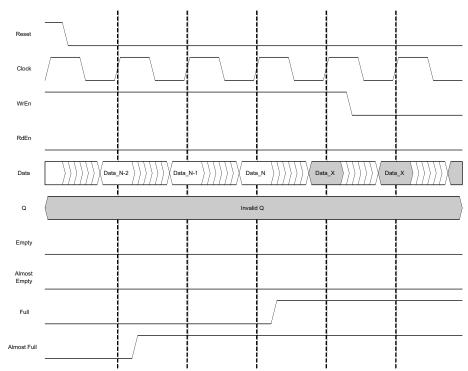

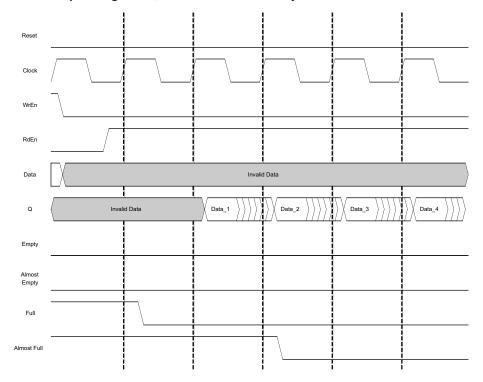

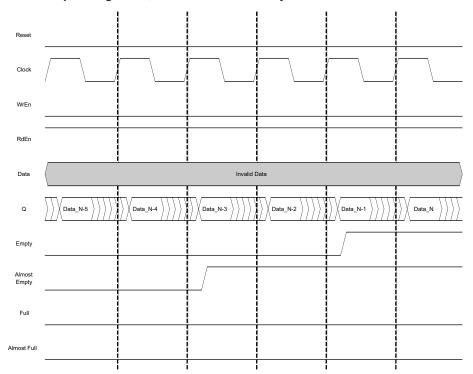

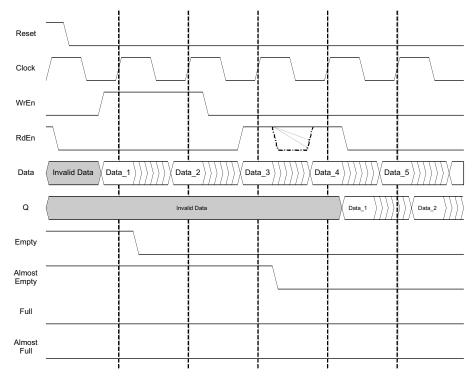

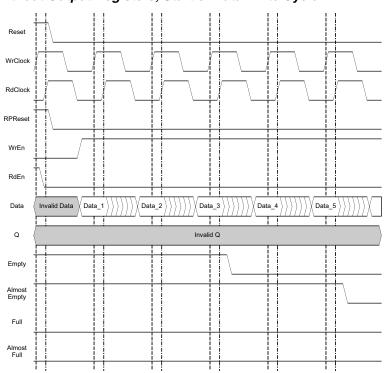

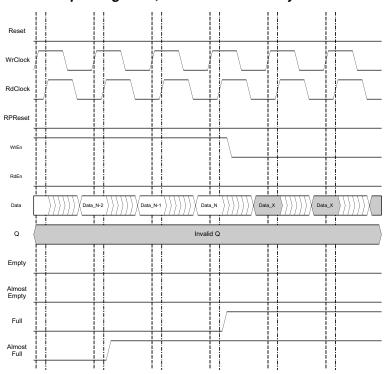

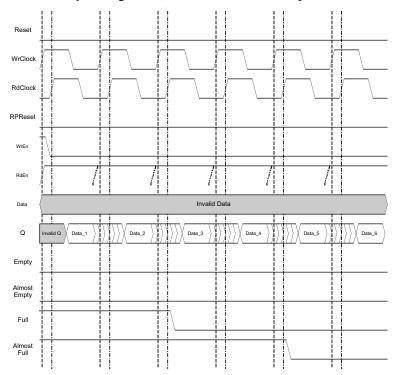

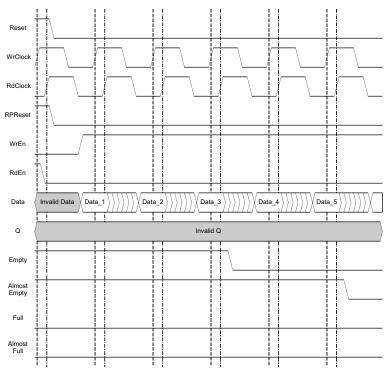

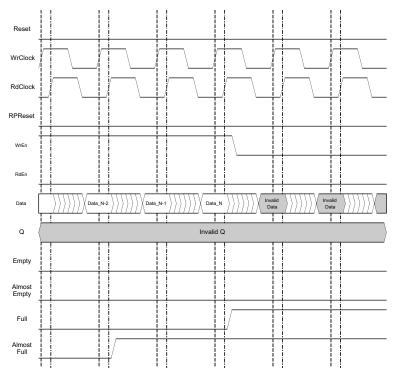

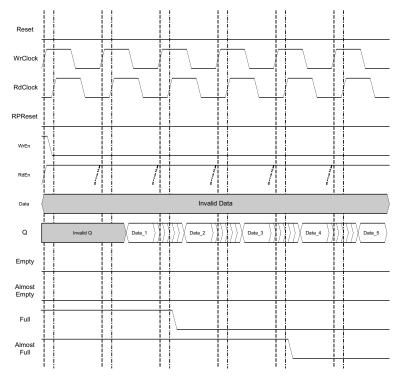

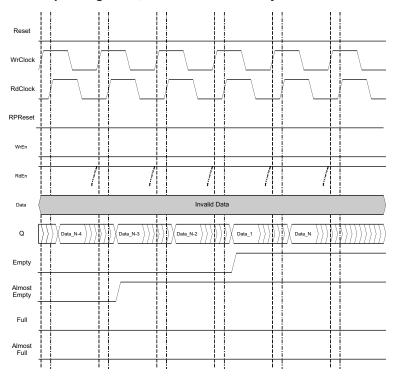

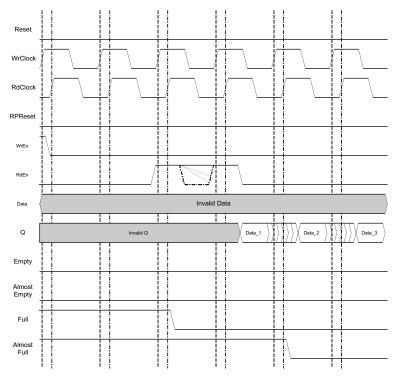

| First In First Out (FIFO, FIFO_DC) – EBR Based                                                |     |

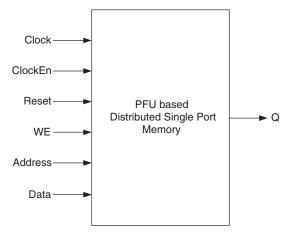

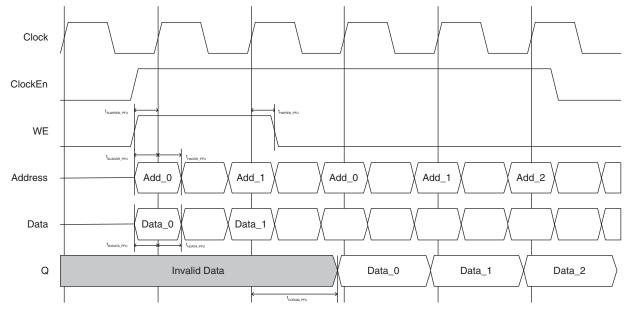

| Distributed Single Port RAM (Distributed_SPRAM) – PFU Based                                   |     |

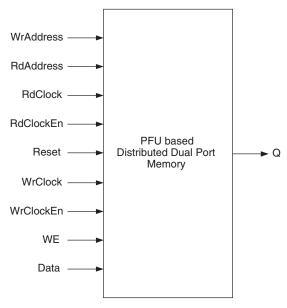

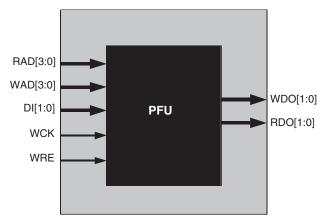

| Distributed Dual Port RAM (Distributed_DPRAM) – PFU Based                                     |     |

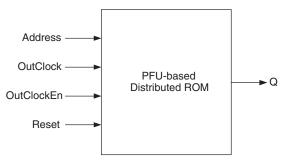

| Distributed ROM (Distributed_ROM) – PFU Based                                                 |     |

| Initializing Memory                                                                           |     |

| Initialization File Format                                                                    |     |

| Technical Support Assistance                                                                  |     |

| Revision History                                                                              |     |

| Appendix A. Attribute Definitions                                                             |     |

| DATA_WIDTH                                                                                    |     |

| REGMODE                                                                                       |     |

| RESETMODE                                                                                     |     |

| CSDECODE                                                                                      |     |

| WRITEMODE                                                                                     |     |

| GSR                                                                                           |     |

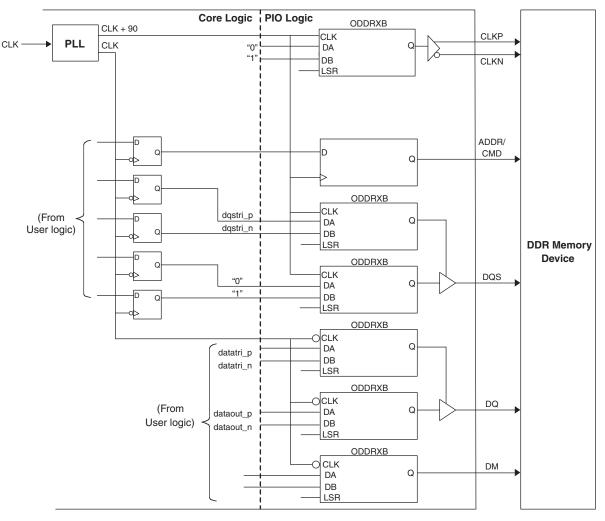

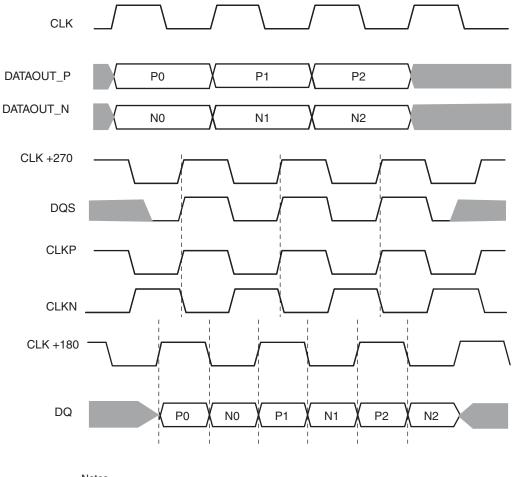

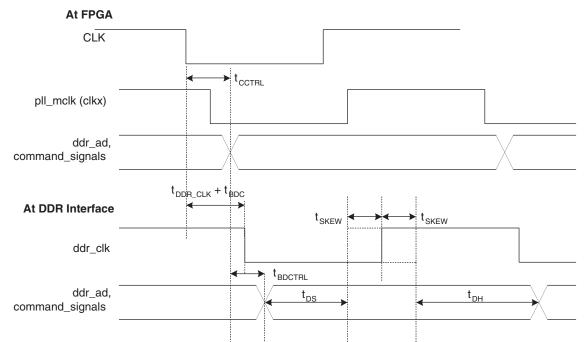

| LatticeECP/EC and LatticeXP DDR Usage Guide                                                   |     |

| Introduction                                                                                  |     |

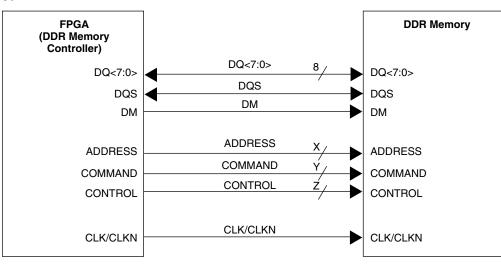

| DDR SDRAM Interfaces Overview                                                                 |     |

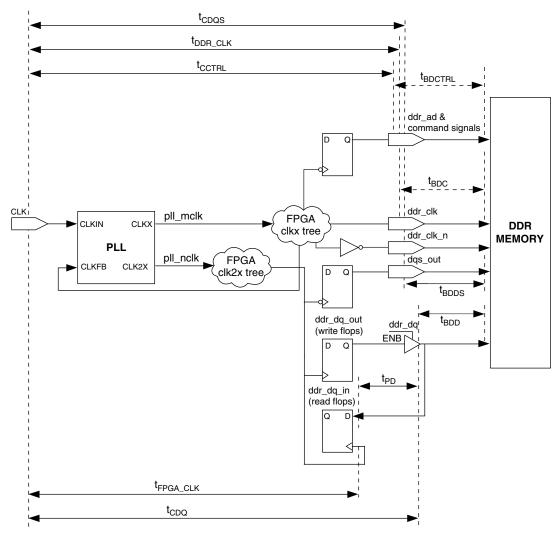

| Implementing DDR Memory Interfaces with the LatticeECP/EC Devices                             |     |

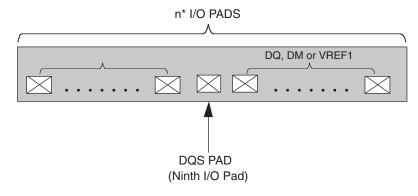

| DQS Grouping                                                                                  |     |

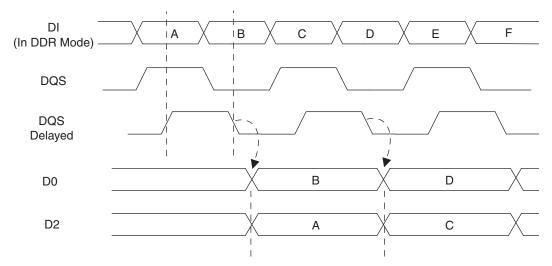

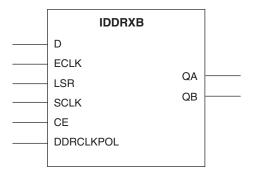

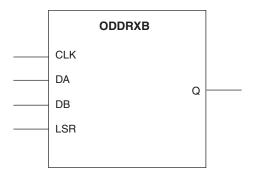

| DDR Software Primitives                                                                       |     |

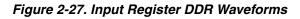

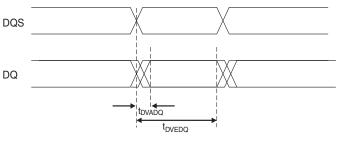

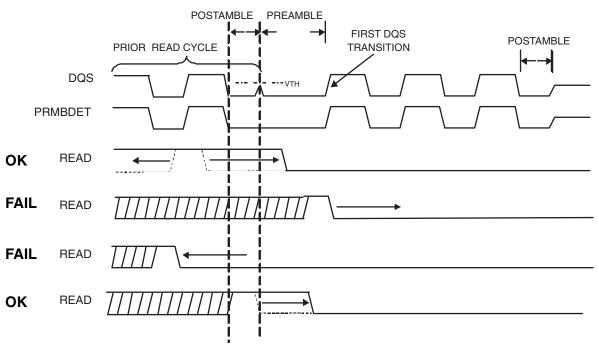

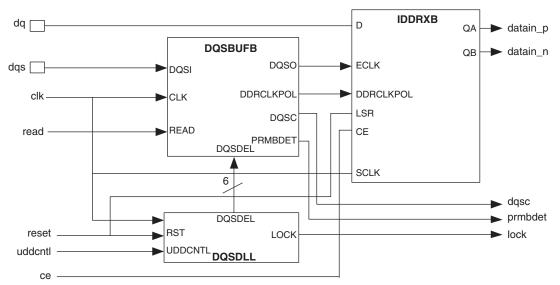

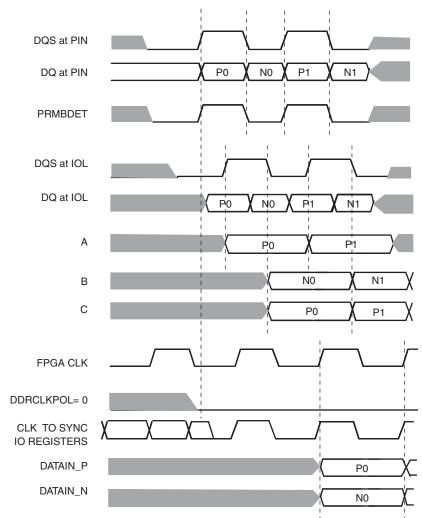

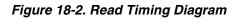

| Memory Read Implementation                                                                    |     |

| Data Read Critical Path                                                                       |     |

| DQS Postamble                                                                                 |     |

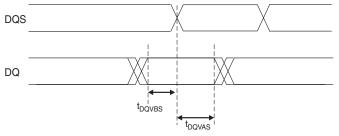

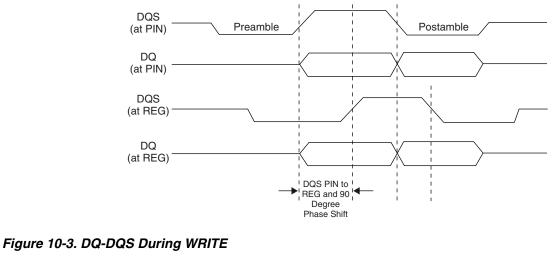

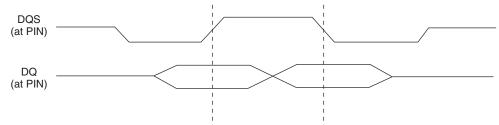

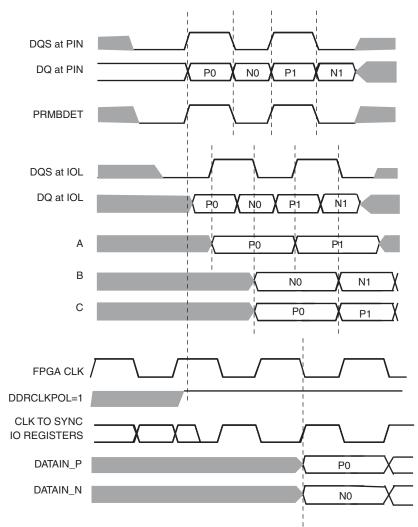

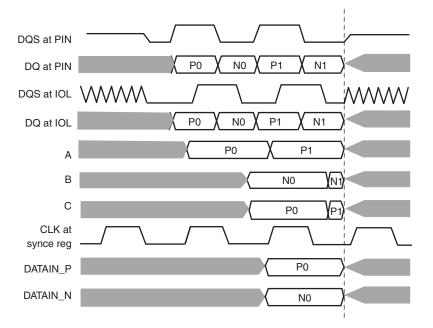

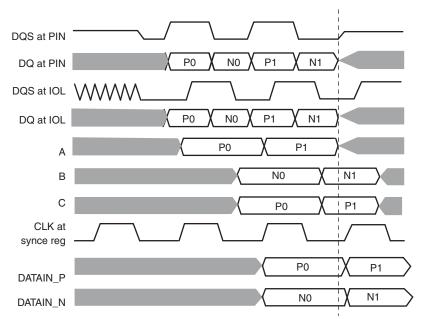

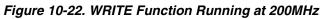

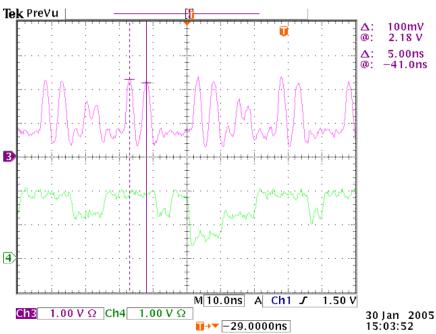

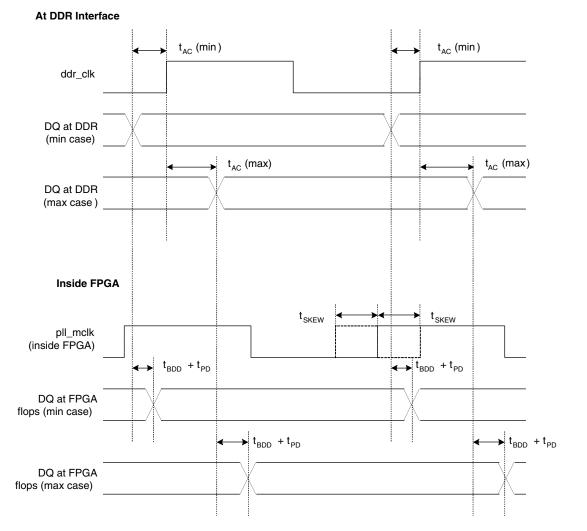

| Memory Write Implementation                                                                   |     |

| Design Rules/Guidelines                                                                       |     |

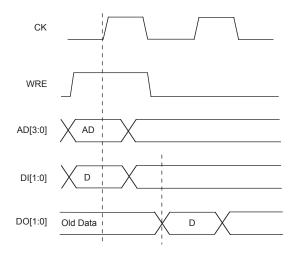

| QDR II Interface                                                                              |     |

|                                                                                               |     |

| FCRAM (Fast Cycle Random Access Memory) Interface                               | 10-17 |

|---------------------------------------------------------------------------------|-------|

| Generic High Speed DDR Implementation                                           | 10-17 |

| Board Design Guidelines                                                         | 10-17 |

| References                                                                      | 10-18 |

| Technical Support Assistance                                                    | 10-18 |

| Revision History                                                                |       |

| Appendix A. Using IPexpress™ to Generate DDR Modules                            | 10-19 |

| DDR Generic                                                                     | 10-19 |

| DDR Memory Interface                                                            | 10-20 |

| Appendix B. Verilog Example for DDR Input and Output Modules                    | 10-21 |

| Appendix C. VHDL Example for DDR Input and Output Modules                       | 10-23 |

| Appendix D. Generic (Non-Memory) High-Speed DDR Interface                       | 10-28 |

| VHDL Implementation                                                             | 10-28 |

| Verilog Example                                                                 | 10-30 |

| Preference File                                                                 | 10-31 |

| Appendix E. List of Compatible DDR SDRAM                                        | 10-32 |

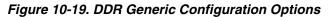

| Appendix F. DDR400 Interface using the LatticeEC Evaluation Board               | 10-35 |

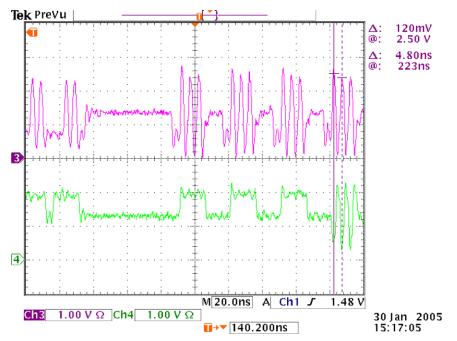

| LatticeECP/EC and LatticeXP sysCLOCK PLL Design and Usage Guide                 |       |

| Introduction                                                                    | 11-1  |

| Features                                                                        | 11-1  |

| Functional Description                                                          | 11-1  |

| PLL Divider and Delay Blocks                                                    | 11-1  |

| PLL Inputs and Outputs                                                          | 11-2  |

| PLL Attributes                                                                  |       |

| LatticeECP/EC and LatticeXP PLL Primitive Definitions                           | 11-4  |

| PLL Attributes Definitions                                                      |       |

| Dynamic Delay Adjustment                                                        |       |

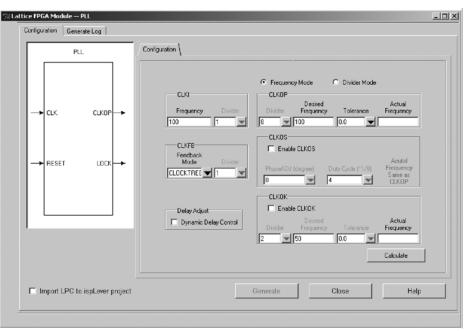

| PLL Usage in IPexpress                                                          |       |

| Including sysCLOCK PLLs in a Design                                             |       |

| IPexpress Usage                                                                 |       |

| EHXPLLB Example Projects                                                        |       |

| Equations for Generating Input and Output Frequency Ranges                      |       |

| f <sub>VCO</sub> Constraint                                                     |       |

| f <sub>PFD</sub> Constraint                                                     |       |

| Clock Distribution in LatticeECP/EC and LatticeXP                               |       |

| Primary Clock Sources and Distribution                                          |       |

| Clock Net Preferences                                                           |       |

| Primary-Pure and Primary-DCS                                                    |       |

| Global Primary Clock and Quadrant Primary Clock                                 |       |

| Secondary Clock Sources and Distribution                                        |       |

| Limitations on Secondary Clock Availability                                     |       |

| Dynamic Clock Selection (DCS)                                                   |       |

| DCS Waveforms                                                                   |       |

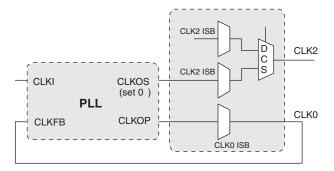

| Use of DCS with PLL                                                             |       |

| Other Design Considerations                                                     |       |

| Jitter Considerations                                                           |       |

| Simulation Limitations                                                          |       |

| PCB Layout Recommendations for VCCPLL and GNDPLL if Separate Pins are Available |       |

| DCS Usage with Verilog                                                          |       |

| DCS Usage with VHDL                                                             |       |

| Technical Support Assistance                                                    |       |

| Revision History                                                                |       |

| Appendix A. Clock Preferences                                                   |       |

| ASIC                                                                            | 11-20 |

| FREQUENCY                                                               |       |

|-------------------------------------------------------------------------|-------|

| MAXSKEW                                                                 |       |

| MULTICYCLE                                                              |       |

| PERIOD                                                                  |       |

| PROHIBIT                                                                |       |

| CLOCK TO OUT                                                            |       |

| INPUT SETUP                                                             |       |

| PLL PHASE BACK                                                          |       |

| Power Estimation and Management for LatticeECP/EC and LatticeXP Devices |       |

| Introduction                                                            |       |

| Power Supply Sequencing and Hot Socketing                               |       |

| Power Calculator Hardware Assumptions                                   |       |

| Power Calculator                                                        |       |

| Power Calculator Equations                                              |       |

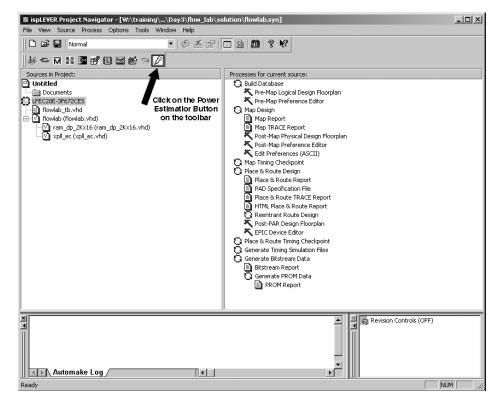

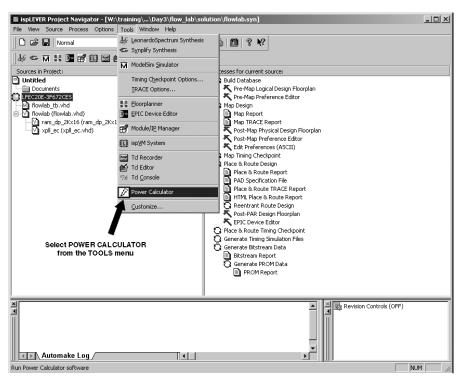

| Starting the Power Calculator                                           | 12-3  |

| Starting a Power Calculator Project                                     |       |

| Power Calculator Main Window                                            |       |

| Power Calculator Wizard                                                 | 12-8  |

| Power Calculator – Creating a New Project Without the NCD File          | 12-13 |

| Power Calculator – Creating a New Project With the NCD File             |       |

| Power Calculator – Open Existing Project                                | 12-16 |

| Power Calculator – Total Power                                          | 12-17 |

| Activity Factor                                                         |       |

| Ambient and Junction Temperature and Airflow                            | 12-18 |

| Managing Power Consumption                                              |       |

| Power Calculator Assumptions                                            | 12-19 |

| Revision History                                                        |       |

| Technical Support Assistance                                            |       |

| Appendix A. Power Calculator Project Example                            | 12-21 |

| LatticeECP/EC sysCONFIG Usage Guide                                     |       |

| Introduction                                                            |       |

| Configuration Pins                                                      |       |

| Dedicated Control Pins                                                  |       |

| Dual-Purpose sysCONFIG Pins                                             |       |

| ispJTAG Pins                                                            |       |

| Configuration and JTAG Pin Physical Description                         |       |

| Configuration Modes<br>Configuration Options                            |       |

| •                                                                       |       |

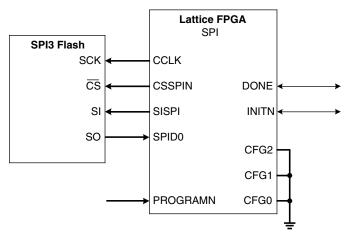

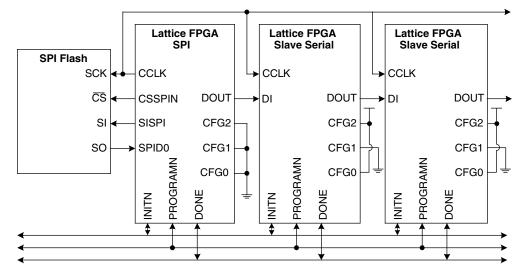

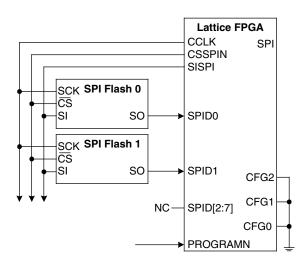

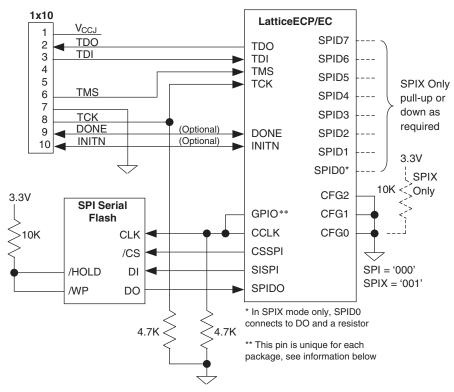

| SPI Mode<br>Multiple FPGA, One SPI Flash                                |       |

|                                                                         |       |

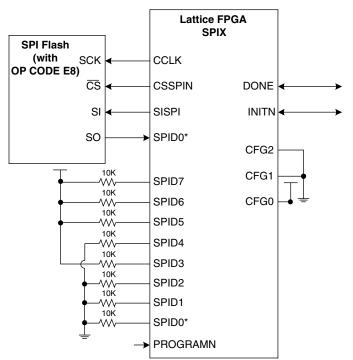

| SPIX Mode<br>Master Serial Mode                                         |       |

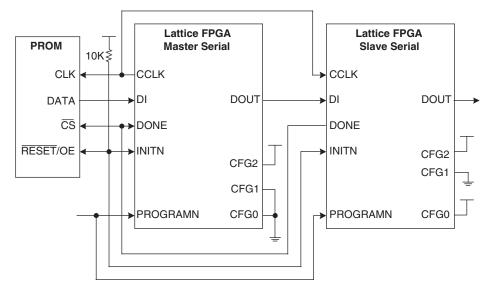

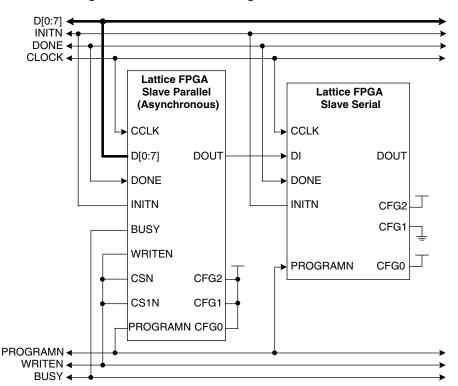

| Slave Serial Mode                                                       |       |

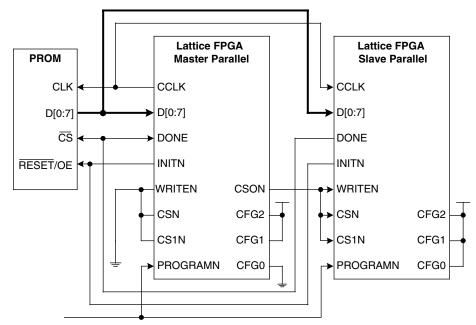

| Master Parallel Mode                                                    |       |

| Slave Parallel Mode                                                     |       |

| ispJTAG Mode                                                            |       |

| Configuration Flow                                                      |       |

| Clearing the Configuration Memory                                       |       |

| Loading the Configuration Memory                                        |       |

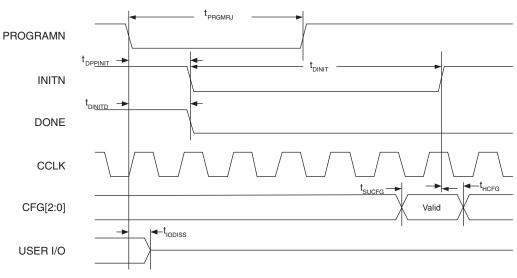

| Wake Up the Device                                                      |       |

| Read Back                                                               |       |

| Read Sequence                                                           |       |

| Software Control                                                        |       |

| Persistent                                                              |       |

| Configuration Mode                                              |  |

|-----------------------------------------------------------------|--|

| DONE Open Drain                                                 |  |

| DONE External                                                   |  |

| Master Clock Selection                                          |  |

| Security                                                        |  |

| Wake-up Sequence                                                |  |

| Wake-up Clock Selection                                         |  |

| Bit Stream Compression                                          |  |

| SPI Compatible SPI Flash Vendors                                |  |

| Technical Support Assistance                                    |  |

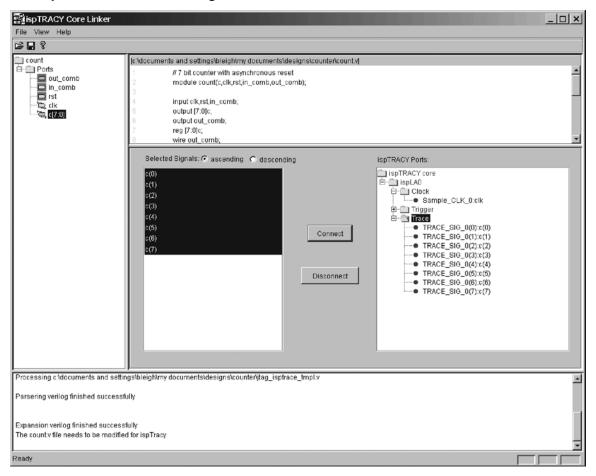

| Lattice ispTRACY Usage Guide                                    |  |

| Introduction                                                    |  |

| ispTRACY IP Core Features                                       |  |

| ispTRACY IP Module Generator                                    |  |

| ispTRACY Core Generator                                         |  |

| ispTRACY Core Linker                                            |  |

| ispTRACY ispLA Program                                          |  |

| Conclusion                                                      |  |

| References                                                      |  |

| Technical Support Assistance                                    |  |

| LatticeECP-DSP sysDSP Usage Guide                               |  |

| Introduction                                                    |  |

| sysDSP Block Hardware                                           |  |

| Overview                                                        |  |

| sysDSP Block Software                                           |  |

| Overview                                                        |  |

| Targeting the sysDSP Block Using IPexpress                      |  |

| Targeting the sysDSP Block by Inference                         |  |

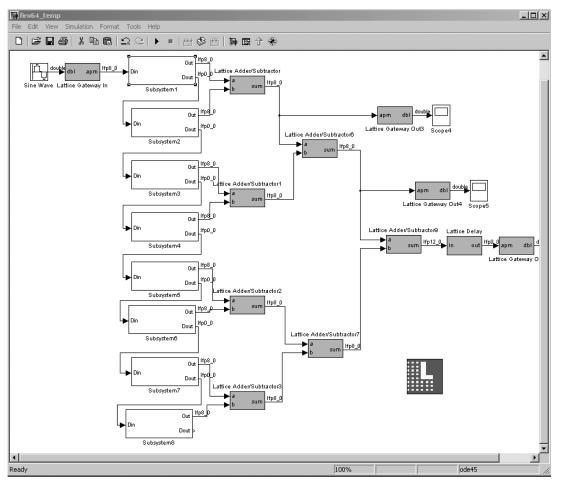

| Targeting the sysDSP Block using Simulink                       |  |

| Targeting the sysDSP Block by Instantiating Primitives          |  |

| sysDSP Blocks in the Report File                                |  |

| MAP Report File                                                 |  |

| Post PAR Report File                                            |  |

| Technical Support Assistance                                    |  |

| Appendix A. DSP Block Primitives                                |  |

| MULT36X36 Primitive                                             |  |

| MULT18X18 Primitive                                             |  |

| MULT18X18MAC Primitive                                          |  |

| MULT18X18ADDSUB Primitive                                       |  |

| MULT18X18ADDSUBSUM Primitive                                    |  |

| MULT9X9 Primitive                                               |  |

| MULT9X9MAC Primitive                                            |  |

| MULT9X9ADDSUB Primitive                                         |  |

| MULT9X9ADDSUBSUM Primitive                                      |  |

| HDL Synthesis Coding Guidelines for Lattice Semiconductor FPGAs |  |

| Introduction                                                    |  |

| General Coding Styles for FPGA                                  |  |

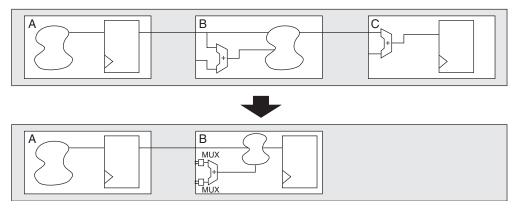

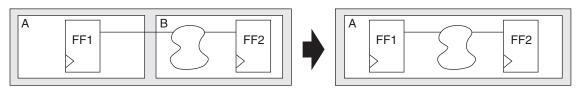

| Hierarchical Coding                                             |  |

| Design Partitioning                                             |  |

| State Encoding Methodologies for State Machines                 |  |

| Coding Styles for FSM                                           |  |

| Using Pipelines in the Designs                                  |  |

| Comparing IF statement and CASE statement                       |  |

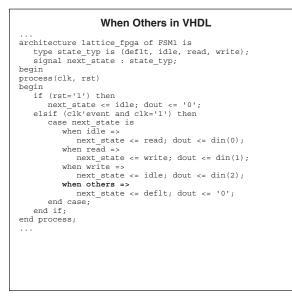

| Avoiding Non-intentional Latches                                |  |

| g                                                               |  |

| HDL Design with Lattice Semiconductor FPGA Devices                              | 16-8  |

|---------------------------------------------------------------------------------|-------|

| Lattice Semiconductor FPGA Synthesis Library                                    |       |

| Implementing Multiplexers                                                       | 16-10 |

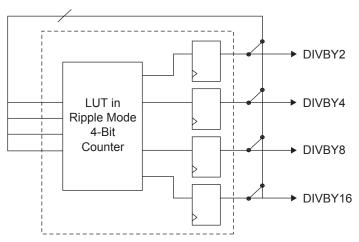

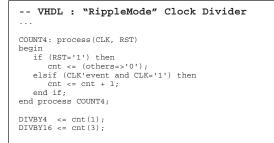

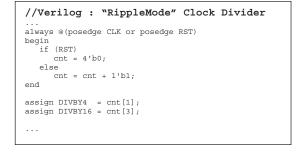

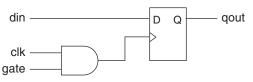

| Clock Dividers                                                                  | 16-10 |

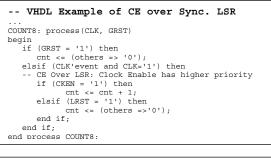

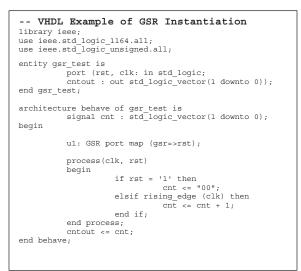

| Register Control Signals                                                        | 16-12 |

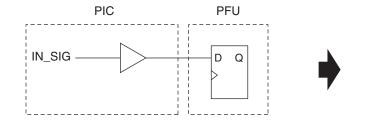

| Use PIC Features                                                                |       |

| Implementation of Memories                                                      |       |

| Preventing Logic Replication and Limited Fanout                                 |       |

| Use ispLEVER Project Navigator Results for Device Utilization and Performance   |       |

| Technical Support Assistance                                                    | 16-17 |

| Lattice Semiconductor Design Floorplanning                                      |       |

| Introduction                                                                    |       |

| Supported Architectures                                                         |       |

| Related Documentation                                                           |       |

| Floorplanning Definition                                                        |       |

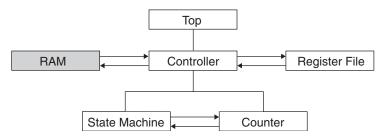

| Complex FPGA Design Management                                                  |       |

| Floorplanning Design Flow                                                       |       |

| When to Floorplan                                                               |       |

| Floorplan to Improve Design Performance                                         |       |

| Floorplan to Preserve Module Performance                                        |       |

| Floorplan for Design Reuse                                                      |       |

| How to Floorplan a Design                                                       |       |

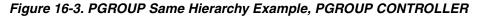

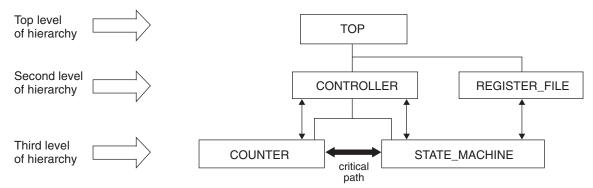

| Design Performance Enhancement Strategies<br>Design Floorplanning Methodologies |       |

| When to use PGROUP vs. UGROUP                                                   |       |

| Floorplanner GUI Usage                                                          |       |

| Special Floorplanning Considerations                                            |       |

| Embedded Block RAM Placement                                                    |       |

| I/O Grouping                                                                    |       |

| Large Module Grouping                                                           |       |

| Carry Chains and Bus Grouping                                                   |       |

| SLICs in Groups                                                                 |       |

| Summary                                                                         |       |

| Technical Support Assistance                                                    |       |

| Lattice Semiconductor FPGA Successful Place and Route                           |       |

| Introduction                                                                    |       |

| ispLEVER Place and Route Software (PAR)                                         |       |

| Placement                                                                       |       |

| Routing                                                                         |       |

| Timing Driven PAR Process                                                       |       |

| General Strategy Guidelines                                                     |       |

| Typical Design Preferences                                                      |       |

| Proper Preferences                                                              |       |

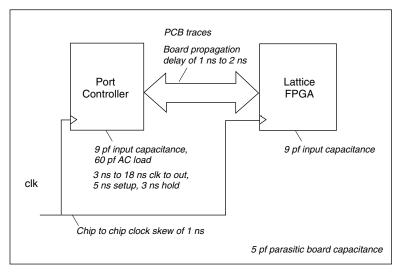

| Translating Board Requirements into FPGA Preferences                            |       |

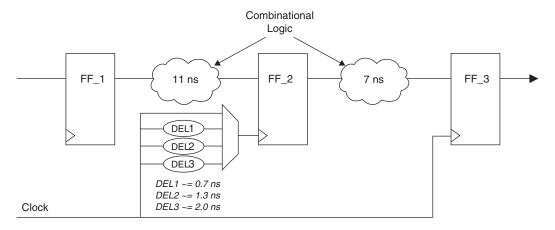

| Analyzing Timing Reports                                                        |       |

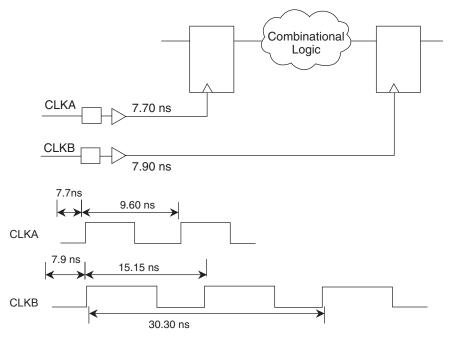

| Example 1. Multicycle Between Two Different Clocks                              |       |

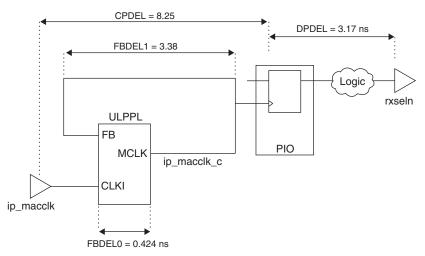

| Example 2. CLOCK_TO_OUT with PLL Feedback                                       |       |

| ispLEVER Controlled Place and Route                                             |       |

| . Running Multiple Routing Passes                                               |       |

| Using Multiple Placement Iterations (Cost Tables)                               |       |

| Clock Boosting                                                                  |       |

| Guided Map and PAR                                                              |       |

| Notes on Guided Mapping                                                         |       |

| Notes on Guided PAR                                                             |       |

| Conclusion                                                        |  |

|-------------------------------------------------------------------|--|

| Technical Support Assistance                                      |  |

| Board Timing Guidelines for the DDR SDRAM Controller IP Core      |  |

| Introduction                                                      |  |

| Read Operation                                                    |  |

| Set-up Time Calculation for the Data Input (Max. Case)            |  |

| Hold Time Calculation for the Data Input (Min. Case)              |  |

| Write Operation                                                   |  |

| Write Set-up                                                      |  |

| Write Hold                                                        |  |

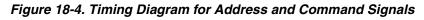

| Address and Command Signals                                       |  |

| Set-up Calculation                                                |  |

| Hold Calculation                                                  |  |

| Board Design Guidelines                                           |  |

| Technical Support Assistance                                      |  |

| Appendix A. Example Extractions of Delays from Timing Reports     |  |

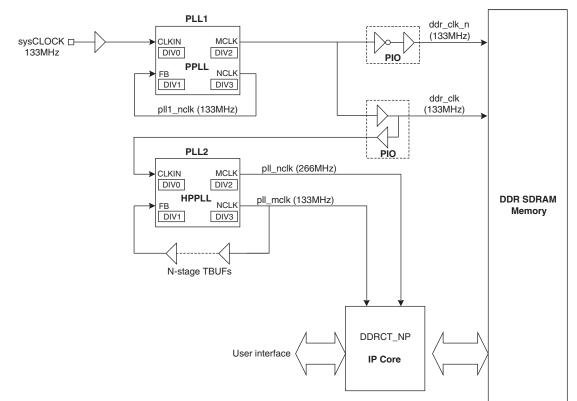

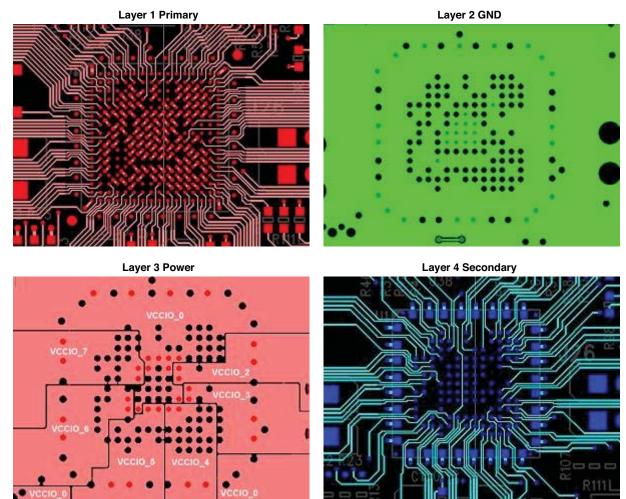

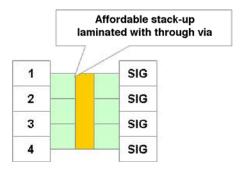

| PCB Layout Recommendations for BGA Packages                       |  |

| Introduction                                                      |  |

| Advantages and Disadvantages of BGA Packaging                     |  |

| PCB Layout                                                        |  |

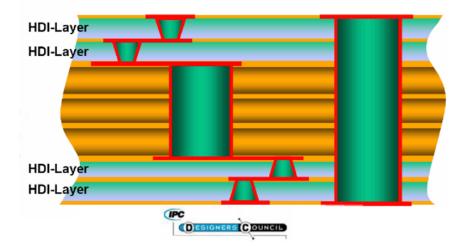

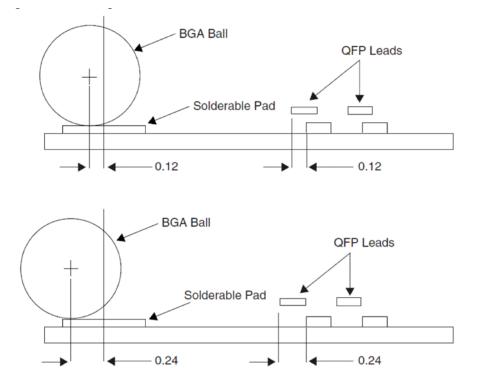

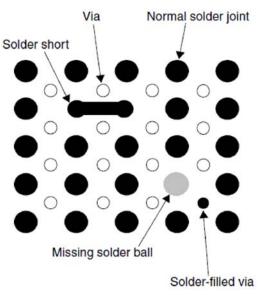

| Plated Through Hole (Via) Placement                               |  |

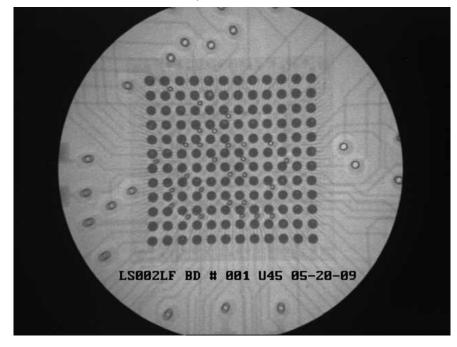

| BGA Board Layout Recommendations                                  |  |

| BGA Package Types                                                 |  |

| Further Information                                               |  |

| Technical Support Assistance                                      |  |

| Revision History                                                  |  |

| SPI Serial Flash Programming Using ispJTAG on LatticeECP/EC FPGAs |  |

| Introduction                                                      |  |

| Related Documents                                                 |  |

| Hardware and Software Requirements                                |  |

| SPI/SPIX Differences                                              |  |

| SPI Serial Flash Sizing                                           |  |

| Hardware                                                          |  |

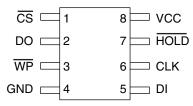

| SPI Serial Flash Interface                                        |  |

| ispJTAG Interface                                                 |  |

| Schematic                                                         |  |

| Software                                                          |  |

| Programming Procedure                                             |  |

| Including the SPI Interface in the FPGA Design                    |  |

| Sample Code                                                       |  |

| Locking the Pins                                                  |  |

| Design Notes                                                      |  |

| Conclusion                                                        |  |

| Technical Support Assistance                                      |  |

|                                                                   |  |

# Section III. LatticeECP/EC Family Handbook Revision History

| sion History |

|--------------|

|--------------|

# Section I. LatticeECP/EC Family Data Sheet

DS1000 Version 02.7, February 2008

# LatticeECP/EC Family Data Sheet Introduction

#### May 2005

# **Features**

- Extensive Density and Package Options

- 1.5K to 32.8K LUT4s

- 65 to 496 I/Os

- Density migration supported

- sysDSP<sup>™</sup> Block (LatticeECP<sup>™</sup> Versions)

- High performance multiply and accumulate

- 4 to 8 blocks

- 4 to 8 36x36 multipliers or

- 16 to 32 18x18 multipliers or

- 32 to 64 9x9 multipliers

#### Embedded and Distributed Memory

- 18 Kbits to 498 Kbits sysMEM<sup>™</sup> Embedded Block RAM (EBR)

- Up to 131 Kbits distributed RAM

- Flexible memory resources:

- Distributed and block memory

#### ■ Flexible I/O Buffer

Programmable sysl/O<sup>™</sup> buffer supports wide range of interfaces:

#### Table 1-1. LatticeECP/EC Family Selection Guide

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- SSTL 3/2 Class I, II, SSTL18 Class I

- HSTL 18 Class I, II, III, HSTL15 Class I, III

- PCI

- LVDS, Bus-LVDS, LVPECL, RSDS

- Dedicated DDR Memory Support

- Implements interface up to DDR400 (200MHz)

#### ■ sysCLOCK<sup>™</sup> PLLs

- Up to four analog PLLs per device

- · Clock multiply, divide and phase shifting

#### System Level Support

- IEEE Standard 1149.1 Boundary Scan, plus ispTRACY™ internal logic analyzer capability

- SPI boot flash interface

- 1.2V power supply

#### Low Cost FPGA

- · Features optimized for mainstream applications

- Low cost TQFP and PQFP packaging

| Device                         | LFEC1 | LFEC3 | LFEC6/<br>LFECP6 | LFEC10/<br>LFECP10 | LFEC15/<br>LFECP15 | LFEC20/<br>LFECP20 | LFEC33/<br>LFECP33 |

|--------------------------------|-------|-------|------------------|--------------------|--------------------|--------------------|--------------------|

| PFU/PFF Rows                   | 12    | 16    | 24               | 32                 | 40                 | 44                 | 64                 |

| PFU/PFF Columns                | 16    | 24    | 32               | 40                 | 48                 | 56                 | 64                 |

| PFUs/PFFs                      | 192   | 384   | 768              | 1280               | 1920               | 2464               | 4096               |

| LUTs (K)                       | 1.5   | 3.1   | 6.1              | 10.2               | 15.4               | 19.7               | 32.8               |

| Distributed RAM (Kbits)        | 6     | 12    | 25               | 41                 | 61                 | 79                 | 131                |

| EBR SRAM (Kbits)               | 18    | 55    | 92               | 276                | 350                | 424                | 498                |

| EBR SRAM Blocks                | 2     | 6     | 10               | 30                 | 38                 | 46                 | 54                 |

| sysDSP Blocks <sup>1</sup>     | _     | —     | 4                | 5                  | 6                  | 7                  | 8                  |

| 18x18 Multipliers <sup>1</sup> | _     | —     | 16               | 20                 | 24                 | 28                 | 32                 |

| V <sub>CC</sub> Voltage (V)    | 1.2   | 1.2   | 1.2              | 1.2                | 1.2                | 1.2                | 1.2                |

| Number of PLLs                 | 2     | 2     | 2                | 4                  | 4                  | 4                  | 4                  |

| Packages and I/O Combination   | ons:  | •     |                  |                    |                    |                    |                    |

| 100-pin TQFP (14 x 14 mm)      | 67    | 67    |                  |                    |                    |                    |                    |

| 144-pin TQFP (20 x 20 mm)      | 97    | 97    | 97               |                    |                    |                    |                    |

| 208-pin PQFP (28 x 28 mm)      | 112   | 145   | 147              | 147                |                    |                    |                    |

| 256-ball fpBGA (17 x 17 mm)    |       | 160   | 195              | 195                | 195                |                    |                    |

| 484-ball fpBGA (23 x 23 mm)    |       |       | 224              | 288                | 352                | 360                | 360                |

| 672-ball fpBGA (27 x 27 mm)    |       |       |                  |                    |                    | 400                | 496                |

1. LatticeECP devices only.

#### Data Sheet

<sup>© 2005</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Introduction

The LatticeECP/EC family of FPGA devices is optimized to deliver mainstream FPGA features at low cost. For maximum performance and value, the LatticeECP<sup>TM</sup> (<u>EC</u>onomy <u>P</u>lus) FPGA concept combines an efficient FPGA fabric with high-speed dedicated functions. Lattice's first family to implement this approach is the LatticeECP<sup>TM</sup> (<u>EC</u>onomy <u>P</u>lus <u>DSP</u>) family, providing dedicated high-performance DSP blocks on-chip. The LatticeEC<sup>TM</sup> (<u>EC</u>onomy) family supports all the general purpose features of LatticeECP devices without dedicated function blocks to achieve lower cost solutions.

The LatticeECP/EC FPGA fabric, which was designed from the outset with low cost in mind, contains all the critical FPGA elements: LUT-based logic, distributed and embedded memory, PLLs and support for mainstream I/Os. Dedicated DDR memory interface logic is also included to support this memory that is becoming increasingly prevalent in cost-sensitive applications.

The ispLEVER<sup>®</sup> design tool suite from Lattice allows large complex designs to be efficiently implemented using the LatticeECP/EC FPGA family. Synthesis library support for LatticeECP/EC is available for popular logic synthesis tools. The ispLEVER tool uses the synthesis tool output along with the constraints from its floor planning tools to place and route the design in the LatticeECP/EC device. The ispLEVER tool extracts the timing from the routing and back-annotates it into the design for timing verification.

Lattice provides many pre-designed IP (Intellectual Property) ispLeverCORE<sup>™</sup> modules for the LatticeECP/EC family. By using these IPs as standardized blocks, designers are free to concentrate on the unique aspects of their design, increasing their productivity.

# LatticeECP/EC Family Data Sheet Architecture

May 2007

Data Sheet

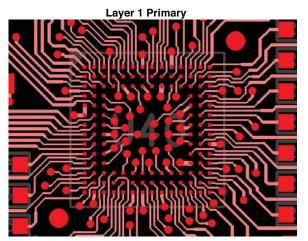

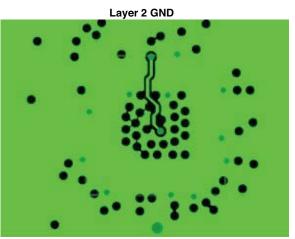

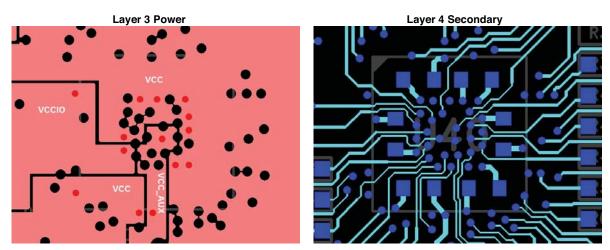

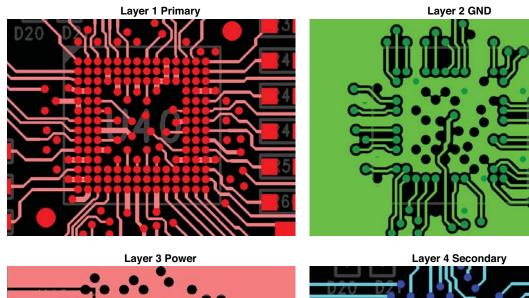

# **Architecture Overview**

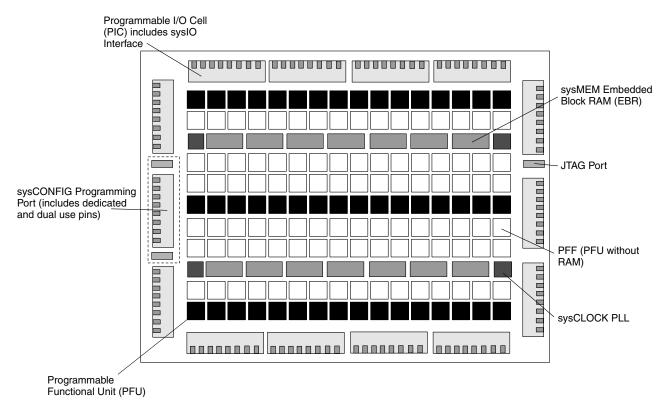

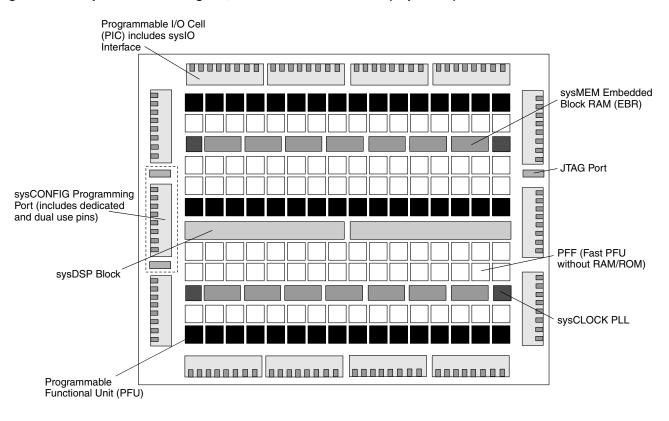

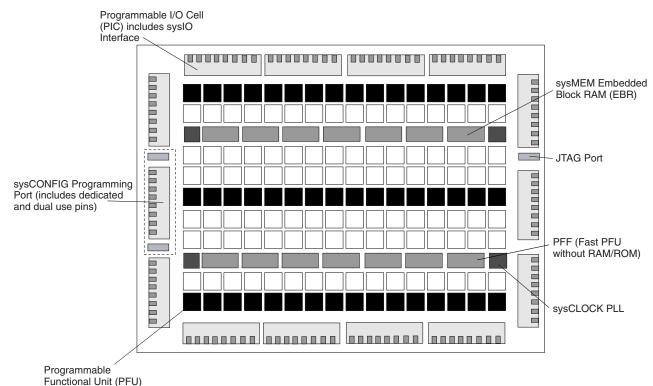

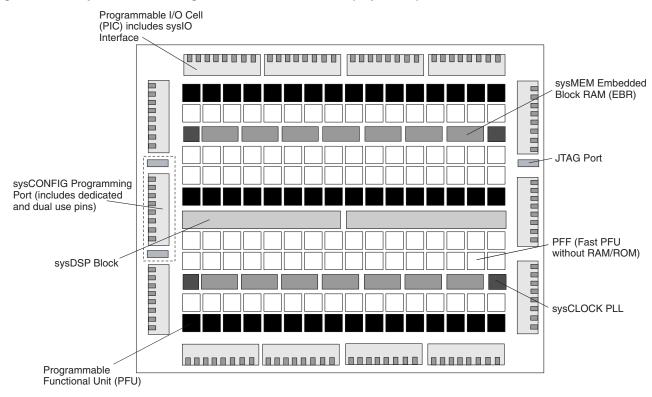

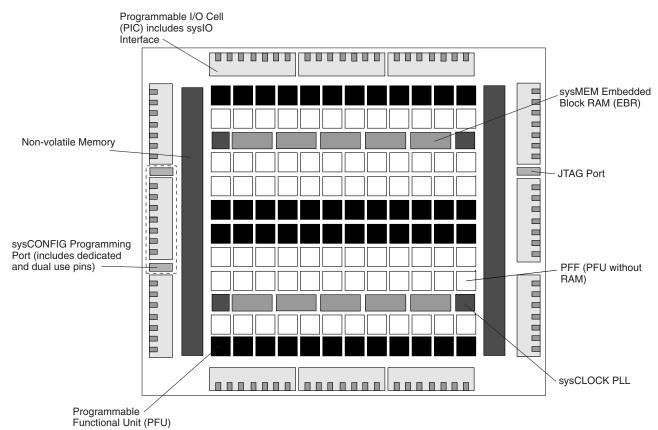

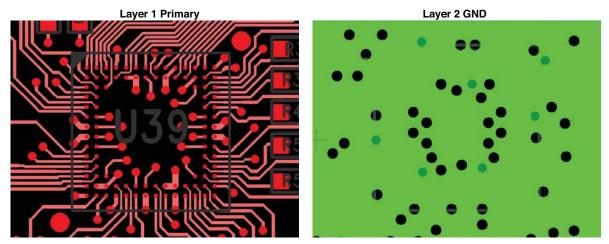

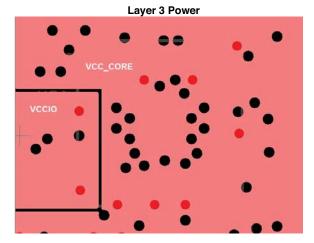

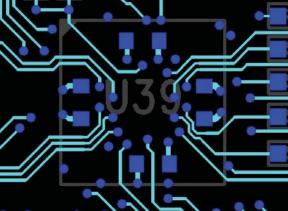

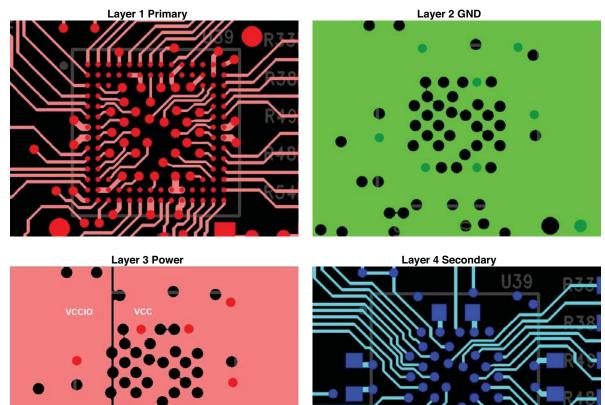

The LatticeECP-DSP and LatticeEC architectures contain an array of logic blocks surrounded by Programmable I/ O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR), as shown in Figures 2-1 and 2-2. In addition, LatticeECP-DSP supports an additional row of DSP blocks, as shown in Figure 2-2.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional unit without RAM/ROM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM and register functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row. The PFU blocks are used on the outside rows. The rest of the core consists of rows of PFF blocks interspersed with rows of PFU blocks. For every three rows of PFF blocks there is a row of PFU blocks.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. sysMEM EBRs are large dedicated fast memory blocks. They can be configured as RAM or ROM.

The PFU, PFF, PIC and EBR Blocks are arranged in a two-dimensional grid with rows and columns as shown in Figure 2-1. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

At the end of the rows containing the sysMEM Blocks are the sysCLOCK Phase Locked Loop (PLL) Blocks. These PLLs have multiply, divide and phase shifting capability; they are used to manage the phase relationship of the clocks. The LatticeECP/EC architecture provides up to four PLLs per device.

Every device in the family has a JTAG Port with internal Logic Analyzer (ispTRACY) capability. The sysCONFIG<sup>™</sup> port which allows for serial or parallel device configuration. The LatticeECP/EC devices use 1.2V as their core voltage.

© 2007 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Figure 2-1. Simplified Block Diagram, LatticeEC Device (Top Level)

Figure 2-2. Simplified Block Diagram, LatticeECP-DSP Device (Top Level)

# **PFU and PFF Blocks**

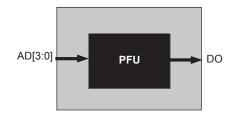

The core of the LatticeECP/EC devices consists of PFU and PFF blocks. The PFUs can be programmed to perform Logic, Arithmetic, Distributed RAM and Distributed ROM functions. PFF blocks can be programmed to perform Logic, Arithmetic and ROM functions. Except where necessary, the remainder of the data sheet will use the term PFU to refer to both PFU and PFF blocks.

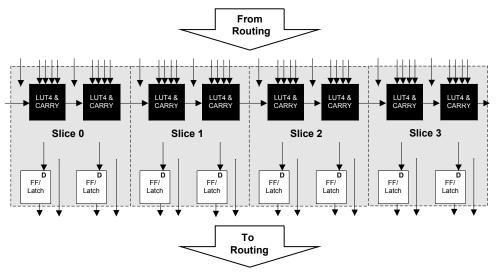

Each PFU block consists of four interconnected slices, numbered 0-3 as shown in Figure 2-3. All the interconnections to and from PFU blocks are from routing. There are 53 inputs and 25 outputs associated with each PFU block.

## Figure 2-3. PFU Diagram

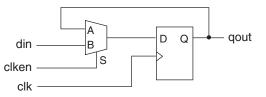

# Slice

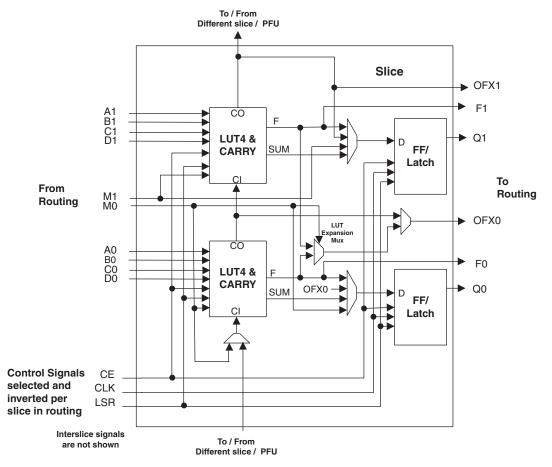

Each slice contains two LUT4 lookup tables feeding two registers (programmed to be in FF or Latch mode), and some associated logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. There is control logic to perform set/reset functions (programmable as synchronous/asynchronous), clock select, chip-select and wider RAM/ROM functions. Figure 2-4 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge/level clocks.

There are 14 input signals: 13 signals from routing and one from the carry-chain (from adjacent slice or PFU). There are 7 outputs: 6 to routing and one to carry-chain (to adjacent PFU). Table 2-1 lists the signals associated with each slice.

#### Figure 2-4. Slice Diagram

Table 2-1. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | MO             | Multipurpose Input                                                   |

| Input    | Multi-purpose    | M1             | Multipurpose Input                                                   |

| Input    | Control signal   | CE             | Clock Enable                                                         |

| Input    | Control signal   | LSR            | Local Set/Reset                                                      |

| Input    | Control signal   | CLK            | System Clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast Carry In <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register Outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | For the right most PFU the fast carry chain output <sup>1</sup>      |

1. See Figure 2-3 for connection details.

2. Requires two PFUs.

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

#### Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM         |

|-----------|--------------------|-----------------------|---------|-------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SPR16x2 | ROM16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- · Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

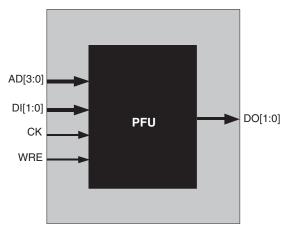

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x1-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

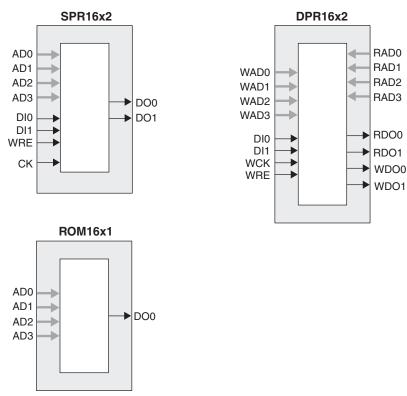

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-5 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices, one Slice functions as the read-write port. The other companion Slice supports the read-only port. For more information about using RAM in LatticeECP/EC devices, please see the list of technical documentation at the end of this data sheet.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

| Number of aliana 1 0 |                  | SPR16x2 | DPR16x2 |

|----------------------|------------------|---------|---------|

| Number of slices 1 2 | Number of slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

#### Figure 2-5. Distributed Memory Primitives

**ROM Mode:** The ROM mode uses the same principal as the RAM modes, but without the Write port. Pre-loading is accomplished through the programming interface during configuration.

#### **PFU Modes of Operation**

Slices can be combined within a PFU to form larger functions. Table 2-4 tabulates these modes and documents the functionality possible at the PFU level.

| Logic                      | Ripple            | RAM <sup>1</sup>           | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

1. These modes are not available in PFF blocks

# Routing

There are many resources provided in the LatticeECP/EC devices to route signals individually or as busses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with x1 (spans two PFU), x2 (spans three PFU) and x6 (spans seven PFU). The x1 and x2 connections provide fast and efficient connections in horizontal and vertical directions. The x2 and x6 resources are buffered, the routing of both short and long connections between PFUs.

The ispLEVER design tool suite takes the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

# **Clock Distribution Network**

The clock inputs are selected from external I/O, the sysCLOCK<sup>™</sup> PLLs or routing. These clock inputs are fed through the chip via a clock distribution system.

# **Primary Clock Sources**

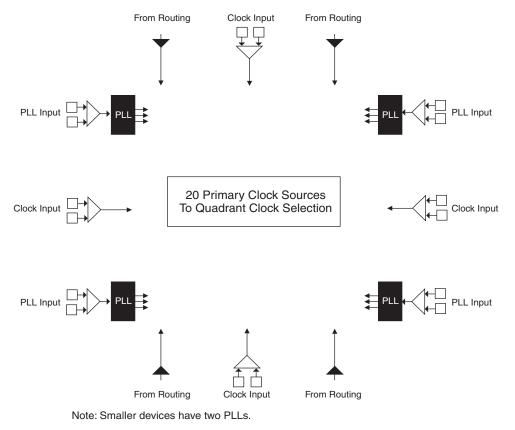

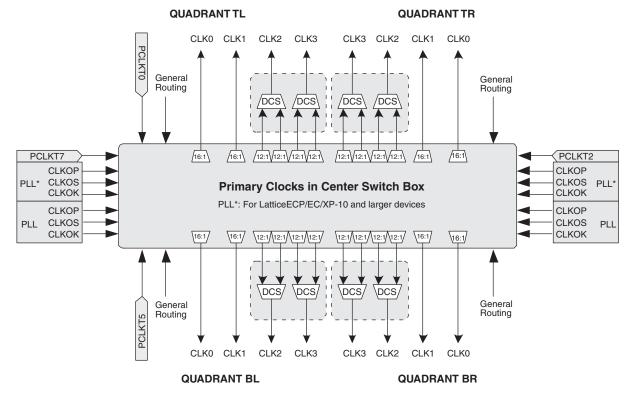

LatticeECP/EC devices derive clocks from three primary sources: PLL outputs, dedicated clock inputs and routing. LatticeECP/EC devices have two to four sysCLOCK PLLs, located on the left and right sides of the device. There are four dedicated clock inputs, one on each side of the device. Figure 2-6 shows the 20 primary clock sources.

# Figure 2-6. Primary Clock Sources

# Secondary Clock Sources

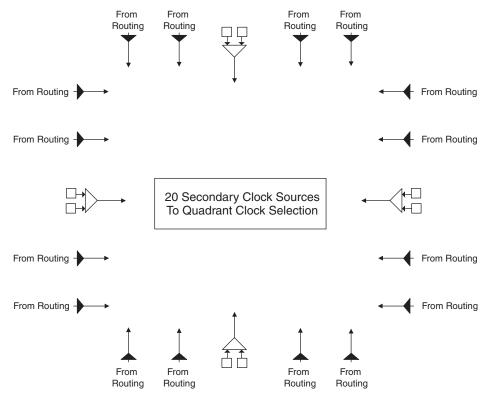

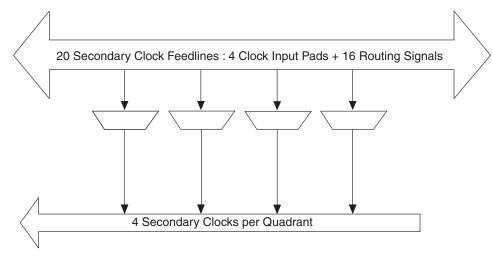

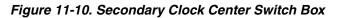

LatticeECP/EC devices have four secondary clock resources per quadrant. The secondary clock branches are tapped at every PFU. These secondary clock networks can also be used for controls and high fanout data. These secondary clocks are derived from four clock input pads and 16 routing signals as shown in Figure 2-7.

#### Figure 2-7. Secondary Clock Sources

# **Clock Routing**

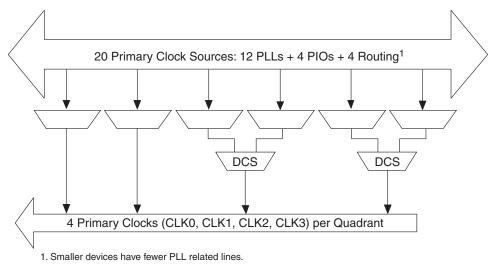

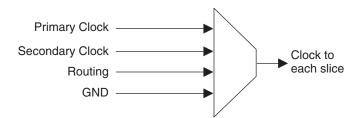

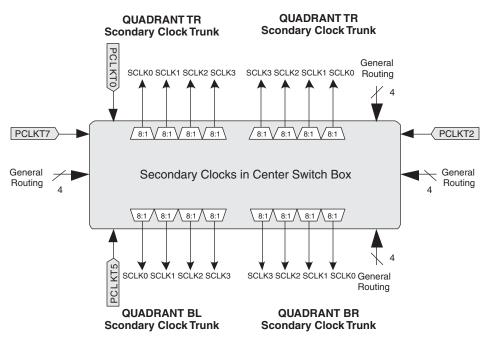

The clock routing structure in LatticeECP/EC devices consists of four Primary Clock lines and a Secondary Clock network per quadrant. The primary clocks are generated from MUXs located in each quadrant. Figure 2-8 shows this clock routing. The four secondary clocks are generated from MUXs located in each quadrant as shown in Figure 2-9. Each slice derives its clock from the primary clock lines, secondary clock lines and routing as shown in Figure 2-10.

# Lattice Semiconductor

#### Figure 2-8. Per Quadrant Primary Clock Selection

Figure 2-9. Per Quadrant Secondary Clock Selection

Figure 2-10. Slice Clock Selection

# sysCLOCK Phase Locked Loops (PLLs)

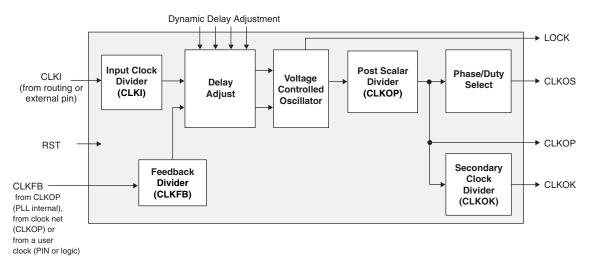

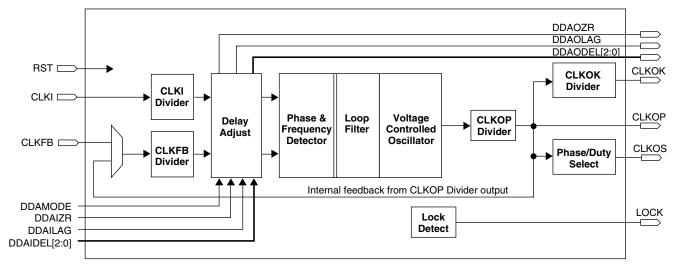

The PLL clock input, from pin or routing, feeds into an input clock divider. There are three sources of feedback signal to the feedback divider: from CLKOP (PLL Internal), from clock net (CLKOP) or from a user clock (PIN or logic). There is a PLL\_LOCK signal to indicate that VCO has locked on to the input clock signal. Figure 2-11 shows the sysCLOCK PLL diagram.

The setup and hold times of the device can be improved by programming a delay in the feedback or input path of the PLL which will advance or delay the output clock with reference to the input clock. This delay can be either pro-

# Lattice Semiconductor

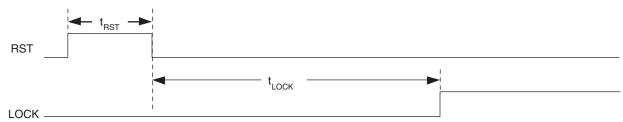

grammed during configuration or can be adjusted dynamically. In dynamic mode, the PLL may lose lock after adjustment and not relock until the t<sub>LOCK</sub> parameter has been satisfied. Additionally, the phase and duty cycle block allows the user to adjust the phase and duty cycle of the CLKOS output.

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. Each PLL has four dividers associated with it: input clock divider, feedback divider, post scalar divider and secondary clock divider. The input clock divider is used to divide the input clock signal, while the feedback divider is used to multiply the input clock signal. The post scalar divider allows the VCO to operate at higher frequencies than the clock output, thereby increasing the frequency range. The secondary divider is used to derive lower frequency outputs.

#### Figure 2-11. PLL Diagram

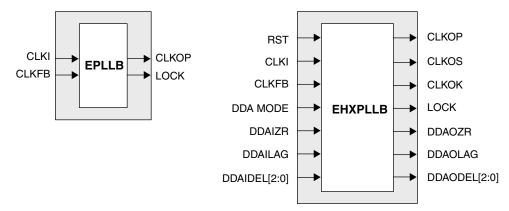

Figure 2-12 shows the available macros for the PLL. Table 2-5 provides signal description of the PLL Block.

### Figure 2-12. PLL Primitive

| Table 2-5. | PLL | Signal | Descriptions |

|------------|-----|--------|--------------|

|------------|-----|--------|--------------|

| Signal       | I/O | Description                                                                                              |

|--------------|-----|----------------------------------------------------------------------------------------------------------|

| CLKI         | I   | Clock input from external pin or routing                                                                 |

| CLKFB        | I   | PLL feedback input from CLKOP (PLL internal), from clock net (CLKOP) or from a user clock (PIN or logic) |

| RST          | I   | "1" to reset PLL                                                                                         |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)                                        |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                                                          |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                                                 |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                                                           |

| DDAMODE      | I   | Dynamic Delay Enable. "1": Pin control (dynamic), "0": Fuse Control (static)                             |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                                                      |

| DDAILAG      | I   | Dynamic Delay Lag/Lead. "1": Lead, "0": Lag                                                              |

| DDAIDEL[2:0] | I   | Dynamic Delay Input                                                                                      |

| DDAOZR       | 0   | Dynamic Delay Zero Output                                                                                |

| DDAOLAG      | 0   | Dynamic Delay Lag/Lead Output                                                                            |

| DDAODEL[2:0] | 0   | Dynamic Delay Output                                                                                     |

For more information about the PLL, please see the list of technical documentation at the end of this data sheet.

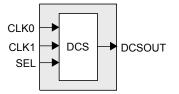

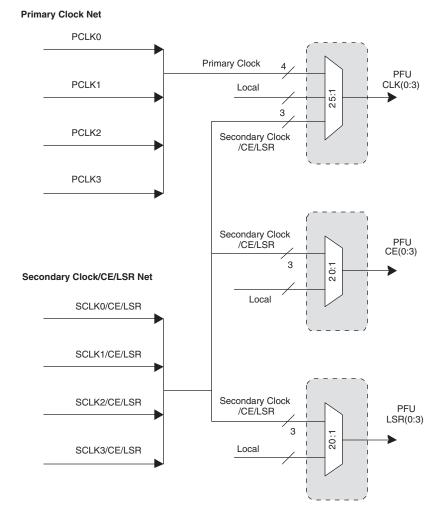

# **Dynamic Clock Select (DCS)**

The DCS is a global clock buffer with smart multiplexer functions. It takes two independent input clock sources and outputs a clock signal without any glitches or runt pulses. This is achieved regardless of where the select signal is toggled. There are eight DCS blocks per device, located in pairs at the center of each side. Figure 2-13 illustrates the DCS Block Macro.

#### Figure 2-13. DCS Block Primitive

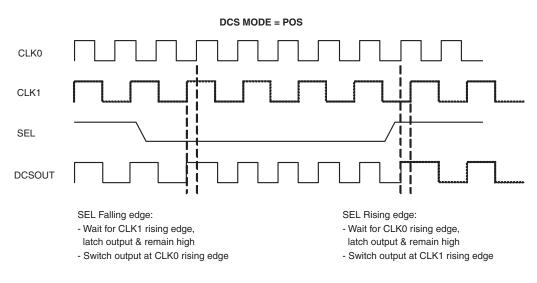

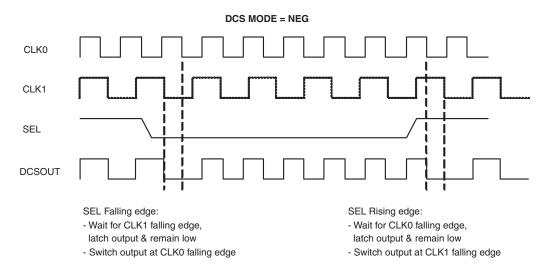

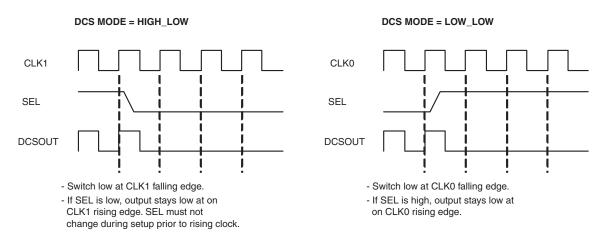

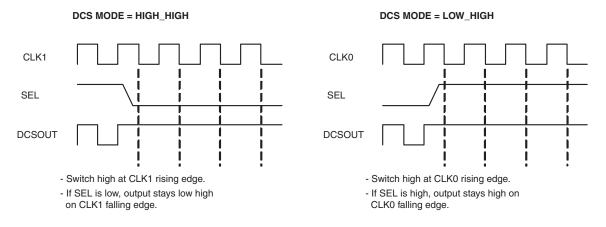

Figure 2-14 shows timing waveforms of the default DCS operating mode. The DCS block can be programmed to other modes. For more information about the DCS, please see the list of technical documentation at the end of this data sheet.

#### Figure 2-14. DCS Waveforms

# sysMEM Memory

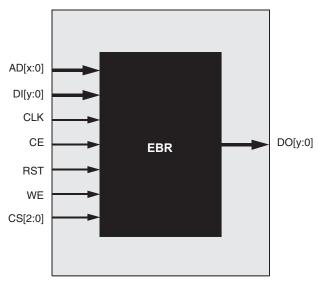

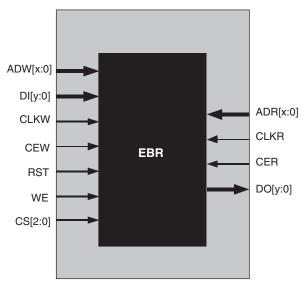

The LatticeECP/EC devices contain a number of sysMEM Embedded Block RAM (EBR). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers.

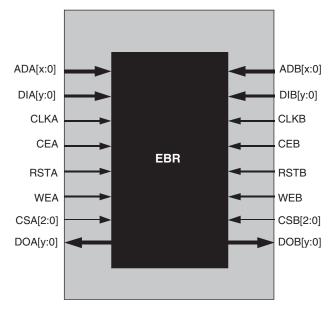

## sysMEM Memory Block

The sysMEM block can implement single port, dual port or pseudo dual port memories. Each block can be used in a variety of depths and widths as shown in Table 2-6.

#### Table 2-6. sysMEM Block Configurations

| Memory Mode      | Configurations                                                           |  |

|------------------|--------------------------------------------------------------------------|--|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |  |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |  |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |  |

# Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1 and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

# RAM Initialization and ROM Operation

If desired, the contents of the RAM can be pre-loaded during device configuration. By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

# Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

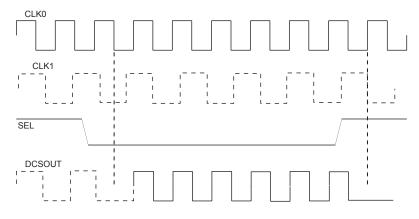

# Single, Dual and Pseudo-Dual Port Modes

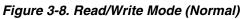

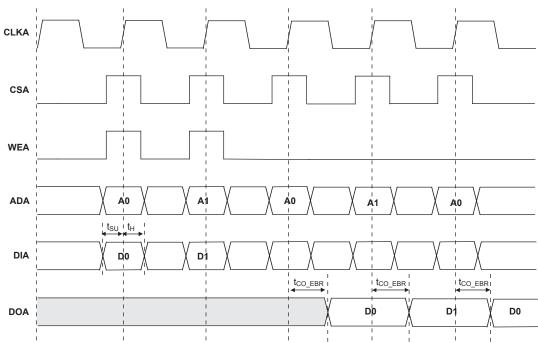

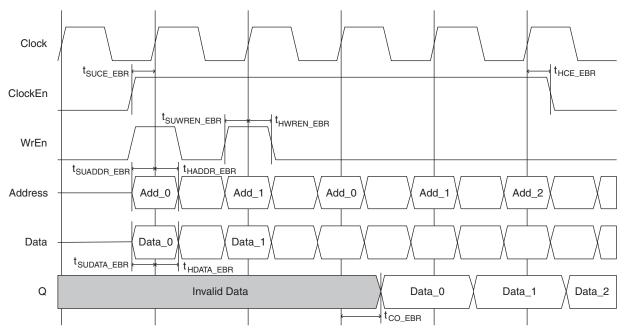

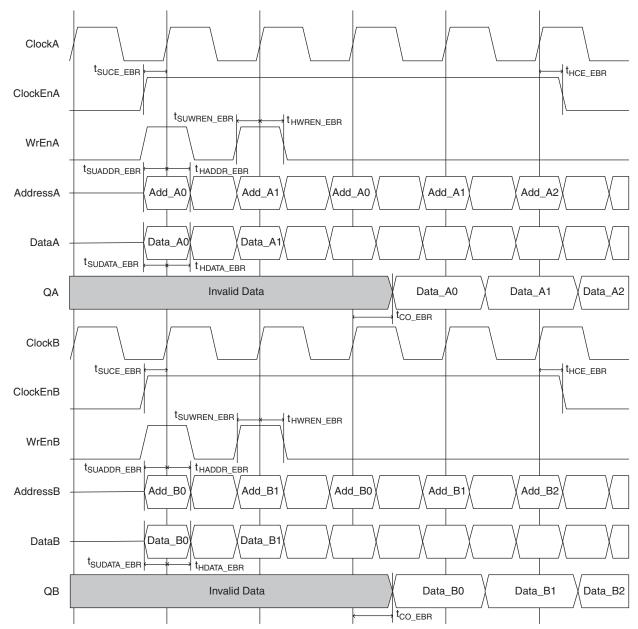

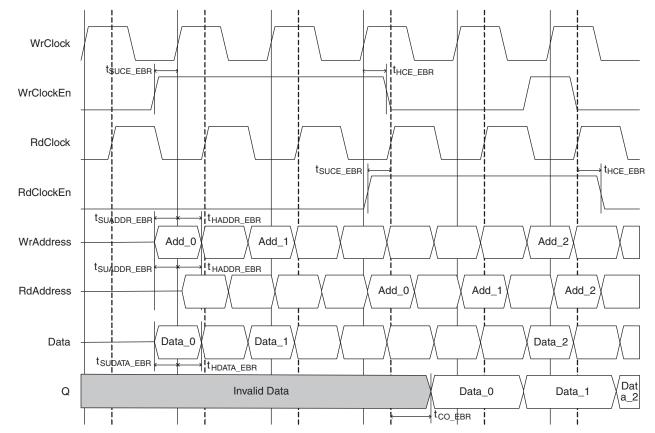

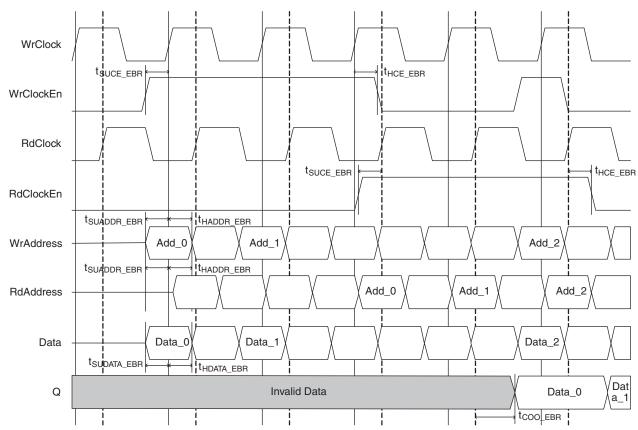

Figure 2-15 shows the four basic memory configurations and their input/output names. In all the sysMEM RAM modes the input data and address for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the output.

#### Figure 2-15. sysMEM EBR Primitives

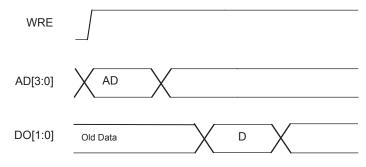

The EBR memory supports three forms of write behavior for single port or dual port operation:

- 1. **Normal** data on the output appears only during read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through a copy of the input data appears at the output of the same port during a write cycle. This mode is supported for all data widths.

- 3. **Read-Before-Write** when new data is being written, the old content of the address appears at the output. This mode is supported for x9, x18 and x36 data widths.

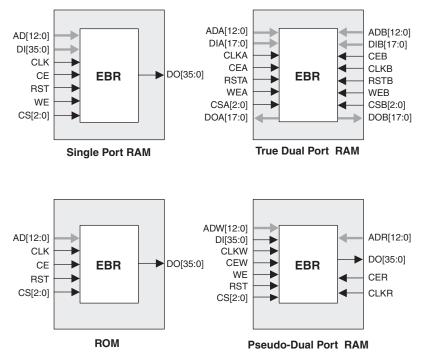

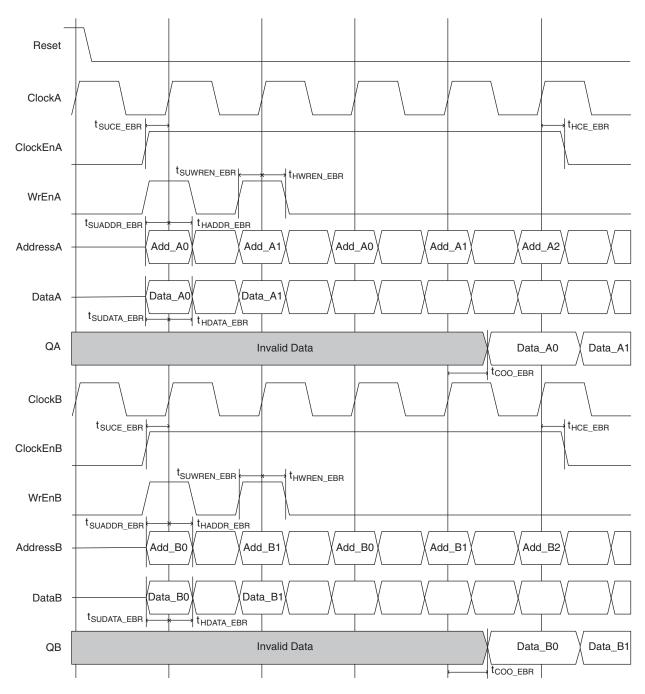

# **Memory Core Reset**

The memory array in the EBR utilizes latches at the A and B output ports. These latches can be reset asynchronously or synchronously. RSTA and RSTB are local signals, which reset the output latches associated with Port A and Port B, respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-16.

#### Figure 2-16. Memory Core Reset

For further information about sysMEM EBR block, please see the the list of technical documentation at the end of this data sheet.

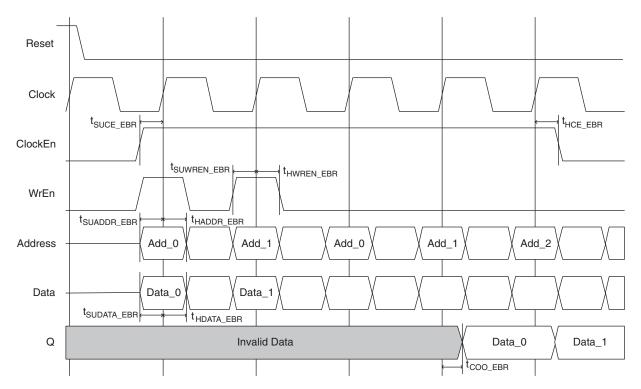

# EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-17. The GSR input to the EBR is always asynchronous.

#### Figure 2-17. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset           |  |

|-----------------|--|

| Clock           |  |

| Clock<br>Enable |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of  $1/f_{MAX}$  (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device Wake Up must occur before the release of the device I/Os becomes active.

These instructions apply to all EBR RAM and ROM implementations.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

# sysDSP Block

The LatticeECP-DSP family provides a sysDSP block, making it ideally suited for low cost, high performance Digital Signal Processing (DSP) applications. Typical functions used in these applications are Finite Impulse Response (FIR) filters; Fast Fourier Transforms (FFT) functions, correlators, Reed-Solomon/Turbo/Convolution encoders and

# Lattice Semiconductor

decoders. These complex signal processing functions use similar building blocks such as multiply-adders and multiply-accumulators.

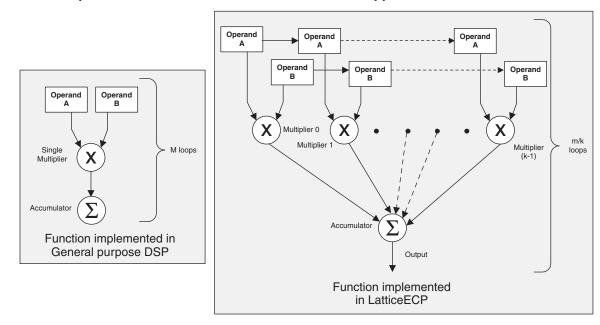

# sysDSP Block Approach Compared to General DSP

Conventional general-purpose DSP chips typically contain one to four (Multiply and Accumulate) MAC units with fixed data-width multipliers; this leads to limited parallelism and limited throughput. Their throughput is increased by higher clock speeds. The LatticeECP, on the other hand, has many DSP blocks that support different data-widths. This allows the designer to use highly parallel implementations of DSP functions. The designer can optimize the DSP performance vs. area by choosing an appropriate level of parallelism. Figure 2-18 compares the serial and the parallel implementations.

#### Figure 2-18. Comparison of General DSP and LatticeECP-DSP Approaches

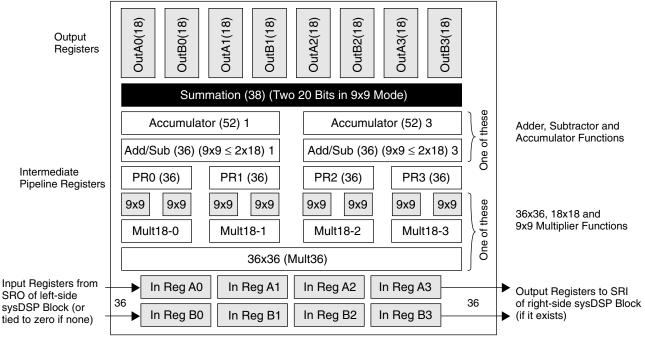

# sysDSP Block Capabilities

The sysDSP block in the LatticeECP-DSP family supports four functional elements in three 9, 18 and 36 data path widths. The user selects a function element for a DSP block and then selects the width and type (signed/unsigned) of its operands. The operands in the LatticeECP-DSP family sysDSP Blocks can be either signed or unsigned but not mixed within a function element. Similarly, the operand widths cannot be mixed within a block.

The resources in each sysDSP block can be configured to support the following four elements:

| <ul> <li>MULT</li> </ul> | (Multiply) |

|--------------------------|------------|

|--------------------------|------------|

- MAC (Multiply, Accumulate)

- MULTADD (Multiply, Addition/Subtraction)

- MULTADDSUM (Multiply, Addition/Subtraction, Accumulate)

The number of elements available in each block depends on the width selected from the three available options x9, x18, and x36. A number of these elements are concatenated for highly parallel implementations of DSP functions. Table 2-1 shows the capabilities of the block.

| Width of Multiply | x9 | x18 | x36 |

|-------------------|----|-----|-----|

| MULT              | 8  | 4   | 1   |

| MAC               | 2  | 2   | —   |

| MULTADD           | 4  | 2   | —   |

| MULTADDSUM        | 2  | 1   | —   |

Some options are available in four elements. The input register in all the elements can be directly loaded or can be loaded as shift registers from previous operand registers. In addition by selecting "dynamic operation" in the 'Signed/Unsigned' options the operands can be switched between signed and unsigned on every cycle. Similarly by selecting 'Dynamic operation' in the 'Add/Sub' option the Accumulator can be switched between addition and subtraction on every cycle.

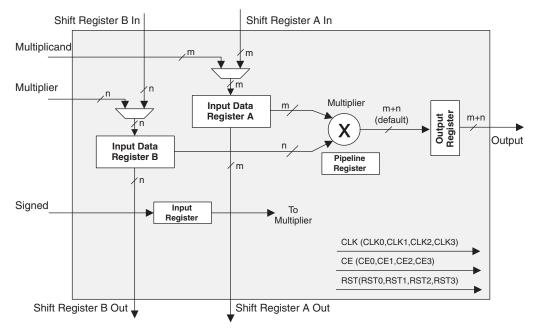

### **MULT sysDSP Element**

This multiplier element implements a multiply with no addition or accumulator nodes. The two operands, A and B, are multiplied and the result is available at the output. The user can enable the input/output and pipeline registers. Figure 2-19 shows the MULT sysDSP element.

#### Figure 2-19. MULT sysDSP Element

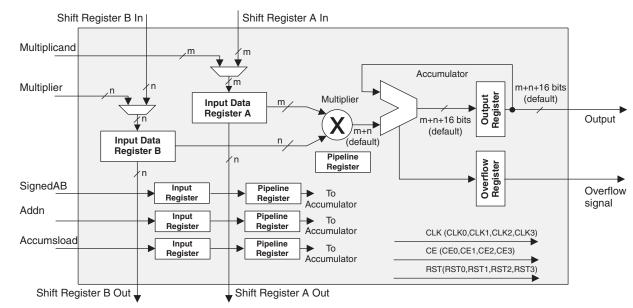

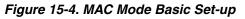

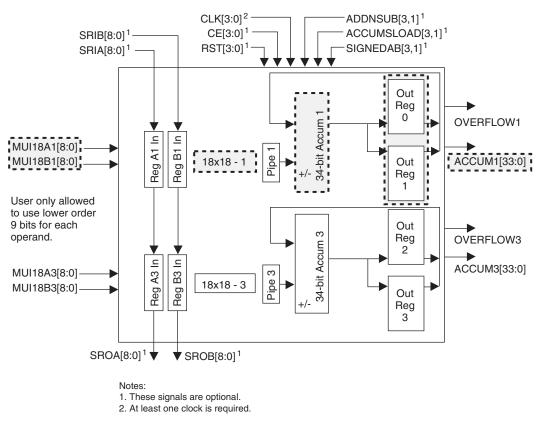

# MAC sysDSP Element

In this case the two operands, A and B, are multiplied and the result is added with the previous accumulated value. This accumulated value is available at the output. The user can enable the input and pipeline registers but the output register is always enabled. The output register is used to store the accumulated value. A registered overflow signal is also available. The overflow conditions are provided later in this document. Figure 2-20 shows the MAC sysDSP element.

#### Figure 2-20. MAC sysDSP Element

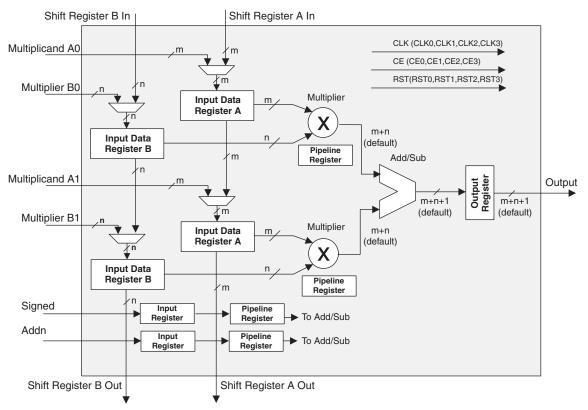

# **MULTADD sysDSP Element**

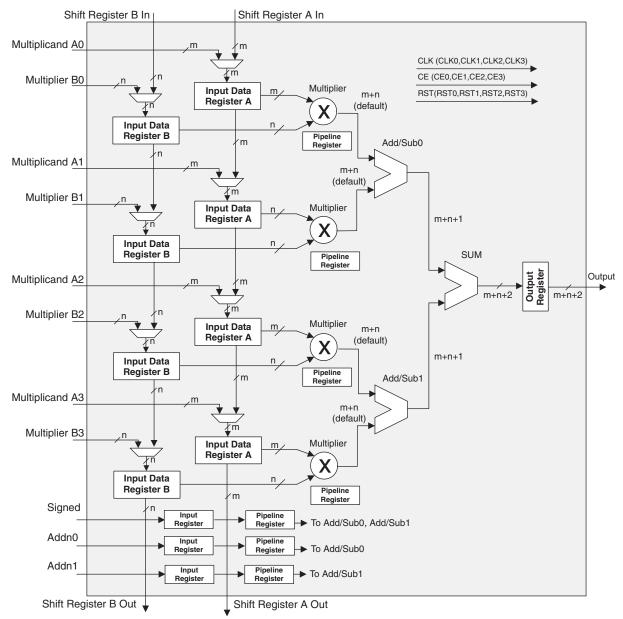

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and A2. The user can enable the input, output and pipeline registers. Figure 2-21 shows the MULTADD sysDSP element.

#### Figure 2-21. MULTADD

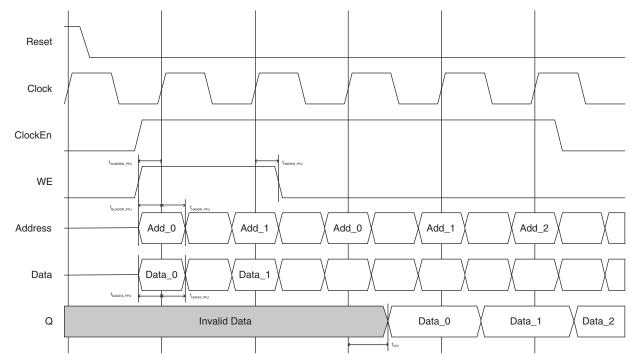

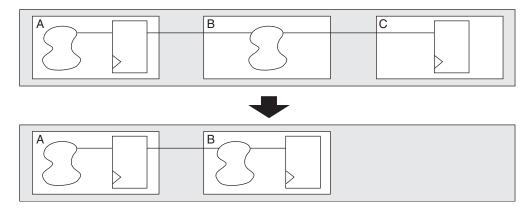

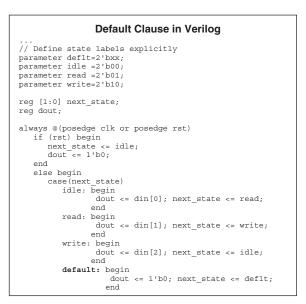

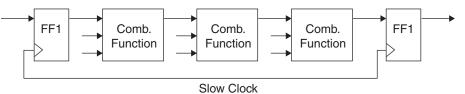

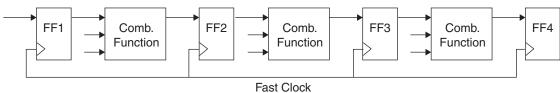

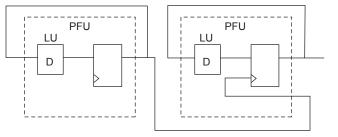

# MULTADDSUM sysDSP Element