# Preliminary Specification

#### DESCRIPTION

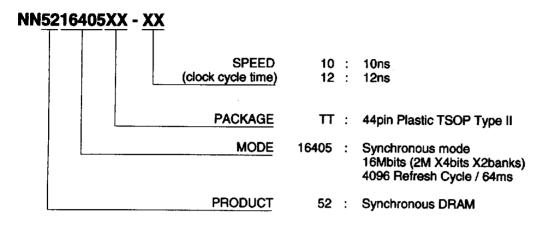

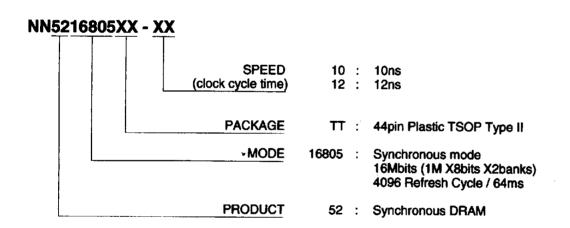

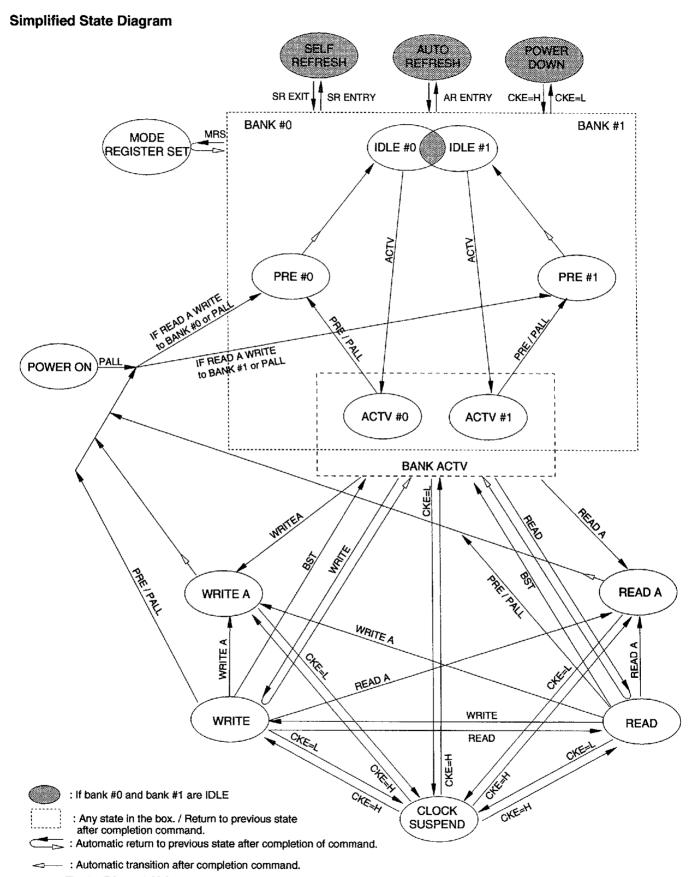

This product is a CMOS Synchronous Dynamic Random Access Memory (SDRAM) organized as 2,097,152 words x4bits x 2banks (NN5216405).1,048,576 words x8bits x 2banks (NN5216805)

This product features a fully synchronous operation referenced to a positive edge of clock input. The read/write operation can be performed in burst mode where data is transferred in either a 2, 4, 8 words or full page (1,024 (NN5216405) / 512 (NN5216805) words) burst accesses, using a two bank architecture, and allows continual read/write operation.

Refresh is accomplished by Auto refresh or Self refresh.

This product is available in 44-pin plastic TSOP TYPE II.

All inputs and outputs are compatible with Low Voltage TTL (LVTTL).

## **FEATURES**

- Organization

- 1,048,576words x8bits x2banks (NN5216805) 2,097,152 words x4bits x 2banks (NN5216405)

- Single 3.3V ±0.3V Power Supply

- Performance Ranges

| Paran                        | neter               | -10  | -12   |

|------------------------------|---------------------|------|-------|

| Min. Clock Cycle             | Time                |      |       |

| (tCK)                        | CL=3                | 10ns | 12ns  |

|                              | CL=2                | 15ns | 18ns  |

|                              | CL=1                | 30ns | 36ns  |

| Max. RAS Acces               | s Time <sup>2</sup> |      |       |

| (tRCD+tACK)                  | CL=3                | 57ns | 63ns  |

| ,                            | CL=2                | 54ns | 60ns  |

|                              | CL=1                | 55ns | 60ns  |

| Max. Read Com                | mand                |      |       |

| Access Time                  | CL=3                | 27ns | 33ns  |

| (tACK)                       | CL=2                | 24ns | 30ns  |

|                              | CL=1                | 25ns | 30ns  |

| Max. CLK Acces               | s Time              |      |       |

| (tAC)                        | CL=3                | 7ns  | 9ns   |

|                              | CL=2                | 9ns  | 12ns  |

|                              | CL=1                | 25ns | 30ns  |

| Max. Active Con              |                     |      |       |

| Cycle Time <sup>1</sup> (tRC | C)                  | 90ns | 108ns |

NOTE:

1. Same bank

2. Clock cycle = tCK

- Single Pulsed RAS

- 2 Bank Operation (simultaneously and independently)

- Read/Write Operation Type

- Burst Read / Write Operation

- Burst Read / Single Write Operation

- Programmable Burst Sequence

- Sequential

- Interleaved

- Programmable Burst Length (1, 2, 4, 8, and Full Page)

- Full Page Burst Stop Capability

- Programmable CAS Latency (1, 2, and 3)

- Fully LVTTL compatible Inputs/Outputs and Clock

- 4,096 Refresh Cycles / 64ms

- Refresh Modes

Auto Refresh

Self Refresh

- High Reliability Package

Plastic 44pin TSOP TYPE II (P44TP-3B-L)

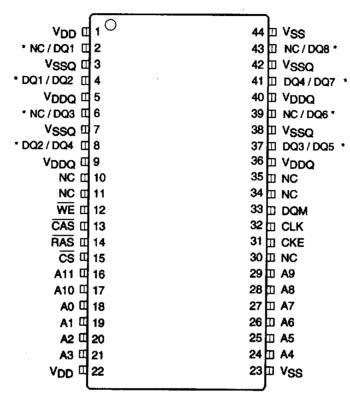

## **PIN CONFIGURATION (TOP VIEW)**

\* NOTE: NN5216405/NN5216805

44-pin TSOP TYPE ( II )(400mil) P44TP-3B-L

## **PIN NAMES**

| A0 - A11               | Address Input Row Address :A0 - A10 Column Address :A0 - A8 | DQM              | Input / Output Mask                                           |

|------------------------|-------------------------------------------------------------|------------------|---------------------------------------------------------------|

|                        | Bank Select Address :A11                                    | CLK              | Clock Input                                                   |

|                        |                                                             | CKE              | Clock Enable                                                  |

| DQ1 - DQ4<br>DQ1 - DQ8 | Data Input/Output (NN5216405) (NN5216805)                   | V <sub>DD</sub>  | Power Supply (for Internal Circuit)                           |

| CS                     | Chip Select V <sub>DDQ</sub>                                |                  | Power Supply (for DQ Buffer)<br>Isolated from V <sub>DD</sub> |

| RAS                    | Row Address Strobe                                          | V <sub>SS</sub>  | Ground (for Internal Circuit)                                 |

| CAS                    | Column Address Strobe                                       | V <sub>SSQ</sub> | Ground(for DQ Buffer) Isolated from V <sub>SS</sub>           |

| WE                     | Write Enable                                                | NC               | No Connection                                                 |

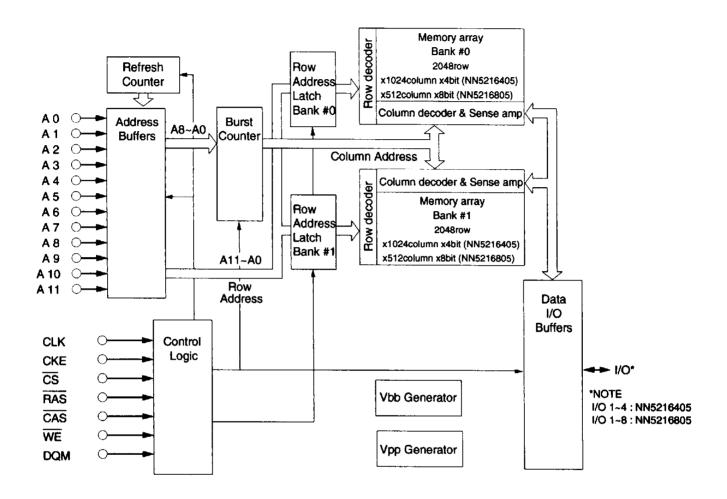

#### **FUNCTIONAL BLOCK DIAGRAM**

## **PIN FUNCTIONS**

| CLK                      | input            | CLK is the master clock. All inputs and data out are referenced to positive edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                       | input            | When CS is low, the device starts a command input cycle on rising edge of CLK; if CS is high, all new commands are ignored but internal operations are continued.                                                                                                                                                                                                                                                                                                                                                        |

| RAS<br>CAS<br>WE         | input            | RAS, CAS and WE have the same signal name with conventional DRAMs but different functions. Most of the commands are defined by these pins.                                                                                                                                                                                                                                                                                                                                                                               |

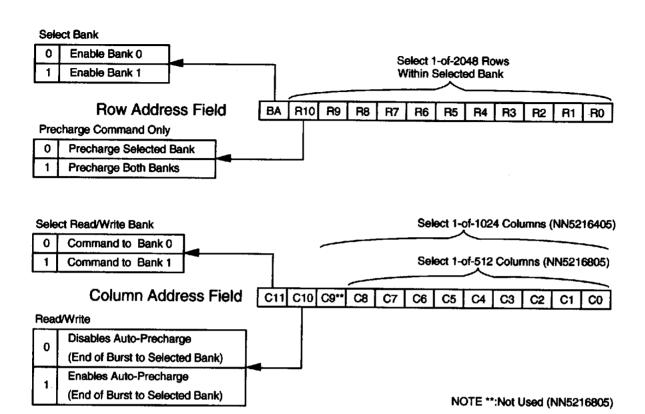

| A0 - A11                 | input            | Row Address is determined by A0-A10 in the active command cycle.  Column Address is determined by A0-*A9/A8 in the read or write command cycle.  Bank Address is determined by A11.  During a read or write command cycle, A10 determines if auto-precharge is enabled or disabled.  During a precharge command cycle, A10 determines if only the selected bank is precharged or if both banks are precharged. A0-A9 are used to select operating modes during a mode register set command.                              |

| CKE                      | input            | CKE determines the device operation of next clock(CLK) cycle. If CKE is high, device is active at the next clock cycle. If CKE is low, the internal clock is suspended and device is not active at the next clock cycle. When in the Idle mode and CKE goes low, the device enters power down mode. To remain in power down mode, CKE must be kept at a low level.  When at least one bank is active and CKE goes low, the device enters clock suspend mode.                                                             |

| DQM                      | input            | These pins control Input/Output buffers.  During read mode cycle, DQM controls the output buffers. If DQM is high during a read cycle, the associated output buffers assume a high impedance state two clock cycles later.  Likewise, if DQM is low during a read cycle, the associated output buffers are enabled (low impedance) two cycles later.  DQM control the output impedance state of DQ1 through *DQ4/DQ8.  In write mode cycles, DQM perform as a write mask. If DQM is high, the input data is not written. |

| DQ                       | input<br>/output | These pins are the data input/output lines of SDRAM. DQ0 - DQ3 : NN5216405 DQ0 - DQ7 : NN5216805                                                                                                                                                                                                                                                                                                                                                                                                                         |

| / <sub>DD</sub><br>/ss   | power<br>supply  | VDD and VSS are power supply pins for internal circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| / <sub>DDQ</sub><br>/ssq | power<br>supply  | V <sub>DDQ</sub> and V <sub>SSQ</sub> are power supply pins for output buffers. V <sub>DDQ</sub> and V <sub>SSQ</sub> are isolated from V <sub>DD</sub> and V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                            |

\*NOTE: NN5216405 / NN5216805

## **EXPLANATION OF COMMANDS**

|                              | Mode Register Set                                                                                                                                                               | CS, RAS, CAS, WE = Low , A0-A11 = OP-Code                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The                          | de register defines how the device of default value of the mode register mode register before any other cor                                                                     | operates. A0-A11 are operation codes (OP-Codes) in this cycle.  r after power-on is undefined. Therefore, this command must be executed to set mmands are executed.                                                                                                                                                                                                                                                                        |

| 2                            | Bank Active                                                                                                                                                                     | CS, RAS = Low, CAS, WE = High, A11 = Bank, A0-A10 = Row Address                                                                                                                                                                                                                                                                                                                                                                            |

| omn                          | Active command activates a bank<br>nand and the cell data is read out to<br>entional DRAM's.                                                                                    | selected by A11. Row addresses are latched on A0 to A10 at the time of this the sense amplifiers. This command corresponds to RAS going low on                                                                                                                                                                                                                                                                                             |

| 3                            | Read                                                                                                                                                                            | CS, CAS = Low , RAS, WE = High , A11 = Bank , A10 = Low A0-*A9/A8 = Column Address                                                                                                                                                                                                                                                                                                                                                         |

|                              | st start address is given by A0-*A9/                                                                                                                                            | peration to the bank selected by A11.<br>A8 (column address). After a read burst has completed, the output buffers becom                                                                                                                                                                                                                                                                                                                   |

| 4                            | Read with Auto-Precharge                                                                                                                                                        | CS, CAS = Low , RAS, WE = High , A11 = Bank , A10 = High A0-*A9/A8=Column Address                                                                                                                                                                                                                                                                                                                                                          |

| Rea<br>oper                  | d with Auto-Precharge command in ration. When the burst length is full                                                                                                          | nitiates an automatic precharge operation after the completion of a read burst page, this command is illegal.                                                                                                                                                                                                                                                                                                                              |

| •                            |                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5                            | Write                                                                                                                                                                           | CS, CAS, WE = Low , RAS = High , A11 = Bank , A10 = Low A0-*A9/A8 = Column Address                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>Write<br>Burs<br>Whe    | e command initiates a burst write o<br>st start address is given by A0-*A9/<br>en the single write mode (WT=1 in N                                                              | CS, CAS, WE = Low , RAS = High , A11 = Bank , A10 = Low A0-*A9/A8 = Column Address  peration to the bank selected by A11.                                                                                                                                                                                                                                                                                                                  |

| 5<br>Write<br>Burs<br>Whe    | e command initiates a burst write o<br>st start address is given by A0-*A9/<br>en the single write mode (WT=1 in N                                                              | CS, CAS, WE = Low , RAS = High , A11 = Bank , A10 = Low A0-*A9/A8 = Column Address  peration to the bank selected by A11.  A8 (column address).  Mode Register), this command initiates a single write operation to the selected                                                                                                                                                                                                           |

| Write<br>Burs<br>Whe<br>ank. | e command initiates a burst write of st start address is given by A0-*A9/, on the single write mode (WT=1 in No. In this case data is only written to Write with Auto-Precharge | CS, CAS, WE = Low , RAS = High , A11 = Bank , A10 = Low A0-*A9/A8 = Column Address  peration to the bank selected by A11.  A8 (column address).  Mode Register), this command initiates a single write operation to the selected the location specified by A0-*A9/A8.  CS, CAS, WE = Low , RAS = High , A11 = Bank , A10 = High A0-*A9/A8 = Column Address  itiates an automatic precharge operation after the completion of a write burst |

\*NOTE: NN5216405 / NN5216805

## **EXPLANATION OF COMMANDS (cont.)**

| 8             | Precharge All Bank                                                           | $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{WE}}$ = Low , $\overline{\text{CAS}}$ = High , A10 = High , A0-A9 / A11 = Don't care                                                                                                                                          |

|---------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | narge All Banks command precharg banks are switched to the idle state        | •                                                                                                                                                                                                                                                                                                 |

| 9             | Auto Refresh                                                                 | CS, RAS, CAS = Low, WE = High, A0-A11 = Don't care, CKE = High                                                                                                                                                                                                                                    |

| conv          | entional DRAMs. Row addresses a rmed 4096 times within 64ms. Befo            | resh operation. Auto-refresh is the same as CAS-before-RAS refresh on re generated by internal refresh counter. The refresh operation must be re executing auto refresh, the device must be in the Idle state. Not necessary. Precharge operation starts automatically after a refresh operation. |

| 10            | Burst Stop                                                                   | CS, WE = Low , RAS, CAS = High , A0-A11 = Don't care                                                                                                                                                                                                                                              |

|               | t Stop command stops full page burs<br>st mode is not full page, this comma  | st operation. Full page burst continues until this command is issued. and is ignored.                                                                                                                                                                                                             |

| 11            | Enter Self-Refresh                                                           | CKE = Low , $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ = Low , $\overline{\text{WE}}$ = High , A0-A11 = Don't care                                                                                                                                                |

| While<br>oper | •                                                                            | operation is maintained as long as CKE stays low.  peration is automatically performed, so there is no need to control refresh  self-Refresh command.                                                                                                                                             |

| 12            | Exit Self-Refresh                                                            | CKE = High, $\overline{CS}$ = Low, $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ = High or $\overline{CS}$ = High                                                                                                                                                                         |

|               | Self-Refresh command is used to exiting from self refresh mode, both         |                                                                                                                                                                                                                                                                                                   |

| 13            | No Operation                                                                 | CS = Low , FAS, CAS, WE = High , A0-A9 = Don't care                                                                                                                                                                                                                                               |

| No C          | Operation command initiates nothing                                          | . This command is similar to Device Deselect command.                                                                                                                                                                                                                                             |

| 14            | Device Deselect                                                              | CS = High , RAS, CAS, WE, A0-A11 = Don't care                                                                                                                                                                                                                                                     |

|               | on Device Deselect command is ex<br>command is similar to No Operation       | ecuted, the RAS, CAS, WE and address input are ignored. n command.                                                                                                                                                                                                                                |

| 15            | Enter Power Down                                                             | CKE = Low                                                                                                                                                                                                                                                                                         |

|               | on both banks are in the idle state, E<br>e power down mode, all input and c | inter Power Down command switches device into the power down mode.                                                                                                                                                                                                                                |

| 16            | Exit Power Down                                                              | CKE = High , $\overline{\text{CS}}$ = Low , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ = High or CKE, $\overline{\text{CS}}$ = High                                                                                                                               |

|               | Power Down command is used to e<br>r exiting this mode, both banks are i     | ·                                                                                                                                                                                                                                                                                                 |

## **EXPLANATION OF COMMANDS (cont.)**

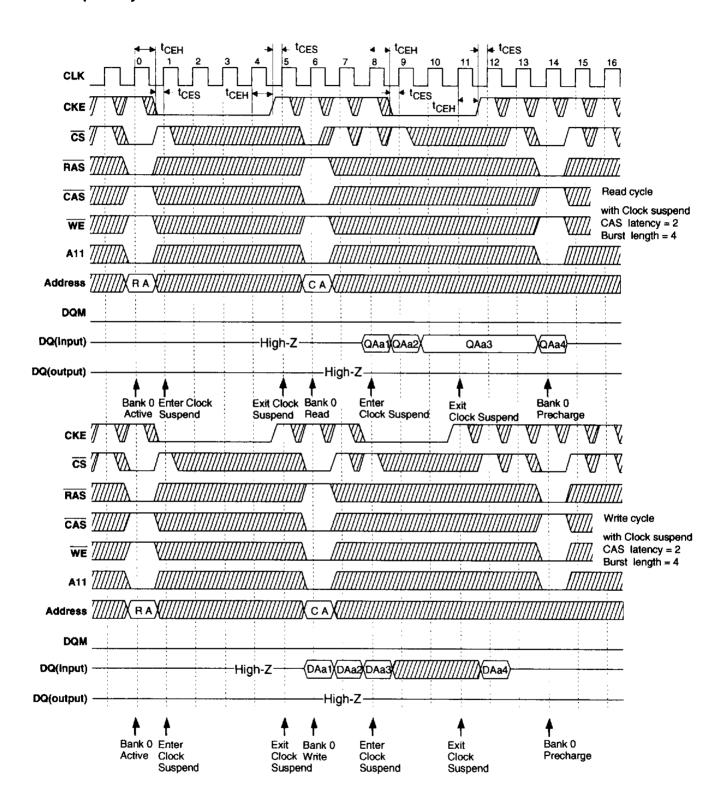

|     | Enter Clock Suspend                                                 | CKE = Low                                                                                                                                                            |

|-----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Whe | n either bank is in the active st<br>device operation is held while | ate, Enter Clock Suspend command switches device into the clock suspend mode. CLK is low.                                                                            |

| 18  | Exit Clock Suspend                                                  | CKE = High, $\overline{\text{CS}}$ = Low , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ = High , or CKE, $\overline{\text{CS}}$ = High |

#### **COMMAND OPERATION**

#### **Simplified Functional Truth Table**

|    | Function                       | Command | Ck<br>(n-1) | Œ<br>(n)       | cs | RAS | CAS | WE | DQM              | A11 | A10  | <b>A</b> 9 | <b>A8-A</b> 0 |

|----|--------------------------------|---------|-------------|----------------|----|-----|-----|----|------------------|-----|------|------------|---------------|

| 1  | Mode Register Set <sup>4</sup> | MRS     | Н           | X <sup>5</sup> | L  | L   | L   | L  | Х                |     | — Op | -Code -    | <b>→</b>      |

| 9  | Auto-Refresh<br>(CBR-Refresh)  | REF     | Н           | H              | L  | L   | L   | Н  | Х                | Х   | Х    | Х          | Х             |

| 11 | Enter Self-Refresh             | SELF    | Н           | L6             | L  | L   | L   | Н  | Х                | Х   | Х    | Х          | Х             |

| 12 | Exit Self-Refresh              | XSELF   | L           | Н              | L  | Н   | Н   | Н  | Х                | Х   | Х    | Х          | Х             |

|    |                                |         | L           | Н              | Н  | Х   | Х   | Х  | Х                | Х   | Х    | Х          | Х             |

| 2  | Bank Active                    | ACTV    | Н           | χ5             | L  | L   | Н   | Н  | Х                | BA  | -    | - Row      |               |

| 3  | Read                           | READ    | Н           | χ5             | L  | Н   | L   | Н  | H/L <sup>1</sup> | BA  | L    | *Col/X     | Col           |

| 4  | Read with Auto-Precharge       | READA   | Н           | χ5             | L  | Н   | L   | Н  | H/L <sup>1</sup> | BA  | Н    | *Col/X     | Col           |

| 10 | Burst Stop                     | BST     | Н           | χ5             | L  | Н   | Н   | L  | Х                | Х   | Х    | Х          | Х             |

| 5  | Write                          | WRITE   | Н           | χ5             | L  | Н   | L   | L  | H/L <sup>2</sup> | ВА  | L    | *Col/X     | Col           |

| 6  | Write with Auto-Precharge      | WRITEA  | Н           | X <sup>5</sup> | L  | Н   | L   | L  | H/L <sup>2</sup> | ВА  | Н    | *Col/X     | Col           |

| 7  | Single Bank Precharge          | PRE     | Н           | X <sup>5</sup> | L  | L   | Н   | L  | Х                | ВА  | L    | Х          | X             |

| 8  | Precharge All Banks            | PALL    | Н           | X <sup>5</sup> | L  | L   | Н   | L  | Х                | Х   | Н    | Х          | X             |

| 13 | No Operation                   | NOP     | Н           | X <sup>5</sup> | L  | Н   | Н   | н  | Х                | Х   | Х    | Х          | Х             |

| 14 | Device Deselect                | DESEL   | Н           | X <sup>5</sup> | Н  | Х   | Х   | Х  | Х                | Х   | Х    | Х          | Х             |

| 15 | Clock Suspend                  | CLKS    | L           | L <sup>6</sup> | Х  | Х   | Х   | Х  | Х                | Х   | Х    | Х          | Х             |

| 17 | Power Down                     | PD      |             |                |    |     |     |    |                  |     |      |            |               |

| 16 | Exit Clock Suspend             | XCLKS   | L           | Н              | L  | Н   | Н   | Н  | Х                | Х   | Х    | Х          | Х             |

| 18 | Power Down                     | XPD     | L           | Н              | Н  | Х   | Х   | Х  | Х                | Х   | Х    | Х          | Х             |

\*NOTE: NN5216405 / NN5216805

#### Notes:

- 1. Operation depends on the state of DQM;

- if DQM=H, then the associated output is High-Z after 2 clock latency and if DQM=L then the associated output is Low-Z after 2 clock latency.

- 2. Operation depends on the state of DQM;

- if DQM=H, then the associated byte is not written

- but if DQM=L, then the associated byte data is written.

- 3. Device that has one or more banks active will enter "Clock Suspend" and device that has all banks "Idle" will enter "Power Down".

- 4. Banks do not have to be in "Idle" state to execute these commands, but read or write operations simultaneously with these commands are prohibited.

- 5. If CKE=L, then a "Clock Suspend" or "Power Down" will occur on next clock cycle.

- 6. CKE(n) must remain low in order to remain in "Clock Suspend" or in "Power Down" mode. When in "Power Down" mode, exiting occurs when CKE(n) goes high, but "NOP" must be executed during exiting. When in "Clock Suspend", CKE(n) going high exits "Clock Suspend" mode and normal operation will be resumed on the next clock.

#### **ROW/COLUMN ADDRESS FIELDS**

## **FUNCTIONAL TRUTH TABLE**

| Current State | CS  | RAS          | CAS | WE         | Command      | Address                  | Action                                | Note                                             |

|---------------|-----|--------------|-----|------------|--------------|--------------------------|---------------------------------------|--------------------------------------------------|

| ldle          | Н   | X            | Х   | Х          | DESEL        | X                        | NOP                                   |                                                  |

|               | L   | Н            | н   | Н          | NOP          | X                        | NOP                                   |                                                  |

|               | L   | н            | Н   | L          | BST          | X                        | ILLEGAL                               | 2                                                |

|               | L   | н            | L   | н          | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                               | 2                                                |

|               | L   | н            | L   | L          | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                               | 2                                                |

|               | L   | L            | Н   | н          | ACTV         | RA11(BA),RA10            | Bank Active, RA Latch                 |                                                  |

|               | L   | L            | Н   | L          | PRE          | RA11(BA),RA10            | NOP                                   |                                                  |

|               | ī   | _            | L   | Н          | REF          | X                        | Auto-Refresh                          |                                                  |

|               | ī   | _            | ן ב | L          | MRS          | OP-code                  | Mode Register Set                     |                                                  |

|               | LIN | _<br>IDEFINI | Ţ   | -          | INIT 13      | OF-Code                  | ILLEGAL                               |                                                  |

| Row Active    | H   | X            | X   | X          | DESEL        | X                        | NOP                                   |                                                  |

| HOW ACTIVE    |     | 1            |     |            |              |                          | 1                                     |                                                  |

|               | L   | H            | H   | H          | NOP          | X                        | NOP                                   | İ                                                |

|               | L   | H            | H   | L          | BST          | X                        | NOP                                   |                                                  |

|               | L   | l H          | L   | Н          | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | Begin Read,Latch CA,Determine AP      | İ                                                |

|               | L   | H            | L   | L          | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | Begin Write,Latch CA,Determine AP     |                                                  |

|               | L   | L            | H   | Н          | ACTV         | RA11(BA),RA10            | ILLEGAL                               | 1                                                |

|               | L   | L            | Н   | L          | PRE          | RA11(BA),RA10            | Precharge                             |                                                  |

|               | L   | L            | L   | н          | REF          | X                        | ILLEGAL                               |                                                  |

|               | L L | L            | L   | L          | MRS          | OP-code                  | Mode Register Set**                   | -                                                |

|               | Ur  | DEFIN        | ĖD  | ' <u>-</u> | -            |                          | ILLEGAL                               |                                                  |

| Read          | Н   | X            | X   | X          | DESEL        | Х                        | NOP(Continue Burst,                   | <del>                                     </del> |

|               |     | 1            |     | ''         |              |                          | Bank remains Active)                  |                                                  |

|               | L   | Н            | H   | н          | NOP          | x                        | NOP(Continue Burst,                   |                                                  |

|               | -   | ''           | ''  | ''         | 1101         | ^                        | Bank remains Active)                  |                                                  |

|               | ١.  | Н            | Н   | 1 .        | BST          | x                        | 1                                     |                                                  |

|               | L   | "            | "   | L          | 1001         | ^                        | NOP (Bank remains Active)             |                                                  |

|               |     |              | ŀ   | 1          |              |                          | BL≠FP:Continue Burst                  |                                                  |

|               |     | 1            |     | l          |              |                          | BL=FP:Term Burst)                     |                                                  |

|               | L   | Н            | L   | H          | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | Term Burst,New Read,Determine AP      | 1                                                |

|               | L   | H            | L   | L          | WRITEWRITEA  | CA11(BA),CA10,*CA9/8-CA0 | Term Burst,Start Write,Determine AP   | ļ                                                |

|               | L   | L            | H   | Н          | ACTV         | RA11(BA),RA10            | ILLEGAL                               |                                                  |

|               | L   | L            | н   | L          | PRE          | RA11(BA),RA10            | Term Burst,Precharge Timing for Read  |                                                  |

|               | L   | L            | L   | н          | REF          | x                        | ILLEGAL                               |                                                  |

|               | L   | L            | L   | L          | MRS          | OP-code                  | ILLEGAL                               |                                                  |

|               | U   | NDEFIN       | ĖD  | ٠ -        | -            |                          | ILLEGAL                               |                                                  |

| Write         | Н   | TX           | X   | X          | DESEL        | Х                        | NOP(Continue Burst                    | +                                                |

|               |     |              |     |            |              |                          | Bank remains Active)                  |                                                  |

|               | L   | Н            | н   | н          | NOP          | x                        | NOP(Continue Burst                    |                                                  |

|               | _   | ''           | ''  | 1          | 1101         | <u> </u>                 | Bank remains Active)                  |                                                  |

|               | L   | Н            | Н   | L          | DCT          | x                        | ,                                     |                                                  |

|               | -   | "            | "   | -          | BST          | ^                        | NOP(Bank remains Active               |                                                  |

|               |     |              |     |            |              |                          | BL≠FP:Continue Burst                  |                                                  |

|               |     |              |     |            |              |                          | BL=FP:Term Burst)                     |                                                  |

|               | L   | H            | L   | H          | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | Term Burst,Start Read,Determine AP    |                                                  |

|               | L   | ) н          | L   | L          | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | Term Burst, New Write, Determine AP   |                                                  |

|               | L   | L            | н   | н          | ACTV         | RA11(BA),RA10            | ILLEGAL                               |                                                  |

|               | L   | L            | н   | L          | PRE          | RA11(BA),RA10            | Term Burst, Precharge Timing for Read |                                                  |

|               | L   | L            | L   | н          | REF          | x                        | ILLEGAL                               |                                                  |

|               | L   | L            | L   | L          | MRS          | OP-code                  | ILLEGAL                               |                                                  |

|               |     |              |     |            |              |                          |                                       | - 1                                              |

\*NOTE: NN5216405 / NN5216805

## **FUNCTIONAL TRUTH TABLE (cont.)**

| Current State  | CS  | RAS           | CAS      | WE | Command      | Address                  | Action                          | Note |

|----------------|-----|---------------|----------|----|--------------|--------------------------|---------------------------------|------|

| Read With      | Н   | X             | Х        | Х  | DESEL        | X                        | NOP(Continue Burst to End       | +    |

| Auto Precharge |     | 1             |          |    | 1            |                          | Then Precharge)                 |      |

|                | L   | Н             | Н        | Н  | NOP          | x                        | NOP(Continue Burst to End       |      |

|                |     |               |          | ĺ  |              |                          | Then Precharge)                 |      |

|                | L   | Н             | Н        | ٠L | BST          | X                        | ILLEGAL                         |      |

|                | L   | н             | L        | Н  | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 |                                 |      |

|                | L   | Н             | L        | L  | WRITE/WRITEA |                          |                                 |      |

|                | L   | L             | н        | H  | ACTV         | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | L   | L             | н        | L  | PRE          | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | L   | L             | L        | Н  | REF          | x                        | ILLEGAL                         | ~    |

|                | L   | L             | L        | L  | MRS          | OP-code                  | ILLEGAL                         |      |

|                | UN  | DEFINE        | D '      | •  | _            |                          | ILLEGAL                         |      |

| Write With     | Н   | Х             | x        | X  | DESEL        | X                        | NOP(Continue Burst to End       |      |

| Auto Precharge |     |               |          |    |              | <b> </b> ^               | Then Precharge)                 | }    |

| 3.             | L   | н             | н        | Н  | NOP          | x                        | NOP(Continue Burst to End       |      |

|                |     |               | · · · ·  | •• |              | ^                        | 1                               |      |

|                | L   | н             | н        | L  | вет          | x                        | Then Precharge)                 |      |

|                | L   | н             | <u>"</u> | Н  | READ/READA   |                          | ILLEGAL                         |      |

|                | _   | н             | L        | L  | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 |                                 |      |

|                | ב l | L             | н        | Н  | ACTV         | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         | 1 _  |

|                | ו ו | L             | н        |    | ŀ            | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | -   | -             | ŀ        | L  | PRE          | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | -   | -             | L        | Н  | REF          | X                        | ILLEGAL                         |      |

| ĺ              | - I | ا ا<br>DEFINE | <u> </u> | L  | MRS          | OP-code                  | ILLEGAL                         |      |

| Precharging    | H   | X             |          |    | -<br>DE051   |                          | ILLEGAL                         |      |

| Frechaiging    | ļ   |               | X        | X  | DESEL        | X                        | NOP, Idle after tPR             |      |

|                | . i | H             | Н        | H  | NOP          | X                        | NOP, Idle after t <sub>PR</sub> | 1    |

|                | 1   | H             | Н        | L  | BST          | X                        | ILLEGAL                         | 2    |

|                | -   | H             | L        | Н  | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         | 2    |

|                | L   | H             | L        | L  | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         | 2    |

|                | L   | L             | н        | Н  | ACT          | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | L   | L             | н        | L  | PRE          | RA11(BA),RA10            | NOP                             |      |

|                | L   | r             | ᆫ        | н  | REF          | Χ                        | ILLEGAL                         |      |

|                | L   | L             | L        | ᅵᅵ | MRS          | OP-code                  | ILLEGAL                         |      |

|                |     | DEFINE        |          | -  | -            |                          | ILLEGAL                         |      |

| Row Activating | н   | X             | x        |    | DESEL        | Х                        | NOP Bank Active After tRCD      |      |

|                | L   | н [           | н        | Н  | NOP          | x                        | NOP Bank Active After tRCD      | 1 1  |

| 1              | L   | H ]           | н        | L  | BST          | X                        | ILLEGAL                         | 2    |

| ļ              | L   | Н             | L        | н  | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         | 2    |

| 1              | L   | н             | L        | L  | ľ            | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         | 2    |

|                | L   | L             | н        | н  |              | RA11(BA),RA10            | ILLEGAL                         | 2    |

|                | L   | L             | н        | L  |              | RA11(BA),RA810           | ILLEGAL                         | 2    |

| J              | L   | L             | L        | н  |              | x                        | ILLEGAL                         | -    |

|                | L   | L             | L        | L  |              | OP-code                  | ILLEGAL                         |      |

| I              |     | EFINĖ         | ,        |    |              |                          |                                 | 1 1  |

\*NOTE: NN5216405 / NN5216805

## **FUNCTIONAL TRUTH TABLE (cont.)**

| Current State | <del>cs</del> | RAS    | CAS | WE  | Command      | Address                  | Action                          | Note |

|---------------|---------------|--------|-----|-----|--------------|--------------------------|---------------------------------|------|

| Write         | Н             | Х      | X   | Х   | DESEL        | X                        | NOP, Row Active After twR/tBWR  | i    |

| Recovering    | L             | Н      | н   | Н   | NOP          | x                        | NOP ,Row Active After twR/tBWR  |      |

|               | L             | Н      | ) н | L   | BST          | x                        | ILLEGAL                         |      |

|               | L             | Н      | L   | Н   | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | Start Read, Determine AP        |      |

|               | L             | H      | L   | L   | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | Start Read, Determine AP        |      |

|               | L             | L      | н   | Н   | ACT          | RA11(BA),RA10            | ILLEGAL                         | 2    |

|               | L             | L      | Н   | L   | PRE          | RA11(BA),RA10            | ILLEGAL                         | 2    |

|               | L             | L      | L   | н   | REF          | x                        | ILLEGAL                         |      |

|               | L             | L      | L   | L   | MRS          | OP-code                  | ILLEGAL                         |      |

|               | Ur            | NDEFIN | ED  | -   | -            |                          | ILLEGAL                         |      |

| Refreshing    | Н             | Х      | Х   | Х   | DESEL        | X                        | NOP, Idle After tBC             |      |

|               | L             | н      | Н   | Н   | NOP          | x                        | NOP, Idie After t <sub>RC</sub> |      |

|               | L             | н      | Н   | L   | BST          | x                        | ILLEGAL                         |      |

|               | L             | Н      | L   | н   | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         |      |

|               | L             | Н      | L   | L   | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         |      |

|               | L             | L      | Н   | Н   | ACT          | RA11(BA),RA10            | ILLEGAL                         | ļ    |

|               | L             | L      | н   | L   | PRE          | RA11(BA),RA10            | ILLEGAL                         | ŀ    |

|               | L             | L      | L   | н   | REF          | x                        | ILLEGAL                         | 1    |

|               | L             | L      | L   | L   | MRS          | OP-code                  | ILLEGAL                         | ĺ    |

|               | וט            | NDEFIN | ED  | · - | -            |                          | ILLEGAL                         |      |

| Mode Register | Н             | X      | X   | Х   | DESEL        | X                        | NOP                             |      |

| Accessing     | L             | н      | Н   | ] н | NOP          | x                        | NOP                             |      |

|               | L             | Н      | Н   | L   | BST          | x                        | ILLEGAL                         |      |

|               | L             | н      | L   | Н   | READ/READA   | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         |      |

|               | L             | Н      | L   | L   | WRITE/WRITEA | CA11(BA),CA10,*CA9/8-CA0 | ILLEGAL                         |      |

|               | L             | L      | н   | Н   | ACT          | RA11(BA),RA10            | ILLEGAL                         |      |

|               | L             | L      | Н   | L   | PRE          | RA11(BA),RA10            | ILLEGAL                         |      |

|               | L             | L      | L   | Н   | REF          | x                        | ILLEGAL                         |      |

|               | L             | L      | L   | L   | MRS          | OP-code                  | ILLEGAL                         |      |

|               | U             | NDEFIN | ĖD  | · - | -            |                          | ILLEGAL                         |      |

\*NOTE: NN5216405 / NN5216805

#### Notes:

- 1. All entries assume that CKE was active (High) during the preceding clock cycle.

- 2. Illegal to bank in specified state; function may be legal in the bank indicated by BA, depending on the state of that bank.

- 3. Device dose not require "2n-rule", but minimum timing between commands are specified.

- 4. NOP to bank precharging or in idle state. May precharge bank(s) indicated by BA (A11) and RA10.

- 5. If illegal states are executed, the device operation and data-integrity are not guaranteed.

## **MODE REGISTER CONFIGURATION**

Mode register has 5 fields.

A11- A8: Write Type

A7: (Must be a " 0 ")

A6 - A4: CAS Latency

A3: Burst Type

A2 - A0: Burst Length

## **Mode Register Options**

| A11 | A10 | A9 | <b>A8</b> | A7 | <b>A</b> 6 | A5    | A4       | АЗ | A2 | <b>A</b> 1 | AO | Function          |

|-----|-----|----|-----------|----|------------|-------|----------|----|----|------------|----|-------------------|

|     | W   | T  |           | 0  | . L        | TMODE | <b>.</b> | BT |    | BL         |    | Mode Register Set |

#### WT: Write

| WT   | Write Type                  |

|------|-----------------------------|

| 0000 | Burst Read and Burst Write  |

| XX01 | Reserved                    |

| XX10 | Burst Read and Single Write |

| XX11 | Reserved                    |

## **BT: Burst Type**

| BT | Burst Type |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

## LTMODE: Latency Mode

| LTMODE | CAS Latency |

|--------|-------------|

| 000    | Reserved    |

| 001    | 1           |

| 010    | 2           |

| 011    | 3           |

| 100    | Reserved    |

| 101    | Reserved    |

| 110    | Reserved    |

| 111    | Reserved    |

## **BL: Burst Length**

| BL  | Burst Length           |          |  |  |  |  |  |

|-----|------------------------|----------|--|--|--|--|--|

|     | BT=0                   | BT=1     |  |  |  |  |  |

| 000 | 1                      | . 1      |  |  |  |  |  |

| 001 | 2 (Modulo-2)           | 2        |  |  |  |  |  |

| 010 | 4 (Modulo-4)           | 4        |  |  |  |  |  |

| 011 | 8 (Modulo-8)           | 8        |  |  |  |  |  |

| 100 | Reserved               | Reserved |  |  |  |  |  |

| 101 | Reserved               | Reserved |  |  |  |  |  |

| 110 | Reserved               | Reserved |  |  |  |  |  |

| 111 | Full Page <sup>1</sup> | Reserved |  |  |  |  |  |

## Notes:

- Length of full page burst is \*1024/512 (\*1024 4 bit words / 512 8 bit words).

When the burst pointer reaches column address = \*1023/511, then the pointer wraps around to column address = 0. Auto-precharge is disabled when full page burst is enabled.

- 2 BL values of 100, 101, and 110 for Sequential and 100, 101, 110, and 111 for Interleave are defined as "Reserved" in JEDEC specification.

\*NOTE: NN5216405 / NN5216805

## **BURST SEQUENCE**

|              | Wrap                           | Туре                  |

|--------------|--------------------------------|-----------------------|

| Burst Length | Sequential (Modulo-N)          | Interleave            |

|              | (JEDEC Standard)               | (JEDEC Standard)      |

|              | Sequential, Modulo - 2         | Interleave            |

| 2            | 0 - 1                          | 0 - 1                 |

|              | 1 - 0                          | 1-0                   |

|              | Sequential, Modulo - 4         | Interleave            |

|              | 0-1-2-3                        | 0-1-2-3               |

| 4            | 1-2-3-0                        | 1 - 0 - 3 - 2         |

|              | 2-3-0-1                        | 2-3-0-1               |

|              | 3-0-1-2                        | 3-2-1-0               |

|              | Sequential, Modulo - 8         | Interleave            |

|              | 0-1-2-3-4-5-6-7                | 0-1-2-3-4-5-6-7       |

|              | 1-2-3-4-5-6-7-0                | 1-0-3-2-5-4-7-6       |

|              | 2-3-4-5-6-7-0-1                | 2-3-0-1-6-7-4-5       |

| 8            | 3-4-5-6-7-0-1-2                | 3-2-1-0-7-6-5-4       |

|              | 4-5-6-7-0-1-2-3                | 4-5-6-7-0-1-2-3       |

|              | 5-6-7-0-1-2-3-4                | 5-4-7-6-1-0-3-2       |

|              | 6-7-0-1-2-3-4-5                | 6-7-4-5-2-3-0-1       |

|              | 7-0-1-2-3-4-5-6                | 7-6-5-4-3-2-1-0       |

|              | Sequential, Modulo -*1024/512  | Interleave            |

| Full Page    | CA(s),CA(s+1),,CA(s+*1022/510) | Reserved              |

|              | CA(*1023/511),CA(0),           | Not Presently Defined |

CA: Column Address

#### **OPERATION**

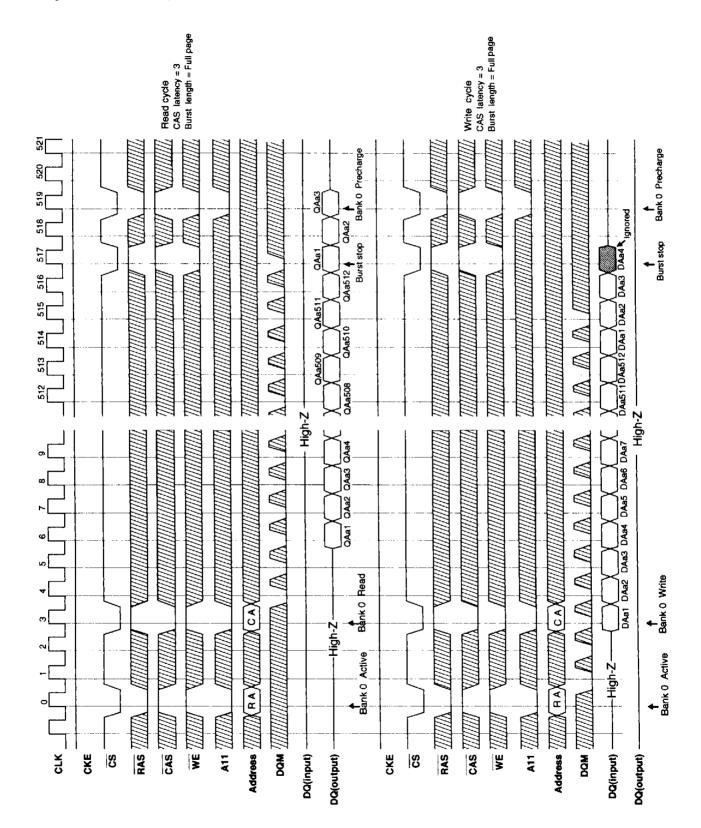

#### Read / Write

#### **Bank Active**

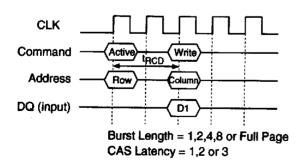

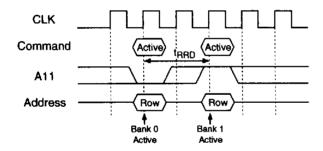

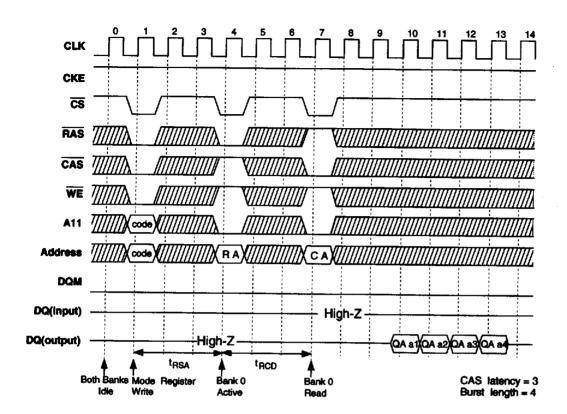

Before executing a read or write operation, Bank Active command must be issued. In a bank Active command cycle, either bank 0 or bank 1 is selected by BA(A11), and the row address is selected by A0 to A10. An interval of t<sub>RCD</sub> is required between Bank Active command and Read or Write command.

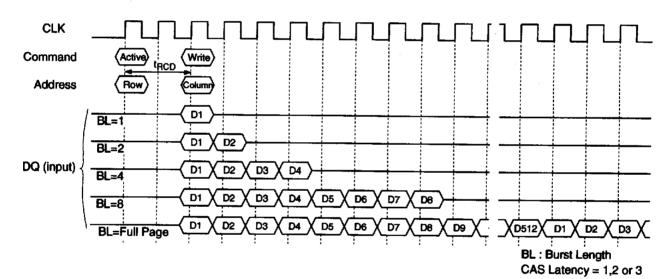

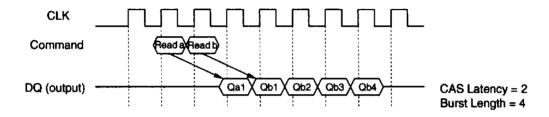

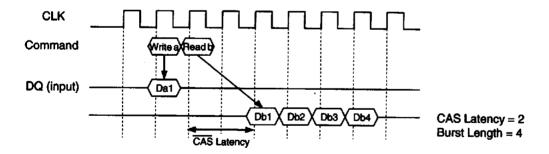

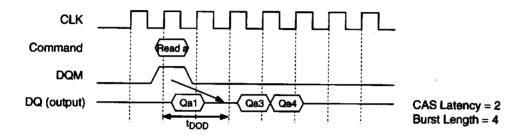

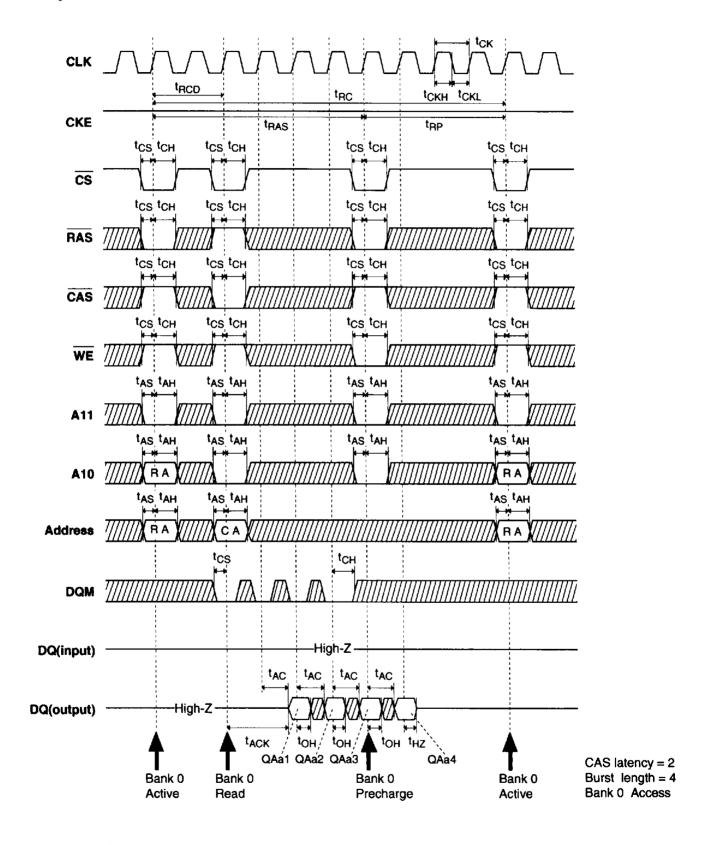

#### Read

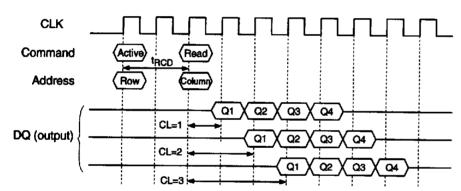

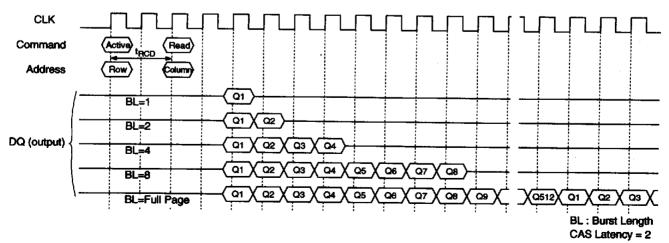

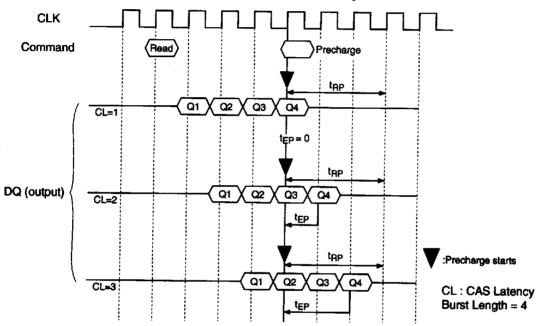

When Read command is issued, a burst read operation is performed. In a Read command cycle, the bank select address and the column address is asserted by A11 and A0 to A8. Data output starts after the number of cycles specified by the CAS latency. The CAS latency can be set to 1, 2 or 3. The burst length can be set to 1, 2, 4, 8 or full page. The start address for a burst read is specified by A0 to A8. When the burst length is 1, 2, 4 or 8, the output buffers automatically become High-Z after the completion of a read burst operation. When the burst length is full page, a read operation continues until Burst Stop command is issued.

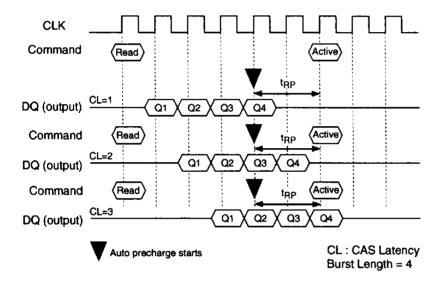

#### **CAS Latency for Reads**

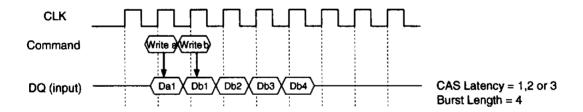

CL : CAS Latency Burst Length = 4

#### **Burst Length for Reads**

## Read / Write (cont.)

#### Read with Auto-Precharge

Read with auto-precharge operation is a function to execute automatic precharge operation after the completion of a read burst operation. An interval of the is required between the start point of Auto-Precharge and next Bank Active command of the same bank. When the burst length is full page, this operation cannot be used.

## **Read with Auto-Precharge**

#### Read / Write (cont.)

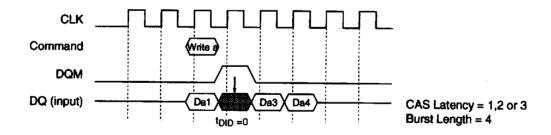

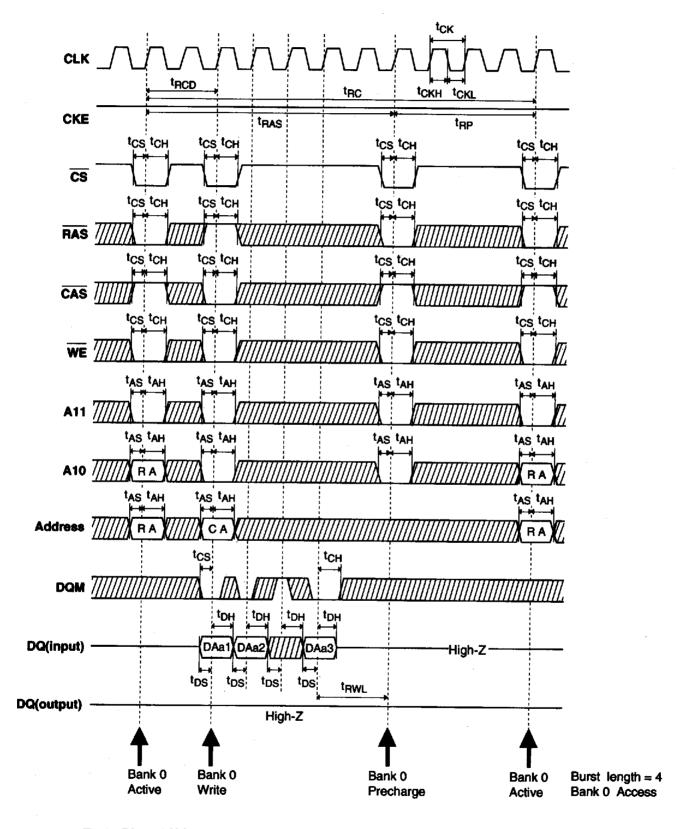

#### Write

When Write command is issued, a burst write or single write operation is performed. Burst write or single write mode is selected by WT (A11-A8) of the mode register. When WT is 0000, a burst write operation is enabled. When WT is XX01, a single write operation is enabled. In Write command cycle, the barik select address and the column addresses are asserted by A11 and A0 to A8.

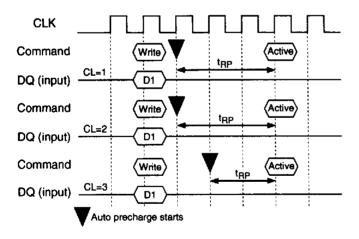

#### **Burst Write**

A burst write operation starts in the same cycle of Write command for all CAS latency. The burst length can be set to 1,2,4,8 and full page. A11 and A0 to A8 is also used as a start address of a burst write operation. **Single Write**

In a single write operation, data is only written to the column address of the selected bank at the Write command cycle without regard to the burst length setting.

#### **Burst Write**

## Single Write

## Read / Write (cont.)

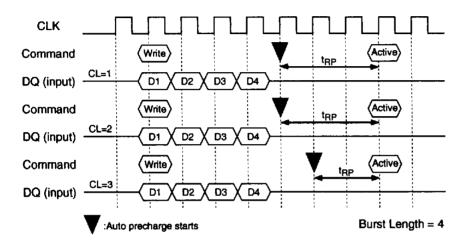

## Write with Auto-Precharge

Write with auto-precharge operation is a function to execute automatic precharge operation after a write operation. An interval of t<sub>RP</sub> is required between the start point of Auto-Precharge and next Bank Active command of the same bank. When the burst length is full page, this operation cannot be used.

## **Burst Write with Auto-Precharge**

## Single Write with Auto-Precharge

#### **Precharge**

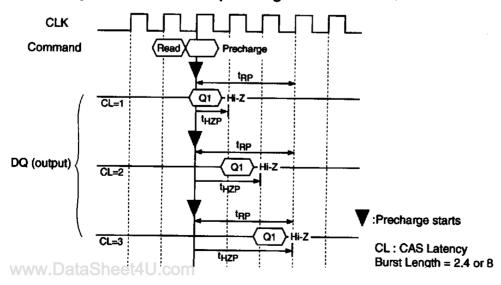

### Read to Precharge Command

An interval between Read command and Precharge command is minimum 1 clock.

#### To read all data

Precharge command makes the output buffer High-Z when the precharge bank is the same bank as accessed with the previous Read command. If all of the burst locations are to be read, the Precharge command must not be issued earlier than the tEP interval. The tEP is an interval between the final data output and Precharge command to ensure that all data are read.

## Read to Precharge Command: To read all data in burst sequence

#### To stop reading data

Precharge command makes output buffer High-Z after the cycles defined tHZP.

## Read to Precharge Command: To stop reading data

## Precharge (cont.)

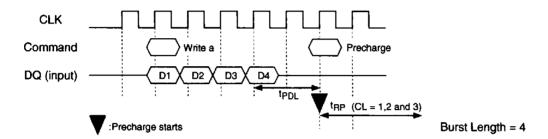

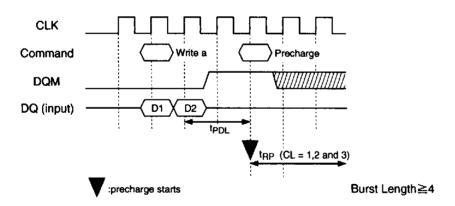

#### Write to Precharge Command

An interval between Write command and Precharge command is minimum 1clock.

#### To write all data

If it is necessary to write all of input data, Precharge command must be asserted after the cycle defined by tpDL. The tpDL is an interval between the final data input and Precharge command to ensure that all data are written.

## Write to Precharge Command: To write all data

#### To stop writing data

If Precharge command is asserted during a write operation, the input data must be masked by setting DQM high for assurance of the cycle defined by tpDL.

## Write to Precharge Command: To stop writing data

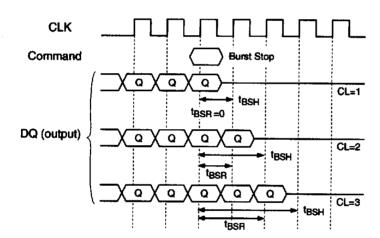

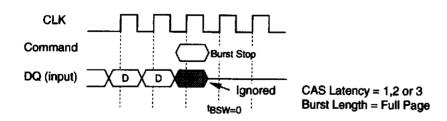

## **Full Page Burst Stop**

A full page burst read or write operation can be terminated by Burst Stop command. Burst Stop command will terminate Full Page and non-wrapped Sequential bursts (Mode Register: BL(MSB)=1 and BT=0). Burst Stop command will not terminate wrapped Sequential (modulo-n; n = 2, 4, or 8) bursts or Interleave bursts (Mode Register: BL(MSB)=0).

#### Full Page Burst Read

When CAS latency is 1, data remains valid in the same cycle as Burst Stop command, and output buffer goes to High-Z in the next cycle.

When CAS latency is 2, data remains valid in one clock cycle after Burst Stop command, and output buffer goes to High-Z in the next cycle.

When CAS latency is 3, data remains valid in two clock cycles after Burst Stop command, and output buffer goes to High-Z in the next cycle.

#### **Full Page Burst Write**

In all cases of CAS latency, no data is written in same cycle as Burst Stop command.

## **Full Page Burst Read Stop**

CL : CAS Latency Burst Length = Full Page

## **Full Page Burst Write Stop**

#### Command Intervals

#### **Read to Read Command Interval**

During burst read operation, when new Read command is issued, the previous burst read is interrupted and the new burst read starts after the number of cycles specified by CAS latency. An interval between the commands is minimum 1clock. During burst read operation, next Read command can be issued in every cycle.

#### Read to Read Command Interval

#### Write to Write Command Interval

During burst write operation, when new Write command is issued, the previous burst write is interrupted and the new burst write starts in the same cycle as setting new command. An interval between the commands is minimum 1clock. During burst write operation, next Write command can be issued in every cycle.

#### Write to Write Command Interval

## Command Intervals (cont.)

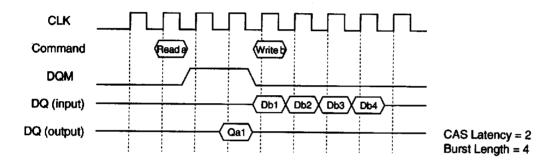

#### Read to Write Command Interval

During burst read operation, when Write command is issued, the burst read is interrupted and the burst write starts in the same cycle as setting new command. An interval between the commands is minimum 1clock. There is a restriction to avoid data conflict. Before asserting Write command, DQM must be set high so that the output buffer becomes High-Z before data-in is applied.

## Read to Write Command Interval

#### Write to Read Command Interval

During burst write operation, when Read command is issued, data is written until one cycle before setting new command and data output starts after the number of cycles specified by CAS latency. An interval between the commands is minimum 1 clock. During burst read operation, next Write command can be issued in every cycle without any restriction.

#### Write to Read Command Interval

## Command Intervals (cont.)

#### For the same bank

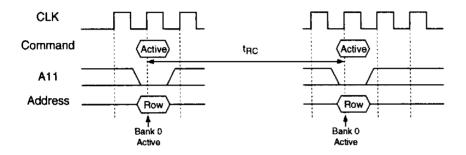

An interval between the two Bank Active Commands for the same bank must be no less than t<sub>RC</sub>.

#### Bank Active to Bank Active Command Interval for same bank

#### For different bank

An interval between the two Bank Active Commands for different bank must be no less than tRRD

## Bank Active to Bank Active Command Interval for different bank

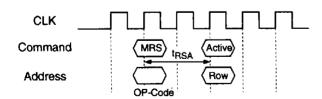

## **Mode Register Set Command Interval**

An interval between Mode Register Set command and Bank Active command must be no less than tRSA.

## Mode Register Set to Bank Active Command Interval

## **DQM Control**

DQM controls output buffer. DQM mask the DQ data.

#### Reading

When DQM is low and data is being read, the output buffer becomes Low-Z and data output is enabled. When DQM is high, the output buffer becomes High-Z two cycles( tDOD) after. tDOD doesn't depend on CAS latency.

#### **DQM Control: Reading**

## Writing

When DQM is low, data is written. When DQM is high, data is not written and the previous data is maintained. In this case, the latency ( $t_{DID}$ ) is 0.  $t_{DID}$  doesn't depend on CAS latency.

#### **DQM** Control: Writing

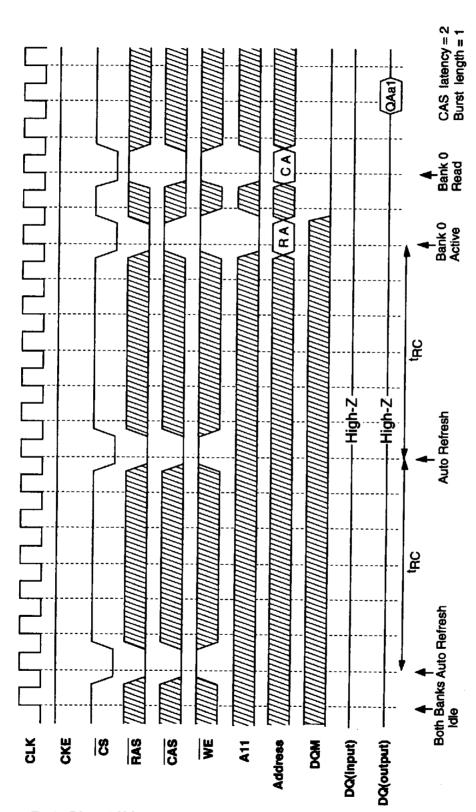

#### Refresh

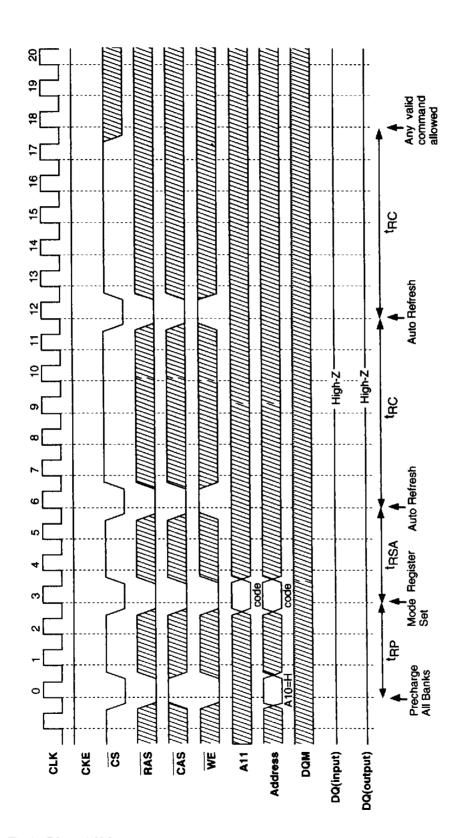

#### **Auto-Refresh**

Before executing Auto-Refresh command, both banks must be idle. When Auto-Refresh command is executed, the refresh address is generated internally and the refresh is executed. The refresh operation should be performed 4096 times within 64ms. A minimum interval of t<sub>RC</sub> is required between two Auto-Refresh commands or between an Auto-Refresh command and bank active command.

A precharge is completed automatically after the auto-refresh, therefore, an additional precharge operation is not necessary.

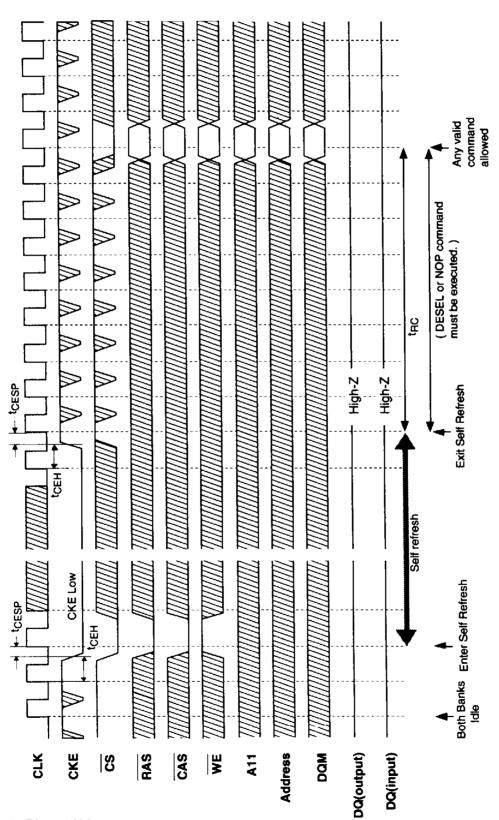

#### Self-Refresh

After executing Enter Self-Refresh command, the self-refresh operation continues as long as CKE stays low. In this mode, power consumption is reduced by turning off all input and output buffers. While in self-refresh mode, refresh operation is performed internally, so there is no need to control refresh operation externally. The self-refresh mode is exited by Exit Self-Refresh command. After exiting self refresh mode , NOP command or DESEL command should be asserted within one  $t_{\rm RC}$  period. It is recommended to assert an Auto-Refresh command just after the  $t_{\rm RC}$  period to avoid the violation of refresh period.

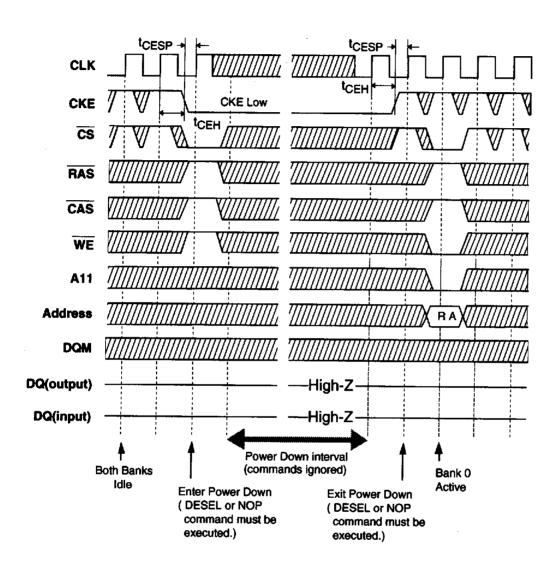

## **Power Down Mode**

Power down mode starts when CKE goes low in the idle state. This mode continues as long as CKE remains low. In this mode, power consumption is reduced by turning off all input and output buffers. However, self-refresh is not performed in this mode. When CKE goes high, the power down mode is terminated, and command input is enabled on the second low-to-high transition of CLK after CKE goes high.

#### **Clock Suspend Mode**

Clock suspend mode starts when CKE goes low while a bank is active. This mode continues as long as CKE stays low. In this mode, the internal state is maintained and external input signals are ignored.

When CKE goes high, clock suspend mode is terminated, and command input is enabled on the second low-to high transition of CLK after CKE goes high.

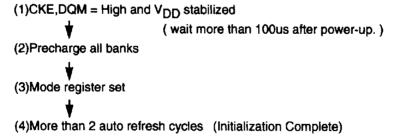

### Initialization Sequence

After power-up the following initialize sequence should be used:

## **ABSOLUTE MAXIMUM RATINGS**

| RATING                                         | SYMBOL          | VALUE       | UNIT |

|------------------------------------------------|-----------------|-------------|------|

| Voltage on Any Pin Relative to V <sub>SS</sub> | VT              | -1.0 to 4.6 | V    |

| Supply Voltage Relative to V <sub>SS</sub>     | V <sub>CC</sub> | -1.0 to 4.6 | ٧    |

| Short Circuit Output Current                   | lout            | . 50        | mA   |

| Power Dissipation                              | PT              | 1.0         | w    |

| Operating Temperature                          | Topr            | 0 to + 70   | °C   |

| Storage Temperature                            | Tstg            | -55 to +125 | °C   |

Notes: 1.Short circuit output current, lout, is limited to one output at a time, 1 second maximum duration.

## RECOMMENDED DC OPERATING CONDITIONS (Ta = 0 to 70 °C)

| SYMBOL          | PARAMETER                                          | MIN. | MAX.                  | UNIT | TEST CONDITIONS                                   |

|-----------------|----------------------------------------------------|------|-----------------------|------|---------------------------------------------------|

| V <sub>DD</sub> | Supply Voltage: V <sub>DD</sub> , V <sub>DDQ</sub> | 3.0  | 3.6                   | ٧    | All Voltages Referenced to V <sub>SS</sub>        |

|                 | Input High Voltage: DQ                             | 2.0  | V <sub>DDQ</sub> +1.0 | ٧    | V <sub>IH</sub> (MAX.)=5.5V for Pulse Width ≦5ns  |

| V <sub>IH</sub> | Input High Voltage: All Except DQ                  | 2.0  | V <sub>DD</sub> +1.0  | ٧    | V <sub>IH</sub> (MAX.)=5.5V for Pulse Width ≤5ns  |

| V <sub>IL</sub> | Input Low Voltage                                  | -0.3 | 0.8                   | V    | V <sub>IL</sub> (MAX.)=-1.0V for Pulse Width ≦5ns |

## CAPACITANCE (Ta = 25 °C, f = 1MHz)

| PARAMETER                                          | SYMBOL | MIN. | MAX. | UNIT |

|----------------------------------------------------|--------|------|------|------|

| Input Capacitance, All Control Signals & Addresses | CI     | -    | 5    | рF   |

| Output Capacitance (DQ) <sup>1</sup>               | со     | -    | 7    | pF   |

Notes : 1. DQM =  $V_{\mbox{\scriptsize IH}}$  to disable Dout.

## DC ELECTRICAL CHARACTERISTICS (Ta = 0 to 70 °C, $V_{DD}$ = 3.3V $\pm$ 0.3V, $V_{SS}$ = 0V)

| Speed Version                            |                  | -1   | 0    | -1    | 2    |      |                                                                 |      |

|------------------------------------------|------------------|------|------|-------|------|------|-----------------------------------------------------------------|------|

| Frequency                                | ĺ                | 100  | MHz  | 83MHz |      |      |                                                                 |      |

| Parameter                                | Symbol           | Min. | Max. | Min.  | Max. | Unit | Test condition                                                  | Note |

| Operating Current                        | lcc1             | _    | 100  | -     | 85   | mA   | Burst Length = 1 t <sub>RC</sub> = min.                         | 1    |

| Standby Current                          | I <sub>CC2</sub> | -    | 3    | -     | 3    | mA   | CKE = V <sub>IL</sub> ,t <sub>CK</sub> = min.                   |      |

|                                          |                  | -    | 2    | -     | 2    | mA   | $CKE = V_{IL}$ $CLK = V_{IL} \text{ or } V_{IH} \text{ (fix)}$  |      |

|                                          |                  | -    | 35   | -     | 25   | mA   | $CKE = V_{IH}$ , NOP<br>$t_{CK} = min$ .                        |      |

| Active Standby Current (One Bank Active, | Icc3             | -    | 7    | •     | 7    | mA   | CKE = $V_{IL}$ , $t_{CK}$ = min.<br>I/O = High-Z                | 1    |

| One Bank Idle)                           |                  | -    | 35   | •     | 30   | mA   | CKE = $V_{IH}$ , NOP<br>$t_{CK}$ = min., I/O = High-Z           | -Z   |

| Burst Operating Current                  | I <sub>CC4</sub> | -    | 75   | -     | 65   | mA   | $CL = 1,t_{CK} = min.$                                          | 1    |

|                                          |                  | -    | 120  | -     | 100  | mA   | CL = 2,t <sub>CK</sub> = min.                                   |      |

|                                          |                  | •    | 165  | -     | 145  | mA   | $CL = 3,t_{CK} = min.$                                          |      |

| Refresh Current                          | 1 <sub>CC5</sub> | -    | 95   | -     | 80   | mA   | t <sub>RC</sub> = min.                                          |      |

| Self-Refresh Current                     | ICC6             | •    | 2    | -     | 2    | mA   | V <sub>IH</sub> ≥V <sub>DD</sub> -0.2V<br>V <sub>IL</sub> ≤0.2V |      |

| Input Leakage Current                    | ILi              |      | ±1.0 | -     | ±1.0 | μΑ   | 0≦Vin≦V <sub>DD</sub>                                           |      |

| Output Leakage Current                   | ILo              |      | ±1.0 | -     | ±1.0 | μΑ   | 0≦Vin≦V <sub>DD</sub><br>I/O = Disable                          |      |

| Output High Voltage                      | V <sub>OH</sub>  | 2.4  |      | 2.4   |      | ٧    | I <sub>OH</sub> = -2mA                                          |      |

| Output Low Voltage                       | V <sub>OL</sub>  |      | 0.4  |       | 0.4  | ٧    | I <sub>OH</sub> = 2mA                                           |      |

Notes: 1. I<sub>CC</sub> depends on output load condition when the device is selected. I<sub>CC</sub>(max) is specified at the output open condition.

<sup>2.</sup> Input signal transition is once per two CLK cycles.

# AC Characteristics (Ta = 0 to 70 °C, $V_{DD}$ = 3.3V ± 0.3V, $V_{SS}$ = 0V)

|     | SPEED VERSI       | ON                        | ***          |          | 10     |      | -12     |      |      |

|-----|-------------------|---------------------------|--------------|----------|--------|------|---------|------|------|

|     | FREQUENC          | Y                         |              | 100      | MHz    | 83   | MHz     |      |      |

| NO. | SYMBOL            | PARAMETE                  | R            | MIN.     | MAX.   | MIN. | MAX.    | UNIT | NOTE |

| 1   | t <sub>CK</sub>   | System Clock              | (CL=3)       | 10       | -      | 12   |         | ns   | 1    |

|     |                   |                           | (CL=2)       | 15       | -      | 18   | -       | ns   | ]    |

|     |                   |                           | (CL=1)       | 30       | -      | 36   | -       | ns   |      |

| 2   | t <sub>CKH</sub>  | CLK High Pulse Width      | ·            | 3        | -      | 4    | -       | ns   | 1    |

| 3   | t <sub>CKL</sub>  | CLK Low Pulse Width       |              | 3        | -      | 4    | -       | ns   | 1    |

| 4   | t <sub>AC</sub>   | Access Time from CLK      | (CL=3)       | -        | 7      | •    | 9       | ns   | 1,2  |

|     |                   |                           | (CL=2)       | -        | 9      | -    | 12      | ns   | ]    |

|     |                   |                           | (CL=1)       | -        | 25     | -    | 30      | ns   | 1    |

| 5   | t <sub>ACK</sub>  | Read Command              | (CL=3)       | _        | 2CLK+7 | -    | 2CLK+9  | ns   | 1,2  |

|     |                   | to Data Valid             | (CL=2)       | -        | 1CLK+9 | •    | 1CLK+12 | ns   |      |

|     |                   |                           | (CL=1)       | <b>-</b> | 25     | -    | 30      | ns   |      |

| 6   | t <sub>OH</sub>   | Data Out Hold Time        |              | 3        | -      | 3    | -       | ns   | 1,2  |

| 7   | t <sub>LZ</sub>   | CLK to Data Out Low Imp   | edance       | 0        | -      | 0    | -       | ns   | 1,2  |

| 8   | t <sub>HZ</sub>   | CLK to Data Out           | (CL=3)       | 4        | 7      | 4    | 8       | ns   | 1,3  |

|     |                   | High Impedance            | (CL=2)       | 4        | 7      | 4    | 8       | ns   |      |