# 64K x 4 SRAM Module

#### **Features**

- Very high speed 256K SRAM module

Access time of 10 nsec.

- 300-mil-wide hermetic DIP package

- Low active power

- 1.8W (max.)

- SMD technology

- TTL-compatible inputs and outputs

- On-chip decode for speed and density

- JEDEC pinout—compatible with 7C194 monolithic SRAMs

- Small PCB footprint

- 0.36 sq. in.

### **Functional Description**

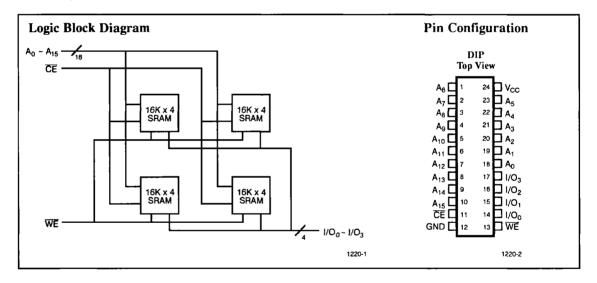

The CYM1220 is an extremely high performance 256-kilobit static RAM module organized as 65,536 words by 4 bits. This module is constructed using four 16K x 4 static RAMs in LCC packages mounted on a 300-mil-wide ceramic substrate. Extremely high speed and density are achieved by using BiCMOS SRAMs containing internal address decoding logic.

Writing to the module is accomplished when the chip enable  $(\overline{CE})$  and write enable  $(\overline{WE})$  inputs are both LOW. Data on the four input pins  $(I/O_0$  through  $I/O_3)$

of the device is written into the memory location specified on the address pins (A<sub>0</sub> through A<sub>15</sub>).

Reading the device is accomplished by taking the chip enable  $(\overline{CE})$  LOW, while write enable  $(\overline{WE})$  remains inactive or HIGH. Under these conditions, the contents of the memory location specified on the address pins  $(A_0$  through  $A_{15})$  will appear on the four output pins  $(I/O_0$  through  $I/O_3)$ .

The data output pins remain in a highimpedance state unless the module is selected and write enable (WE) is HIGH.

#### **Selection Guide**

|                          |            | 1220HD-10 | 1220HD-12 | 1220HD-15 | 1220HD-20 |

|--------------------------|------------|-----------|-----------|-----------|-----------|

| Maximum Access Time (ns) |            | 10        | 12        | 15        | 20        |

| Maximum Operating        | Commercial | 325       | 325       | 325       |           |

| Current (mA)             | Military   |           | 375       | 375       | 375       |

| Maximum Standby          | Commercial | 200       | 200       | 200       |           |

| Current (mA)             | Military   |           | 250       | 250       | 250       |

#### **Maximum Ratings**

(Above which the useful life may be impaired)

| (13000 when the assist the may be imparted)           |

|-------------------------------------------------------|

| Storage Temperature65°C to +150°C                     |

| Ambient Temperature with                              |

| Power Applied55°C to +125°C                           |

| Supply Voltage to Ground Potential $-0.5V$ to $+7.0V$ |

| DC Voltage Applied to Outputs                         |

| in High Z State0.5V to +7.0V                          |

| DC Input Voltage0.5V to +7.0V                         |

## **Operating Range**

| Range      | Ambient<br>Temperature | $v_{cc}$ |

|------------|------------------------|----------|

| Commercial | 0°C to +70°C           | 5V ± 10% |

| Military   | -55°C to +125°C        | 5V ± 10% |

| Parameters Description |                           | Took Conditions                                                                            | CYM1220HD       |      |      |       |

|------------------------|---------------------------|--------------------------------------------------------------------------------------------|-----------------|------|------|-------|

|                        |                           | lest Conditions                                                                            | Test Conditions |      |      | Units |

| VOH                    | Output HIGH Voltage       | $V_{CC} = Min.$ , $I_{OH} = -4.0 \text{ mA}$                                               |                 | 2.4  |      | V     |

| V <sub>OL</sub>        | Output LOW Voltage        | $V_{CC} = Min., I_{OL} = 8.0 \text{ mA}$                                                   |                 |      | 0.4  | V     |

| V <sub>IH</sub>        | Input HIGH Voltage        |                                                                                            |                 | 2.2  | Vcc  | v     |

| V <sub>IL</sub>        | Input LOW Voltage[1]      |                                                                                            |                 | -0.5 | 0.8  | V     |

| I <sub>IX</sub>        | Input Load Current        | $GND \le V_I \le V_{CC}$                                                                   |                 | -20  | + 20 | μА    |

| loz                    | Output Leakage Current    | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> , Output Disabled                                   |                 | -20  | + 20 | μА    |

| I <sub>CC</sub>        | V <sub>CC</sub> Operating | $\underline{V_{CC}} = Max., I_{OUT} = 0 mA,$                                               | Commercial      |      | 325  | ^     |

| ICC                    | Supply Current            | $\overline{CE} \leq V_{IL}$                                                                | Military        | _    | 375  | mA    |

| ,                      | Automatic CE              | $V_{CC} = Max., \overline{CE} \ge V_{H},$                                                  | Commercial      |      | 200  |       |

| $I_{SB1}$              | Power-Down Current        | Min. Duty Cycle = 100%                                                                     | Military        |      | 250  | mA.   |

| Ione                   | Automatic CE              | $V_{CC} = Max., \overline{CE} \ge V_{CC} - 0.2V,$<br>$V_{IN} \ge V_{CC} - 0.2V \text{ or}$ | Commercial      |      | 200  | mA    |

| I <sub>SB2</sub>       | Power-Down Current        | $V_{IN} \leq 0.2V$                                                                         | Military        |      | 250  | "     |

## Capacitance[2]

| Parameters      | Description        | Test Conditions                         | Max. | Units |

|-----------------|--------------------|-----------------------------------------|------|-------|

| C <sub>IN</sub> | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 25   | pF    |

| Cour            | Output Capacitance | $V_{CC} = 5.0V$                         | 30   | pF    |

#### Notes

## AC Test Loads and Waveforms

<sup>1.</sup>  $V_{IL(MIN)} = -3.0V$  for pulse widths less than 20 ns.

<sup>2.</sup> Tested on a sample basis.

### Switching Characteristics Over the Operating Range [3]

| Parameters       | Description                      | 1220HD-10 |      | 1220HD-12 |      | 1220HD-15 |      | 1220HD-20 |      | Units  |

|------------------|----------------------------------|-----------|------|-----------|------|-----------|------|-----------|------|--------|

| rarameters       | Description                      | Min.      | Max. | Min.      | Max. | Min.      | Max. | MIn.      | Max. | Oillis |

|                  |                                  |           |      |           |      |           |      |           |      |        |

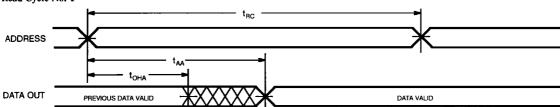

| t <sub>RC</sub>  | Read Cycle Time                  | 10        |      | 12        |      | 15        |      | 20        |      | ns     |

| t <sub>AA</sub>  | Address to Data Valid            |           | 10   |           | 12   |           | 15   |           | 20   | ns     |

| <sup>t</sup> OHA | Data Hold from Address Change    | 2         |      | 3         |      | 3         |      | 3         |      | ns     |

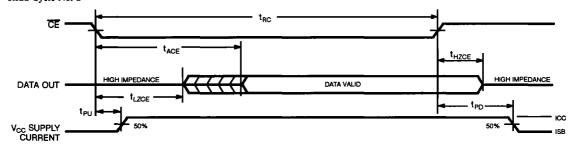

| tACE             | CE LOW to Data Valid             |           | 10   |           | 12   |           | 15   |           | 20   | ns     |

| tLZCE            | CE LOW to Low Z                  | 2         |      | 3         |      | 3         |      | 3         |      | ns     |

| tHZCE            | CE HIGH to High Z <sup>[4]</sup> |           | 6    |           | 8    |           | 8    |           | 8    | ns     |

| tpU              | CE LOW to Power Up               | 0         |      | 0         |      | 0         |      | 0         |      | ns     |

| tPD              | CE HIGH to Power Down            |           | 10   |           | 12   |           | 15   |           | 20   | ns     |

|                  |                                  |           |      |           |      |           |      |           |      |        |

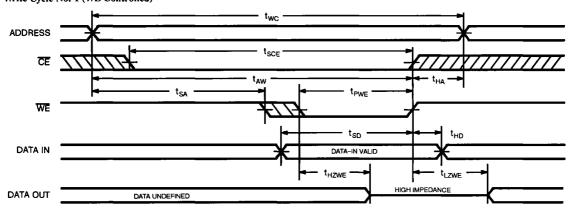

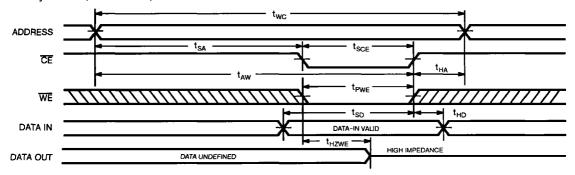

| twc              | Write Cycle Time                 | 10        |      | 12        |      | 15        |      | 20        |      | ns     |

| tSCE             | CE LOW to Write End              | 8         |      | 10        |      | 12        |      | 15        |      | ns     |

| t <sub>AW</sub>  | Address Set-up to Write End      | 8         |      | 10        |      | 12        |      | 15        |      | ns     |

| t <sub>HA</sub>  | Address Hold from Write End      | 1         |      | 1         |      | 1         |      | 1         |      | ns     |

| tsA              | Address Set-up from Write Start  | 0         |      | 0         |      | 0         |      | 0         |      | ns     |

| tPWE             | WE Pulse Width                   | 8         | 1    | 10        |      | 12        |      | 15        |      | ns     |

| tSD              | Data Set-Up to Write End         | 8         | 2    | 10        |      | 10        | ·    | 10        |      | ns     |

| tHD              | Data Hold from Write End         | 1         |      | 1         |      | 1         |      | 1         |      | ns     |

| tLZWE            | WE HIGH to Low Z                 | 3         |      | 5         |      | 5         |      | 5         |      | ns     |

| tHZWE            | WE LOW to High Z [4]             | 0         | 5    | 0         | 7    | 0         | 7    | 0         | 10   | ns     |

#### Notes:

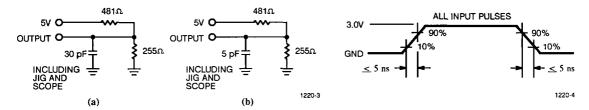

- Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input levels of 0 to 3.0V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance.

- t<sub>HZCS</sub> and t<sub>HZWE</sub> are specified with C<sub>L</sub> = 5 pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady state voltage.

- 5. The internal write time of the memory is defined by the overlap of  $\overline{\text{CE}}$  LOW and  $\overline{\text{WE}}$  LOW. Both signals must be LOW to initiate a write and

- either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

- 6. WE is HIGH for read cycle.

- 7. Device is continuously selected,  $\overline{\text{CE}} = V_{\text{IL}}$ .

- 8. Address valid prior to or coincident with  $\overline{\text{CE}}$  transition low.

- If <del>CE</del> goes HIGH simultaneously with <del>WE</del> HIGH, the output remains in a high-impedance state.

### **Switching Waveforms**

Read Cycle No. 1[6, 7]

1220-5

## Switching Waveforms (continued)

Read Cycle No. 2 [6,8]

1220-8

Write Cycle No. 1 (WE Controlled) [5]

1220-7

Write Cycle No. 2 (CE Controlled)[5,9]

1220-8

## Truth Table

| CE | WE | Inputs/Outputs | Mode                |

|----|----|----------------|---------------------|

| Н  | X  | High Z         | Deselect/Power-Down |

| L  | Н  | Data Out       | Read Word           |

| L  | L  | Data In        | Write Word          |

# **Ordering Information**

| Speed | Ordering Code  | Package<br>Type | Operating<br>Range |

|-------|----------------|-----------------|--------------------|

| 10    | CYM1220HD-10C  | HD08            | Commercial         |

| 12    | CYM1220HD-12C  | HD08            | Commercial         |

|       | CYM1220HD-12MB |                 | Military           |

| 15    | CYM1220HD-15C  | HD08            | Commercial         |

|       | CYM1220HD-15MB |                 | Military           |

| 20    | CYM1220HD-20MB | HD08            | Military           |

Document #: 38-00025