# PBL 3796, PBL 3796/2 Subscriber Line Interface Circuit

### Description

PBL 3796 (63 V) and PBL 3796/2 (48 V) are analog Subscriber Line Interface Circuits (SLICs), which are fabricated in a 75 V bipolar, monolithic process.

The programmable battery feed is resistive with short-loop current limiting. A switchmode regulator reduces on-chip power dissipation in the active state. In the standby state, power dissipation is further reduced, while still permitting supervisory functions to be active.

Tip-ring polarity is reversible without altering SLIC supervisory and voice frequency (vf) functions. Tip and ring outputs can be set to high impedance states. These and other operating states are activated via a parallel, four bit control word.

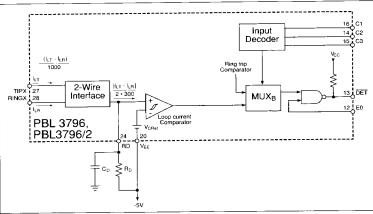

An external resistor controls the off-hook detector threshold current. The ring trip detector can operate with both balanced and unbalanced ringing systems. The two detectors are read via a shared output.

Ring and test relay drivers with internal clamp diodes are provided.

The complex or real two-wire impedance is set by a scaled, lumped element network.

Two- to four-wire and four- to two-wire signal conversion is provided by the SLIC in conjunction with either a conventional or a programmable CODEC/filter.

Longitudinal line voltages are suppressed by a control loop within the SLIC.

Packages are 28-pin, dual-in-line; or 32-pin, leadless chip carrier (PBL 3796/2 only) .

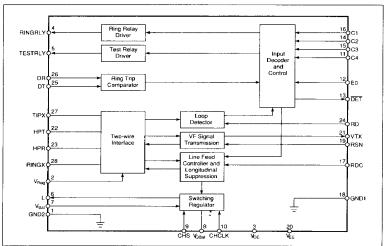

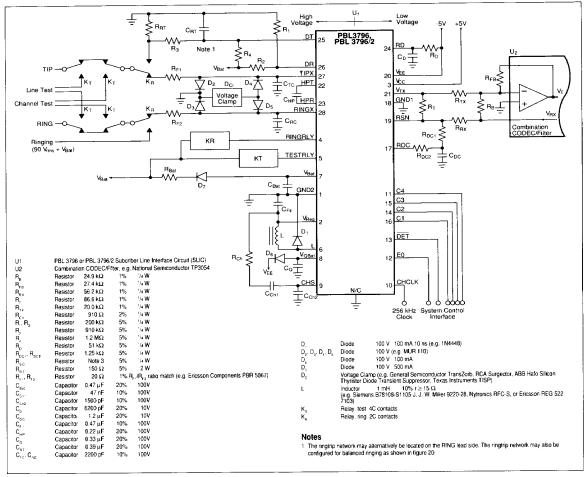

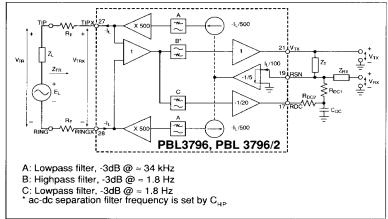

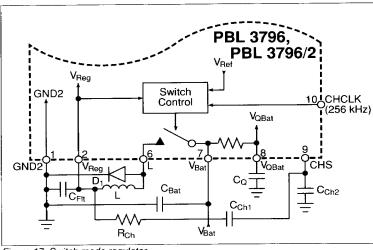

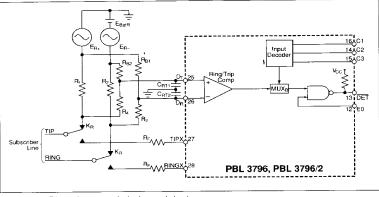

Figure 1. Block diagram. Pin numbers refer to the dual-in-line package.

### Key features

- On-chip switch mode regulator to minimize power dissipation

- Programmable, resistive battery feed with short-loop current limiting

- Line feed characteristics independent of battery variations

- · Tip-ring polarity reversal function

- Tip and ring open circuit state; tip open with ring active state

- Detectors:

- programmable loop current / ring ground detector

- ring trip detector

- · Ring and test relay drivers

- Line terminating impedance, complex or real, set by a simple external network

- Hybrid function with conventional or programmable CODEC/filters

- · 70 dB longitudinal to metallic balance

- 79 mApeak longitudinal current suppression

- Idle noise < 10 dBrnC, < -80 dBup</li>

# **Absolute Maximum Ratings**

Note: pin numbers refer to the 28-pin, dual-in-line package, unless otherwise indicated.

| Parameter                                                                                                                                                            | Symbol                                | Min              | Мах             | Unit      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-----------------|-----------|

| Temperature and humidity                                                                                                                                             |                                       |                  |                 |           |

| Storage temperature range                                                                                                                                            | T <sub>Stg</sub>                      | -55              | +150            | °C        |

| Operating ambient temperature range                                                                                                                                  | T <sub>Amb</sub>                      | -40              | +85             | °C        |

| Operating junction temperature range (Note 1)                                                                                                                        | $I_{\dagger}$                         | -40              | 135             | °C        |

| Storage humidity (Note 2)                                                                                                                                            | RH                                    | 5                | 95              | %RH       |

| Power supply                                                                                                                                                         |                                       |                  |                 |           |

| V <sub>CC</sub> with respect to ground                                                                                                                               | V <sub>cc</sub>                       | -0.4             | +6.5            | V         |

| V <sub>EE</sub> with respect to ground                                                                                                                               | V <sub>EE</sub>                       | -6.5             | +0.4            | V         |

| V <sub>Bat</sub> with respect to ground                                                                                                                              | V <sub>Bat</sub>                      | -70              | +0.4            | V         |

| Power dissipation                                                                                                                                                    |                                       |                  |                 |           |

| Continuous power dissipation at T <sub>Amb</sub> = 70 °C (Note 3)                                                                                                    |                                       |                  |                 | 144       |

| 28-pin, ceramic dual-in-line package                                                                                                                                 |                                       |                  | 1.7             | W         |

| 32-pin, leadless chip carrier                                                                                                                                        |                                       |                  | 1.7             |           |

| Ground                                                                                                                                                               |                                       |                  |                 |           |

| Voltage between GND1 and GND2 (Note 4)                                                                                                                               | V <sub>G12</sub>                      | -0.1             | +0.1            |           |

| Switch mode regulator                                                                                                                                                |                                       |                  | 150             | mA —      |

| Peak current through regulator switch (pin L)                                                                                                                        | I <sub>IPk</sub>                      |                  | +2              |           |

| Regulator switch output (pin L) peak off-state voltage                                                                                                               | V <sub>IPk</sub>                      |                  | +2              |           |

| Relay drivers                                                                                                                                                        |                                       |                  |                 |           |

| Test relay supply voltage                                                                                                                                            | V <sub>TRIy</sub>                     | V <sub>Bat</sub> | V <sub>cc</sub> |           |

| Ring relay supply voltage                                                                                                                                            | V <sub>RRIy</sub>                     | V <sub>Bat</sub> | 80              | mA        |

| Test relay current                                                                                                                                                   | TRIy                                  |                  | 80              | mA —      |

| Ring relay current                                                                                                                                                   | RRIY                                  |                  | 80              | 11/2      |

| Ring trip comparator                                                                                                                                                 | $V_{DT}, V_{DB}$                      | V <sub>Bat</sub> | 0               |           |

| Input voltage                                                                                                                                                        |                                       | -2               | +2              | mA .      |

| Input current, t <sub>p</sub> = 10 ms                                                                                                                                | DT, DR                                |                  |                 |           |

| Digital inputs, outputs C1 - C4, E0, DET, CHCLK                                                                                                                      | V <sub>ID</sub>                       | -0.4             | V <sub>cc</sub> |           |

| Input voltage                                                                                                                                                        | V ID                                  | -0.3             | V <sub>cc</sub> | V         |

| Output voltage (DET not active)                                                                                                                                      | V <sub>op</sub>                       |                  | 3               | mA        |

| Output current                                                                                                                                                       | ОД                                    |                  |                 |           |

| TIPX and RINGX terminals                                                                                                                                             | $V_{T}, V_{R}$                        | -70              | 1               |           |

| TIPX or RINGX continuous voltage (Notes 5, 6)                                                                                                                        | $V_{\rm T}, V_{\rm R}$                | -70              | 5               |           |

| TIPX or RINGX, pulsed voltage, $t_w < 10$ ms and $t_{rep} > 10$ s (Notes 5, 6)<br>TIPX or RINGX, pulsed voltage, $t_w < 1$ $\mu s$ and $t_{rep} > 10$ s (Notes 5, 6) | $V_{\rm T}, V_{\rm R}$                | -90              | 10              |           |

| TIP or RINGA, pulsed voltage, $t_w < 1 \mu s$ and $t_{rep} > 10.3$ (Notes 5, 6, 7)                                                                                   | $V_{T}, V_{B}$                        | 120              | 15              |           |

| TIPX or RINGX current                                                                                                                                                | I <sub>Ldc</sub>                      | -105             | 105             | mA        |

|                                                                                                                                                                      |                                       |                  |                 |           |

| Recommended operating conditions                                                                                                                                     | Symbol                                | Min              | Max             | Unit      |

| Parameter                                                                                                                                                            |                                       | 0                | 70              | °C        |

| Ambient temperature                                                                                                                                                  | T <sub>Amb</sub><br>T <sub>Case</sub> | 0                | 90              | <u>~č</u> |

| Case temperature                                                                                                                                                     | V <sub>CC</sub>                       | 4.75             | 5.25            |           |

| V <sub>cc</sub> with respect to ground                                                                                                                               | V <sub>FF</sub>                       | -5.25            | -4.75           | V         |

| V <sub>EE</sub> with respect to ground V <sub>Bat</sub> with respect to ground — PBL 3796 (Note 8)                                                                   | V <sub>Bat</sub>                      | -64.5            | -61.5           | V         |

| V <sub>Bat</sub> with respect to ground — PBL 3796 (Note 8)                                                                                                          | V <sub>Bat</sub>                      | -58.0            | -46.0           | V         |

| GND2 with respect to GND1 (Note 9)                                                                                                                                   | V <sub>G12</sub>                      | 0                | 0               | V         |

| CIADZ WITH TESPECT to CIADT (Note 5)                                                                                                                                 | G12                                   |                  |                 |           |

### **Notes**

- The circuit includes thermal protection. Refer to section Over-temperature protection. Operation above 140 °C may degrade

device reliability.

- 2. Applies to ceramic packages.

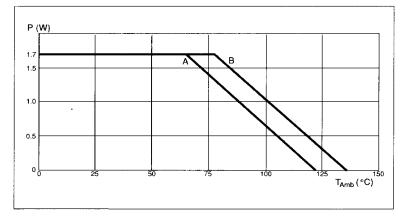

- 3. A power derating diagram is shown in figure 18. Values apply for momentary junction temperature of 120°C without heat sink.

- 4. The GND1 and GND2 pins should be connected together via a direct printed circuit board trace.

- V<sub>τ</sub> and V<sub>n</sub> are referenced to ground. t<sub>w</sub> is pulse width of a rectangular test pulse and t<sub>ren</sub> is pulse repetition rate.

- These voltage ratings require a diode to be installed in series with the V<sub>nat</sub> pin as shown in figure 11 (D<sub>7</sub>).

- 7.  $R_{E1}$ ,  $R_{E2} \ge 20$  ohms is also required. Pulse is supplied to TIP and RING outside  $R_{E1}$ ,  $R_{E2}$

- V<sub>Bat</sub> should be applied with a ∂V<sub>Bat</sub>/∂t < 4 V/µsec. A time constant of 2.6 µs is suggested (e.g. 5.6 ohms and 0.47 µF). The V<sub>Bat</sub> terminal must at all times be at a lower potential than any other terminal to maintain proper junction isolation. Refer to section Power-up sequence.

- 9. GND1 and GND2 must be connected before supply voltages.

### **Electrical characteristics**

$\begin{array}{l} 0\ ^{\circ}C\le T_{Amb}\le 70\ ^{\circ}C,\ V_{CC}=\pm 5\ V\ \pm 5\%,\ V_{EE}=-5V\ \pm 5\%,\ GND1=GND2,\ R_{DC1}=R_{DC2}=1.25\ kohms,\ R_{D}=51.1\ kohms,\ R_{CH}=910\ ohms,\ R_{Bat}=10\ ohms,\ C_{Hp}=0.22\ \mu F,\ C_{DC}=1.2\ \mu F,\ C_{D}=0.01\ \mu F,\ C_{TC}=C_{RC}=2200\ pF,\ C_{CH1}=0.047\ \mu F,\ C_{CH2}=1500\ pF,\ C_{Fl}=0.47\ \mu F,\ C_{Ba1}=0.47\ \mu F,\ C_{O}=0.33\ \mu F,\ L=1\ mH;\ \textbf{PBL}\ \textbf{3796:}\ -64.5\ V\le V_{Ba1}\le -61.5\ V,\ Z_{TR}\ (2-wire\ ac\ terminating\ impedance)=900\ ohms,\ R_{T}=R_{F2}=0\ ohm,\ R_{T}=90\ kohms,\ R_{RX}=45\ kohms;\ \textbf{PBL}\ \textbf{3796/2:}\ -58.0\ V\le V_{Ba1}\le -46.0\ V,\ Z_{TR}\ (2-wire\ ac\ terminating\ impedance)=600\ ohms,\ Z_{C}\ (line\ impedance)=600\ ohms,\ R_{F}=R_{F2}=0\ ohm,\ R_{T}=60\ kohms,\ R_{RX}=30\ kohms;\ unless\ otherwise\ specified. The\ specifications\ are\ with\ respect\ to\ exact\ external\ component\ values. \end{array}$

| Parameter                                                       | tig | Conditions                                      | Min  | Тур  | Max | Unit                    |

|-----------------------------------------------------------------|-----|-------------------------------------------------|------|------|-----|-------------------------|

| 2-wire port                                                     |     |                                                 |      |      |     |                         |

| Overload level, V <sub>TRO</sub>                                | 2   | 1% THD, E <sub>1</sub> = 0, f = 1 kHz,          | 3.1  | 3.5  |     | V <sub>Pk</sub>         |

|                                                                 |     | (Notes 1, 2)                                    | 7.2  | 8.3  |     | dBm                     |

|                                                                 |     |                                                 | 9.0  | 10.1 |     | dBu                     |

| Input impedance, Z <sub>TRX</sub>                               |     | Note 3                                          |      |      |     |                         |

| Longitudinal impedance, Z <sub>LoT</sub> , Z <sub>LoB</sub>     | 3   | f ≤ 100 Hz                                      |      | 25   | 40  | ohm/wire                |

| Longitudinal current limit, I <sub>LoT</sub> , I <sub>LoB</sub> |     | f ≤ 100 Hz                                      |      |      |     |                         |

|                                                                 |     | Active state                                    | 20   | 28   |     | mA <sub>rms</sub> /wire |

|                                                                 |     | Stand-by state                                  | 8.5  | 19   |     | mA <sub>rms</sub> /wire |

| Longitudinal to metallic balance, B <sub>LM</sub>               |     | IEEE Standard 455-1985                          |      |      | *   |                         |

|                                                                 |     | 0.2kHz < f < 3.4kHz, Note 4                     |      |      |     |                         |

|                                                                 |     | Normal polarity                                 | 63.0 | 70.0 |     | dB                      |

|                                                                 |     | Reversed polarity                               | 55.0 | 65.0 |     | dB                      |

| Metallic to longitudinal balance, B <sub>Mi</sub>               |     | FCC part 68 paragraph 68.310                    |      |      |     |                         |

|                                                                 |     | 1 kHz                                           |      |      |     | dB                      |

| Longitudinal to metallic balance, B <sub>LME</sub>              | 4   | 0.2kHz < f < 3.4kHz,                            |      |      |     |                         |

|                                                                 |     | $B_{LME} = 20 \cdot \log \frac{E_{Lo}}{V_{TR}}$ |      |      |     |                         |

|                                                                 |     | Normal polarity                                 | 63   | 70   |     | dB                      |

|                                                                 |     | Reversed polarity                               | 55   | 65   |     | dB                      |

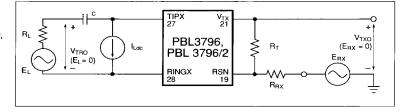

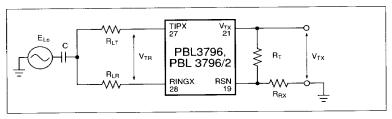

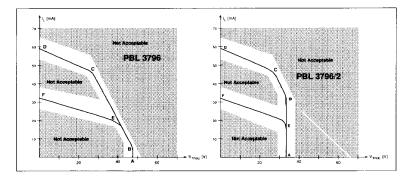

Figure 2. Overload level.

$1/\omega C \ll R_i$ ,

**PBL 3796:**  $R_L = 600 \text{ ohm}, R_T = 60 \text{ kohms},$

$R_{\rm BX} = 30 \text{ kohms.}$

**PBL 3796/2:** R<sub>L</sub> = 900 ohm,

$R_{\tau} = 90 \text{ kohms}, R_{Bx} = 45 \text{ kohms}.$

# PBL 3796, PBL 3796/2

| Parameter                                          | Ref<br>fig | Conditions                                                                            | Min   | Тур  | Max  | Unit |

|----------------------------------------------------|------------|---------------------------------------------------------------------------------------|-------|------|------|------|

| Longitudinal to four wire balance,B, FF            | 4          | 0.2kHz < f < 3.4kHz                                                                   |       |      |      |      |

|                                                    |            | $B_{LFE} = 20 \cdot \log \frac{E_{Lo}}{V_{TV}}$                                       |       |      |      |      |

|                                                    |            | Normal polarity                                                                       | 63    | 70   |      | dB   |

|                                                    |            | Reversed polarity                                                                     | 55    | 65   |      | dB   |

| Metallic to longitudinal balance, B <sub>MLE</sub> | 5          | $B_{MLE} = 20 \cdot \log \frac{E_{TR}}{V_{LO}}$ , $E_{RX} = 0$                        |       |      |      |      |

|                                                    |            | 0.2kHz < f < 4.0kHz                                                                   | 40    |      |      | dB   |

|                                                    |            | f = 1.0 kHz                                                                           |       | 53   |      | dB   |

| Four wire to longitudinal balance,B <sub>FLE</sub> | 5          | $B_{FLE} = 20 \cdot \log \frac{E_{RX}}{V_{LR}}$ , $E_{TR}$ source re                  | moved |      |      |      |

|                                                    |            | 0.2kHz < f < 4.0kHz                                                                   | 40    |      |      | dB   |

|                                                    |            | f = 1.0  kHz                                                                          |       | 53   |      | dB   |

| 2-wire return loss, r                              |            | $r = 20 \cdot \log \left  \frac{Z_L + Z_{TR}}{Z_1 - Z_{TR}} \right  , \text{ Note 5}$ |       |      |      |      |

|                                                    |            | 0.2kHz ≤ f < 0.5kHz                                                                   | 30    | 35   |      | dB   |

|                                                    |            | 0.5kHz ≤ f < 1.0kHz                                                                   | 25    | 30   |      | dB   |

|                                                    |            | $1.0kHz \le f \le 3.4kHz$                                                             | 15    | 21   |      | dB   |

| Polarity reversal time, t <sub>pol</sub>           |            | Normal to reversed polarity or                                                        |       | 4    | 15   | ms   |

| , and a por                                        |            | reversed to normal polarity                                                           |       |      |      |      |

| TIPX idle voltage, V <sub>Ti</sub>                 |            | Normal polarity                                                                       |       |      |      |      |

| 3 - 11                                             |            | $V_{Bat} = -63 \text{ V (PBL 3796)}$                                                  | -5.0  | -3.5 | -2.0 | V    |

|                                                    |            | V <sub>Bat</sub> = -48 V (PBL 3796/2)                                                 | -5.0  | -3.5 | -2.0 | V    |

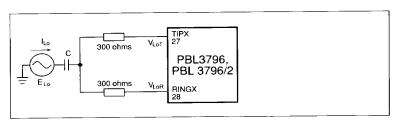

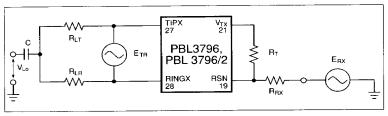

Figure 3. Longitudinal input impedance.  $Z_{LoT} = Z_{LoR} = \frac{V_{LoT} + V_{LoR}}{I_{I_{CA}}}$

Figure 4. Longitudinal-to-metallic ( $B_{\rm LME}$ ) and Longitudinal-to-four-wire ( $B_{\rm LFE}$ ) balance.

$1/\omega C \ll 150$  ohms,

**PBL 3796:**  $R_{LT} = R_{LR} = 450$  ohms,  $R_{T} = 90$  kohms,  $R_{RX} = 45$  kohms.

**PBL 3796/2:**  $R_{LT} = R_{LR} = 300$  ohms,  $R_{_{T}} = 60$  kohms,  $R_{_{RX}} = 30$  kohms.

Figure 5. Metallic-to-longitudinal ( $\mathcal{B}_{\text{MLE}}$ ) and four-wire-to-longitudinal ( $\mathcal{B}_{\text{FLE}}$ ) balance.

$1/\omega$  C << 150 ohms,

**PBL 3796:**  $R_{LT} = R_{LR} = 450$  ohms,  $R_{T} = 90$  kohms,  $R_{RX} = 45$  kohms.

**PBL 3796/2:**  $R_{LT} = R_{LR} = 300$  ohms,  $R_{T} = 60$  kohms,  $R_{RX} = 30$  kohms.

| Parameter                                   | Ref<br>fig | Conditions                                            | Min   | Тур   | Max   | Unit            |

|---------------------------------------------|------------|-------------------------------------------------------|-------|-------|-------|-----------------|

| RINGX idle voltage, V <sub>Ri</sub>         |            | Normal polarity                                       |       |       |       |                 |

|                                             |            | V <sub>Bat</sub> = -63 V (PBL 3796)                   | -54.5 | -51   | -48   | V               |

|                                             |            | V <sub>Bat</sub> = -48 V (PBL 3796/2)                 | -40   | -37   | -34   | ٧               |

| 4-wire transmit port (V <sub>τx</sub> )     |            |                                                       |       |       |       |                 |

| Overload level, V <sub>TX0</sub>            | 2          | Load impedance > 20 kohms,                            | 3.1   | 3.5   |       | V <sub>Pk</sub> |

| ···-                                        |            | $f = 1 \text{ kHz}$ , 1% THD, $E_{Rx} = 0$            | 9.0   | 10.1  |       | dBu             |

|                                             |            | Note 6                                                |       |       |       |                 |

| Output offset voltage, $\Delta V_{TX}$      |            |                                                       | -20   | ±5    | +20   | mV              |

| Output impedance, Z <sub>TX</sub>           |            | 0.2kHz ≤ f ≤ 3.4kHz                                   |       | 6     | 20    | ohm             |

| 4-wire receive port (RSN)                   |            |                                                       |       |       |       |                 |

| RSN dc voltage, V <sub>RSN</sub>            |            | I <sub>RSN</sub> = 0                                  | -10   | 0     | +10   | mV              |

| RSN impedance, Z <sub>RSN</sub>             |            | 0.2kHz ≤ f ≤ 3.4kHz                                   |       | 3     | 20    | ohm             |

| RSN current (I <sub>RSN</sub> ) to metallic |            | $0.2kHz \le f \le 3.4kHz$ ,                           |       | 40    |       | dB              |

| loop current (IL) gain, α <sub>RSN</sub>    |            | l,                                                    |       |       |       |                 |

|                                             |            | $\alpha_{RSN} = \frac{I_L}{I_{RSN}}$                  |       |       |       |                 |

| Frequency response                          |            |                                                       |       |       |       |                 |

| Two-wire to four-wire, g <sub>2,4</sub>     | 6          | 0.3kHz ≤ f ≤ 3.4kHz                                   | -0.1  | ±0.03 | +0.1  | dB              |

| 52.4                                        |            | Relative to 1.0 kHz, 0 dBu                            |       |       |       |                 |

|                                             |            | E <sub>Bx</sub> = 0 V, (Notes 2, 7)                   |       |       |       |                 |

| Four-wire to two-wire, g <sub>4-2</sub>     | 6          | 0.3kHz ≤ f ≤ 3.4kHz                                   | -0.1  | ±0.03 | +0.1  | dB              |

| , -                                         |            | Relative to 1.0 kHz, 0 dBu                            |       |       |       |                 |

|                                             |            | E <sub>1</sub> = 0 V, (Notes 2, 8, 14)                |       |       |       |                 |

| Four-wire to four-wire, g <sub>4-4</sub>    | 6          | 0.3kHz ≤ f ≤ 3.4kHz                                   | -0.1  | ±0.06 | +0.1  | dB              |

|                                             |            | Relative to 1.0 kHz, 0 dBu                            |       |       |       |                 |

|                                             |            | E <sub>L</sub> = 0 V, (Notes 2, 8, 14)                |       |       |       |                 |

| Insertion loss                              |            |                                                       |       |       |       |                 |

| Two-wire to four-wire, G <sub>2-4</sub>     | 6          | 0 dBu, 1 kHz, E <sub>RX</sub> = 0, (Notes 7, 9)       | -0.15 | ±0.1  | +0.15 | dB              |

| Four-wire to two-wire, G <sub>4-2</sub>     | 6          | 0 dBu, 1 kHz, E <sub>1</sub> = 0, (Notes 8, 9)        | -0.15 | ±0.1  | +0.15 | dB              |

| Four-wire to four-wire, G <sub>4-4</sub>    | 6          | 0 dBu, 1 kHz, E <sub>L</sub> = 0, (Notes 8, 9)        | -0.15 | ±0.1  | +0.15 | dB              |

| Gain Tracking                               |            |                                                       |       |       |       |                 |

| Two-wire to four-wire (Note 7) and          | 6          | Referenced to -10 dBu, 1 kHz                          |       |       |       |                 |

| Four-wire to two-wire (Note 8)              |            | +3 dBu to -30 dBu                                     | -0.1  |       | +0.1  | dB              |

|                                             |            | -30 dBu to -55 dBu                                    |       | ±0.1  |       | dB              |

| Noise                                       |            |                                                       |       |       |       |                 |

| ldle channel noise at two-wire              | 6          | E <sub>RX</sub> = E <sub>L</sub> = 0, Notes 2, 10, 14 |       |       |       |                 |

| (TIPX-RINGX) or four-wire ( $V_{TX}$ ) port |            | C-msg weighting                                       |       | 10    | 14    | dBrnC           |

|                                             |            | Psophometrical weighting                              |       | -80   | -76   | dBup            |

| Single frequency out-of-band noise (N       | Note 11)   |                                                       |       |       |       |                 |

| Metallic, V <sub>TR</sub>                   | 7          | 12 kHz ≤ f ≤ 1 MHz                                    |       | -58   | -55   | dBV             |

| Longitudinal, V <sub>Lo</sub>               | 7          | 12 kHz ≤ f ≤ 90 kHz                                   |       | -68   | -63   | dBV             |

| Longitudinal, V <sub>Lo</sub>               | 7          | 90 kHz ≤ f ≤ 1 MHz                                    |       | -53   | -50   | dBV             |

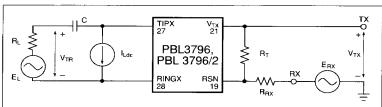

Figure 6. Frequency response, insertion loss, gain tracking, idle channel noise, THD, inter-modulation.

$1/\omega C \ll R_L$

**PBL 3796:**  $R_L = 900$  ohms,  $R_T = 90$  kohms,  $R_{BX} = 45$  kohms.

**PBL 3796/2:**  $R_{\rm L} = 600$  ohms,  $R_{\rm T} = 60$  kohms,  $R_{\rm RX} = 30$  kohms.

# PBL 3796, PBL 3796/2

| Parameter                                                       | Ref<br>fig | Conditions                                                      | Min                 | Тур                 | Max                 | Unit      |

|-----------------------------------------------------------------|------------|-----------------------------------------------------------------|---------------------|---------------------|---------------------|-----------|

| Total Harmonic Distortion                                       |            |                                                                 |                     |                     |                     | - 10      |

| Two-wire to four-wire,                                          | 6          | 0.3kHz ≤ f ≤ 3.4kHz                                             |                     | -64                 | -50                 | dB        |

| Four-wire to two-wire                                           |            | 0 dBu, 1 kHz test signal, Note 2                                |                     |                     |                     |           |

| Intermodulation                                                 |            |                                                                 |                     |                     |                     |           |

| Type 2f <sub>1</sub> - f <sub>2</sub>                           | 6          | $0.3 \text{ kHz} < f_1, f_2 < 3.4 \text{ kHz},$                 |                     |                     |                     |           |

|                                                                 |            | Level $f_1 = \text{level } f_2 = -25 \text{ to } 0 \text{ dBv}$ |                     |                     |                     |           |

|                                                                 |            | $f_1 \neq nf_2, f_2 \neq nf_1, \text{ Note 2}$                  |                     | 20                  | 50                  | dB        |

| Two-wire to four-wire                                           |            | $E_{RX} = 0$                                                    |                     | -60                 | -50<br>-50          | dB        |

| Four-wire to two-wire                                           |            | $E_L = 0$                                                       |                     | -60                 | -30                 | ub        |

| Type f <sub>1</sub> ±50 Hz                                      | 6          | 0.3kHz < f <sub>1</sub> < 3.4kHz                                |                     |                     |                     |           |

|                                                                 |            | Level 50 Hz = level f <sub>1</sub> - 14 dB,                     |                     |                     |                     |           |

|                                                                 |            | Level f <sub>1</sub> = -15 dBv to 0 dBv                         |                     |                     |                     |           |

|                                                                 |            | f <sub>1</sub> ≠ n • 50 Hz, Note 2                              |                     | -65                 | -50                 | dB        |

| Two-wire to four-wire                                           |            | E <sub>RX</sub> = 0                                             |                     | -65                 | -50                 | <u>ав</u> |

| Battery Feed Characteristics                                    |            |                                                                 |                     |                     |                     |           |

| Apparent battery voltage, E <sub>BAp</sub>                      |            | Active state                                                    | 47.5                | 50                  | 52.5                | V         |

| <u> </u>                                                        |            | Active, polarity reversal state                                 | -52.5               | -50                 | -47.5               | V         |

| Feed resistance (R <sub>Feed</sub> )                            |            | Active and                                                      | 4.75                | 5.00                | 5.25                | Ratio     |

| to programming resistance (R <sub>DC1</sub> +R <sub>DC2</sub> ) |            | active, polarity reversal state                                 |                     |                     |                     |           |

| conversion factor, K <sub>1</sub>                               |            |                                                                 |                     |                     |                     |           |

|                                                                 |            | $K_1 = \frac{R_{DC1} + R_{DC2}}{R_{Feed}}$                      |                     |                     |                     |           |

| Active state short circuit loop                                 |            | $R_{po1} + R_{po2} = 2.5 \text{ kohms}$                         | 53                  | 59                  | 65                  | mA        |

| current, I <sub>LShAct</sub>                                    |            | 145                                                             |                     |                     |                     |           |

| LSIIACI                                                         |            | $I_{LShAct} = \frac{145}{R_{DC1} + R_{DC2}}$                    |                     |                     |                     |           |

| Active state loop current limiting                              |            | $R_{DC1} + R_{DC2} = 2.5 \text{ kohms}$                         |                     | 46                  |                     | mA        |

| threshold, ILLIMACT                                             |            | $I_{LLimAct} = \frac{115}{R_{DC1} + R_{DC2}}$ , Note 12         |                     |                     |                     |           |

|                                                                 |            | 'LLimAct R <sub>DC1</sub> + R <sub>DC2</sub>                    |                     |                     |                     |           |

| Stand-by state short circuit loop                               |            | $R_{DC1} + R_{DC2} = 2.5 \text{ kohms}$                         | 26                  | 32                  | 38                  | mA        |

| current, I <sub>LShSb</sub>                                     |            | $I_{LShSb} = \frac{80}{R_{DC1} + R_{DC2}}$                      |                     |                     |                     |           |

|                                                                 |            | Lanan H <sub>DC1</sub> + H <sub>DC2</sub>                       |                     | 18                  |                     | mA        |

| Stand-by state loop current limiting                            |            | $R_{DC1} + R_{DC2} = 2.5 \text{ kohms}$                         |                     | 10                  |                     | ША        |

| threshold, I <sub>LLimSb</sub>                                  |            | $I_{LLimSb} = \frac{45}{R_{DC1} + R_{DC2}}$ , Note 12           |                     |                     |                     |           |

| Tip open circuit state                                          |            | 501 502                                                         |                     |                     |                     |           |

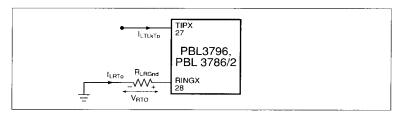

| Tip open circuit state  TIPX current, I <sub>LTLkTo</sub>       | 8          | Tip open circuit state                                          | -100                | ±5                  | 100                 | μA        |

| RINGX current, I <sub>LRTo</sub>                                | 8          | Tip open circuit state                                          |                     |                     |                     |           |

| Till Carrent, I <sub>LRTo</sub>                                 | _          | R <sub>LRGnd</sub> = 0 ohm                                      | 23                  | 35                  | 50                  | mA        |

|                                                                 |            | R <sub>LRGnd</sub> = 2.5 kohms                                  |                     |                     |                     |           |

|                                                                 |            | V <sub>Bat</sub> = -63 V (PBL 3796)                             | 22                  | 24                  |                     | mA        |

|                                                                 |            | $V_{Bat} = -48 \text{ V (PBL } 3796/2)$                         | 16                  | 18                  |                     | mA        |

| RINGX voltage, V <sub>RTo</sub>                                 | - 8        | I <sub>LRTo</sub> < 23 mA                                       | V <sub>Bat</sub> +1 | V <sub>Bai</sub> +4 | V <sub>eat</sub> +6 | V         |

|                                                                 |            | LITTO                                                           |                     |                     |                     |           |

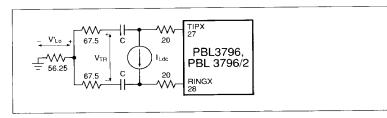

Figure 7. Single-frequency out of band noise. Resistance values in ohms,  $V_{Lo} = 1.6 \cdot V'_{Lo}$   $1/\omega C << 100 \text{ ohms}$

| Parameter                                                        | Ref<br>fig | Conditions                                                                                    | Min                   | Тур                   | Max                   | Unit |

|------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------|

| Loop Current Detector                                            |            |                                                                                               |                       |                       |                       |      |

| Tolerance with respect to                                        |            | Active, stand-by and                                                                          | -15                   |                       | 15                    | %    |

| programmed threshold, ILTROM                                     |            | polarity reversal states                                                                      |                       |                       |                       |      |

|                                                                  |            | Tip open circuit state                                                                        | -20                   |                       | 20                    | %    |

|                                                                  |            | Note 15                                                                                       |                       |                       |                       |      |

| Hysteresis, ∂I <sub>LTh</sub>                                    |            | Active, stand-by and                                                                          | 0.4                   | 0.9                   | 1.4                   | mA   |

|                                                                  |            | polarity reversal states,                                                                     |                       |                       |                       |      |

|                                                                  |            | $R_D = 51.1$ kohms, Note 16                                                                   |                       |                       |                       |      |

| Dial pulse distortion                                            |            | 10 pps, Off-hook: 900 ohms                                                                    |                       | 1                     | 5                     | %    |

|                                                                  |            | On-hook: ∞ ohms                                                                               |                       |                       |                       |      |

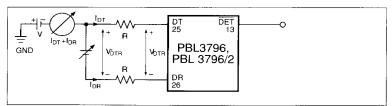

| Ring Trip Comparator Inputs (DT, DR)                             |            |                                                                                               |                       |                       |                       |      |

| Offset voltage, ΔV <sub>DIB</sub>                                | 9          | $V_{Bat} + 1 V < V_{DT}, V_{DR} < -2 V$                                                       |                       |                       |                       |      |

| <u></u>                                                          |            | R = 0 kohm                                                                                    | -20                   | ±10                   | 20                    | mV   |

|                                                                  |            | R = 200 kohm                                                                                  | -40                   | ±10                   | 40                    | mV   |

| Input offset current, ΔI <sub>B</sub>                            | 9          | $V_{Bat} + 1 V < V_{DT}, V_{DH} < -2 V$<br>$V_{Bat} + 1 V < V_{DT}, V_{DH} < -2 V,$           |                       | 0.05                  | 1                     | μА   |

| Input bias Current, I <sub>B</sub>                               | 9          |                                                                                               |                       | 0.1                   | 1                     | μА   |

| Input resistance                                                 |            | $I_B = (I_{DT} + I_{DH})/2$<br>$V_{Bat} + 1 V < V_{DT}, V_{DH} < -2 V$                        |                       |                       | -                     |      |

| unbalanced, R <sub>p.r</sub> , R <sub>p.s</sub>                  |            |                                                                                               | 1                     |                       |                       | Mohm |

| balanced, R <sub>DTR</sub>                                       |            |                                                                                               | 3                     |                       |                       | Mohm |

| Common mode range, V <sub>DT</sub> , V <sub>DR</sub>             |            |                                                                                               | V <sub>Bat</sub> +1   |                       | -2                    | V    |

| Relay Driver Outputs (RINGRLY, TEST                              | RLY)       |                                                                                               |                       |                       |                       |      |

| On state voltage, V <sub>TRIY</sub> , V <sub>RRIY</sub>          |            | $I_{TRly}$ , $I_{RRLy} = 25 \text{ mA}$<br>$0^{\circ}\text{C} < T_{Amb} < 25^{\circ}\text{C}$ |                       |                       |                       |      |

|                                                                  |            | $0^{\circ}\text{C} < \text{T}_{Amb} < 25^{\circ}\text{C}$                                     | V <sub>cc</sub> - 2.0 | V <sub>cc</sub> - 1.8 |                       | V    |

|                                                                  |            | $25^{\circ}\text{C} < \text{T}_{\text{Amb}} < 70^{\circ}\text{C}$                             | V <sub>cc</sub> - 1.8 | V <sub>cc</sub> - 1.6 | V <sub>cc</sub> - 1.0 | ٧    |

| Off state leakage current, I <sub>TRIy</sub> , I <sub>RRLy</sub> |            | $V_{TRIy}, V_{RRIy} = V_{Bat}$                                                                |                       | 5                     | 100                   | μА   |

| Clamp voltage                                                    |            | $I_{TRIy}$ , $I_{RRLy} = 25 \text{ mA}$                                                       | V <sub>Bat</sub> - 3  |                       | V <sub>Bat</sub> - 1  | V    |

| Digital Inputs (C1-C4, E0, CHCLK)                                |            |                                                                                               |                       |                       |                       |      |

| Input low voltage, V <sub>IL</sub>                               |            |                                                                                               |                       |                       | 0.8                   | ٧    |

| Input high voltage, V <sub>IH</sub>                              |            |                                                                                               | 2.0                   |                       |                       | ٧    |

| Input low current, I <sub>IL</sub>                               |            | $V_{IL} = 0.4 \text{ V}$<br>$V_{IH} = 2.4 \text{ V}$                                          | -0.4                  |                       |                       | mA   |

| Input high current, I,,,                                         |            | V - 24 V                                                                                      |                       |                       | 40                    | μА   |

Dof

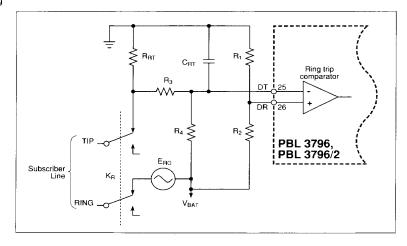

Figure 8. Tip open circuit state.

Figure 9. Ring trip comparator.  $2V < V < |V_{Bat} + 1|,$   $\frac{I_{DT} + I_{DR}}{2} = I_{B},$   $V'_{DTR} = \Delta V_{DTR},$   $V'_{DTR} - V_{DTR}$

# PBL 3796, PBL 3796/2

| Parameter                                              | Ref<br>fig | Conditions                                           | Min | Тур | Max  | Unit       |

|--------------------------------------------------------|------------|------------------------------------------------------|-----|-----|------|------------|

| Digital output (DET)                                   |            |                                                      |     |     |      |            |

| Output low voltage, V <sub>OL</sub>                    |            | I <sub>OL</sub> = 1.0 mA                             |     |     | 0.45 | V          |

| Output high voltage, V <sub>GH</sub>                   |            | I <sub>OH</sub> = -0.1 mA                            | 2.4 |     |      | V          |

| Resistive pull-up                                      |            |                                                      | 12  | 15  | 18   | kohm       |

| Switch Mode Regulator Transistor Ou                    | tput (L    | )                                                    |     |     |      |            |

| Switch transistor saturation voltage, V <sub>isa</sub> | t          | I <sub>i</sub> = 100 mA, Note 17                     |     |     | 1.5  | V          |

| Leakage current, IILk                                  |            | V <sub>1</sub> = 0 V                                 |     |     | 200  | μ <b>А</b> |

| Switch Mode Regulator Clock Input (                    | CHCLK      | <b>)</b>                                             |     |     |      |            |

| Clock frequency, f <sub>ChClk</sub>                    |            |                                                      | 253 | 256 | 259  | kHz        |

| Power supply rejection ratio (PSRR)                    |            |                                                      |     |     |      | _          |

| V <sub>cc</sub> to two-wire port and                   |            | saturation guard off                                 |     |     |      |            |

| V <sub>cc</sub> to four-wire port                      |            | 50 Hz < f < 4 kHz                                    | 35  |     |      | dB         |

| rejection ratio, PSRR <sub>cc</sub>                    |            | 4 kHz < f < 50 kHz                                   | 20  |     |      | dB         |

| 10,000.0.1.141.0, 1 0111.160                           |            | saturation guard on                                  |     |     |      |            |

|                                                        |            | 50 Hz < f < 50 kHz                                   | 30  |     |      | dB         |

|                                                        |            | Note 18                                              |     |     |      |            |

| V <sub>EF</sub> to two-wire port and                   |            | saturation guard off                                 |     |     |      |            |

| V <sub>EE</sub> to four-wire port                      |            | 50 Hz < f < 50 kHz                                   | 18  |     |      | dB         |

| rejection ratio, PSRR <sub>EE</sub>                    |            | saturation guard on                                  |     |     |      |            |

| rejection fallo, FShN <sub>EE</sub>                    |            | 50 Hz < f < 50 kHz                                   | 10  |     |      | dB         |

|                                                        |            | Note 18                                              |     |     |      |            |

| V to two wire port and                                 |            | Note 18                                              |     |     |      |            |

| V <sub>Bat</sub> to two-wire port and                  |            | 50 Hz < f < 4 kHz                                    | 25  |     |      | dB         |

| V <sub>Bat</sub> to four-wire port                     |            | 4 kHz < f < 50 kHz                                   | 20  |     |      | dB         |

| rejection ratio, PSRR <sub>Bat</sub>                   |            | 4 KHZ C I C 30 KHZ                                   |     |     |      |            |

| Power supply currents (relay drivers                   | off)       | On- or off-hook, active state                        |     | 8   | 12   | mA         |

| V <sub>cc</sub> supply current, I <sub>cc</sub>        |            | On- or off-hook, active state                        |     | 6   | 9    | mA         |

| V <sub>EE</sub> supply current, I <sub>EE</sub>        |            |                                                      |     | 3.5 | 6    | mA         |

| V <sub>Bat</sub> supply current, I <sub>Bat</sub>      |            | On-hook, active state                                |     | 3.3 |      | 1005       |

| Power dissipation (PBL 3796)                           |            | N CO V O size it state                               |     | 70  | 100  | mW         |

| On-hook total dissipation, P <sub>OnOp</sub>           |            | V <sub>Bat</sub> = -63 V, Open circuit state         |     | 225 | 275  | mW         |

| On-hook total dissipation, P <sub>OnSb</sub>           |            | V <sub>Bat</sub> = -63 V, Stand-by state             |     | 275 | 350  | mW         |

| On-hook total dissipation, P <sub>OnAct</sub>          |            | V <sub>Bat</sub> = -63 V, Active state               |     |     | 1000 | mW         |

| Off-hook total dissipation, P <sub>Off95</sub>         |            | V <sub>Bat</sub> = -63 V, Active state               |     | 750 | 1000 | ITIVV      |

|                                                        |            | $R_{L}$ = 900 ohms, $R_{Feed}$ = 500 ohms<br>Note 19 |     |     |      |            |

| Power dissipation (PBL 3796/2)                         |            |                                                      | •   |     |      |            |

| On-hook total dissipation, Ponop                       |            | V <sub>Bat</sub> = -48 V, Open circuit state         |     | 60  | 100  | mW         |

| On-hook total dissipation, P <sub>OnSb</sub>           | -          | V <sub>Bat</sub> = -48 V, Stand-by state             |     | 190 | 250  | mW         |

| On-hook total dissipation, P <sub>OnAct</sub>          |            | V <sub>Bat</sub> = -48 V, Active state               |     | 275 | 350  | mW         |

| Off-hook total dissipation, Poffes                     |            | V <sub>Bat</sub> = -48 V, Active state               |     | 750 | 1000 | mW         |

| Off95                                                  |            | $R_{L} = 600$ ohms, $R_{Eeed} = 500$ ohms            |     |     |      |            |

|                                                        |            | Note 19                                              |     |     |      |            |

| Temperature guard                                      |            |                                                      |     |     |      | <u> </u>   |

| Junction temperature at threshold, T                   |            |                                                      | 135 | 140 | 145  | °C         |

| Temperature guard hysteresis, $\partial T_{16}$        |            |                                                      |     | 10  |      | °C         |

### **Notes**

- The overload level is specified at the two-wire port with the signal source at the four-wire receive port, i.e. E<sub>L</sub> = 0 in figure 2.

- dBm is the ratio between power level P and a 1 mW reference power level, expressed in decibels, i.e.

$$dBm = 10 \cdot \log_{10} \frac{P}{1 \text{ mW}}$$

dBu is the ratio between voltage Vrms and a 0.775 Vrms reference, expressed in decibels, i.e.

$$dBu = 20 \cdot log_{10} \frac{Vrms}{0.775 Vrms}$$

dBu = dBm at impedance level 600 ohms

dBv is the ratio between voltage V and and a 1 V reference, expressed in decibels, i.e.

$$dBv = 20 \cdot \log_{10} \frac{V}{1 V}$$

dBup is the ratio between voltage  $V_{\rm p}$ , measured via a psophometrical filter and and a 0.775 Vrms reference, expressed in decibels, i.e.

$$dBup = 20 \cdot log_{10} \frac{V_p}{0.775 \text{ Vrms}}$$

dBrnC is the ratio between power level  $P_{\rm C}$ , measured via a C-message filter and a 1 pW reference power level, expressed in decibels, i.e.

$$dBrnC = 10 \cdot log_{10} \frac{P_C}{1 pW}$$

The two-wire impedance, Z<sub>TRX</sub>, is programmable by selection of external component values according to:

$$Z_{TRX} = Z_T / (G_{2.4} \cdot \alpha)$$

$Z_{\text{TRX}}$  = impedance between the TIPX and RINGX terminals  $Z_{\text{T}}$  = programming network between the  $V_{\text{TX}}$  and RSN terminals

$G_{2-4}$  = transmit gain, nominally = 1 (0 dB ±0.15 dB)

$\alpha$  = receive current gain, nominally = 100 (40 dB ±0.15 dB) The fuse resistors  $R_{\rm F}$  add to the impedance presented by the SLIC at terminals TIPX and RINGX for a total two-wire impedance of  $Z_{\rm TR}$  =  $Z_{\rm TRX}$  +  $2R_{\rm F}$ .

- Normal polarity is defined as the tip lead being at a more

positive potential than the ring lead. Reversed polarity is

defined as the ring lead being at a more positive potential

than the tip lead.

- 5. Higher return loss values can be achieved by adding a reactive component to R<sub>T</sub>, the two-wire terminating impedance programming resistor, e.g. by dividing R<sub>T</sub> into two equal halves and connecting a capacitor from the common point to ground. For R<sub>T</sub> = 90 kohms the capacitance value is approximately 220 pF.

- The overload level, V<sub>TXO</sub>, is specified at the four-wire transmit port, V<sub>TX</sub>, with the signal source at the two-wire port. Note that the gain from the two-wire port to the fourwire transmit port is G<sub>2.4</sub> = 1.

- 7. The level is specified at the two-wire port.

- The level is specified at the four-wire receive port (RX).

- Fuse resistors R<sub>F</sub>, and R<sub>F2</sub> impact the insertion loss as explained in the text, section Transmission. The specified insertion loss is for R<sub>F1</sub> = R<sub>F2</sub> = 0 ohm.

- The two-wire idle noise is specified with the port terminated in 900 ohms (R<sub>L</sub>) and with the four-wire receive port grounded (E<sub>RX</sub> = 0, E<sub>L</sub> = 0; see figure 6).

The four-wire idle noise at  $V_{TX}$  is specified with the two-wire port terminated in 900 ohms  $(R_L)$ . The four-wire receive port is grounded  $(E_{RX} = 0, E_L = 0)$ ; see figure 6).

The idle channel noise degrades by approximately 5 dB when the saturation guard is active. Refer to section Battery feed for a description of the saturation guard.

- These specifications are valid for a longitudinal impedance of 90 ohms and a metallic impedance of 135 ohms.

- When the loop current exceeds the limiting threshold the line feed changes from resistive feed (R<sub>Feed</sub> = (R<sub>DC1</sub> + R<sub>DC2</sub>)/5) to nearly constant current feed.

- This parameter degrades when the saturation guard is active.

- 15. Loop current at the detector threshold, active and active reversed polarity and stand-by states (nominal values):

$I_{\rm LThOH}$  (detector threshold for on-hook to off-hook transition) = 465/R  $_{\rm O}$

$I_{\rm LThOn}$  (detector threshold for off-hook to on-hook transition) = 410/ $R_{\rm D}$ .

Loop current at the detector threshold, tip open circuit state (nominal values):

$I_{L_{RThOff}}$  (detector threshold for on-hook to off-hook transition) = 930/R<sub>D</sub>

$I_{LRThOn}$  (detector threshold for off-hook to on-hook transition) = 820/ $R_{\rm p}$ .

- 16. The loop current detector threshold hysteresis is a function of the  $\rm R_{\rm h}$  value. Refer to note 15 above.

- 17.  $V_{ISat}$  is the voltage across the saturated transistor, i.e. between terminals  $V_{Bat}$  and L.

- Power supply rejection ratio test signal is 100 mVrms (sinusoidal).

- 19. Fuse resistor  $R_{E_1} = R_{E_2} = 0$  ohm.

## **Pin Description**

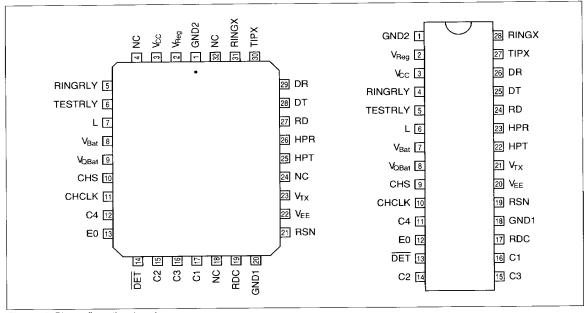

DIP: 28-pin dual in-line. LCC: 32-pin leadless chip carrier. Refer to figure 10.

| DIP | LLCC | Symbol            | Description                                                                                                                                                                                                                                                                                                         |

|-----|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 1    | GND2              | Ground. No internal connection to GND1 (pin 18). Note 1.                                                                                                                                                                                                                                                            |

| 2   | 2    | $V_{Reg}$         | Regulated negative voltage for power amplifiers. The switch-mode regulator inductor, filter capacitor and RC stabilization network connect to this pin.                                                                                                                                                             |

| 3   | 3    | V <sub>cc</sub>   | +5 V power supply.                                                                                                                                                                                                                                                                                                  |

| _   | 4    | NC                | No internal connection. Note 2.                                                                                                                                                                                                                                                                                     |

| 4   | 5    | RINGRLY           | Ring relay driver output. Sources up to 80 mA from Vcc.                                                                                                                                                                                                                                                             |

| 5   | 6    | TESTRLY           | Test relay driver output. Sources up to 80 mA from Vcc.                                                                                                                                                                                                                                                             |

| 6   | 7    | L                 | Switch-mode regulator drive transistor output. The 1 mH inductor and the catch diode connect to this pin. These components must be connected with shortest possible lead lengths. The catch diode, including connecting leads, must exhibit a low inductance to clamp effectively, when the regulator switch opens. |

| 7   | 8    | $V_{\rm Bat}$     | Battery supply voltage. Negative with respect to GND2, pin 1.                                                                                                                                                                                                                                                       |

| 8   | 9    | V <sub>QBat</sub> | Quiet battery. An external filter capacitor connects between this pin and GND1 to provide filtered battery supply to signal processing circuits.                                                                                                                                                                    |

| 9   | 10   | CHS               | Switch-mode regulator stabilization network input. From this pin a capacitor connects to GND1 and a series RC network to $V_{\rm Red}$ , pin 2.                                                                                                                                                                     |

| 10  | 11   | CHCLK             | Switch-mode regulator TTL compatible clock input. Nominal frequency: 256 kHz                                                                                                                                                                                                                                        |

| 11  | 12   | C4                | C1 (pin 16), C2 (pin 14), C3 (pin 15) and C4 are TTL compatible decoder inputs controlling the SLIC operating states.                                                                                                                                                                                               |

| 12  | 13   | E0                | Detector output enable. A logic high level enables the $\overline{\text{DET}}$ (pin 13) output. A logic low level disables the $\overline{\text{DET}}$ output. TTL compatible input.                                                                                                                                |

Figure 10. Pin configuration, top view.

| DIP | LLCC | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | 14   | DET          | Detector output. Inputs C1 C3 select the detector to be connected to this output. When $\overline{DET}$ is enabled via E0 (pin 12) a logic low level indicates that the selected detector is tripped. The $\overline{DET}$ output is open collector with internal pull-up resistor (15 kohms) to $V_{cc}$ (pin 3). When disabled, $\overline{DET}$ thus appears to be a resistor connected to $V_{cc}$ .                             |

| 14  | 15   | C2           | Refer to pin 11 description.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | 16   | C3           | Refer to pin 11 description.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16  | 17   | C1           | Refer to pin 11 description.                                                                                                                                                                                                                                                                                                                                                                                                         |

| _   | 18   | NC           | No internal connection. Note 2.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17  | 19   | RDC          | Dc loop feed resistance is programmed by two resistors connected in series from this pin to the receive summing node (RSN, pin 19). The resistor junction point is decoupled to GND1 to filter noise and other disturbances before reaching the RSN input. $V_{\rm RDC}$ polarity is negative for normal tip-ring polarity and positive for reversed tip-ring polarity. $ V_{\rm RDC}  =  ( V_{\rm Tdc} - V_{\rm Rdc} /20) - 2.5 $ . |

| 18  | 20   | GND1         | Ground. No internal connection to GND2 (pin 1). Note 1.                                                                                                                                                                                                                                                                                                                                                                              |

| 19  | 21   | RSN          | Receive summing node. 100 times the current (dc and ac) flowing into this pin equals the metallic (transversal) current flowing between the TIPX (pin 27) and RINGX (pin 28) terminals. Programming networks for feed resistance, 2-wire impedance, and receive gain connect to the receive summing node.                                                                                                                            |

| 20  | 22   | $V_{EE}$     | -5 V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21  | 23   | $V_{\tau_X}$ | Transmit vf output. The ac voltage difference between TIPX (pin 27) and RINGX (pin 28), the ac metallic voltage, is reproduced as an unbalanced GND1 referenced signal at $V_{TX}$ with a gain of one. The two-wire impedance programming network connects between $V_{TX}$ and RSN (pin 19).                                                                                                                                        |

| _   | 24   | NC           | No internal connection. Note 2.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22  | 25   | HPT          | Tip side of ac/dc separation capacitor $(C_{HP})$ .                                                                                                                                                                                                                                                                                                                                                                                  |

| 23  | 26   | HPR          | Ring side of ac/dc separation capacitor $(C_{HP})$ .                                                                                                                                                                                                                                                                                                                                                                                 |

| 24  | 27   | RD           | Loop current detector programming resistor, $R_{\rm D}$ , connects from RD to $V_{\rm EE}$ (pin 20). A filter capacitor $C_{\rm D}$ may be connected from RD to GND1.                                                                                                                                                                                                                                                                |

| 25  | 28   | DT           | Inverting ring trip comparator input.                                                                                                                                                                                                                                                                                                                                                                                                |

| 26  | 29   | DR           | Non-inverting ring trip comparator input.                                                                                                                                                                                                                                                                                                                                                                                            |

| 27  | 30   | TIPX         | The TIPX pin connects to the tip lead of the 2-wire line interface via overvoltage protection components, ring and test relays.                                                                                                                                                                                                                                                                                                      |

| 28  | 31   | RINGX        | The RINGX pin connects to the ring lead of the 2-wire line interface via overvoltage protection components, ring and test relays.                                                                                                                                                                                                                                                                                                    |