# MOS INTEGRATED CIRCUIT $\mu PD1711CU, \mu PD1712CU$

# SINGLE-CHIP MICROCOMPUTER WITH A DIGITAL PHASE-LOCKED-LOOP FREQUENCY SYNTHESIZER

$\mu$ PD1711 and  $\mu$ PD1712 are 4-bit digital tuning CMOS microcomputers incorporating a Phased Locked Loop (PLL) and controller in a chip. They can be connected directly to a fluorescent indicator panel.

The CPU has 4-bit parallel addition and subtraction instructions (AD and SU), logical operation instructions (such as EXL), bit test instructions (such as TMT), carry F/F set and reset instructions (such as STC), interrupt function, and timer function.

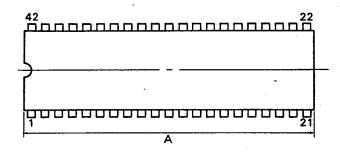

Each chip is made of a 42-pin shrink DIP provided with sufficient I/O ports controlled with effective input/output instructions (such as IN and OUT), 8-bit serial interface (serial I/O and shift CLOCK) of the  $\mu$ COM standard, 6-bit A/D converter, and Clock Generator Port (CGP) with variable frequency and duty.

The A/D converter for FM/AM tuning can input the signal meter data output from the IF detection stage to determine the electric field intensity or the automatic tuning stop level.

The A/D converter for TV is applicable to various fields as a pin to input S-shaped curves for Automatic Fine Tuning (AFT).

The CGP can be used as a simple 64-step D/A converter by adding a Low Pass Filter (LPF) in output stage or used as a 128-step frequency generator pin.

$\mu$ PD1711 and  $\mu$ PD1712 only differ in their ROM capacities.

### **FEATURES**

- 4-bit microcomputer for digital tuning

- Built-in PLL and controller

- Single power supply of 5 V ±10 %

- Low power consumption CMOS

- Easy data memory (RAM) backup (with CE pin)

- Programmable memory (ROM): 16 bits x 1016 steps (μPD1711)

16 bits x 2040 steps ( $\mu$ PD1712)

- Data memory (RAM): 4 bits x 128 (= 2 x 64) words

- Eighty-five 1-word instructions

- Instruction execution time: 33.3 μs (4.5 MHz crystal oscillator)

- Ample addition and subtraction instructions (12 addition instructions and 12 subtraction instructions)

- Compound decision instructions (such as TMT and TMF)

- Memory-to-memory data transfer enabled at same row address

- Instructions for indirect data transfer between registers (such as MVRD and MVRS).

- Sixteen general registers (allocated in RAM space)

- Stack level: 3 levels

- Dedicated pin for display and key input (dynamic display in six 7-segment digits)

- Direct drive of Fluorescent Indicator Panel (FIP) (segments only)

- Segments (Sa to Sg) P-ch open drain output (maximum with stand voltage: 35 V)

- ullet Clock stop instruction (CKSTP) (Power supply current reduced to less than 10  $\mu$ A)

NEC cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

© 1986 NEC Corporation

# REPORT REPORT TAZCU

- Four I/O lines (PA3 to PA0) individual lines can be configured as input or output.

- Eight output lines (PB3 to PB0 and PC3 to PC0) N-ch open drain output port.

- Built-in serial interface (PA<sub>3</sub> = shift clock, PA<sub>2</sub> = serial input, PB<sub>0</sub> = serial output) for data transfer in 8-bit units by SIO instruction

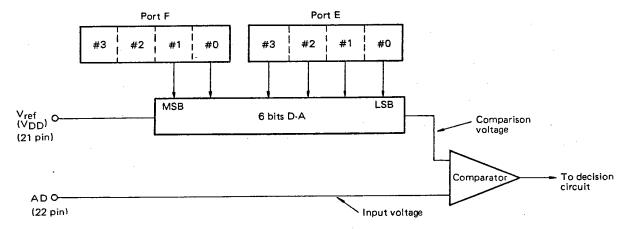

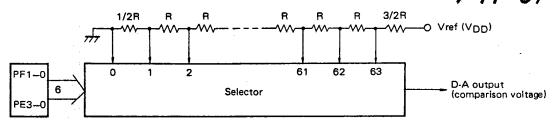

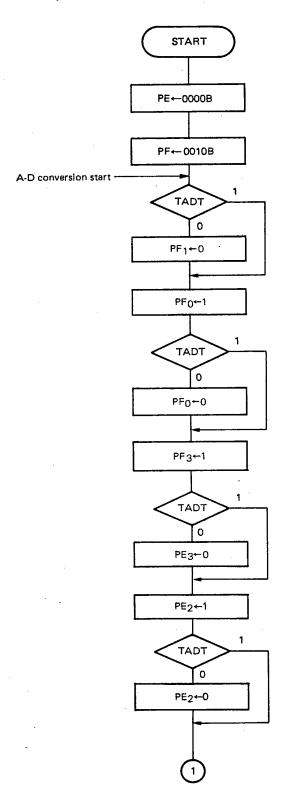

- Built-in 6-bit successive approximation A/D converter (V<sub>ref</sub> = V<sub>DD</sub>) executed by microcode using TADT and TADF instructions.

- Built-in Clock Generator Port (CGP) (64-step variable duty at 2.69 kHz or variable frequency with 180 kHz or 18 kHz as the base frequency)

- Effective I/O instructions (such as IN and OUT)

- Input and output port test instructions (TPT and TPF)

- Edge triggered vectored interrupt function (INT pin)

- Built-in timer F/F (This F/F is set every 125 ms, and the time of day clock function can be implemented easily.)

- Built-in interval pulse output (internal output of 5 ms pulse (200 Hz with 60 %duty)) tested by TIP instruction.

- PLL lock state test (TUL instruction)

- Transferring frequency division ratio, frequency division method, and reference frequency data to PLL section with only one instruction (PLL instruction)

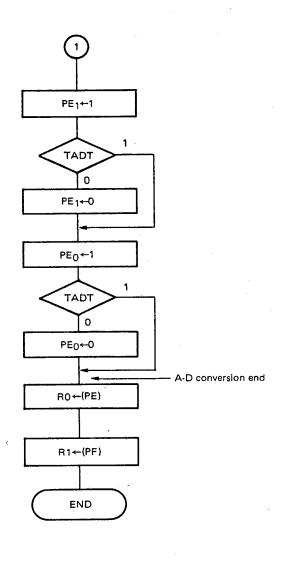

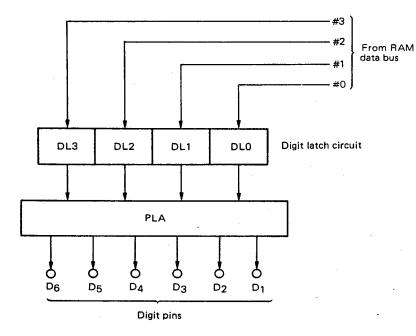

- Built-in Programmable Logic Array (PLA) for segments and digits (user mask programmable)

- Independent frequency input pins for AM and FM (maximum input frequency: 15 MHz for VCOH (FM) and VCOL (AM) pins)

- Direct connection to Two-Modules Prescaler: μPB553AC (130 MHz MAX.) and μPB562AC (1 GHz MAX.) signal connection is made via FM and PSC pins.

- Selection of pulse-swallow or direct frequency divisions by program

- Independent Error Out pin for AM and FM (EO<sub>1</sub> and EO<sub>2</sub> pins)

- Selection of seven reference frequencies by program 1, 5, 6.25, 9, 10, 12.5, and 25 kHz

- Hardware support: EVAKIT-1700 and EV-1707 (development tools), SE-1700 and EV-1707 (PROM base emulation board)

- Software support: Cross-assembler under CP/M<sup>TM</sup> and MP/M<sup>TM</sup>

Note: CP/M<sup>TM</sup> and MP/M<sup>TM</sup> are the trademarks of Digital Research Co., Ltd. EVAKIT<sup>TM</sup> is a trademark of NEC Corporation.

98D 17262

D 7-77-07-05

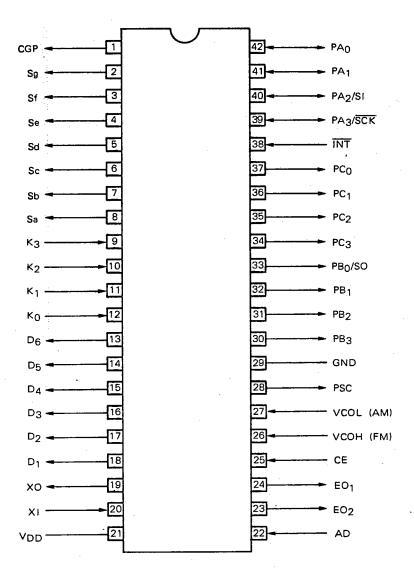

6427525 N E C ELECTRONICS INC PIN CONFIGURATION (Top View)

\_ 7-77-07-05

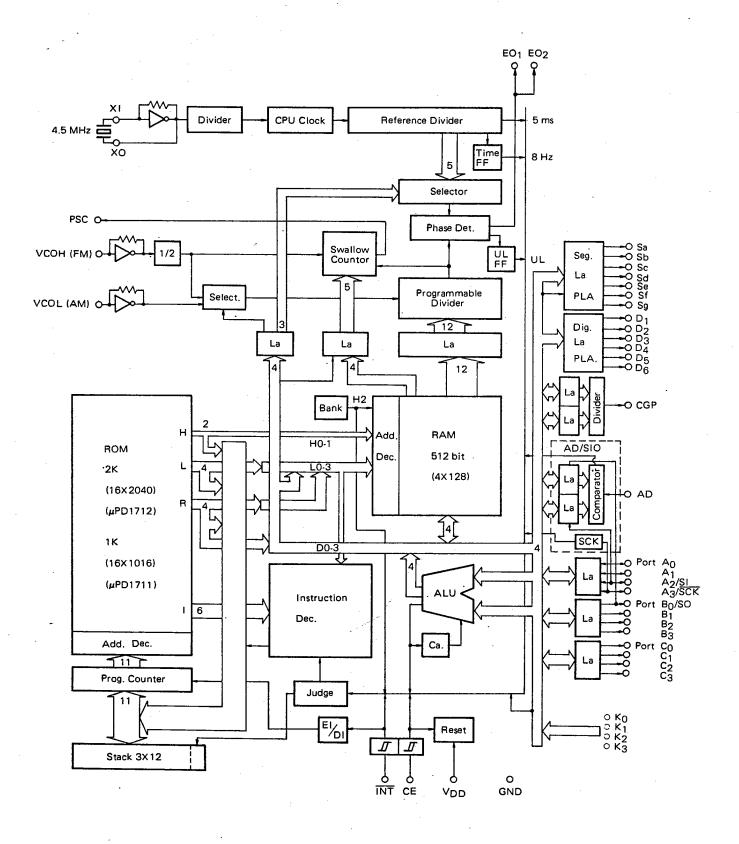

# **BLOCK DIAGRAM**

# PIN DESCRIPTION

| SYMBOL                           | NAME                                                                                                                                                                                                                                           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OUTPUT TYPE        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Clock<br>CGP Generator<br>Port   |                                                                                                                                                                                                                                                | This terminal can be used as Clock Generator Port (CGP) or 1-bit output port (PG2) by program control.  Two type of signals can be generated by the CGP: variable duty signal or variable frequency signal.  During the variable duty mode (VDP) mode, 2.69 kHz signal is output continuously with its duty changeable in 64 steps.  During the signal generator mode (SG) 50 % duty signal is output continuously with its frequency changeable in 64 steps with 180 Hz or 18 kHz as the reference frequency.  Since this port is N-channel open drain, an external pull-up resister is necessary. (See notes 1 and 2.) | N-ch open<br>drain |

| Sa to Sg                         | Segment<br>Outputs                                                                                                                                                                                                                             | Display segment output pins.  The SEG instruction unconditionally loads the contents of specified address in the data memory (RAM) to the programmable logic array (PLA). The selected data are output to these pins from PLA. (See the segment PLA section.)  The data is used to address one of 32 location in Segment PLA. These pins can also be used as a key return signal source for a key matrix. Since this port is P-channel open drain, an external pull-up resister is necessary.                                                                                                                            | P-ch open<br>drain |

| K <sub>3</sub> to K <sub>0</sub> | 4-bit input port. Unlike other ports, data can be input from these pins to a specified data memory (RAM) with a KI or KIN instruction. Normally, these pins are used as key return signal input pins from the externally connected key matrix. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |

| D <sub>6</sub> to D <sub>1</sub> | Digit<br>Outputs                                                                                                                                                                                                                               | 6-bit output port.  This port is used as digit signal output pins for display.  Unlike other ports (PA, PB, and PC), this port is controlled by a DIG instruction. The register contents specified in the DIG instruction are loaded to the digit PLA, and the contents are of specified digit patterns output from the PLA to these pins.  Sixteen patterns can be specified in the digit PLA. Whether or not to activate this port when CE pin = low can be specified at mask generation.                                                                                                                              | CMOS<br>push-pull  |

| XI, XO                           | X'tal                                                                                                                                                                                                                                          | Crystal oscillator connector pin. Connect a 4.5 MHz crystal oscillator to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CMOS<br>push-pull  |

| V <sub>DD</sub>                  | Power<br>Supply                                                                                                                                                                                                                                | Device power supply pin.  This pin supplies 5 V ±10 % while the device is operating.  This voltage can be dropped to 2.5 V to hold the internal data memory (RAM) with a CKSTP instruction. When the voltage applied to this pin changes from 0 → 4.5 V, the device is reset and the program starts from address 0. (within 500 ms)                                                                                                                                                                                                                                                                                      |                    |

| AD                               | Analog<br>Digital Input                                                                                                                                                                                                                        | Analog/Digital (A/D) converter input pin. The built-in A/D converter employs a 6-bit successive approximation method. The A/D converter reference voltage is $V_{DD}$ (5 V $\pm$ 10 %).                                                                                                                                                                                                                                                                                                                                                                                                                                  | Input              |

# 6427525 N E C ELECTRONICS INC

| SYMBOL                                                                                                                                                                                                                                                                    | NAME                                                                                                                                                              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OUTPUT TYPE          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| EO <sub>1</sub> , EO <sub>2</sub>                                                                                                                                                                                                                                         | Error<br>Output                                                                                                                                                   | PLL error output pins.  When the divided oscillation frequency is higher than the reference frequency, this pin outputs a high-level signal; when it is lower, this pin outputs a low-level signal; and when they are the same, this pin is set to high impedance.  This output is applied to the tuner varactor diode via the low pass filter.  Both AM and FM low pass filters can be connected to these pins because the same signal is output to the EO1 and EO2 pins simultaneously.                                                                                                                                                                                                                     | CMOS<br>three states |

| CE                                                                                                                                                                                                                                                                        | Chip Enable                                                                                                                                                       | Device selection signal input pin.  This pin must be high level to enable the device and low level to disable the device. When this pin is in the low level, the PLL, segment output, and digit outputs are disabled; however, an input of 134 \(mu\)s or less will not be accepted as a valid low.  When a CKSTP instruction in the program is executed while the CE pin is low level, the internal clock generator and CPU stop, and the memory can enter the hold state requiring low power consumption (10 \(mu\)A MAX.). When the CE pin goes to the high level from the low level, the device is reset and the program starts from address 0.  In this case, port A (PA3 to PA0) enters the input mode. | Input                |

| Programmable counter input pin for pulse-swallow od. To this pin, input the local oscillator (VCO divided by 1/16 or 1/17 with the prescaler μPB553. 1/128 or 1/136 with μPB562AC. Since this pin internal AC amplifier, cut the DC component capacitor before inputting. |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input                |

| VCOL (AM)                                                                                                                                                                                                                                                                 | AM Local<br>Oscillator<br>Signal Input                                                                                                                            | Programmable counter input pin for direct frequency division.  Input the local oscillator (VCO) output to this pin.  Since this pin has an internal AC amplifier, cut the DC component with a capacitor before inputting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input                |

| PSC                                                                                                                                                                                                                                                                       | Pin to output frequency division ratio selection signal to two-modulus prescaler μPB553AC or μPB562AC.  Pulse Connect this pin directly to PSC pin of μPB553AC or |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CMOS<br>push-pull    |

| GND                                                                                                                                                                                                                                                                       | Ground                                                                                                                                                            | Device ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                    |

| PB <sub>3</sub> to<br>PB <sub>0</sub>                                                                                                                                                                                                                                     | Port B                                                                                                                                                            | 4-bit output port. Since this pin is of the N-ch open drain output type (with maximum withstand voltage ±8.5 V), an external pull-up resistor is necessary.  The PB <sub>0</sub> pin can be used as an SO (Serial Output) pin by executing an SIO instruction. (See Notes 1 and 2.)                                                                                                                                                                                                                                                                                                                                                                                                                           | N-ch<br>open drain   |

| PC <sub>3</sub> to<br>PC <sub>0</sub>                                                                                                                                                                                                                                     | Port C                                                                                                                                                            | 4-bit output port. Since this pin is of the N-ch open drain output type (maximum voltage $V_{DD}$ ), an external pull-up resistor is necessary. (See Notes 1 and 2.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | N-ch<br>open drain   |

N E C ELECTRONICS INC 98

# 6427525 N E C ELECTRONICS INC

98D 17266

D 7-77 -07-05

| SYMBOL                                | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OUTPUT TYPE       |  |

|---------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| ĪNT                                   | Interrupt | Interrupt request signal input pin.  An interrupt request is issued at the trailing edge of the signal applied to this pin. When the interrupt request is accepted, control unconditionally jumps to address 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input             |  |

| PA <sub>3</sub> to<br>PA <sub>0</sub> | Port A    | 4-bit input/output port.  The contents at address 1FH in the data memory (RAM) bank 0 specify the input or output state of each bit in this port. In addition, this port can be used as a serial interface with an SIO instruction. In this case, the PA3 pin operates as an SCK (Shift Clock) pin. In the same way, the PA2 pin operates as an SI (Serial Input) pin and the PB0 pin operates as an SO (Serial Output) pin.  This port enters the input mode when the device is reset (VDD = low → high and CE = low → high) or when a CKSTP instruction is executed. To use the PA3 pin as the SCK pin, a pull-up resistor must be connected to the PA3 pin. Otherwise, no shift clocks are generated. (See Note 1.) | CMOS<br>push-pull |  |

#### Notes:

- PA<sub>0</sub> is associated with the least significant bit of the register or operand data, PA<sub>3</sub> is associated with the most significant bit of the register or operand data for port operation instructions (I/O, test, and set/reset instructions). This is the same as for PB, PC, and CGP (PG<sub>2</sub>).

- 2. The output ports (PB, PC, and CGP) enter the high-impedance state when the device is reset (VDD = low → high only) or when a CKSTP instruction is executed.

- When the CE pin goes from low to high, the output ports remain in the same state and they do not enter the high-impedance state. When the V<sub>DD</sub> pin goes from low to high or when the CE pin goes from low to high after executing a CKSTP instruction, the output ports are in the high-impedance state.

# **CONTENTS**

| 1. | CPU  | *************************************** | 10  |

|----|------|-----------------------------------------|-----|

|    | 1.1  | PROGRAM COUNTER                         | 10  |

|    | 1.2  | STACK REGISTER                          | 10  |

|    | 1.3  | PROGRAMMABLE MEMORY (ROM)               | 10  |

|    | 1.4  | DATA MEMORY (RAM)                       | 13  |

|    | 1.5  | TIMER F/F                               | 14  |

|    | 1.6  | INTERVAL PULSE                          | 17  |

|    | 1.7  | UNLOCK F/F                              | 17  |

|    | 1.8  | CARRY F/F                               | 18  |

|    | 1.9  | BANK F/F                                | 18  |

|    | 1.10 | INT F/F AND INTE F/F                    | 18  |

|    | 1.11 | STATUS WORDS                            | 19  |

|    |      |                                         |     |

| 2. | PLL  | *************************************** |     |

|    | 2.1  | REFERENCE FREQUENCY GENERATOR           | 20  |

|    | 2.2  | PHASE DETECTOR                          |     |

|    | 2.3  | PROGRAMMABLE DIVIDER                    |     |

|    | 2.4  | PLL REGISTER                            |     |

|    | 2.5  | PLL INFORMATION SETTING                 | 22  |

| _  |      | TS                                      |     |

| 3. |      | ·                                       |     |

|    | 3.1  | PORT A                                  |     |

|    | 3.2  | PORTS B AND C                           | 26  |

| 4. | CGP  | *************************************** | 27  |

|    | 4.1  | PG #2 THROUGH MODE                      |     |

|    | 4.2  | VDP MODE                                |     |

|    | 4.3  | SG MODE                                 |     |

|    |      |                                         |     |

| 5. | SER  | IAL I/O                                 |     |

|    | 5.1  | SHIFT MODE REGISTER (SMR)               |     |

|    | 5.2  | PRESETTABLE SHIFT REGISTER (PSR)        |     |

|    | 5.3  | SHIFT CLOCK COUNTER (SCC)               |     |

|    | 5.4  | SHIFT CLOCK GENERATOR (SCG)             |     |

|    | 5.5  | EXPANDED SERIAL I/O APPLICATIONS        | 38  |

| 6. | Δ.D  | CONVERTER                               | 4 4 |

| ٥. | 6.1  | OPERATION                               |     |

|    | 6.2  | D-A CONVERTER CONFIGURATION             | - • |

|    | 6.3  | A-D CONVERSION PROGRAM EXAMPLE          | •   |

|    | 0.3  | AD COM VERSION PROGRAM EXAMINEE         | +5  |

| 7. | PRO  | GRAMABLE LOGIC ARRAY                    | 17  |

|    | 7.1  | SEGMENT PLA CONFIGURATION               | 17  |

|    | 7.2  | SEGMENT PLA PATTERN EXAMPLES            | •   |

| -  | 7.3  | DIGIT PLA CONFIGURATION                 | _   |

|    | 7.4  | PLA PROGRAM EXAMPLE                     | _   |

#### N E C ELECTRONICS INC 981

6427525 0017268 4

7-77-07-05

| 8. | ELE   | CTRICAL CHARACTERISTICS63           |

|----|-------|-------------------------------------|

|    | 8.1   | ABSOLUTE MAXIMUM RATINGS 63         |

|    | 8.2   | RECOMMENDED OPERATING CONDITIONS 63 |

|    | 8.3   | DC CHARACTERISTICS 64               |

|    | 8.4   | AC CHARACTERISTIC 64                |

| _  | D.4.6 | CKAGE DIMENSION                     |

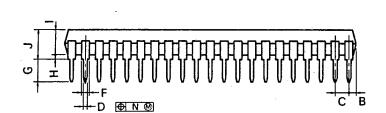

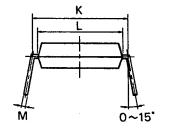

| 9. | PAC   | ;KAGE                               |

T-77-07 -05

## 1. CPU

#### 1.1 PROGRAM COUNTER

The program counter addresses the programmable memory (ROM) that stores the programs.  $\mu$ PD1711 has a 10-bit binary counter and  $\mu$ PD1712 has a 11-bit binary counter.

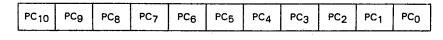

11 bits (for µPD 1712)

Usually, the counter increments by one every time an instruction is executed. When a jump or subroutine call instruction is executed, the address specified in the operand field is loaded to the counter. When a skip instruction (such as ADS, TMT, RTS, etc.) is executed, the address succeeding this skip instruction address is loaded to the counter regardless of the skip conditions. If the skip conditions are satisfied, the instruction succeeding this skip instruction is assumed to be Not Operational (NOP). The NOP instruction is executed, then the next instruction address is loaded to the counter.

When an interrupt request is accepted, address 1 is unconditionally loaded to the counter.

Note: μPD1701, 1703, 1704, 1705, 1710, and 1711 (microcomputer series containing 1K or fewer steps in the ROM) have a 10-bit program counter.

#### 1.2 STACK REGISTER

The stack register is a 3 x 12 bit (3 x 11 for  $\mu$ PD1711) register which stores the program counter value plus 1, that is the 11-bit (10-bit for  $\mu$ PD1711) return address, when a subroutine call instruction is executed or an interrupt request is accepted. In addition, if an instruction having a skip function is executed when accepting the interrupt request, the stack register also stores the 1-bit decision result. The stack register value is loaded to the program counter when a return instruction (RT or RTS) is executed and control returns to the main program flow.

The stack register can be used for both subroutine calls and interrupts. If one level is used for interrupts, the remaining two levels are used for subroutine calls.

#### 1.3 PROGRAMMABLE MEMORY (ROM)

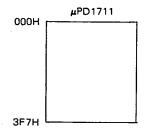

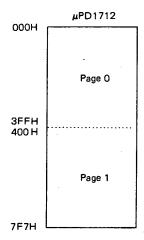

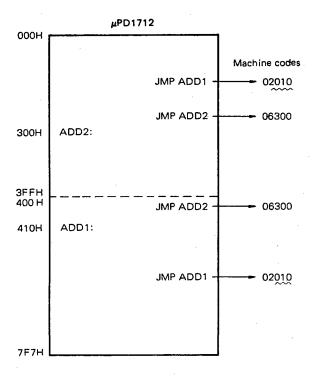

The ROM capacity of  $\mu$ PD1711 is 16 bits x 1016 steps and for  $\mu$ PD1712 is 16 bits x 2040 steps.  $\mu$ PD1711 allows access of 1016 steps at ROM addresses 000H to 3F7H and  $\mu$ PD1712 allows access to 2040 steps at ROM addresses 000H to 7F7H. The difference between  $\mu$ PD1711 and  $\mu$ PD1712 is only in the ROM capacity.

#### **ROM** configuration

10

The  $\mu$ PD1711 ROM addressing has no pages and fields; JMP instruction can be executed at any location to any arbitrary address. Similarly, CAL instruction can be executed at any location to any arbitrary address.

$\mu$ PD1712, do to increase in ROM size has a different concept. Precautions in using  $\mu$ PD1712 are given below.

The entire  $\mu$ PD1712 ROM area (000H to 7F7H) is divided into two pages: page 0 at addresses 000H to 3FFH and page 1 at addresses 400H to 7F7H.

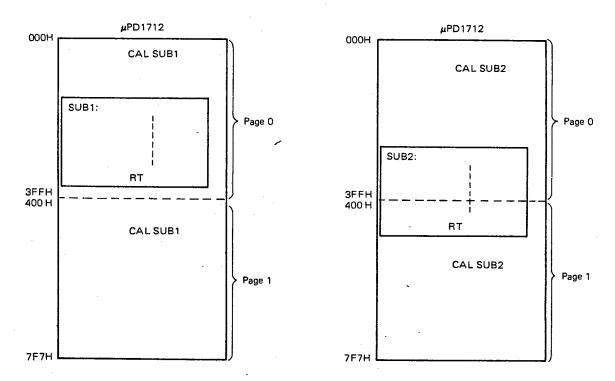

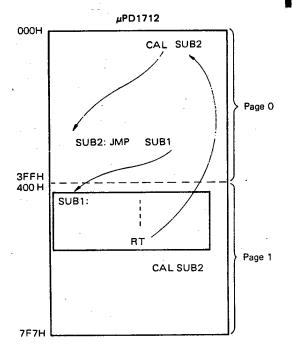

A µPD1712 subroutine must start at page 0. A subroutine starting at page 1 cannot be called from page 0 nor page 1. (See CAL instruction operation precautions.)

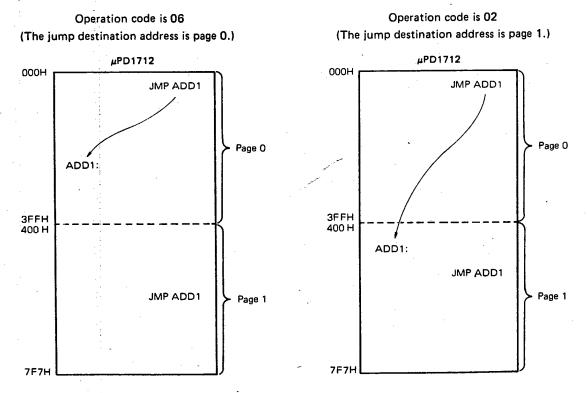

In the assembler language, a JMP instruction can be executed (JMP ADDR) at addresses 000H to 7F7H without the consideration of pages.

A JMP instruction for jumping into page 0 has a different operation code from that for jumping into page 1. Therefore, during program debugging, a careful attention must be made when jump code is generated. (See JMP instruction operation precautions.)

Since the  $\mu$ PD1712 ROM area is divided into pages 0 and 1, CAL and JMP instructions must be used considering the following precautions:

#### CAL instruction operating precautions

When a CAL instruction is used, its calling address, that is the subroutine start address, must be in page 0 (addresses 000H to 3FFH). A subroutine, whose starting address is in page 1 (addresses 400H to 7F7H), cannot be called. The return address (for an RT or RTS instruction) may be in page 1.

Example 1. When a subroutine start address is in page 0

As shown above, the return address may be in either page 0 or 1 if the subroutine start address is in page 0.

As long as the subroutine start address is in page 0, a CAL instruction can be used without considering pages.

If the subroutine start address cannot be placed in page 0 for any reason, the following method should be used.

7-77-07-05

Specify a JMP instruction in page 0 and call the necessary Subroutine (SUB1) via this JMP instruction.

# **JMP Instruction Operating Precautions**

In the assembler language, a JMP instruction can be used for the same description at addresses 000H to 7F7H without considering pages.

A JMP instruction to jump to page 0 (addresses 000H to 3FFH), has a different operation code from that for jumping to page 1 (addresses 400H to 7F7H). The operation code of the JMP instruction to jump to page 0 is 06 and to jump to page 1 is 02.

The µPD1700 Series assembler automatically converts these codes, referring to the jump destination.

For patch correction during program debugging, the programmer must select operation code 06 or 02.

If a JMP instruction causes a jump to a location at or after address 400H (with operation code 02), the addresses must also be offset by 400H. That is, address 400H must be considered as address 000H, from which the following addresses are incremented by 1 sequentially.

Therefore, address 7F7H is assumed as address 3F7H.

For example, JMP 400H written in the assembler must be input as 02000 for patch correction. JMP 000H must be input as 06000 in the same way.

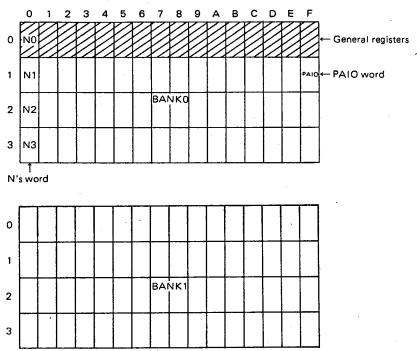

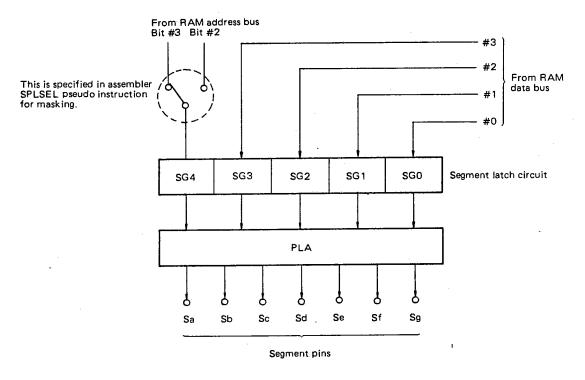

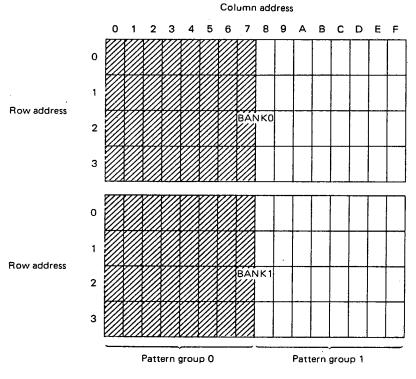

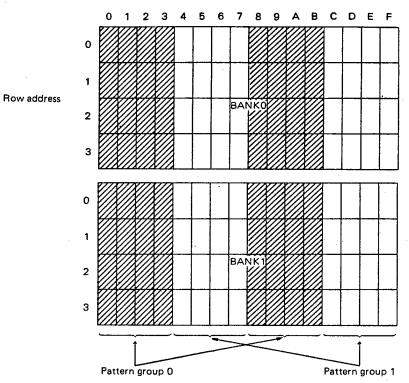

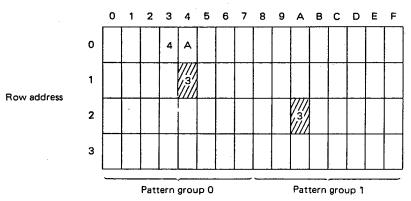

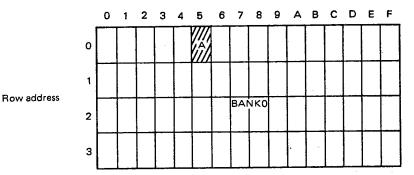

#### 1.4 DATA MEMORY (RAM)

The RAM consists of 4 bits x 128 words to store data. It is divided into banks 0 and 1, with 64 words each. To process data in either bank, the bank must be specified previously with a BANKO or BANK1 instruction.

Addresses 00H to 0FH in bank 0 compose general registers used for arithmetic operations and data transfer to and from the memory. They can also be used as an ordinary memory. (When bank 0 is used as a register, bank specification is not necessary, but when it is used as a memory, BANKO instruction must be used.)

The division ratio and reference frequency necessary for PLL control can also be set in the RAM.

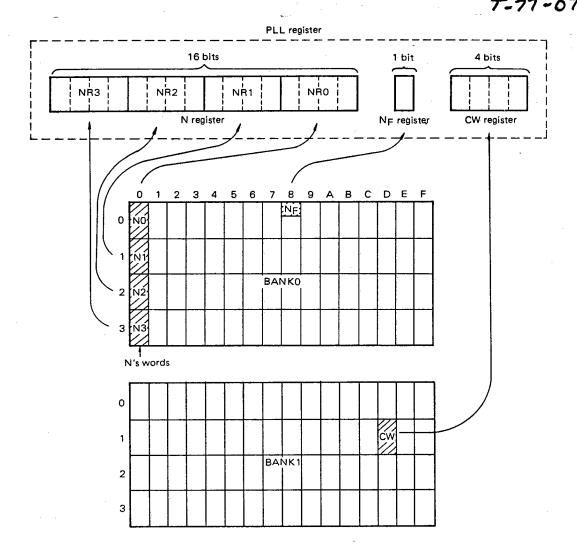

The division ratio in PLL registers (16-bit N word) are loaded from designated RAM location at addresses 00H, 10H, 20H and 30H. The N<sub>F</sub> bit is designated as MSB of specified general register (operand of PLL instruction). For the reference frequency, a specified word (4 bits) in the RAM (operand of PLL instruction), excluding locations 00, 10, 20, 30 and the word containing the N<sub>F</sub> bit is assigned as the control word. The 17-bit N-data and CW are transferred to the PLL registers by the PLL instruction.

The area at address 1FH in bank 0, called a PAIO word, specifies the input and output mode of port A (PA<sub>0</sub> to PA<sub>3</sub>).

a **a**

T-77-07-05

Row address

Fig. 1 RAM Configuration

Note: The most important point you should keep in mind in the general register operation in BANK1 is that μPD1711 and μPD1712 don't have operational instructions between the general registers and the immediate data. For example, expression "AI 00,1" in a program in BANK0 adds one to the general register which is stored in address 00 in the data memory. This AI instruction is the operation between memory and the immediate data. This instruction is not the operation between the register and the immediate data. If the above instruction is executed when BANK1 is specified, this expression does not add one to the address 00 of the general register but adds one to the address 00 of the data memory in BANK1.

# 1.5 TIMER F/F

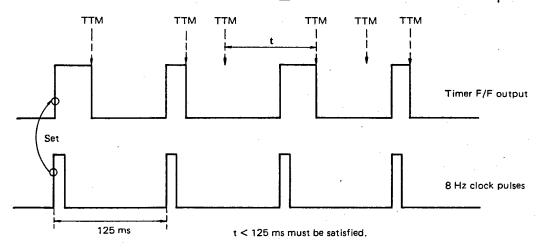

The timer F/F is set by a 8 Hz (125 ms) signal. It is reset by a Test Timer instruction (TTM).

Since the timer F/F is automatically set every 125 ms, it can be used for time of day clock (8 counts per second) and mute time counting.

The timer F/F is reset only by a TTM instruction, so a TTM instruction must be executed within every 125 ms period. Otherwise, the counting error will occur.

T-77-07-05

Fig. 2 TTM Instruction Execution Timings

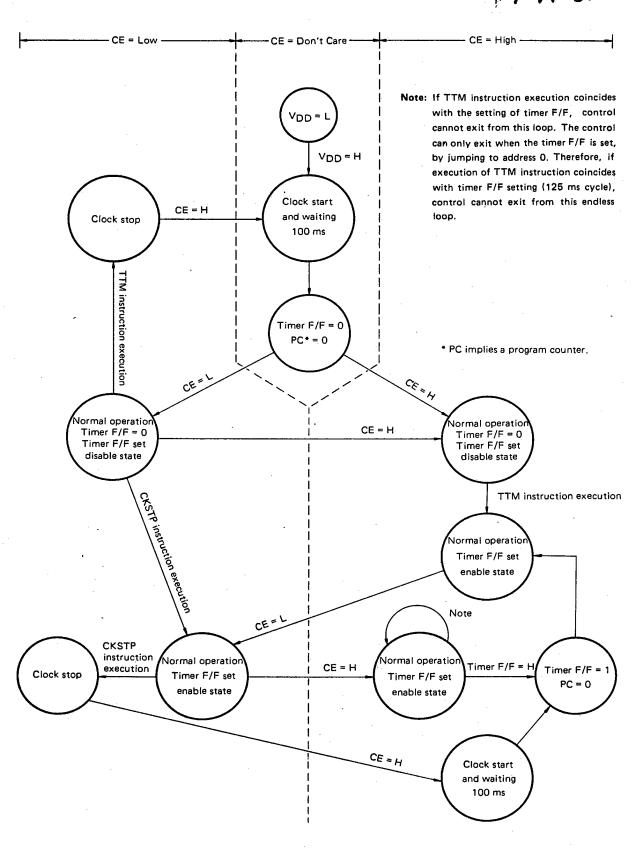

The timer F/F can also detect a power failure. The timer F/F is reset when the power is turned on (the V<sub>DD</sub> pin goes from low to high), and set when a CKSTP instruction is executed or the CE pin goes from low to high. (See Figure 3 for the status transition diagram.)

As shown in Figure 3, after the power is turned on  $(V_{DD} = low \rightarrow high)$ , the program starts from address 0 regardless of the CE pin state, at this time the timer F/F is being reset.

Subsequently, the timer F/F can not set by the internal 8 Hz clock before a TTM instruction is executed (timer F/F set disable state). Once a TTM instruction is executed, the timer F/F enters the set enable state and it can be set at 125 ms cycle.

When CE pin goes from low to high, after being in the backup mode ( $V_{DD} = high$ ), the control will not jumps to address 0 until timer F/F is set. That is, the program starts from address 0 after the timer F/F is set by the internal 8 Hz clock.

As explained above, the timer F/F value at recovery from a power failure ( $V_{DD}$  = low  $\rightarrow$  high) differs from that at recovery from a backup state ( $V_{DD}$  = high and CE = low  $\rightarrow$  high). Therefore, recovery from a power failure or backup state can be recognized by checking the timer F/F value with a TTM instruction.

A TTM instruction must be executed within 125 ms after the program starts from address 0. If the result = 0 (false) indicates a power failure and the result = 1 (true) indicates backup state.

To continue the timer function (no CKSTP instruction is executed) when CE = low, the program must be coded carefully for recovery from a backup state ( $V_{DD}$  = high, CE = low  $\rightarrow$  high). Since control jumps to address 0 immediately when the timer F/F is set, the timer must be updated after executing a TTM instruction for power failure detection (with true result). Otherwise, the timer lags 125 ms each time the CE pin goes from low to high.

Note: For μPD1711 and μPD1712, the timer F/F is set and the program starts from address 0 when the CE pin goes from low to high after executing a CKSTP instruction. For μPD1701, μPD1703, μPD1704, and μPD1710, the timer F/F is reset and the program starts from address 0 in this case. Note that the timer F/F value after CKSTP instruction execution for μPD1711 and μPD1712 differs from that for μPD1701, μPD1703, μPD1704, and μPD1710.

Z

Fig. 3 CPU Status Transition Diagram Associated with CE Pin

7-77-07-05

#### 1.6 INTERVAL PULSE

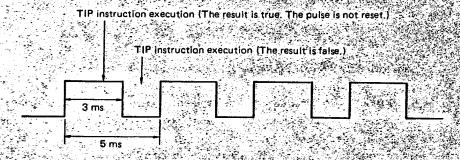

An interval pulse is a 60 % duty pulse signal at 5 ms cycle. It can be tested with a TIP instruction.

Since no Flip-Flop (F/F) is provided for this pulse, the pulse output will not be reset by executing a TIP instruc-

An accurate timer in 5 ms units can be generated by successively executing a TIP instruction to check the interval pulse edges.

Fig. 4 Interval Pulse Timings

#### 1.7 UNLOCK F/F

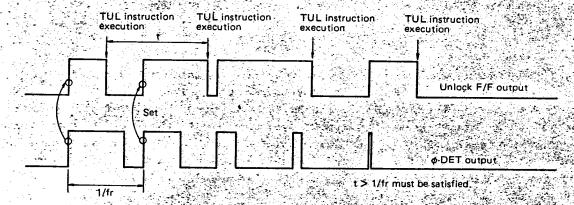

While PLL is unlocked, that is, while the reference frequency (fr) differs in phase with the divided frequency output from the VCO, the phase detector ( $\phi$ -DET) outputs a pulse at the fr cycle. The unlock F/F is set by this pulse and reset by executing a TUL instruction. Therefore, a TUL instruction must be executed at a interval greater than 1/fr. Otherwise, false PLL status can be detected. Furthermore, the execution of first TUL instruction must take place at least 1/fr duration after the execution of the PLL instruction.

Fig. 5 TUL Instruction Execution Timings

#### 1.8 CARRY F/F

Usually, when a carry or borrow is generated by executing an arithmetic instruction, the carry F/F is set. This F/F is reset when no carry nor borrow is generated. The carry F/F value remains unchanged unless arithmetic instructions are executed. The carry F/F can be set or reset directly by carry F/F set/reset instructions (STC and RSC) or status word operation instructions (SS and RS).

Note: Even when an interrupt request is accepted, the carry F/F value is not automatically saved.

#### 1.9 BANK F/F

The bank F/F is used for bank specification in the data memory (RAM) and port group addressing. RAM consists of 128 words, divided into banks 0 and 1 with 64 words each. In order to access data in either banks, the bank must be specified by executing a BANKO or BANK1 instruction. The bank specification is not necessary when addresses 00H to 0FH in bank 0 are used as general registers. These registers can be accessed from either of these banks. To use these addresses as a memory, a BANKO instruction must be specified.

The bank F/F is used for port group addressing. A port is addressed by the two bits in the instruction operand field and the contents of this bank F/F. (See explanation on ports.)

The bank F/F is automatically reset when the power is turned on for the first time (V<sub>DD</sub> = low → high) or the CE pin goes from low to high, that is, when the device is reset. In this case, bank 0 is specified automatically.

Note: Even when an interrupt request is accepted, the contents of bank F/F are not automatically saved.

#### 1.10 INT F/F AND INTE F/F

The INT F/F is set unconditionally by the trailing edge of a signal applied to the INT pin. If the internal INTE F/F is enabled then interrupt request is accepted; if it is disabled then interrupt request is not accepted. If the INT F/F is generated while the INTE F/F is being enabled, the interrupt request will be accepted.

The INTE F/F can be enabled by executing an EI instruction in the program and disabled by executing a DI instruction.

The INT F/F is reset when an instruction (DI or RS) which disables the INTE F/F is executed in the DI state.

When an interrupt request is accepted, the DI state is set automatically and control jumps to address 1 (interrupt processing routine). At this time, the address of the instruction succeeding that issuing the interrupt request is stored in the stack register. (When a JMP instruction is executed, the jump destination address is stored.) If the instruction issuing the interrupt request has a skip function, the skip condition decision result is also stored in the stack register. When an RT instruction is executed in the interrupt processing routine, the stack register contents are recovered and control returns to the source program. Since the carry F/F and bank F/F contents are not saved in the stack register, they must be saved by the interrupt routine.

Since the interrupt processing uses one stack level, stack level management is necessary.

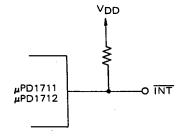

The INT pin can also be used as an ordinary input port by a TITT or TITF instruction. Note that INT pin value is tested true for a low level input and false for a high level input, that is, this pin is active only at the low level.

Note: A high level signal must be input to the INT pin at least once before it can recognize a valid low. Otherwise, a low level input is internally recognized to be high until a high level signal is input. Once a high level signal is input, the interrupt will work correctly. Therefore, the INT pin must be pulled up to VDD via a resistor in the application circuit.

T-77-07-05

# 1.11 STATUS WORDS

Internal device states, which must be checked or specified for program execution, are stored in 4-bit status words. They can be set or reset by programs.

There are status words 1 and 2 to which some pins and F/F's are connected.

# (1) Status word 1 (write-only word)

Operation instructions: SS, RS, etc.

| #3 | #2   | #1    | #0   |

|----|------|-------|------|

| -  | BANK | Carry | INTE |

|    | F/F  | F/F   | F/F  |

Status word 1 is a write-only word to be set and reset by instructions such as SS, RS, and EI.

#### (2) Status word 2 (read-only word)

Operation instructions: TST, TSF, etc.

| #3 | #2   | . #1 | #0  |

|----|------|------|-----|

| _  | BANK | CE   | INT |

|    | F/F  | pin  | pin |

Status word 2 is a ready-only word whose contents can be judged by instructions such as TST, TSF, and SBKO.

7-77-07-05

### 2. PLL

# 2.1 REFERENCE FREQUENCY GENERATOR

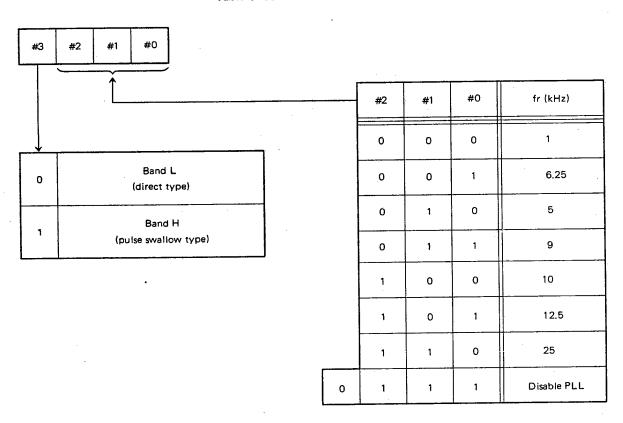

The external crystal oscillator (4.5 MHz) generates seven reference frequencies: 1 kHz, 5 kHz, 6.25 kHz, 9 kHz, 12.5 kHz, and 25 kHz. One of these frequencies can be selected by the program (control word data).

#### 2.2 PHASE DETECTOR

The phase detector circuit detects phase difference between the reference frequency (fr) and VCO output divided by the programmable divider. The output signal is input to the internal charge pump to output the following pulses to the EO<sub>1</sub> and EO<sub>2</sub> pins:

(1) fr >  $f_{osc}/N$ : Low level (2) fr <  $f_{osc}/N$ : High level (3) fr =  $f_{osc}/N$ : Floating

where, fosc is the VCO oscillation frequency and N is the division ratio of the programmable divider.

#### 2.3 PROGRAMMABLE DIVIDER

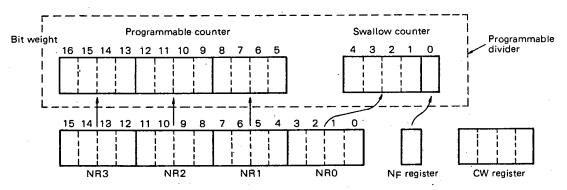

The programmable divider consists of a swallow and programmable counters which are binary decrement counters.

The swallow counter is a 5-bit presettable decrement counter. The contents of the 4-bit NRO register and 1-bit NF register are loaded to this counter at every 1/fr period.

The programmable counter is a 12-bit counter. The contents of the NR1 to NR3 registers are loaded to this counter which count down simultaneously with the swallow counter.

Fig. 6 Programmable Divider Configuration

The 5-bit swallow counter data is output from the PSC pin to the prescaler.

# 2.4 PLL REGISTER

To control the PLL of  $\mu$ PD1711 or  $\mu$ PD1712, the following information must be stored in the PLL register:

- (1) Division ratio (N)

- (2) Frequency reference (fr)

- (3) Division method (direct or pulse swallow type)

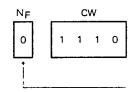

The PLL register consists of the 16-bit N register and 1-bit N<sub>F</sub> register to store the division ratio and the 4-bit Control Word (CW) register for storing the reference frequency. They are associated with the N's words, N<sub>F</sub> bit, and Control Word (CW) in the data memory (RAM), respectively. The contents of designated RAM locations are transferred with a PLL instruction in a single execution cycle. N's words are assigned to addresses 00H, 10H, 20H and 30H in RAM bank 0, the N<sub>F</sub> bit is assigned to the most significant bit of specified general register, and the CW is assigned to specified RAM area, excluding the N's words, and the word containing the N<sub>F</sub> bit.

5

Fig. 7 PLL Instruction Functions

Since the Control Word (CW) is in bank 1 in the example above, a BANK1 instruction must be executed before the PLL instruction. Otherwise, the contents at address 1DH in bank 0 are transferred to the CW register as the CW data, disabling to set the correct reference frequency.

The control word data codes are as follows. The most significant bit (#3) specifies the division method. The three low-order bits (#2 to #0) specify one of the seven reference frequencies.

# PSZBYRDINGUORA

7-77-07-05

**Table 1 Control Word Codes**

The PLL disable mode can be set by setting 07H in the Control Word (CW) and executing a PLL instruction. By disabling the PLL, the device can be put into a low power consumption mode.

# 2.5 PLL INFORMATION SETTING

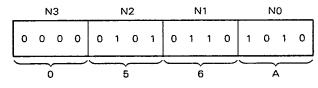

The PLL information (division ratio, reference frequency, and division method) is set by the program. The programmable divider division ratio is set as follows:

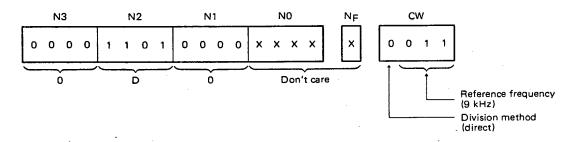

## Example 1. Direct method (AM)

(Receive frequency: 1422 kHz, reference frequency: 9 kHz, intermediate frequency (IF): 450 kHz)

$$N = \frac{1422 + 450}{9} = 208$$

= 0D0H (H implies a hexadecimal code.)

In the direct method, the contents of NO and  $N_{\textrm{F}}$  are ignored.

# 6427525 N E C ELECTRONICS INC

98D 17282

D 7-77-07-05

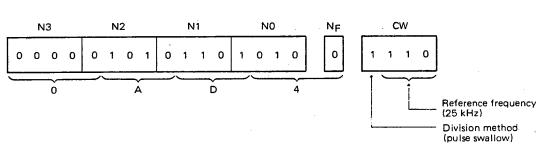

Example 2. Pulse swallow method (FM)

(Receive frequency: 80.0 MHz, reference frequency: 25 kHz, 1F: -10.7 MHz)

$$N = \frac{(80.0 - 10.7) \times 10^3}{25} = 2772$$

$$= 0AD4H$$

In this example, the  $N_F$  bit is used to change the VCO oscillation frequency by 25 kHz steps. To change the VCO frequency in 50 kHz, 100 kHz, or 200 kHz steps, increment N0 by 1, 2, or 4.

Usually, the  $N_F$  bit is used for IF fine tuning. When the  $N_F$  bit is set to 1 in the example above, the division ratio N becomes 2773. Assuming that the receive frequency is the same 80.0 MHz, the IF ( $f_{\rm IF}$ ) is as follows:

$$\frac{(80.0 - f_{IF}) \times 10^3}{25} = 2773$$

$$f_{IF} = (69.325 - 80.0)$$

$$= -10.675 \text{ MHz}$$

This is equivalent to the IF changed 25 kHz in the case above.

Thus, the N<sub>F</sub> bit can be used for IF correction.

The N value is decided by assuming that the N<sub>F</sub> bit is the least significant bit in the above example; however, the program would be understood more easily by grouping every four bits from NO. That is, assume that the reference frequency is 50 kHz.

$$N = \frac{(80.0 - 10.7) \times 10^3}{50} = 1386$$

$$= 056AH$$

IF offset bit

This is the same as when the reference frequency is 25 kHz.

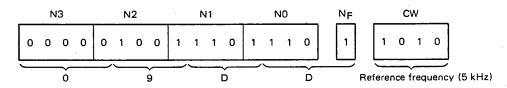

Example 3. For USA TV band 02 ch

$$N = \frac{f_p + f_{1F}}{P \times fr} \text{ (where, } f_{osc} = f_p + f_{1F} \text{)}$$

fp = Picture carrier frequency

fif = Intermediate frequency

P = Prescaler division ratio

fr = Reference frequency

N = Programmable divider division ratio

fosc = Local oscillation frequency

6427525 N E C ELECTRONICS INC

98D 17283

D **T-77-07 -05**

When the prescaler is  $\mu PB562AC$ , use the prescaler division ratio P = 8.

$$N = \frac{(55.25 \text{ MHz}, f_{IF} = 45.75 \text{ MHz}, P = 8, fr = 5 \text{ kHz})}{8 \times 5} = 2525$$

$$= 09DDH \text{ (H implies a hexadecimal number.)}$$

In this example, the N<sub>F</sub> bit is used to change the VCO oscillation frequency  $f_{osc} = f_p + f_{1F}$  by 40 kHz (P × fr) steps. That is, the resolution is the product of the prescaler division ratio and reference frequency.

In the example above, when bit 0 of N0 is changed (N0 is changed by 1),  $f_{osc}$  is changed by 80 kHz; when bit 1 is changed (N0 is changed by 2),  $f_{osc}$  is changed by 160 kHz; and when bit 2 is changed (N0 is changed by 4),  $f_{osc}$  is changed by 320 kHz.

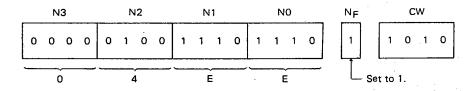

The N value is decided assuming that the  $N_F$  bit is the least significant bit in the above example; however, the program would be understood more easily by grouping every four bits from N0. That is, assume that the  $N_F$  bit is fixed and change N0. In this case, N can be calculated as follows:

$$N = \frac{(f_p + f_{|F|}) - (P \times fr) N_F}{2 \times (P \times fr)}$$

When the N<sub>F</sub> bit is "1", (P x fr) N<sub>F</sub> becomes (P x fr), when this bit is 0, this item becomes 0. 2 x (P x fr) implies changing 80 kHz since the bits are changed from N0.

The value in Example 1 can be applied to the above expression as follows:

$$N = \frac{(55.25 + 45.75) \times 10^3 - 40}{2 \times 8 \times 5} = 1262$$

$$= 04EEH$$

Thus, the programmable divider contents are the same as those in Example 1.

For the USA TV band, the above expression assumes that the N<sub>F</sub> bit is always 1 if f<sub>IF</sub> = 45.75 MHz.

#### 3, PORTS

$\mu$ PD1711 and  $\mu$ PD1712 have I/O port A (PA<sub>3</sub> to PA<sub>0</sub>) and output ports B (PB<sub>3</sub> to PB<sub>0</sub>) and C (PC<sub>3</sub> to PC<sub>0</sub>). Since the output ports are of the N-ch open drain type, they require pull-up resistors.

In addition, there are internal ports E (PE<sub>3</sub> to PE<sub>0</sub>), F (PE<sub>3</sub> to PF<sub>0</sub>), G (PG<sub>3</sub> to PG<sub>0</sub>), and H (PH<sub>3</sub> to PH<sub>0</sub>).

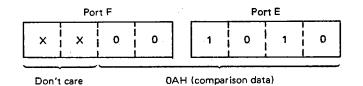

Ports E and F (eight bits in total) are used as a data buffer for accessing A/D converter. Ports G and H (eight bits in total) are used as a data buffer for the Clock Generator Port (CGP): during VDP mode 6 bits duty cycle data is stored, during SG mode 6 bits division ratio is stored.

These ports are addressed according to the direct accessing method specified in 2 bits of the instruction operand and the bank F/F as follows:

Table 2 Port Addressing

| Direct | Add. | BANK F/F |        |  |

|--------|------|----------|--------|--|

| #1 #0  |      | BANK 0   | BANK 1 |  |

| 0 .    | 0 .  | PA       | PE     |  |

| 0      | 1    | PB       | PF     |  |

| 1      | 0    | PC       | PG     |  |

| 1      | 1    | -        | PH     |  |

To access internal ports E, F, G, and H, set the bank F/F to specify bank 1. But, RAM bank 0 cannot be accessed while bank 1 is being set. That is, to access RAM bank 0 after accessing the port group in bank 1, the bank F/F setting must be changed to specify bank 0.

#### Example

MVI OAH,1111B; Sets OFH at address OAH in the register. MVI OBH,1101B; Sets ODH at address OBH in the register.

#### FLOOP:

BANK1

; Outputs the contents of address OAH to PH. OUT 3,0AH Outputs the contents of address OBH to PG. OUT 2, 0BH

; Returns to bank 0 after accessing internal ports. **BANKO**

; Calls a subroutine to wait 1 second. CAL WT1SEC

OBH, 0100B; SIBS OAH, O JMP FLOOP

In the example above, the CGP is accessed and 64 frequencies divided from reference frequency 18 kHz are individually output 1 second, beginning with the lowest frequency.

#### 3.1 PORT A

Port A (PA<sub>3</sub> to PA<sub>0</sub>) can be set to input or output mode by each bit. The input or output mode is determined by the value stored in location 1FH of data memory (RAM) bank 0, called PAIO word. To set the input mode, write a 0, for output mode write a 1, to the corresponding bit of PAIO word.

T-77-07-05

|                            | #3              | #2              | #1              | #0              |

|----------------------------|-----------------|-----------------|-----------------|-----------------|

| PAIO Word<br>(Address 1FH) | PA <sub>3</sub> | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> |

Example 1. Setting PA<sub>3</sub> to PA<sub>0</sub> as an output port.

|                            | #3 | #2 | #1 | #0 |

|----------------------------|----|----|----|----|

| PAIO Word<br>(Address 1FH) | 1  | 1  | 1  | 1  |

Example 2. Setting PA<sub>3</sub> as an output port and PA<sub>2</sub> to PA<sub>0</sub> as input ports.

|                            | #3 | #2 | #1 | #0 |

|----------------------------|----|----|----|----|

| PAIO Word<br>(Address 1FH) | 1  | 0  | 0  | 0  |

For port A, as explained above, an I/O instruction can be executed after setting the I/O mode to the PAIO word. The I/O mode once set remains unchanged unless the PAIO word contents (data at address 1FH) are changed.

Port A automatically enters the input mode when the power is turned on  $(V_{DD} = low \rightarrow high)$ , a CKSTP instruction is executed, or the CE pin goes from low to high.

Note that the PAIO word contents may not match port A I/O mode. Subsequently, port A is in the input mode until the PAIO word contents are set.

The PA<sub>3</sub> and PA<sub>2</sub> pins of port A can also be used as serial I/O pins. They operate as shift clock (SCK) and Serial Input (SI) pins, respectively, during execution of an SIO instruction. To use these pins as SCK and SI pins, it is necessary to set bits 3 and 2 of the PAIO word to 0s, that is, place PA<sub>3</sub> and PA<sub>2</sub> of port A in the input mode. (See 5. "Serial I/O.")

#### 3.2 PORTS B AND C

Port B (PB<sub>3</sub> to PB<sub>0</sub>) and port C (PC<sub>3</sub> to PC<sub>0</sub>) are output ports of the N-ch open drain type. They can be controlled with output instructions (OUT, SPB, and RPB). When an Input Instruction (IN) is executed, the contents of the output latch are read into the specified register. The IN instruction does not change the output latch data.

When "1" is output during output instruction execution, these ports go high (pull-up voltage); When 0 is output, these ports go low (ground voltage).

When the power is turned on  $(V_{DD} = low \rightarrow high)$  or a CKSTP instruction is executed, "1" is output (high-impedance state), that is, the pull-up voltage is output.

At this time the internal output data latch contents do not change. (When the power is turned on  $(V_{DD} = low \rightarrow high)$ , the output data latch contents are undefined.) The output data latch contents can be output immediately by executing the following instruction. This is an example for port C.

SPB 2,0000B or RPB 2,0000B

These instructions do not set or reset port C bits.

When the CE pin goes from low to high, ports B and C remain in the same state, not going to the high-impedance state.

7-77-07-05

#### 4. CGP

The Clock Generator Port (CGP, controlled by internal ports G and H, has the Variable Duty Pulse (VDP) generation function and Signal Generator (SG) function.

Ports G and H act like other ports, except that they are internal ports, controlled by any port operation instructions. When an IN instruction is executed for ports G and H, the data being set in these ports are read into the specified register.

The CGP can be set to one of four modes specified by bits 0 and 1 of port G, called the Control Bits (CB).

Port H Port G #0 #2 #0 #3 #2 #1 LSB MSB CB DATA BITS CB (Control Bits) **Function** #0 0 PG#2 through mode: 0 Outputs the value of port G bit 2 to the CGP pin. 0 1 Variable duty (64 steps) output at frequency 2.69 kHz. 0 . 1 SG mode 0: Outputs 64 frequencies divided from 18 kHz. 1 SG mode 1: Outputs 64 frequencies divided from 180 kHz.

Table 3 Control Bit (CB) Codes and Functions

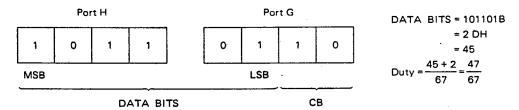

Port H bits 3-0 and port G bits 3-2 are called data bits; they specify the duty value in the VDP mode or the division value in the SG mode. The most significant data bit is port H bit 3 and the least significant data bit is port G bit 2.

Since the CGP pin is of the N-ch open drain output type, it goes to the high impedance state unconditionally when the power is turned on  $(V_{DD} = low \rightarrow high)$  or a CKSTP instruction is executed. The data latch contents of ports G and H remain unchanged when CKSTP instruction is executed. The data latch contents are undefined when the power is turned on  $(V_{DD} = low \rightarrow high)$ .

The CGP pin becomes active from the high-impedance state when data in port G are accessed by I/O instructions. The CGP pin can be activated, holding the data latch contents, by using an instruction (SPB 2,0) which sets no bits in port G or (RPB 2,0) which resets no bits. Executing an instruction which operates only port H will not activate the CGP pin from the high-impedance state.

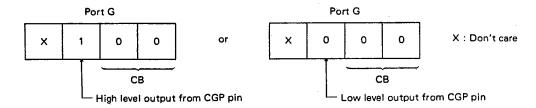

The status of CGP pin remains in the same level when the CE pin level changes. To set the CGP pin to the low level when the CE pin goes from high to low, it is necessary to test the CE pin level with a TCET or TCEF instruction. Then, execute the instruction which places the CGP in the PG #2 through mode, and set CGP pin in the low level according to the test result of CE pin. That is, X000B should be output to port G. (X: don't care)

Ti77-07-05

# 4.1 PG #2 THROUGH MODE

When CB = 00B, the port G bit 2 data is directly output to the CGP pin, that is, the CGP pin goes high when PG #2 = 1 and low when PG #2 = 0. Thus, the CGP pin can be used as a 1-bit output port.

In this case, the port G bit 3 value is ignored. In the same way, the port H value is ignored, therefore, it is not necessary to output data to the port H in the PG #2 through mode.

#### 4.2 VDP MODE

When CB = 10B, a signal having the duty specified by the data in Port G and H ( $PH_3$  to  $PH_0$ ,  $PG_3$ , and  $PG_2$ ) is output contiguously to the CGP pin. The output signal frequency is 2.69 kHz.

The relationships between the output signal duty and the data set in Port G and H are as follows:

Duty =

$$\frac{\text{High level duration}}{\text{Cycle}} = \frac{\text{(data bits)} + 2}{67}$$

The duty can take 64 values ranging from 2/67 to 65/67.

When the VDP and PG #2 through modes are used in combination, the duty can take 66 values including high and low outputs.

#### Example

As this example shows, port H bit 3 becomes the most significant bit of the data bits and port G bit 2 becomes the least significant bit. The CGP pin starts outputting pulses when 10B is set in the CB, the two low-order bits of port G. For example, if CB = 00B, VDP will be disabled and 2.69 kHz signal will not be output.

Therefore, to set the VDP mode from the high-impedance state, it is necessary first to output data to port H, then to port G. If data is first output to port G, the CGP pin operates according to the current port H data before new data is set to port H. Therefore, the desired duty value cannot be obtained.

If the VDP mode has been set and port G data remains unchanged, data can be output to port H alone or to port H first.

**デーファー07-05**

# Programming example

MVI 0AH, 1011B; Sets the port H data in the register.

MVI 0BH, 0110B; Sets the port G data in the register (VDP mode).

BANK1

OUT 3, 0AH; Outputs data to port H.

OUT 2, 0BH; Outputs data (pulses with duty 64/67) to port G.

**BANKO**

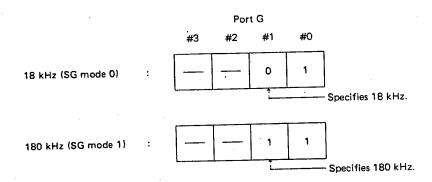

# 4.3 SG MODE

When the Control Bit (CB) 0 (port G bit 0) is set to 1, the CGP pin enters the Signal Generator (SG) mode. The SG mode outputs signals (duty 50 %) at the frequency specified in the data bits to the CGP pin. Frequencies varying in 128 steps can be output during this mode.

The relationship between the data set in the data bits and the output signal frequency (four) are as follows:

$$f_{OUT} = \frac{f_{B}}{2 (2 + (DATA BITS))}$$

Where, f<sub>B</sub> (base frequency) is the reference frequency to output to the CGP pin. The frequency can be selected between 18 kHz and 180 kHz by the CB 1 (port G bit 1) value.

Like the VDP mode, the CGP pin outputs a signal when bit 0 of port B is set. Table 4 gives the relation between CGP pin output frequencies and data bits.

\_ 7-77-07-05

Table 4 Output Frequencies in SG Mode

|     | DATA BITS       | OUTPUT F    | REQUENCY     |     | DATA BITS       | OUTPUT F    | OUTPUT FREQUENCY |  |

|-----|-----------------|-------------|--------------|-----|-----------------|-------------|------------------|--|

| DEC | BINARY<br>PH PG | MODE 0 (Hz) | MODE 1 (kHz) | DEC | BINARY<br>PH PG | MODE 0 (Hz) | MODE 1 (kHz)     |  |

| 0   | 000000          | 4500.000    | 45.0000      | 32  | 1 0 0 0 0 0     | 264.706     | 2.6471           |  |

| 1   | 0 0 0 0 0 1     | 3000.000    | 30.0000      | 33  | 1 0 0 0 0 1     | 257.143     | 2.5714           |  |

| 2   | 0 0 0 0 1 0     | 2250.000    | 22.5000      | 34  | 1 0 0 0 1 0     | 250.000     | 2.5000           |  |

| 3   | 0 0 0 0 1 1     | 1800.000    | 18.0000      | 35  | 100011          | 243.243     | 2.4324           |  |

| 4   | 0 0 0 1 : 0 0   | 1500.000    | 15.0000      | 36  | 100100          | 236.842     | 2.3684           |  |

| 5   | 0 0 0 1 0 1     | 1285.710    | 12.8571      | 37  | 1 0 0 1 0 1     | 230.769     | 2.3077           |  |

| 6   | 0 0 0 1 1 0     | 1125.000    | 11.2500      | 38  | 1 0 0 1 1 0     | 225.000     | 2.2500           |  |

| 7   | 0 0 0 1 1 1     | 1000.000    | 10.0000      | 39  | 1 0 0 1 1 1     | 219.512     | 2.1951           |  |

| 8   | 0 0 1 0 0 0     | 900.000     | 9.0000       | 40  | 1 0 1 0 0 0     | 214.286     | 2.1429           |  |

| 9   | 0 0 1 0 0 1     | 818.182     | 8.1818       | 41  | 1 0 1 0 0 1     | 209.302     | 2.0930           |  |

| 10  | 0 0 1 0 1 0     | 750.000     | 7.5000       | 42  | 1 0 1 0 1 0     | 204.545     | 2.0455           |  |

| 11  | 0 0 1 0 1 1     | 692.308     | 6.9231       | 43  | 1 0 1 0 1 1     | 200.000     | 2.0000           |  |

| 12  | 0 0 1 1 0 0     | 642.857     | 6.4286       | 44  | 1 0 1 1 0 0     | 195.652     | 1.9565           |  |

| 13  | 0 0 1 1 0 1     | 600.000     | 6.0000       | 45  | 1 0 1 1 0 1     | 191.489     | 1.9149           |  |

| 14  | 0 0 1 1 1 0     | 562.500     | 5.6250       | 46  | 1 0 1 1 1 0     | 187.500     | 1.8750           |  |

| 15  | 0 0 1 1 1 1     | 529.412     | 5.2941       | 47  | 101111          | 183.673     | 1.8367           |  |

| 16  | 0 1 0 0 . 0 0   | 500.000     | 5.0000       | 48  | 1 1 0 0 0 0     | 180.000     | 1.8000           |  |

| 17  | 0 1 0 0 0 1     | 473.684     | 4.7368       | 49  | 1 1 0 0 0 1     | 176.471     | 1.7647           |  |

| 18  | 0 1 0 0 1 0     | 450.000     | 4.5000       | 50  | 1 1 0 0 1 0     | 173.077     | 1.7308           |  |

| 19  | 0 1 0 0 . 1 1   | 428.571     | 4.2857       | 51  | 1 1 0 0 1 1     | 169.811     | 1.6981           |  |

| 20  | 0 1 0 1 0 0     | 409.091     | 4.0909       | 52  | 1 1 0 1 . 0 0   | 166.667     | 1.6667           |  |

| 21  | 0 1 0 1 0 1     | 391.304     | 3.9130       | 53  | 1 1 0 1 0 1     | 163.636     | 1.6364           |  |

| 22  | 0 1 0 1 1 0     | 375.000     | 3.7500       | 54  | 1 1 0 1 1 0     | 160.714     | 1.6071           |  |

| 23  | 0 1 0 1 1 1     | 360.000     | 3.6000       | 55  | 1 1 0 1 1 1     | 157.895     | 1.5789           |  |

| 24  | 0 1 1 0 0 0     | 346.154     | 3.4615       | 56  | 1 1 1 0 0 0     | 155.172     | 1.5517           |  |

| 25  | 0 1 1 0 0 1     | 333.333     | 3.3333       | 57  | 1 1 1 0 0 1     | 152.542     | 1.5254           |  |

| 26  | 0 1 1 0 1 0     | 321.429     | 3.2143       | 58  | 1 1 1 0 1 0     | 150.000     | 1.5000           |  |

| 27  | 0 1 1 0 1 1     | 310.345     | 3.1034       | 59  | 1 1 1 0 1 1     | 147.541     | 1.4754           |  |

| 28  | 0 1 1 1 0 0     | 300.000     | 3.0000       | 60  | 1 1 1 1 0 0     | 145.161     | 1.4516           |  |

| 29  | 0 1 1 1 0 1     | 290.323     | 2.9032       | 61  | 1 1 1 1 0 1     | 142.857     | 1.4286           |  |

| 30  | 0 1 1 1 1 0     | 281.250     | 2.8125       | 62  | 1 1 1 1 1 0     | 140.625     | 1.4063           |  |

| 31  | 0 1 1 1 1 1     | 272.727     | 2.7273       | 63  | 1 1 1 1 1 1     | 138.462     | 1.3846           |  |

## 5. SERIAL I/O

The serial I/O is an 8-bit serial I/O of the  $\mu$ COM standard to transfer data in synchronization with the internal or external clock. The serial I/O is associated with three pins:

SI (shared by PA<sub>2</sub>): Serial data input pin SO (shared by PB<sub>0</sub>): Serial data output pin

SCK (shared by PA<sub>3</sub>): Shift clock input/output pin (active low)

Since these pins are shared by other ports ( $PA_3$ ,  $PA_2$ , and  $PB_0$ ), these pins cannot be used as ports ( $PA_3$ ,  $PA_2$ , and  $PB_0$ ) when they are used as serial I/O pins.

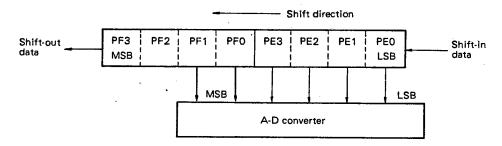

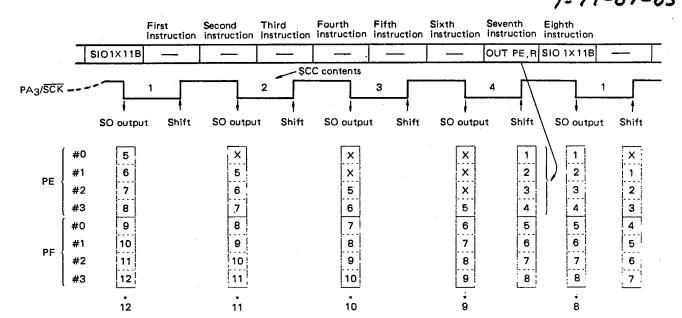

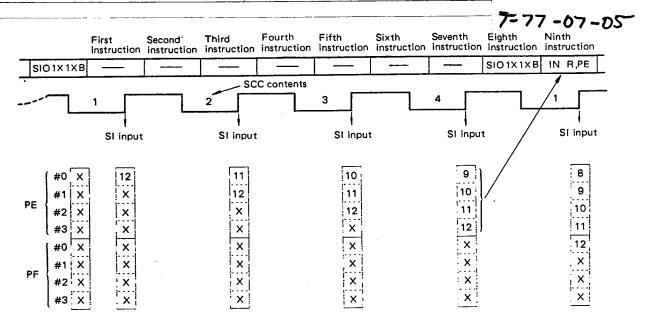

The 8-bit shift register for the serial I/O data buffer is composed of 2 internal ports. The four high-order bits are allocated to internal port F and four low-order bits are allocated to internal port E. Therefore, data can be written to or read from the shift register with a port operation instruction (such as OUT, SPB, RPB, IN, etc.) which accesses ports E and F.

Ports E and F, the shift register are also used as data latch during A-D conversion. Therefore, serial I/O operation cannot be performed simultaneously with A-D conversion operation.

During A-D conversion operation, inputting the shift clocks to the presettable shift register must be inhibited by resetting SMR1 (bit 1) of the shift mode register.

The serial I/O consists of the Shift Mode Register (SMR), Presettable-Shift Register (PSR), Shift Clock Counter (SCC), and Shift Clock Generator (SCG). They are explained in the following sections.

#### 5.1 SHIFT MODE REGISTER (SMR)

The SMR, consisting of three bits (SMR3, SMR1, and SMR0), determines the serial I/O mode. When an SIO instruction is executed, the immediate data in its operand is written in the SMR. The SMR has no bits associated with operand bit 2. That is, immediate data bit 2 in the operand is ignored during SIO instruction execution.

Executing an SIO instruction (SIO b3 b2 b1 b0 B) sets the following data in the SMR and starts the associated mode operation:

SIO b3 b1 ρO b2 **Function** Symbol 0: Uses PBO/SO pin as PBO. SO Enable bit **SMRO** 1: Uses PB<sub>0</sub>/SO pin as SO. 0: Enables shift operation. Shift Enable bit SMR1 1: Disables shift operation. 0: Enables inputting external clock from the PA3/SCK pin. Internal SCK Enable bit SMR3 1: Outputs internal clock to the PA3/SCK pin.

Table 5 SMR Bit Functions

When the power is turned on  $(V_{DD} = low \rightarrow high)$  or the internal clock is stopped with a CKSTP instruction, the SMR bits are reset to all 0s.

# (1) SMR0 (SO enable bit)

After 1 is set in SMR0 (by executing an SIO XXX1B instruction), the PB<sub>0</sub>/SO pin operates as a serial data output pin, that is, an SO pin. Before executing an SIO XXX1B instruction to use the PB<sub>0</sub>/SO pin as SO, 1 must be set in PB<sub>0</sub>. Otherwise, the SO pin keeps outputting low-level data.

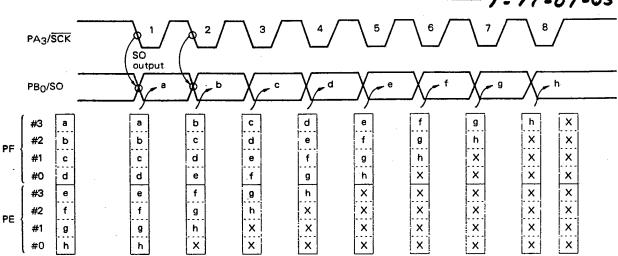

Executing an SIO XX11B instruction sequentially shifts the presettable shift register (PE and PF bits) data from the most significant bit and outputs the shifted data from the PB<sub>0</sub>/SO pin. The PB<sub>0</sub>/SO pin outputs data in synchronization with the falling edge of the clock output (or input) from PA<sub>3</sub>/ $\overline{\text{SCK}}$ . The presettable shift register contents are also shifted at the rising edge of the clock, and at the same time, this register reads data from the PA<sub>2</sub>/SI pin. If the PA<sub>2</sub>/SI pin is operating as a PA<sub>2</sub> output pin, the read data is the contents output from the PA<sub>2</sub> pin.

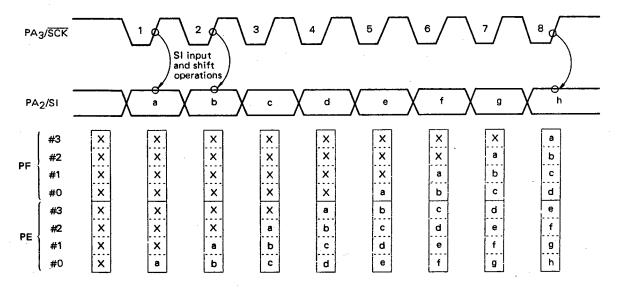

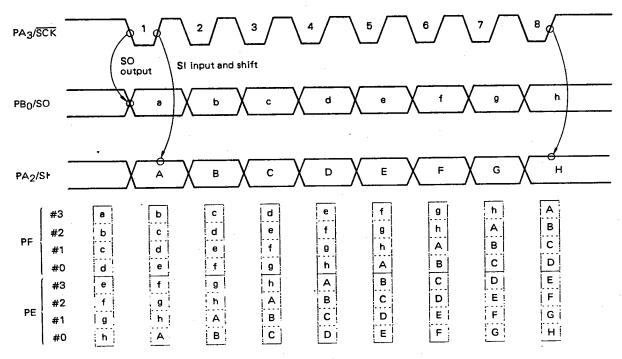

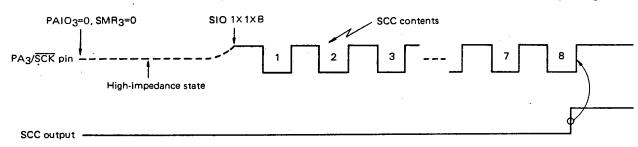

Fig. 8 SO Operation

To use the PB<sub>0</sub>/SO pin as PB<sub>0</sub>, 0 must be set in SMR0 (by executing an SIO XXX0B instruction). When an instruction (such as OUT, SPB, RPB, etc.) for outputting data to PB<sub>0</sub> is executed while SMR 0 is 1, correct data will not be output.

When SMR0 is reset to 0 after a serial output (SO) operation, the  $PB_0/SO$  pin outputs the contents of the  $PB_0$  data latch before the 50 execution, that is, the port B data latch contents.

#### (2) SMR1 (Shift enable bit)

When 1 is set in SMR1, the PA<sub>2</sub>/SI pin contents are read, while being shifted toward the presettable shift register most significant bit (port F bit 3) from the least significant bit (port E bit 0), in synchronization with the clock output (or input) from the PA<sub>3</sub>/ $\overline{SCK}$  pin. The contents are read at the clock's rising edges.

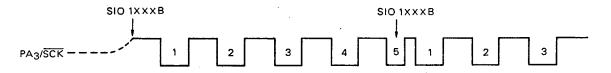

Fig. 9 SI Operation

Before inputting serial data from the PA<sub>2</sub>/SI pin, PA<sub>2</sub> must be placed in the input mode, that is, PAIO word bit 2 must be set to 0. If PA<sub>2</sub> is in the output mode, the PA<sub>2</sub> output contents are sequentially read into the presettable shift register (bits PE and PF) while being shifted. The presettable shift register is set to all 1s when PA<sub>2</sub> outputs 1, and to all 0s when PA<sub>2</sub> outputs 0.

During A-D conversion operation, inputting the shift clock to the presettable shift register must be inhibited by resetting SMR1 to 0.

When 1 is set in SMR0 (by executing an SIO XX11B instruction) while SMR1 is 1, the  $PA_2/SI$  and  $PB_0/SO$  pins operate as the SI and SO pins.

At this time, the data from the SO pin is output at the falling edge of the clock output (or input) from the  $PA_3/\overline{SCK}$  pin and data is shifted in, via SI pin, at the rising edge of the same clock. That is, serial I/O data is first output from the SO pin from the MSB of port F, then read from the SI pin to the LSB of port E synchronized with the shift clock.

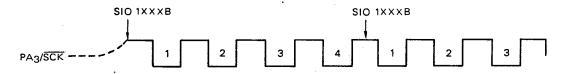

Fig. 10 SIO Operation

As shown in the example above, the presettable shift register contents (bits PF and PE) are sequentially shifted, read, and written. When the  $\mu$ COM standard SI and SO pins are connected to the  $\mu$ PD1711 (or  $\mu$ PD1712) SO and SI pins, the data can be transferred between these devices.

As a general application, serial data can be sent to an external shift register by executing an SIO  $1\times11B$  instruction. Executing this instruction sequentially shifts and outputs the presettable shift register contents (bits PF and PE) from the PB<sub>0</sub>/SO pin, in synchronization with the clock output from the PA<sub>3</sub>/SCK pin.

The presettable register contents are not shifted if SMR1 is 0. The SO pin outputs the last data obtained by executing the previous SIO instruction. Therefore, SMR1 must be set to 1 before using the serial I/O.

#### Example

SOUT:

| ANI   | PAIO, 0111B | ; | Places PAIO#3 in the input mode.     |

|-------|-------------|---|--------------------------------------|

| SPB   | PB, 0001B   | ; | Sets 1 in PBO.                       |

| BANK1 |             |   |                                      |

| OUT   | PE, 02H     | ; | Sets serial output data.             |

| OUT   | PF, 03H     | ; |                                      |

| SIO   | 1011B       | ; | Outputs data by the internal clock.  |

| TSET  |             | ; | Waits until eight clocks are output. |

| JMP   | \$-1        |   |                                      |

| SIO   | 0000B       |   |                                      |

| RT.   |             |   |                                      |

|       |             |   |                                      |

7-77-07-05

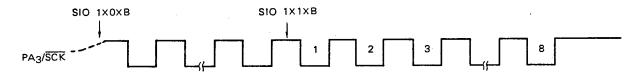

# (3) SMR3 (internal SCK enable bit)

SMR3 selects whether or not the internal or external clock is to be used as the shift clock. Setting 1 in SMR3 causes output of internal clock (15 kHz, duty 15%) from the PA<sub>3</sub>/SCK pin and setting 0 in SMR3 enables external clock input to the PA<sub>3</sub>/SCK pin.