# YAMAHA'L SI

# YM3802

# MIDI Communication & Service Controller (MCS)

#### ■ OUTLINE

The YM3802 is an LSI device featuring an asynchronous serial communication interface, a frequency divider that acts a communication rate generator, an interface for the cassette tape recorder, transmit/receive data buffers, timers, counters and a parallel input/output port. With this LSI a part of the MIDI data processing can be performed by hardware.

The YM3802 LSI has two output pins and three counters that synchronize with the MIDI clock and the tape SYNC can be easily realized. The MIDI clock is generated by the MIDI clock timer, the tape SYNC signal or the clock message which is contained in the received serial data. Another way of the generation of the MIDI clock is a process with the host CPU control. This LSI has the priority transmission and reception capability of the MIDI system real-time message over other messages and also can support the processing of the system exclusive message.

Each of the MIDI counters can be utilized as general-purpose timer/counter.

#### **■ FEATURES**

Serial communication

7- or 8-bits ...... Character

1- or 4-bits ...... Parity bit,

1- or 2-bits ...... Stop bit,

Start bit error detection,

Automatic break detection and break character generation,

Character length, Types of parity and stop bits and communication rate are selectable for transmission and reception separately.

• Cassette tape recorder interface

One-wave/two-wave FSK modulation,

Automatic follow-up function for polarity and phase,

Transfer-rate check function,

Used for ordinary serial communication or cassette tape recorder interface in transmission and reception (separately).

-YAMAHA CORPORATION-

YM3802 CATALOG CATALOG No.: LSI-2138023

1992. 6

• Communication rate generator

Communication rate generation of 75 ~ 19200 bps and 31.25K bps.

Reception is performed at the internal clock rate which is 16 times the communication rate. Communication rates of DC through 125K bps can be obtained by selecting the frequency of the communication rate generating clock.

- General-purpose 8-bit parallel input/output port.

- General-purpose 14-bits timer.

- 128 bytes FIFO buffer for reception and 16 bytes FIFO buffer for transmission.

- MIDI support functions

SYNC out, CLOCK out; output of a pulse signal synchronized to the system real-time message. Automatic transmitting function, priority transmitting function and priority receiving function (without involving the receiving FIFO buffer) of the system real-time message.

8- and 15-bit counters for counting the interpolated, high-accuracy signal of the MIDI clock. Special 14-bit timer for determining MIDI clock generation timing. Detecting function of the MIDI clock from the received serial data.

Tape SYNC function.

Automatic output of the tape SYNC signal

Active sense function

ID code check function for the system exclusive message.

- Vector output function according to 8-level interruput factors

- C-MOS, 4MHz maximum system clock, 50mW power consumption (10mA current consumption)

- Single 5V power supply, TTL level interface

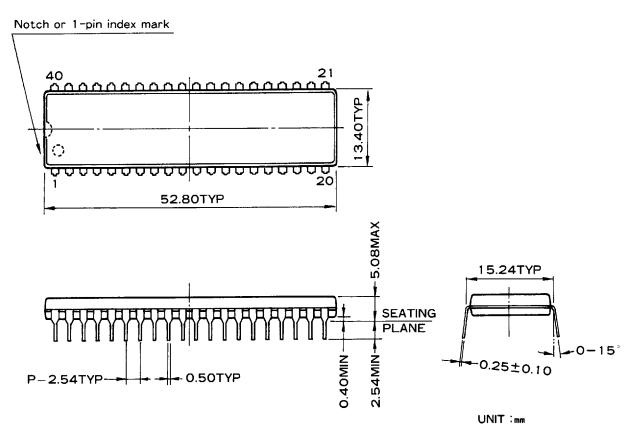

- Package: 40-pin DIP

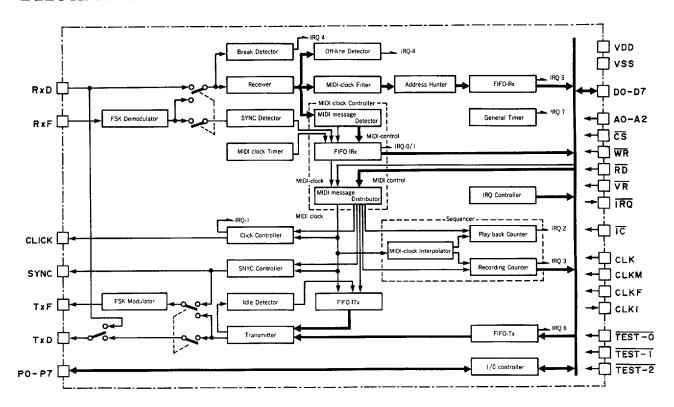

#### **■ BLOCK DIAGRAM**

#### **■ PIN ASSIGNMENT**

|        | 1  | 40   |        |

|--------|----|------|--------|

| VDD    | '  |      | CLK    |

| RxD    | 2  | 39   | CLKI   |

| RxF    | 3  | 38   | TEST-2 |

| CLKM   | 4  | 37   | īC     |

| CLKF   | 5  | 36   | IRQ    |

| ΤxD    | 6  | 35   | VR     |

| TxF    | 7  | 34   | RD     |

| SYNC   | 8  | 33   | WR     |

| CLICK  | 9  | 32   | cs     |

| TEST-0 | 10 | 31   | A2     |

| TEST-I | 11 | 30   | Αï     |

| P7     | 12 | 29   | AO     |

| P6     | 13 | 28   | D7     |

| P5     | 14 | 27   | D6     |

| P4     | 15 | 26   | D5     |

| P3     | 16 | 25   | D4     |

| P2     | 17 | 24   | D3     |

| PΙ     | 18 | 23   | D2     |

| PO     | 19 | 22   | DI     |

| vss    | 20 | 21   | DO     |

|        |    | <br> | J      |

#### **■ PIN FUNCTIONS**

The pin configuration is shown in Fig. 2.1.

# • IC ... Input

The YM3802 is reset by the low level input signal to this terminal. The reset pulse width must be more than 32 clocks of the system clock to the CLK terminal (32 TCLK).

The same reset operation can be made by the host CPU operation on the internal registers of YM3802.

#### • CLK ... Input

System clock input terminal

The internal operation of the YM3802, input signal sampling and output signal changing are all performed in synchronization with the internal timing clock made by this system clock. The clock rate must be more than 32 times the communication rate used. In the case of an MIDI communication rate of 31.25K bps at least a 1MHz clock rate is necessary. The maximum rate is 4MHz.

#### • CLKI ... Output

Internal timing clock output terminal.

#### • CLKM ... Input

Input terminal for a clock that generates an MIDI communication rate of 31.25K bps (baud). Usually 1MHz or 0.5MHz is input, and 1/16 or 1/32 of this can be used as the communication rate.

This clock signal is divided to obtain a count clock for the general-purpose timer and the MIDI clock timer and also for the output pulse width at the SYNC and CLICK terminals. A divide-by-two circuit is included so that the same setting time can be obtained, irrespective of the input signal to the CLKM terminal (1MHz or 0.5MHz).

#### • CLKF ... Input

Input terminal for a clock that generates a communication rate of  $75 \times 2^n$  series. Usually an input of 614.4KHz is required to obtain the communication rates from 1/8192nd of this frequency (75 bps) to 1/32nd of the same frequency (19200 bps). This input can be used also for counting in the MIDI active sense function.

#### • D0 ~ D7 ...Input/Output

| A0 ~                   | A2 Input |

|------------------------|----------|

| CS                     | Input    |

| $\overline{WR}$        | Input    |

| $\overline{\text{RD}}$ | Input    |

| $\overline{VR}$        | Input    |

| ĪRQ                    | Output   |

These terminals are used to provide interface to the host CPU.

• TEST-0 ~ TEST-2 ... Input

Terminals used for testing the LSI. Thus, no connections are generally made.

# RxD ... Input Serial data input terminal

# • TxD ... Output Serial data output terminal

#### • RxF ... Input

Audio signal input terminal from the magnetic tape such as a cassette tape. FSK-modulated serial data are input to this terminal at the TTL level.

#### • TxF ... Output

Audio signal output terminal to the magnetic tape such as a cassette tape. FSK-modulated serial data are output from this terminal at the TTL level.

# • SYNC ... Output

A 2msec width pulse is output from this terminal in synchronization with the MIDI clock. It is used as a SYNC signal for other hardware.

# • CLICK ... Output

A 2msec width pulse is output from this terminal in synchronization with the MIDI clock signal. These pulses occur at a frequency that is a fraction of the MIDI clock signal frequency. It can be used as a metronome, etc., which is synchronized with the MIDI clock.

P0 ~ P7 ... Input/Output

General-purpose I/O port with which the input/output direction of each bit can be separately

#### **■ ELECTRICAL CHARACTERISTICS**

#### **Absolute Maximum Ratings**

| ITEM                  | SYMBOL | RATING           | UNITS |

|-----------------------|--------|------------------|-------|

| Supply voltage        | VDD    | $-0.3 \sim +7.0$ | V     |

| Input voltage         | VI     | $-0.3 \sim +0.5$ | v     |

| Operating temperature | Тор    | 0 ~ 70           | °C    |

| Storage temperature   | Tstg   | <b>−50</b> ~ 125 | °C    |

## Recommended Operating Conditions (Ta = $0 \sim 70^{\circ}$ C)

| ITEM                  | SYMBOL | MIN. | TYP. | MAX. | UNITS |

|-----------------------|--------|------|------|------|-------|

| Supply voltage        | VDD    | 4.75 | 5.00 | 5.25 | v     |

| Operating temperature | Тор    | 0    |      | 70   | °C    |

#### **Electrical Characteristics**

#### (A) DC characteristics

| ITEM                      | SYMBOL | CONDITIONS                                                                     | MIN. | TYP. | MAX.    | UNITS |

|---------------------------|--------|--------------------------------------------------------------------------------|------|------|---------|-------|

| Input low level voltage   | VIL    |                                                                                | -0.3 | _    | 0.8     | V     |

| Input high level voltage  | Vih    |                                                                                | 2.0  | _    | VDD+0.5 | v     |

| Input leakage current     | Ilk    | $VI = 0 \sim 5V$<br>(Except for the pins with pull-up registers)               | _    | _    | 10      | μА    |

| Pull-up resister          | Ru     | $(\overline{\text{TEST0}} \sim \overline{\text{TEST2}}, \overline{\text{IC}})$ | 100  | _    | 1000    | ΚΩ    |

| Output low level voltage  | Vol    | $IOL = 2mA$ $(P0 \sim P7, D0 \sim D7, \overline{1RQ})$                         | Vss  | _    | 0.4     | v     |

| Output low level voltage  | Vol    | IOL = 1mA<br>(Output terminals other than shown above)                         | Vss  | _    | 0.4     | v     |

| Output high level voltage | Ior    | $IOH = -1 \underline{MA}$ (Except for $\overline{IRQ}$ )                       | 4.0  | _    | VDD     | v     |

| Output leakage current    | Iol    | $V_O = 0 \sim 5V$                                                              |      |      | 10      | μΑ    |

| Power supply current      | IDP    | $V_{DD} = 5V$                                                                  | _    | 6    | 10      | mA    |

| Input capacitance         | Cı     | f = 1MHz                                                                       |      | _    | 10      | pF    |

| Output land consistence   | CLI    | $P0 \sim P7, D0 \sim D7,$ $\overline{IRQ}$                                     | _    | _    | 100     | pF    |

| Output load capacitance   | CL2    | Output terminals other than shown above                                        | _    | _    | 50      | pF    |

# (B) AC characteristics

#### • CLK input

| ITEM                   | SYMBOL      | MIN. | MAX. | UNIT  |

|------------------------|-------------|------|------|-------|

| CLK Cycle time         | tcc         | 250  | 2500 | n sec |

| CLK H level setup time | thc         | 100  |      | n sec |

| CLK L level setup time | trc         | 100  |      | n sec |

| CLK Build up time      | trc         | _    | 20   | n sec |

| CLK Release time       | <b>t</b> FC | _    | 20   | n sec |

#### • CLK input and output pins

| ITEM                                | SYMBOL       | MIN.         | MAX. | UNIT  |

|-------------------------------------|--------------|--------------|------|-------|

| CLK-CLKI Delay time*1               | <b>t</b> DCC | _            | 50   | n sec |

| CLK-output change over delay time*1 | tdoc         | <del>-</del> | 100  | n sec |

\*1 : CLIK, SYNC, TXF, TXD,  $\overline{IRQ}$

#### • Register write

| ITEM                | SYMBOL | MIN. | MAX. | UNIT  |

|---------------------|--------|------|------|-------|

| Address setup time  | tsaw   | 20   |      | n sec |

| Address hold time   | thaw   | 20   |      | n sec |

| CS · WR Pulse width | tww    | 100  |      | n sec |

| Data setup time     | tsow   | 50   |      | n sec |

| Data hold time      | thdw   | 20   | _    | n sec |

# • Register read-out

| ITEM                 | SYMBOL | MIN. | MAX. | UNIT  |

|----------------------|--------|------|------|-------|

| Address setup time   | tsar   | 20   |      | n sec |

| Address hold time    | thar   | 20   | _    | n sec |

| CS · WR Setup time*2 | tsrc   | 0    | _    | n sec |

| CS · WR Hold time*2  | thrc   | 150  | _    | n sec |

| Data access time*2   | tade   |      | 150  | n sec |

| Data hold time       | thdr   | 5    | _    | n sec |

#### \*2: Time corresponding to the CLK

## • IRQ vector read-out

| ITEM              | SYMBOL | MIN.         | MAX. | UNIT  |

|-------------------|--------|--------------|------|-------|

| VR Setup time*    | tsvc   | 0            | _    | n sec |

| VR Hold time*     | thvc   | 150          |      | n sec |

| Data access time* | tadc   | <del>-</del> | 150  | n sec |

| Data hold time    | thdv   | 5            |      | n sec |

# $\ensuremath{\boldsymbol{\ast}}$ : Time corresponding to the CLK

## • I/O port output

| ITEM               | SYMBOL | MIN. | MAX. | UNIT  |

|--------------------|--------|------|------|-------|

| Clock setup time   | tscw   | 70   | _    | n sec |

| CS · WR Setup time | tswc   | 0    |      | n sec |

| I/O port hold time | tapc●  | 100  |      | n sec |

# • I/O port input

| ITEM                | SYMBOL | MIN. | MAX. | UNIT  |

|---------------------|--------|------|------|-------|

| Clock setup time    | tscr   | 70   | _    | n sec |

| CS · RD Setup time  | tsrc   | 0    |      | n sec |

| I/O port setup time | tspc   | 0    | _    | n sec |

| I/O port hold time  | tнрс   | 100  |      | n sec |

• Terminal input (CLKM, CLKF, RxD, RxF, IC)

| ITEM                    | SYMBOL | MIN. | MAX. | UNIT  |

|-------------------------|--------|------|------|-------|

| Input signal setup time | tsic   | 0    |      | n sec |

| Input signal hold time  | tніс   | 70   | _    | n sec |

(Note 1): Perfect operation of the  $\overline{IC}$  requires sampling on the L level 32 times.

(Note 2): At least one sampling is made if the setup period for the L-or H-level is T CLK or more.

#### **■ OUTLINE DIMENSIONS**

The specifications of this product are subject to improvement changes without prior notice.

# -YAMAHA CORPORATION-

# -YAMAHA CORPORATION-

Address inquiries to:

■ Osaka Office

Semi-conductor Sales Department

■ Head Office 203, Matsunokijima, Toyooka-mura,

Iwata-gun, Shizuoka-ken, 438-01

Electronic Equipment business section

Tel. 0539-62-4918 Fax. 0539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108

Tel. 03-5488-5431 Fax. 03-5488-5088

3-12-9, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542

Shinsaibashi Plaza Bldg. 4F Tel. 06-252-7980 Fax. 06-252-5615

■U.S.A. Office YAMAHA Systems Technology.

100 Century Center Court, San Jose, CA95112 Tel. 408-467-2300 Fax. 408-437-8791

46765