#### **Features**

- 1,048,576 word by 4 bit organization

- Power Supply: 3.3 ± 0.3V or 5.0 ± 0.5V

- Standard Power (SP) and Low Power (LP)

- 1024 Refresh Cycles

- 16 ms Refresh Rate (SP version)

- 128 ms Refresh Rate (LP version)

- · High Performance:

|                  |                            | -60   | -70   |

|------------------|----------------------------|-------|-------|

| t <sub>RAC</sub> | RAS Access Time            | 60ns  | 70ns  |

| t <sub>CAC</sub> | CAS Access Time            | 15ns  | 18ns  |

| t <sub>AA</sub>  | Column Address Access Time | 30ns  | 35ns  |

| t <sub>RC</sub>  | Cycle Time                 | 110ns | 130ns |

| t <sub>PC</sub>  | Fast Page Mode Cycle Time  | 40ns  | 40ns  |

- · Power Dissipation

- Active (max)

- 85 mA / 70 mA (5.0V)

- 95 mA / 80 mA (3.3V)

- Standby Current: TTL Inputs (max)

- 2.0 mA (SP version)

- 1.0 mA (LP version)

- Standby Current: CMOS Inputs (max)

- 1.0 mA (SP version)

- 0.15 mA (LP version)

- Fast Page Mode

- RAS Only, and CAS before RAS Refresh

- Hidden Refresh

- Self-Refresh (LP version only)

- Packages: SOJ-26/20 (300mil) TSOP-26/20 (300mil)

#### **Description**

The IBM014400 is a fast-page dynamic RAM organized 1,048,576 words by 4 bits. The devices are fabricated in IBM's 4M-bit Shrink 2 CMOS silicon gate technology. The circuits and process have been designed to provide high performance, low power dissipation, and high reliability. The devices operate with either a  $5.0V\pm0.5V$  or  $3.3V\pm0.3V$  power supply and are offered in a plastic 26/20 pin SOJ (300mil) or TSOP (300mil) package. Refreshing may be accomplished by means of a  $\overline{CAS}$  before  $\overline{RAS}$  refresh cycle (CBR) that internally generates the refresh address.  $\overline{RAS}$  - only refresh cycles can

also refresh all memory locations. Self-Refresh mode is entered by holding  $\overline{RAS}$  low for  $\geq 100 \mu S$  during a CBR cycle. Detection of this long  $\overline{RAS}$  time during a CBR cycle starts an internal oscillator that maintains data integrity without external clocking. Self-Refresh mode is included as a standard feature for Low Power devices (IBM014400M and IBM014400P). Self Refresh operating current is  $\leq 170 \mu A$  (max) and typically  $\leq 100 \mu A$ . All low power devices support Extended Data Retention of 128ms, eight times (8x) the retention supported by IBM's standard power devices.

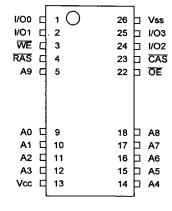

#### Pin Assignments

#### Pin Description

| A0 - A9         | Address Input         |

|-----------------|-----------------------|

| I/O0 - I/O3     | Data Input/Output     |

| RAS             | Row Address Strobe    |

| CAS             | Column Address Strobe |

| WE              | Read/Write Input      |

| ŌĒ              | Output Enable         |

| V <sub>CC</sub> | Power (5.0V or 3.3V)  |

| V <sub>SS</sub> | Ground                |

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 1 of 24

IBM

#### **Ordering Information**

| Part Number      | SP/LP | Self Refresh | Power Supply | Speed | Package           | Notes |

|------------------|-------|--------------|--------------|-------|-------------------|-------|

| IBM014400J1 -60  | SP    | No           | 5.0V         | 60ns  | 300mil SOJ 26/20  | 1     |

| IBM014400J1 -70  | SP    | No           | 5.0V         | 70ns  | 300mil SOJ 26/20  | 1     |

| IBM014400BJ1 -60 | SP    | No           | 3.3V         | 60ns  | 300mil SOJ 26/20  | 1     |

| IBM014400BJ1 -70 | SP    | No           | 3.3V         | 70ns  | 300mil SOJ 26/20  | 1     |

| IBM014400MJ1 -60 | LP    | Yes          | 5.0V         | 60ns  | 300mil SOJ 26/20  | 1     |

| IBM014400MJ1 -70 | LP    | Yes          | 5.0V         | 70ns  | 300mil SOJ 26/20  | 1     |

| IBM014400PJ1 -60 | LP    | Yes          | 3.3V         | 60ns  | 300mil SOJ 26/20  | 1     |

| IBM014400PJ1 -70 | LP    | Yes          | 3.3V         | 70ns  | 300mil SOJ 26/20  | 1     |

| IBM014400MT1 -60 | LP    | Yes          | 5.0V         | 60ns  | 300mil TSOP 26/20 | 1     |

| IBM014400MT1 -70 | LP    | Yes          | 5.0V         | 70ns  | 300mil TSOP 26/20 | 1     |

| IBM014400PT1 -60 | LP    | Yes          | 3.3V         | 60ns  | 300mil TSOP 26/20 | 1     |

| IBM014400PT1 -70 | LP    | Yes          | 3.3V         | 70ns  | 300mil TSOP 26/20 | 1     |

<sup>1.</sup> SP = Standard Power version (IBM014400 and IBM014400B); LP = Low Power version (IBM014400M and IBM014400P)

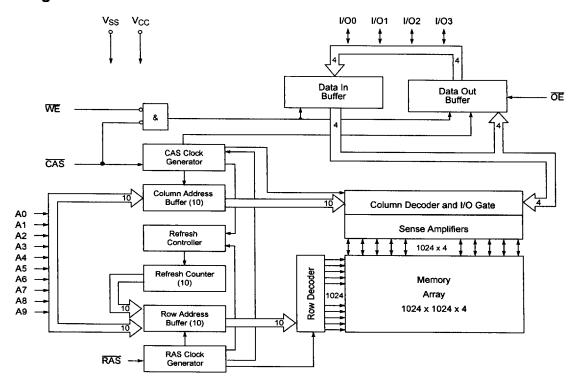

## **Block Diagram**

#### **Truth Table**

| Function                       |                        | RAS   | CAS | WE  | ŌĒ  | Row<br>Address | Col.<br>Address   | I/O0 - I/O3       |

|--------------------------------|------------------------|-------|-----|-----|-----|----------------|-------------------|-------------------|

| Standby                        |                        | Н     | H→X | ×   | ×   | ×              | ×                 | High Impedance    |

| Read                           |                        | L     | L   | н   | L   | Row            | Col.              | Data Out          |

| Early-Write                    |                        | Ł     | L   | L   | х   | Row            | Col.              | Data In           |

| Delayed-Write                  | L                      | L     | H→L | н   | Row | Col.           | Data In           |                   |

| Read-Modify-Write              | L                      | L     | H→L | L→H | Row | Col.           | Data Out, Data In |                   |

| Fast Page Mode Read            | 1st Cycle              | L     | H→L | н   | L   | Row            | Col.              | Data Out          |

| r ast rage Mode Read           | 2nd Cycle              | L     | H→L | Н   | L   | N/A            | Col.              | Data Out          |

| Fast Page Mode Write           | 1st Cycle              | L     | H→L | L   | Х   | Row            | Col.              | Data In           |

| T ast Fage Mode Wille          | 2nd Cycle              | L     | H→L | L   | Х   | N/A            | Col.              | Data In           |

| Fast Page Mode Read-Modify-    | 1st Cycle              | L     | H→L | H→L | L→H | Row            | Col.              | Data Out, Data In |

| Write                          | 2nd Cycle              | L     | H→L | H→L | L→H | N/A            | Col.              | Data Out, Data In |

| RAS-Only Refresh               |                        | L     | Н   | ×   | ×   | Row            | N/A               | High Impedance    |

| CAS-Before-RAS Refresh         | CAS-Before-RAS Refresh |       | L   | н   | х   | х              | N/A               | High impedance    |

| Hidden Refresh Read            |                        | L→H→L | L   | н   | L   | Row            | Col.              | Data Out          |

| Self Refresh (LP version only) |                        | H→L   | L   | L   | н   | х              | х                 | X                 |

27H4339 SA14-4219-04 Revised 6/96 ©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 3 of 24

■ 9006146 0002957 681 **■**

#### **Absolute Maximum Ratings**

| Symbol           | Parameter                    | Ra                                      | Rating                                  |                 |       |  |  |

|------------------|------------------------------|-----------------------------------------|-----------------------------------------|-----------------|-------|--|--|

| Symbol           | Farameter                    | 3.3 Volt Device                         | 5.0 Volt Device                         | Units           | Notes |  |  |

| Vcc              | Power Supply Voltage         | -0.5 to +4.1                            | -1.0 to +6.0                            | V               | 1     |  |  |

| Vin              | Input Voltage                | -0.5 to min (V <sub>CC</sub> +0.5, 4.1) | -0.5 to min (V <sub>CC</sub> +0.5, 6.0) | V               | 1     |  |  |

| Vout             | Output Voltage               | -0.5 to min (V <sub>CC</sub> +0.5, 4.1) | -0.5 to min (V <sub>CC</sub> +0.5, 6.0) | V               | 1     |  |  |

| TA               | Operating Temperature        | 0 to +70                                | 0 to +70                                | <sup>†</sup> °C | 1     |  |  |

| T <sub>STG</sub> | Storage Temperature          | -55 to +150                             | -55 to +150                             | °C              | 1     |  |  |

| PD               | Power Dissipation            | 1.0                                     | 1.0                                     | w               | 1     |  |  |

| l <sub>out</sub> | Short Circuit Output Current | 20                                      | 50                                      | mA              | 1     |  |  |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# Recommended DC Operating Conditions ( $T_A=0$ to $70^{\circ}$ C)

| Symbol          | Parameter          | 5.0 Volt Devices |      |                       | 3    | .3 Volt Devi | ces                   |       | Netes |

|-----------------|--------------------|------------------|------|-----------------------|------|--------------|-----------------------|-------|-------|

|                 | ratameter          | Min.             | Тур. | Max.                  | Min. | Тур.         | Max.                  | Units | Notes |

| V <sub>CC</sub> | Supply Voltage     | 4.5              | 5.0  | 5.5                   | 3.0  | 3.3          | 3.6                   | V     | 1     |

| V <sub>IH</sub> | Input High Voltage | 2.4              | _    | V <sub>CC</sub> + 0.5 | 2.0  |              | V <sub>CC</sub> + 0.3 | ٧     | 1     |

| V <sub>IL</sub> | Input Low Voltage  | -0.5             | _    | 0.8                   | -0.3 |              | 0.8                   | ٧     | 1     |

<sup>1.</sup> All voltages referenced to V<sub>SS</sub>=0V.

## Capacitance (T<sub>A</sub>=25°C, f=1MHz)

| Symbol          | Parameter                            | Min. | Max | Units | Notes |

|-----------------|--------------------------------------|------|-----|-------|-------|

| C <sub>I1</sub> | Input Capacitance (Addresses)        |      | 5   | pF    | 1     |

| C <sub>12</sub> | Input Capacitance (RAS, CAS, WE, OE) |      | 7   | pF    | 1     |

| C <sub>o</sub>  | Output Capacitance (I/O's)           | _    | 7   | pF    | 1     |

<sup>1.</sup> Input capacitance measurements made with rise time shift method with  $\overline{CAS} = V_{IH}$  to disable output.

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H4339 SA14-4219-04 Revised 6/96

Page 4 of 24

9006146 0002958 518

# DC Electrical Characteristics (TA= 0 to +70 C, $V_{CC}$ = 3.3V $\pm$ 0.3V or $V_{CC}$ = 5.0V $\pm$ 0.5V)

| Symbol            | Barameter                                                                                                                                                                                               |               | 3.3 Vol      | Device   | 5.0 Vol     | t Device |       |         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|----------|-------------|----------|-------|---------|

| Symbol            | Parameter                                                                                                                                                                                               |               | Min.         | Max.     | Min.        | Max.     | Units | Notes   |

| l <sub>CC1</sub>  | Operating Current Average Power Supply Operating Current (RAS and CAS Cycling: t <sub>RC</sub> = t <sub>RC</sub> min.)                                                                                  | -60<br>-70    | _            | 95<br>80 | _           | 85<br>70 | mA    | 1,2,3,4 |

| I <sub>CC2</sub>  | Standby Current (TTL) Power Supply Standby Current                                                                                                                                                      | SP version    | _            | 2.0      | _           | 2.0      | mA    | 4       |

| ···               | (RAS = CAS ≥ V <sub>IH</sub> min)                                                                                                                                                                       | LP version    | <u> </u>     | 1.0      | <del></del> | 1.0      |       |         |

| I <sub>CC3</sub>  | RAS Only Refresh Current Average Power Supply Current, RAS Only Mode (RAS Cycling, CAS ≥ V <sub>IH</sub> min: t <sub>RC</sub> = t <sub>RC</sub> min)                                                    | -60<br>-70    | <del>-</del> | 95<br>80 |             | 85<br>70 | mA    | 1,3,4   |

| loo.              | Fast Page Mode Current Average Power Supply Current, Fast Page Mode                                                                                                                                     | -60           |              | 65       | _           | 60       |       |         |

| ICC4              | $(RAS \le V_{IL} min, CAS Cycling, tPC = tPC min)$                                                                                                                                                      | -70           | _            | 65       | _           | 60       | mA    | 1,2,3,4 |

| 1                 | Standby Current (CMOS) Power Supply Standby Current                                                                                                                                                     | SP version    | -            | 1        | _           | 1        | _     |         |

| I <sub>CC5</sub>  | (RAS = CAS ≥ V <sub>IH</sub> )                                                                                                                                                                          | LP version    | _            | 0.15     |             | 0.15     | mA    | 7,8     |

| I <sub>CC6</sub>  | CAS Before RAS Refresh Current Average Power Supply Current, CAS Before RAS Mode (RAS Cycling, CAS before RAS, t <sub>RC</sub> = t <sub>RC</sub> min)                                                   | -60<br>-70    | _            | 95<br>80 | _           | 85<br>70 | mA    | 1,3,4,5 |

| I <sub>CC7</sub>  | Self Refresh Current, LP version only Average Power Supply Current during Self Refresh (CBR cycle with RAS ≥ t <sub>RASS</sub> (min))                                                                   | -             | 170          | _        | 170         | μA       | 7,8   |         |

| I <sub>CC8</sub>  | Battery Backup Refresh Current, LP version only Average Power Supply Current during Battery Backup re (CAS ≤V <sub>IL</sub> , WE ≥V <sub>IH</sub> , t <sub>RAS</sub> ≤ 1μSec, t <sub>RC</sub> =125μSec) | rfresh        | _            | 300      | _           | 300      | μА    | 7,8,9   |

| I <sub>CC9</sub>  | Standby Current Standby current with Output's enabled (RAS ≥ V <sub>IH</sub> (min) and CAS ≤ V <sub>IL</sub> (max))                                                                                     |               | _            | 5        | _           | 5        | mA    | 4,6     |

| l <sub>I(L)</sub> | Input Leakage Current, any input $(0.0 \le V_{IN} \le (V_{CC} + 1.0V))$ for 5.0V, or $(0.0 \le V_{IN} \le (V_{CC} + 0.3V))$ for 3.3V. All Other Pins Not Un                                             | der Test = 0V | -10          | +10      | -10         | +10      | μА    |         |

| I <sub>O(L)</sub> | Output Leakage Current ( $D_{OUT}$ is disabled, $0.0 \le V_{OUT} \le V_{CC}$ max)                                                                                                                       |               | -10          | +10      | -10         | +10      | μА    |         |

| V <sub>OH</sub>   | Output Level (TTL) Output "H" Level Voltage (I <sub>OUT</sub> = -5mA for 5.0V, or I <sub>OUT</sub> = -2mA for 3.3V)                                                                                     |               | 2.4          | Vcc      | 2.4         | Vcc      | v     |         |

| V <sub>OL</sub>   | Output Level (TTL) Output "L" Level Voltage (I <sub>OUT</sub> = +4.2mA for 5.0V, or I <sub>OUT</sub> = +2mA for 3.3V)                                                                                   |               | _            | 0.4      | _           | 0.4      | v     |         |

- 1.  $I_{CC1}$ ,  $I_{CC3}$ ,  $I_{CC4}$  and  $I_{CC6}$  depend on cycle rate.

- 2.  $I_{\text{CC1}}$  and  $I_{\text{CC4}}$  depend on output loading. Specified values are obtained with the output open.

- 3. Column address can be changed once or less while  $\overline{RAS}$  =V<sub>IL</sub> and  $\overline{CAS}$  =V<sub>IH</sub>.

- 4. All I/O and other input pins must be  $\leq V_{IL}(max)$  or  $\geq V_{IH}(min)$ .

- 5. Enables on-chip refresh and address counters.

- 6. Assumes no resistive loads on I/O pins.

- 7.  $((V_{CC}-0.2V \le V_{IH} \le V_{CC}+0.5V)$  and  $(0.0V \le V_{IL} \le 0.2V))$  for 5.0V, or  $((V_{CC}-0.2V \le V_{IH} \le V_{CC}+0.3V))$  and  $(0.0V \le V_{IL} \le 0.2V))$  for 3.3V.

- 8. All other I/O and other inputs at  $V_{IH}$  or  $V_{IL}$ .

- 9. 1024 rows at 128µs = 128ms.

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 5 of 24

**9**006146 0002959 454 **5**

#### AC Characteristics (T<sub>A</sub>=0 to +70°C)

- 1. An initial pause of 100µs is required after power-up followed by 8 RAS only refresh cycles or 8 CAS before RAS refresh cycles.

- 2. AC measurements assume t<sub>T</sub>=5ns.

- 3. V<sub>IH</sub>(min) and V<sub>IL</sub>(max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>).

- 4. In addition to meeting the transition rate specification, all input signals must transit between V<sub>IL</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>) in a monotonic manner.

- 5. If  $\overline{\text{OE}}$  is tied permanently low, Late-Write or Read-Modify-Write operations are not possible.

- If CAS ≥ V<sub>IH</sub>(min), data outputs are in high impedance.

#### Read, Write, Read-Modify-Write and Ref. Cycles (Common Parameters)

| Symbol           | Parameter                           | -(   | 60       | -7   | 0    | Linito | Notes |

|------------------|-------------------------------------|------|----------|------|------|--------|-------|

| Cymbol           | Falameter                           | Min. | Max.     | Min. | Max. | Units  | Notes |

| t <sub>RC</sub>  | Random Read or Write Cycle Time     | 110  | _        | 130  | _    | ns     |       |

| t <sub>RP</sub>  | RAS Precharge Time                  | 40   | _        | 50   | _    | ns     |       |

| t <sub>CP</sub>  | CAS Precharge Time                  | 10   |          | 10   | _    | ns     |       |

| t <sub>RAS</sub> | RAS Pulse Width                     | 60   | 10K      | 70   | 10K  | ns     |       |

| t <sub>CAS</sub> | CAS Pulse Width                     | 15   | 100K     | 18   | 100K | ns     |       |

| t <sub>asr</sub> | Row Address Setup Time              | 0    | _        | 0    | _    | ns     |       |

| t <sub>RAH</sub> | Row Address Hold Time               | 10   | _        | 10   | _    | ns     | ,     |

| tasc             | Column Address Setup Time           | 0    | _        | 0    | _    | ns     |       |

| <b>t</b> CAH     | Column Address Hold Time            | 10   |          | 10   | _    | ns     |       |

| t <sub>RCD</sub> | RAS to CAS Delay Time               | 20   | 45       | 20   | 52   | ns     | 3     |

| t <sub>RAD</sub> | RAS to Column Address Delay Time    | 13   | 30       | 15   | 35   | ns     | 4     |

| t <sub>RSH</sub> | RAS Hold Time                       | 15   | _        | 18   | _    | ns     |       |

| t <sub>сsн</sub> | CAS Hold Time                       | 60   | _        | 70   | _    | ns     |       |

| t <sub>CRP</sub> | CAS to RAS Precharge Time           | 5    | <b> </b> | 5    | _    | ns     |       |

| t <sub>ODD</sub> | ŌĒ to D <sub>IN</sub> Delay Time    | 15   |          | 20   | _    | ns     | 5     |

| t <sub>DZO</sub> | OE Delay Time From D <sub>IN</sub>  | 0    | _        | 0    |      | ns     | 6     |

| t <sub>DZC</sub> | CAS Delay Time From D <sub>IN</sub> | 0    | <u> </u> | 0    |      | ns     | 6     |

| t <sub>T</sub>   | Transition Time (Rise and Fall)     | 3    | 50       | 3    | 50   | ns     | 1,2,  |

- 1. AC measurements assume t<sub>T</sub>=5ns.

- V<sub>IH</sub>(min) and V<sub>IL</sub>(max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>H</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>).

- 3. Operation within the t<sub>RCD</sub>(max) limit ensures that t<sub>RAC</sub>(max) can be met. t<sub>RCD</sub>(max) is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled by t<sub>CAC</sub>.

- 4. Operation within the t<sub>RAD</sub>(max) limit ensures that t<sub>RAC</sub>(max) can be met. t<sub>RAD</sub>(max) is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max) limit, then access time is controlled by t<sub>A</sub>.

- 5. Either t<sub>CDD</sub> or t<sub>ODD</sub> must be satisfied.

- 6. Either t<sub>DZC</sub> or t<sub>DZO</sub> must be satisfied.

- 7. In addition to meeting the transition rate specification, all input signals must transit between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>) in a monotonic manner.

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H4339 SA14-4219-04 Revised 6/96

Page 6 of 24

**■** 9006146 0002960 176 **==**

IBM014400 IBM014400M IBM014400P

1M x 4 10/10 DRAM

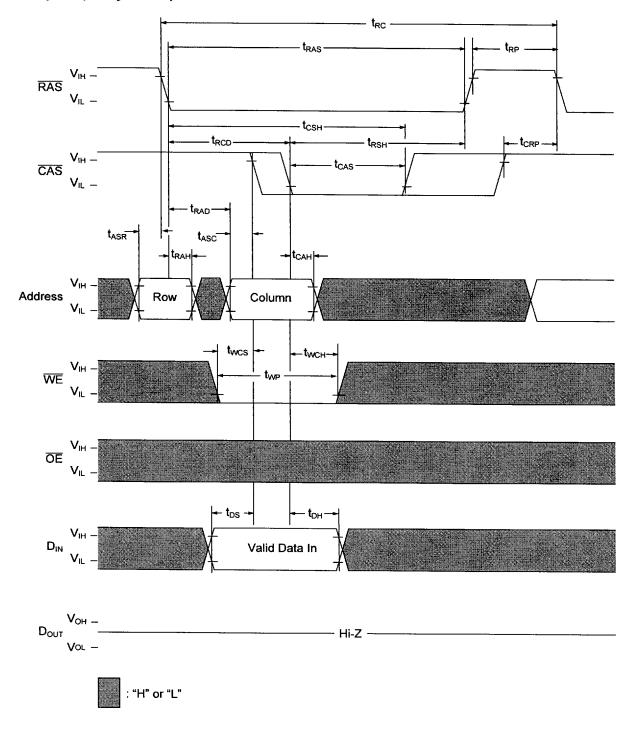

#### **Write Cycle**

| Symbol           | Parameter                      | -(   | 60   | -    | 70   | Units | Notes |

|------------------|--------------------------------|------|------|------|------|-------|-------|

| - Cyrribor       | Falamete                       | Min. | Max. | Min. | Max. |       |       |

| twcs             | Write Command Set Up Time      | 0    |      | 0    | _    | ns    | 1,3,4 |

| twch             | Write Command Hold Time        | 10   |      | 15   | _    | ns    | 3     |

| t <sub>WP</sub>  | Write Command Pulse Width      | 10   | _    | 15   | _    | ns    | 3     |

| t <sub>RWL</sub> | Write Command to RAS Lead Time | 15   | _    | 18   | _    | ns    |       |

| tcwL             | Write Command to CAS Lead Time | 15   |      | 18   | _    | ns    |       |

| tos              | D <sub>IN</sub> Setup Time     | 0    | _    | 0    | _    | пѕ    | 2     |

| t <sub>DH</sub>  | D <sub>IN</sub> Hold Time      | 12   | _    | 15   | _    | ns    | 2     |

- 1. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. t<sub>RWD</sub>, t<sub>CWD</sub>, and t<sub>AWD</sub> apply to Read-Modify-Write cycles. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min), the cycle is an Early Write cycle and the data I/O pins will remain open circuit (high impedance) throughout the entire cycle. If t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>AWD</sub> ≥ t<sub>AWD</sub>(min), the cycle is a Read-Modify-Write cycle and the data I/O pins will contain read data from the selected cells. If neither of the above sets of conditions are satisfied, the condition of the data I/O pins (at access time) is indeterminate.

- These parameters are referenced to the falling edge of CAS for Early-Write cycles and to the falling edge of WE for Delayed-Write

or Read-Modify-Write cycles.

- 3. Parameter two is applicable for a Delayed-Write cycle such as a Read-Write or Read-Modify-Write cycle. For Early-Write cycles, both twos and two must be met.

- 4. The I/O pins go into high impedance during Read cycles once t<sub>OEZ</sub> of t<sub>OFF</sub> occurs. If <del>CAS</del> goes high first, <del>OE</del> becomes a "don't care". If <del>OE</del> goes high and <del>CAS</del> stays low, <del>OE</del> is not a "don't care", and the I/Os will provide the previously read data if <del>OE</del> is taken back low (while <del>CAS</del> remains low).

#### Read-Modify-Write-Cycle

| Symbol           | Parameter                       | -    | -60  |      | 70   | Units |       |

|------------------|---------------------------------|------|------|------|------|-------|-------|

| Cymbol           |                                 | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>RWC</sub> | Read-Modify-Write Cycle Time    | 145  | _    | 175  | _    | ns    |       |

| t <sub>RWD</sub> | RAS to WE Delay Time            | 80   | _    | 90   | _    | ns    | 1     |

| tcwp             | CAS to WE Delay Time            | 35   | _    | 40   | _    | ns    | 1     |

| t <sub>AWD</sub> | Column Address to WE Delay Time | 50   |      | 55   | _    | ns    | 1     |

| t <sub>OEH</sub> | OE Command Hold Time            | 15   | _    | 15   | _    | ns    | 2     |

- 1. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are not restrictive operating parameters. t<sub>RWD</sub>, t<sub>CWD</sub>, and t<sub>AWD</sub> apply to Read-Modify-Write cycles. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min), the cycle is an Early Write cycle and the data I/O pins will remain open circuit (high impedance) throughout the entire cycle. If t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>AWD</sub> ≥ t<sub>AWD</sub>(min), the cycle is a Read-Modify-Write cycle and the data I/O pins will contain read data from the selected cells. If neither of the above sets of conditions are satisfied, the condition of the data I/O pins (at access time) is indeterminate.

- These parameters are referenced to the falling edge of CAS for Early-Write cycles and to the falling edge of WE for Late-Write and Read-Modify-Write cycles must have both toez and toeH satisfied (OE high during Write cycle) in order to insure that the output buffers will be in high impedance during the Write cycle. The data I/O pins will remain in high impedance until the next valid Read cycle.

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 7 of 24

9006146 0002961 002 🖿

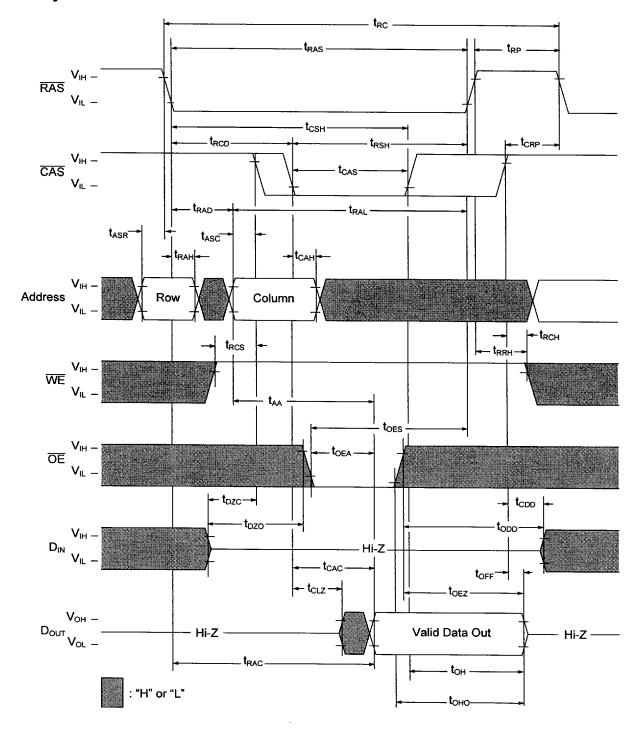

#### **Read Cycle**

| Symbol           | Parameter                             | -4   | 60   | -7   | 70   |       |          |

|------------------|---------------------------------------|------|------|------|------|-------|----------|

| Oymbol           | r arameter                            | Min. | Max. | Min. | Max. | Units | Notes    |

| t <sub>RAC</sub> | Access Time from RAS                  | _    | 60   | _    | 70   | ns    | 1,4      |

| tcac             | Access Time from CAS                  |      | 15   | _    | 18   | ns    | 2,4,7    |

| taa              | Access Time from Address              | _    | 30   | -    | 35   | ns    | 4,7,8    |

| toea             | Access Time From OE                   |      | 15   |      | 18   | ns    | 4,9      |

| t <sub>RCS</sub> | Read Command Setup Time               | 0    |      | 0    |      | ns    | <u> </u> |

| t <sub>RCH</sub> | Read Command Hold Time to CAS         | 0    |      | 0    | _    | ns    | 5        |

| t <sub>RRH</sub> | Read Command Hold Time to RAS         | 0    | _    | 0    | _    | ns    | 5        |

| t <sub>RAL</sub> | Column Address to RAS Lead Time       | 30   |      | 35   |      | ns    |          |

| t <sub>CLZ</sub> | CAS to Output in Low-Z                | 0    |      | 0    |      | ns    | 4        |

| t <sub>ОН</sub>  | Output Data Hold Time                 | 0    | _    | 0    | _    | ns    |          |

| t <sub>оно</sub> | Output Data Hold From OE              | 0    |      | 0    | _    | ns    |          |

| toff             | Output Buffer Turn-Off Delay From CAS | 0    | 15   | 0    | 15   | ns    | 6        |

| toez             | Output Buffer Turn-Off Delay From OE  | 0    | 15   | 0    | 15   | ns    | 6        |

| toes             | OE Setup Time prior to RAS            | 0    | _    | 0    | _    | ns    |          |

| t <sub>CDD</sub> | CAS to D <sub>IN</sub> Delay Time     | 15   |      | 20   | _    | ns    | 3        |

- 1. Assumes that  $t_{RCD} \le t_{RCD}(max)$  and  $t_{RAD} \le t_{RAD}(max)$ . If  $t_{RCD}$  or  $t_{RAD}$  is greater than the maximum recommended value shown in this table, then  $t_{\mbox{\scriptsize RAC}}$  will exceed the value shown.

- 2. Assumes that  $t_{RCD} \ge t_{RCD}(max)$  and  $t_{RAD} \le t_{RAD}(max)$ .

- 3. Either t<sub>CDD</sub> or t<sub>ODD</sub> must be satisfied.

- 4. Measured with a load circuit equivalent to 2 TTL loads and 100pF.

- 5. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a Read cycle.

- 6. t<sub>OFF</sub>(max) and t<sub>OEZ</sub>(max) define the time at which the output achieves the open circuit condition and are not referenced to output voltage levels.

- 7. Access time is determined by the longer of  $t_{AA}$  or  $t_{CAC}$  or  $t_{CPA}$ .

- 8. Assumes that  $t_{RCD} \le t_{RCD}(max)$  and  $t_{RAD} \ge t_{RAD}(max)$ .

- 9. If  $\overline{\text{OE}}$  is tied permanently low, Late-Write or Read-Modify-Write operations are not possible.

## Fast Page Mode Read-Modify-Write Cycle

| Symbol            | Parameter                                   | -60  |      | -70  |             | 11-2- |       |

|-------------------|---------------------------------------------|------|------|------|-------------|-------|-------|

| - Cymbol          |                                             | Min. | Max. | Min. | Max.        | Units | Notes |

| t <sub>PRWC</sub> | Fast Page Mode Read-Modify-Write Cycle Time | 85   | _    | 90   | <del></del> | ns    |       |

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

27H4339 SA14-4219-04

Page 8 of 24

9006146 0002962 749 📟

IBM014400 IBM014400M IBM014400B IBM014400P

1M x 4 10/10 DRAM

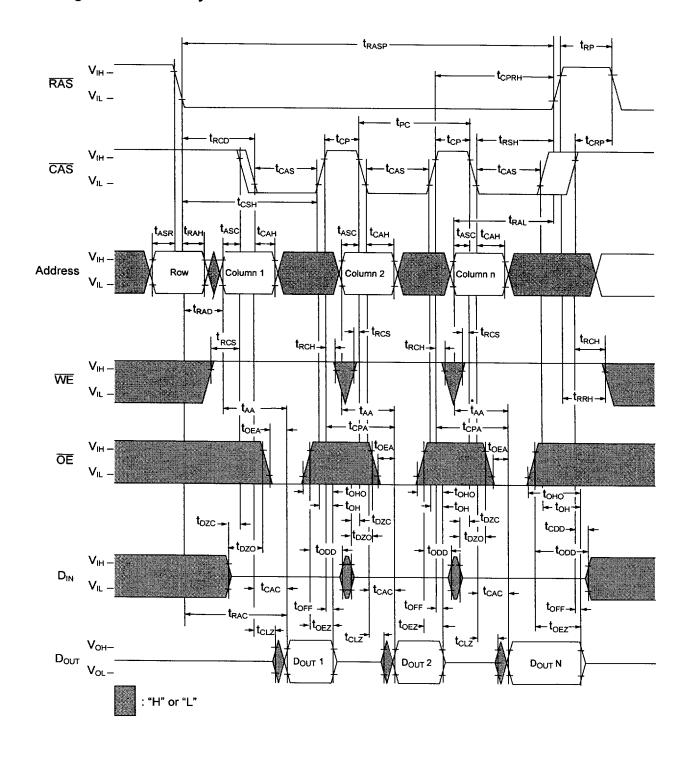

#### **Fast Page Mode Cycle**

| Symbol            | Parameter                        | -1   | -60  |      | -70  |       |       |

|-------------------|----------------------------------|------|------|------|------|-------|-------|

|                   |                                  | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>PC</sub>   | Fast Page Mode Cycle Time        | 40   | _    | 40   | -    | ns    |       |

| t <sub>RASP</sub> | Fast Page Mode RAS Pulse Width   | 60   | 100K | 70   | 100K | ns    | 2     |

| t <sub>CPA</sub>  | Access Time from CAS Precharge   | _    | 35   | _    | 40   | ns    | 1     |

| t <sub>CPRH</sub> | RAS Hold Time from CAS Precharge | 35   | _    | 40   |      | ns    |       |

<sup>1.</sup> Measured with a load circuit equivalent to 2 TTL loads and 100pF.

#### Refresh Cycle

| Symbol           | Parameter                                  |            | -60  |      | -70      |      |       |       |

|------------------|--------------------------------------------|------------|------|------|----------|------|-------|-------|

| - Cyllibor       |                                            |            | Min. | Max. | Min.     | Max. | Units | Notes |

| t <sub>CSR</sub> | CAS Setup Time<br>(CAS before RAS Refresh) |            | 5    | _    | 5        | _    | ns    | 1     |

| t <sub>CHR</sub> | CAS Hold Time<br>(CAS before RAS Refresh)  |            | 10   | _    | 10       |      | ns    | 1     |

| twee             | WE Setup Time<br>(CAS before RAS Refresh)  |            | 10   | _    | 10       | _    | ns    |       |

| t <sub>WRH</sub> | WE Hold Time<br>(CAS before RAS Refresh)   |            | 10   | _    | 10       | -    | ns    |       |

| t <sub>RPC</sub> | RAS Precharge to CAS Hold Time             |            | 0    |      | 0        | _    | ns    |       |

| t <sub>REF</sub> | Refresh period                             | SP version | _    | 16   | _        | 16   | ms    |       |

|                  |                                            | LP version | l –  | 128  | <b> </b> | 128  |       | 2     |

<sup>1.</sup> Enables on-chip refresh and address counters.

## Self Refresh Cycle - Low Power version only

| Symbol            | Parameter                                    | -6   | -60  |      | -70  |       |       |

|-------------------|----------------------------------------------|------|------|------|------|-------|-------|

|                   |                                              | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>RASS</sub> | RAS Pulse Width (Self Refresh)               | 100  |      | 100  | _    | μs    | 1,2   |

| t <sub>RPS</sub>  | RAS Precharge Time During Self Refresh Cycle | 110  | _    | 130  | _    | ns    | 1     |

| t <sub>CHD</sub>  | CAS Hold Time During Self Refresh Cycle      | 10   | _    | 10   | _    | ns    | 1     |

<sup>1.</sup> When using Self Refresh mode, the following refresh operations must be performed to ensure proper DRAM operation: If row addresses are being refreshed in a EVENLY DISTRIBUTED manner over the refresh interval using CBR refresh cycles, then only one CBR cycle must be performed immediately after exit from Self Refresh. If row addresses are being refreshed in a ROR manner over the refresh interval, then a full burst of all row refreshes must be performed immediately before entry to and immediately after exit from Self Refresh. If row addresses are being refreshed in a CBR-Burst manner over the refresh interval (i.e. burst of 8), then upon exiting from Self Refresh the user must conform to whatever refresh (i.e. burst of 8) method that was being used prior to entering Self Refresh.

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 9 of 24

9006146 0002963 985 📟

<sup>2.</sup> t<sub>RASP</sub> defines t<sub>RAS</sub> in fast page mode cycles.

<sup>2. 1024</sup> cycles.

<sup>2.</sup> I/O pins will go into high impedance after 100 us.

## **Read Cycle**

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 10 of 24

9006146 0002964 811

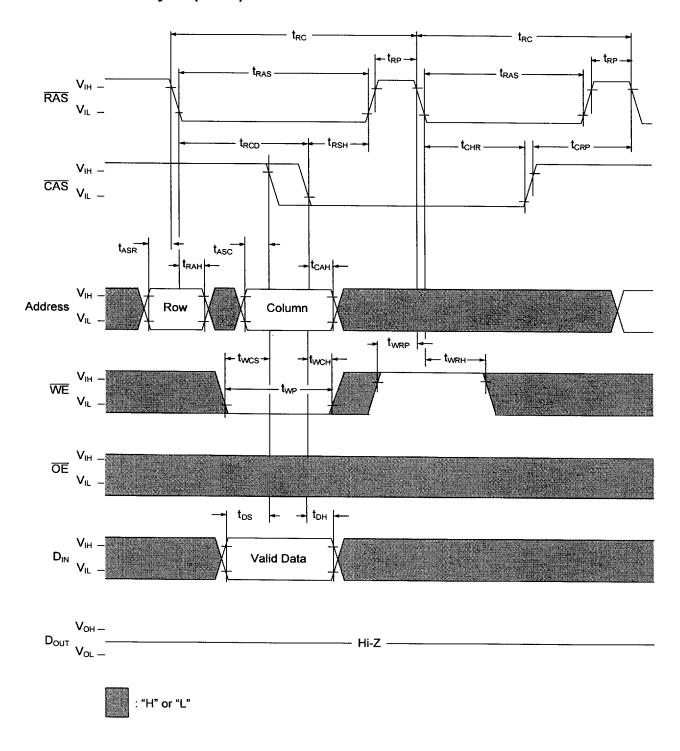

## Write Cycle (Early Write)

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 11 of 24

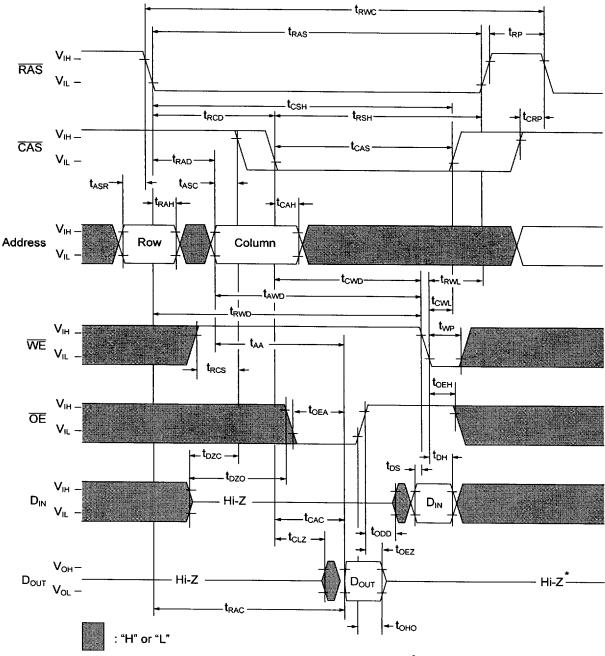

## Write Cycle (Delayed Write)

©IBM Corporation, 1998. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 12 of 24

**---** 9006146 0002966 694 **---**

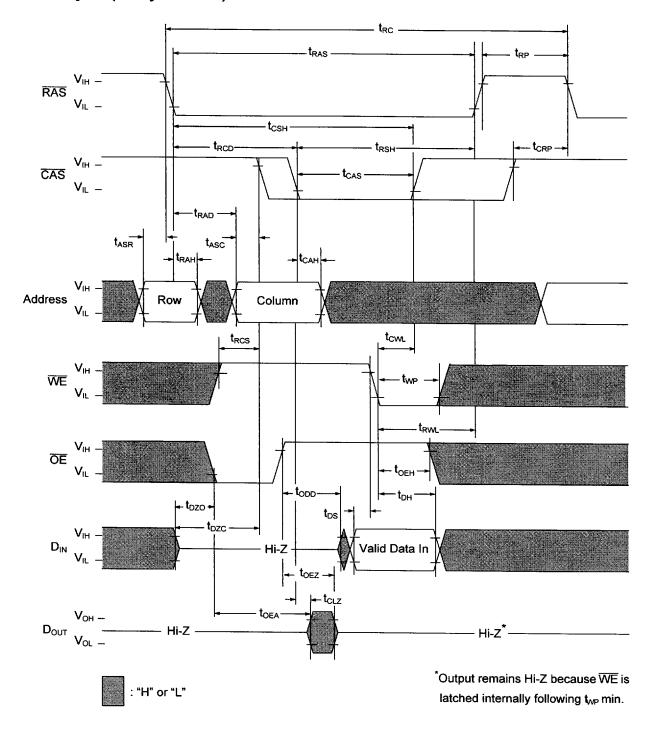

## Read-Modify-Write Cycle

\*Output remains Hi-Z because WE is latched internally following two min.

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 13 of 24

## **Fast Page Mode Read Cycle**

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 14 of 24

9006146 0002968 46?

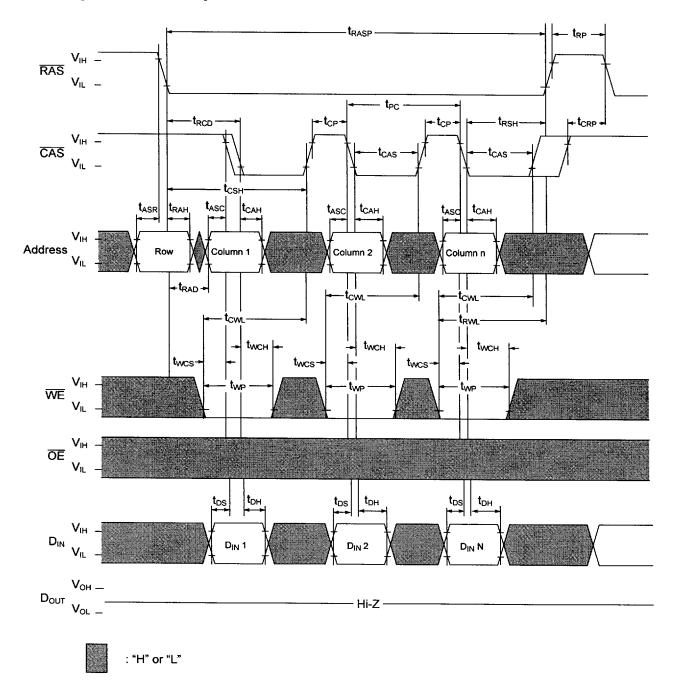

## **Fast Page Mode Write Cycle**

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 15 of 24

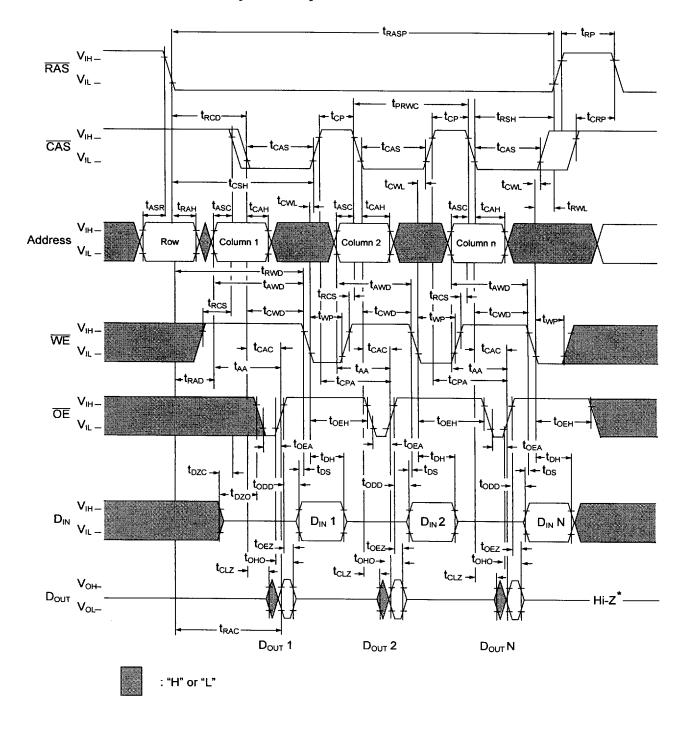

# Fast Page Mode Read-Modify-Write Cycle

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 16 of 24

**--** 9006146 0002970 015 **--**

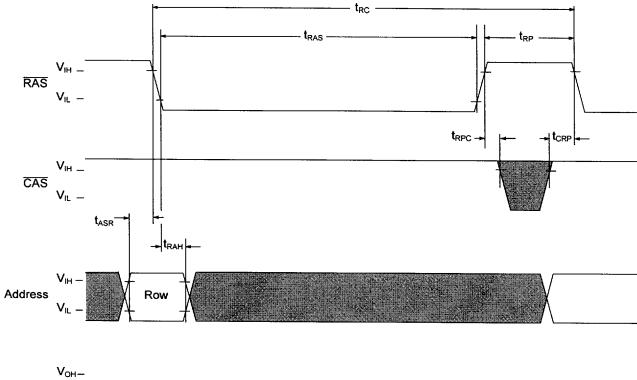

## **RAS** Only Refresh Cycle

: "H" or "L"

NOTE:  $\overline{\text{WE}}$ ,  $\overline{\text{OE}}$  and  $D_{\text{IN}}$  are "H" or "L"

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 17 of 24

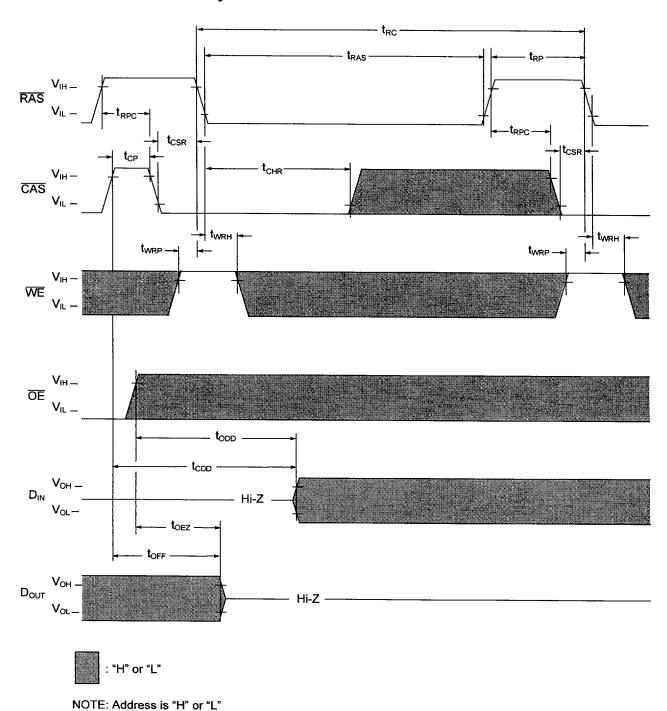

## **CAS** Before RAS Refresh Cycle

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 18 of 24

**--** 9006146 0002972 998 **--**

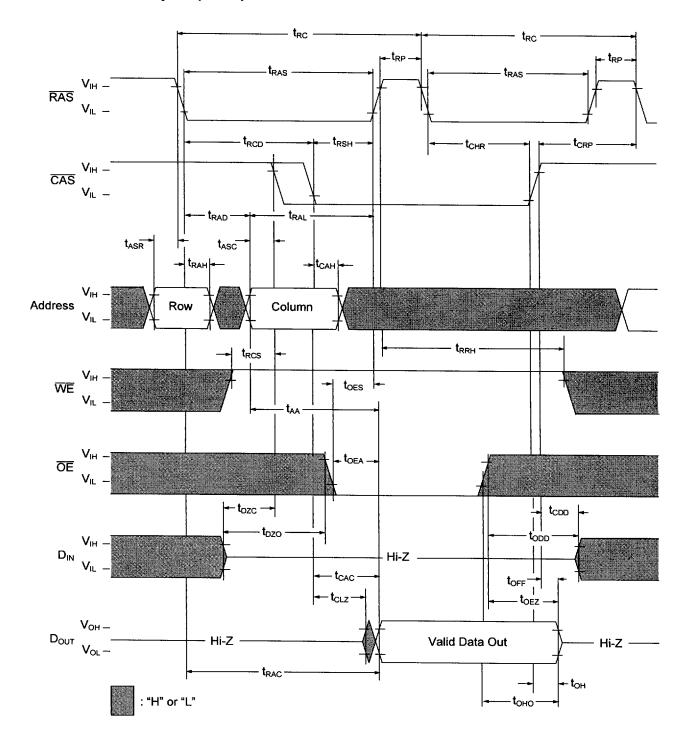

## **Hidden Refresh Cycle (Read)**

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 19 of 24

9006146 0002973 824 **=**

## **Hidden Refresh Cycle (Write)**

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 20 of 24

**■** 9006146 0002974 760 **■**

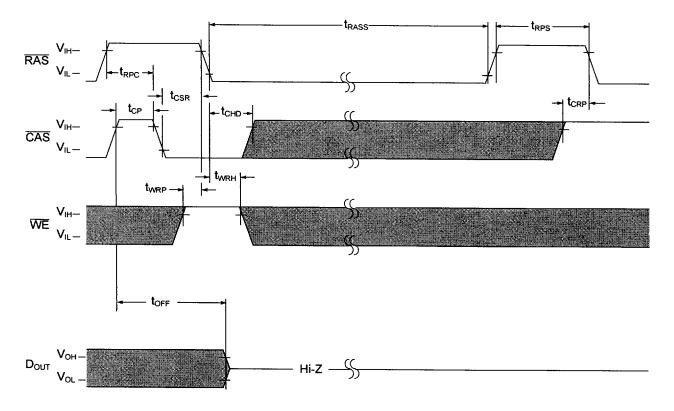

## Self Refresh Cycle (Sleep Mode) - Low Power version only

: "H" or "L"

NOTE: Address and OE are "H" or "L"

Once RAS (min) is provided and RAS remains low, the DRAM will be in Self Refresh, commonly known as "Sleep Mode."

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 21 of 24

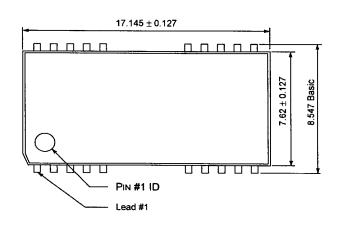

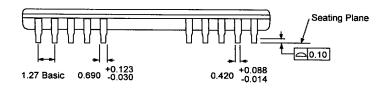

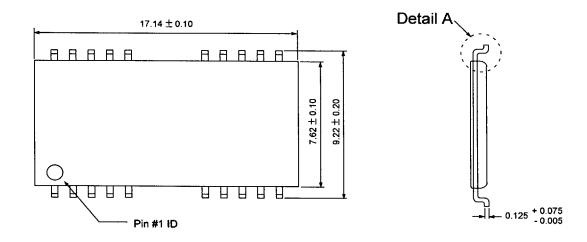

# Package Dimensions (300mil; 26/20 lead; Small Outline J-Lead)

NOTE: All dimensions are in millimeters; Package diagrams are not drawn to scale.

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H4339 SA14-4219-04 Revised 6/96

Page 22 of 24

9006146 0002976 533 📰

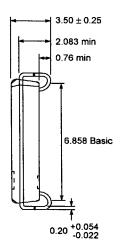

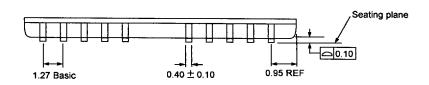

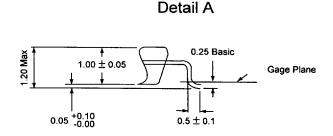

#### PACKAGE DIMENSIONS (300mil; 26/20 lead; Thin Small Outline Package)

NOTE: All dimensions are in millimeters; Package diagrams are not drawn to scale.

27H4339 SA14-4219-04 Revised 6/96

©IBM Corporation, 1996. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 23 of 24

## **Revision Log**

| Revision | Contents of Modification                                                                                                                              |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 12/13/94 | Initial Release                                                                                                                                       |  |  |

| 01/17/95 | t <sub>RPC</sub> removed from CAS Before RAS Refresh Cycle timing diagram (end of cycle only). CAS specified as "Don't Care" after t <sub>CHR</sub> . |  |  |

|          | 2. Corrected t <sub>RPC</sub> value for -70; value changed from 10 to 0.                                                                              |  |  |

|          | Packaging diagrams updated.                                                                                                                           |  |  |

|          | <ol><li>The Low Power and Standard Power Specifications were combined. ES# 27H4338 and ES# 27H4339 were<br/>combined into ES# 27H4339.</li></ol>      |  |  |

|          | 3. Truth Table added.                                                                                                                                 |  |  |

|          | 4. V <sub>IN</sub> and V <sub>OUT</sub> were added to the Absolute Maximum Ratings table.                                                             |  |  |

| 40/40/05 | 5. t <sub>CAH</sub> was changed from 15ns to 10ns for the -70 speed sort.                                                                             |  |  |

| 12/10/95 | 6. t <sub>DH</sub> was reduced from 15ns to 12ns for the -60 speed sort.                                                                              |  |  |

|          | 7. t <sub>CHS</sub> was removed from the Self Refresh Cycle.                                                                                          |  |  |

|          | 8. t <sub>CHD</sub> was added to the Self Refresh Cycle with a value of 10ns for all speed sorts.                                                     |  |  |

|          | 9. The Self Refresh timing diagram was changed to allow CAS to go high t <sub>CHD</sub> (10ns) after RAS falls entering a Self Refresh.               |  |  |

|          | 10. The CBR timing diagram was changed to allow CAS to remain low for back-to-back CBR cycles.                                                        |  |  |

| 05/06/96 | Die Revision G Part Numbers added.                                                                                                                    |  |  |

| 09/00/96 | 2. Add Hidden Refresh (Write) timing diagram.                                                                                                         |  |  |

©IBM Corporation, 1996. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 24 of 24

**9**006146 0002978 306 **5**