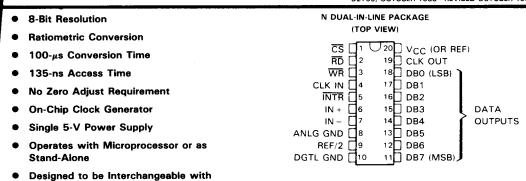

# ADC0804I, ADC0804C 8-BIT ANALOG-TO-DIGITAL CONVERTER WITH DIFFERENTIAL INPUTS

D2755, OCTOBER 1983-REVISED OCTOBER 1988

## description

ADC0804

**National Semiconductor and Signetics**

The ADC0804 is a CMOS 8-bit successive-approximation analog-to-digital converter that uses a modified potentiometric (256R) ladder. The ADC0804 is designed to operate from common microprocessor control buses, with the three-state output latches driving the data bus. The ADC0804 can be made to appear to the microprocessor as a memory location or an I/O port. Detailed information on interfacing to most popular microprocessors is readily available from the factory.

A differential analog voltage input allows increased common-mode rejection and offset of the zero-input analog voltage value. Although a reference input (REF/2) is available to allow 8-bit conversion over smaller analog voltage spans or to make use of an external reference, ratiometric conversion is possible with the REF/2 input open. Without an external reference, the conversion takes place over a span from VCC to analog ground (ANLG GND). The ADC0804 can operate with an external clock signal or, with an additional resistor and capacitor, can operate using an on-chip clock generator.

The ADC0804I is characterized for operation from  $-40\,^{\circ}$ C to  $85\,^{\circ}$ C. The ADC0804C is characterized for operation from  $0\,^{\circ}$ C to  $70\,^{\circ}$ C.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Texas Instruments

Copyright © 1983, Texas Instruments Incorporated

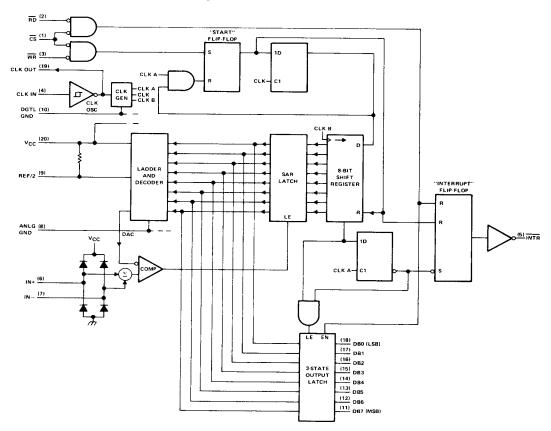

## functional block diagram (positive logic)

##

NOTE 1: All voltage values are with respect to digital ground (DGTL GND) with DGTL GND and ANLG GND connected together (unless otherwise noted).

### recommended operating conditions

|                                                                                                             |          | MIN    | NOM | MAX                    | UNIT |

|-------------------------------------------------------------------------------------------------------------|----------|--------|-----|------------------------|------|

| Supply voltage, V <sub>CC</sub>                                                                             |          | 4.5    | 5   | 6.3                    | V    |

| Voltage at REF/2, V <sub>REF/2</sub> (see Note 2)                                                           |          | 0.25   | 2.5 |                        | V    |

| High-level input voltage at CS, RD, or WR, VIH                                                              |          | 2      |     | 15                     | V    |

| Low-level input voltage at CS, RD, or WR, VIL                                                               |          |        |     | 0.8                    | V    |

| Analog ground voltage (see Note 3)                                                                          |          | -0.05  | 0   | 1                      | V    |

| Analog input voltage (see Note 4)                                                                           |          | - 0.05 |     | V <sub>CC</sub> + 0.05 | V    |

| Clock input frequency, f <sub>clock</sub> (see Note 5)                                                      |          | 100    | 640 | 1460                   | kHz  |

| Duty cycle for f <sub>clock</sub> ≥ 640 kHz (see Note 5)                                                    |          | 40     |     | 60                     | %    |

| Pulse duration clock input (high or low) for f <sub>clock</sub> < 640 kHz, t <sub>w(CLK)</sub> (see Note 5) |          | 275    | 781 |                        | ns   |

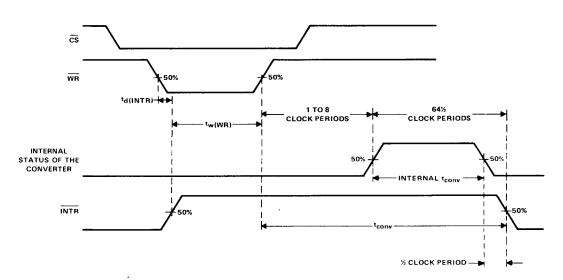

| Pulse duration, WR input low (start conversion), tw(WR)                                                     |          | 100    |     |                        | ns   |

| Operating free-air temperature, TA                                                                          | ADC0804I | - 40   |     | 85                     | °C   |

|                                                                                                             | ADC0804C | 0      |     | 70                     | ٠٠٠  |

- NOTES: 2. The internal reference voltage is equal to the voltage applied to REF/2, or approximately equal to one-half of the V<sub>CC</sub> when REF/2 is left open. The voltage at REF/2 should be one-half the full-scale differential input voltage between the analog inputs. Thus, the differential input voltage when REF/2 is open and V<sub>CC</sub> = 5 V is 0 to 5 V. VREF/2 for an input voltage range from 0.5 V to 3.5 V (full-scale differential voltage of 3 V) is 1.5 V.

- 3. These values are with respect to DGTL GND.

- 4. When the differential input voltage  $(V_{\text{IN}+} V_{\text{in}-})$  is less than or equal to 0 V, the output code is 0000 0000.

- Total unadjusted error is specified only at an f<sub>clock</sub> of 640 kHz with a duty cycle of 40% to 60% (pulse duration 625 ns to 937 ns). For frequencies above this limit or pulse duration below 625 ns, error may increase. The duty cycle limits should be observed for an f<sub>clock</sub> greater than 640 kHz. Below 640 kHz, this duty cycle limit can be exceeded provided t<sub>w(CLK)</sub> remains within limits.

## ADC08041, ADC0804C 8-BIT ANALOG-TO-DIGITAL CONVERTER WITH DIFFERENTIAL INPUTS

# electrical characteristics over recommended operating free-air temperature range, $V_{CC} = 5 \text{ V}$ , $f_{clock} = 640 \text{ kHz}$ , REF/2 = 2.5 V (unless otherwise noted)

| PARAMETER                        |                                        |              | TEST C                               | ONDITIONS                  | MIN       | TYP <sup>†</sup> | MAX | UNIT   |  |

|----------------------------------|----------------------------------------|--------------|--------------------------------------|----------------------------|-----------|------------------|-----|--------|--|

| Vон                              | High-level output voltage              | All outputs  | <del></del>                          | $I_{OH} = -360  \mu A$     | 2.4       |                  |     | _ ···· |  |

|                                  |                                        | DB and INTR  | $V_{CC} = 4.75 V$                    | , I <sub>OH</sub> = -10 μA | 4.5       |                  |     |        |  |

| V <sub>OL</sub>                  |                                        | Data outputs | $V_{CC} = 4.75 \text{ V}$            | , I <sub>OL</sub> = 1.6 mA |           |                  | 0.4 |        |  |

|                                  | Low-level output voltage               | INTR output  | $V_{CC} = 4.75 \text{ V}$            | , I <sub>OL</sub> = 1 mA   |           |                  | 0.4 | V      |  |

|                                  |                                        | CLK OUT      | $V_{CC} = 4.75 V$                    | $I_{OL} = 360  \mu A$      |           |                  | 0.4 |        |  |

| V <sub>T +</sub>                 | Clock positive-going threshold voltage |              |                                      |                            | 2.7 3.1   | 3 1              | 3.5 | V      |  |

|                                  |                                        |              |                                      |                            |           | 3.1              |     |        |  |

| VT -                             | Clock negative-going                   |              |                                      |                            | 1.5 1.8 2 |                  | 2.1 | V      |  |

|                                  | threshold voltage                      |              |                                      |                            | 1.5       | 1.0              | 2.1 |        |  |

| V <sub>T+</sub> - V <sub>7</sub> | T - Clock input hysteresis             |              |                                      |                            | 0.6       | 1.3              | 2   | V      |  |

| ΊΗ                               | High-level input current               |              |                                      |                            |           | 0.005            | 1   | μΑ     |  |

| IIL.                             | Low-level input current                |              |                                      |                            |           | - 0.005          | - 1 | μА     |  |

| loz                              | Off-state output current               |              | V <sub>O</sub> = 0                   |                            |           |                  | -3  |        |  |

|                                  |                                        |              | V <sub>O</sub> = 5 V                 |                            |           |                  | 3   | μΑ     |  |

| lons                             | Short-circuit output current           | Output high  | V <sub>O</sub> = 0,                  | T <sub>A</sub> = 25°C      | -4.5      | 6                |     | mA     |  |

| lols                             | Short-circuit output current           | Output low   | V <sub>O</sub> = 5 V,                | T <sub>A</sub> = 25°C      | 9         | 16               |     | mA     |  |

| lcc                              | Supply current plus reference current  |              | REF/2 open,<br>T <sub>A</sub> = 25°C | CS at 5 V,                 |           | 1.9              | 2.5 | mA     |  |

| R <sub>REF/2</sub>               | Input resistance to reference ladder   |              | See Note 6                           |                            | 1         | 1.3              |     | kΩ     |  |

| Ci                               | Input capacitance (control)            |              |                                      |                            |           | 5                | 7.5 | pF     |  |

| Со                               | Output capacitance (DB)                |              |                                      | -                          |           | 5                | 7.5 | pF     |  |

# operating characteristics over recommended operating free-air temperature range, $V_{CC} = 5 \text{ V}$ , $V_{REF/2} = 2.5 \text{ V}$ , $f_{clock} = 640 \text{ kHz}$ (unless otherwise noted)

|                   | PARAMETER                                          | TEST CONDITIONS                                  | MIN   | TYP <sup>†</sup> | MAX   | UNIT            |

|-------------------|----------------------------------------------------|--------------------------------------------------|-------|------------------|-------|-----------------|

|                   | Supply-voltage-variation error (See Notes 2 and 7) | V <sub>CC</sub> = 4.5 V to 5.5 V                 |       | ± 1/16           | ± 1/8 | L\$B            |

|                   | Total unadjusted error<br>(See Notes 7 and 8)      | V <sub>REF/2</sub> = 2.5 V                       |       |                  | ± 1   | LSB             |

|                   | DC common-mode error<br>(See Note 8)               |                                                  |       | ± 1/16           | ± 1/8 | LSB             |

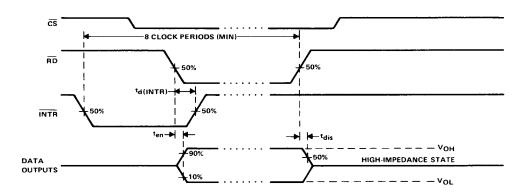

| t <sub>en</sub>   | Output enable time                                 | C <sub>L</sub> = 100 pF                          |       | 135              | 200   | ns              |

| tdis              | Output disable time                                | $C_L = 10 \text{ pF},  R_L = 10 \text{ k}\Omega$ |       | 125              | 200   | ns              |

| td(INTR)          | Delay time to reset INTR                           |                                                  |       | 300              | 450   | ns              |

| <sup>t</sup> conv | Conversion cycle time (See Note 9)                 | f <sub>clock</sub> = 100 kHz to 1.46 MHz         | 651/2 |                  | 721/2 | clock<br>cycles |

|                   | Conversion time                                    |                                                  | 103   |                  | 114   | μS              |

| CR                | Free-running conversion rate                       | INTR connected to WR,<br>CS at 0 V               |       |                  | 8827  | conv/s          |

<sup>†</sup>All typical values are at T<sub>A</sub> = 25 °C.

- NOTES: 2. The internal reference voltage is equal to the voltage applied to REF/2, or approximately equal to one-half of the V<sub>CC</sub> when REF/2 is left open. The voltage at REF/2 should be one-half the full-scale differential input voltage between the analog inputs. Thus, the differential input voltage when REF/2 is open and V<sub>CC</sub> = 5 V is 0 to 5 V. V<sub>REF/2</sub> for an input voltage range from 0.5 V to 3.5 V (full-scale differential voltage of 3 V) is 1.5 V.

- 6. The resistance is calculated from the current drawn from a 5-V supply applied to pins 8 and 9.

- 7. These parameters are specified for the recommended analog input voltage range.

- 8. All errors are measured with reference to an ideal straight line through the end-points of the analog-to-digital transfer characteristic.

- Although internal conversion is completed in 64 clock periods, a CS or WR low-to-high transition is followed by 1 to 8 clock periods before conversion starts. After conversion is completed, part of another clock period is required before a high-to-low transition of INTR completes the cycle.

## timing diagrams

#### READ OPERATION TIMING DIAGRAM

WRITE OPERATION TIMING DIAGRAM

#### PRINCIPLES OF OPERATION

The ADC0804 contains a circuit equivalent to a 256-resistor network. Analog switches are sequenced by successive approximation logic to match an analog differential input voltage ( $V_{in+} - V_{in-}$ ) to a corresponding tap on the 256-resistor network. The most-significant bit (MSB) is tested first. After eight comparisons (64 clock periods), an 8-bit binary code (1111 1111 = full scale) is transferred to an output latch and the interrupt ( $\overline{INTR}$ ) output goes low. The device can be operated in a free-running mode by connecting the  $\overline{INTR}$  output to the write ( $\overline{WR}$ ) input and holding the conversion start ( $\overline{CS}$ ) input at a low level. To ensure start-up under all conditions, a low-level  $\overline{WR}$  input is required during the power-up cycle. Taking  $\overline{CS}$  low anytime after that will interrupt a conversion in process.

When the  $\overline{WR}$  input goes low, the ADC0804 successive approximation register (SAR) and 8-bit shift register are reset. As long as both  $\overline{CS}$  and  $\overline{WR}$  remain low, the ADC0804 remains in a reset state. One to eight clock periods after  $\overline{CS}$  or  $\overline{WR}$  makes a low-to-high transition, conversion starts.

When the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs are low, the start flip-flop is set and the interrupt flip-flop and 8-bit register are reset. The next clock pulse transfers a logic high to the output of the start flip-flop. The logic high is ANDed with the next clock pulse, placing a logic high on the reset input of the start flip-flop. If either  $\overline{\text{CS}}$  or  $\overline{\text{WR}}$  have gone high, the set signal to the start flip-flop is removed, causing it to be reset. A logic high is placed on the D input of the 8-bit shift register and the conversion process is started. If the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs are still low, the start flip-flop, the 8-bit shift register, and the SAR remain reset. This action allows for wide  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  inputs with conversion starting from one to eight clock periods after one of the inputs goes high.

When the logic high input has been clocked through the 8-bit shift register, completing the SAR search, it is applied to an AND gate controlling the output latches and to the D input of a flip-flop. On the next clock pulse, the digital word is transferred to the three-state output latches and the interrupt flip-flop is set. The output of the interrupt flip-flop is inverted to provide an INTR output that is high during conversion and low when the conversion is completed.

When a low is at both the  $\overline{CS}$  and  $\overline{RD}$  inputs, an output is applied to the DBO through DB7 outputs and the interrupt flip-flop is reset. When either the  $\overline{CS}$  or  $\overline{RD}$  inputs return to a high state, the DBO through DB7 outputs are disabled (returned to the high-impedance state). The interrupt flip-flop remains reset.